| Title                | Research and design of high-speed advanced analogue front-ends for fibre-optic transmission systems                                                           |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors              | Quadir, Nasir Abdul                                                                                                                                           |

| Publication date     | 2014                                                                                                                                                          |

| Original Citation    | Quadir, N. A. 2014. Research and design of high-speed advanced analogue front-ends for fibre-optic transmission systems. PhD Thesis, University College Cork. |

| Type of publication  | Doctoral thesis                                                                                                                                               |

| Rights               | © 2014, Nasir Quadir - http://creativecommons.org/licenses/by-nc-nd/3.0/                                                                                      |

| Download date        | 2024-05-07 07:20:31                                                                                                                                           |

| Item downloaded from | https://hdl.handle.net/10468/1767                                                                                                                             |

# RESEARCH AND DESIGN OF HIGH-SPEED ADVANCED ANALOGUE FRONT-ENDS FOR FIBREOPTIC TRANSMISSION SYSTEMS

# BY NASIR ABDUL QUADIR

A THESIS SUBMITTED TO

THE NATIONAL UNIVERSITY OF IRELAND, CORK

FOR THE DEGREE OF

### **DOCTOR OF PHILOSOPHY**

PHOTONICS SYSTEMS GROUP,

TYNDALL NATIONAL INSTITUTE AND DEPARTMENT OF

ELECTRICAL AND ELECTRONIC ENGINEERING,

NATIONAL UNIVERSITY OF IRELAND

IRELAND

### NOVEMBER 2013

RESEARCH SUPERVISOR: DR. PETER OSSIEUR

CO-RESEARCH SUPERVISOR: PROF. PAUL TOWNSEND

HEAD OF THE DEPARTMENT: PROF. NABEEL RIZA

# TABLE OF CONTENTS

| Ta | able of Contents                                                  | 3  |

|----|-------------------------------------------------------------------|----|

| A  | cknowledgements                                                   | 7  |

| ΑI | bstract                                                           | 9  |

| Li | st of Publications                                                | 12 |

| Li | st of Acronyms                                                    | 14 |

| Li | st of Figures                                                     | 17 |

| 1  | Introduction                                                      | 23 |

|    | 1.1MOTIVATION                                                     | 24 |

|    | 1.2 Short reach optical interconnect applications                 | 25 |

|    | 1.2.1 LAN (Local Area Networks) and SAN (storage Area             |    |

|    | Networks)                                                         | 25 |

|    | 1.2.2 Data Centres                                                | 26 |

|    | 1.2.3 High Performance Computing                                  | 27 |

|    | 1.2.4 Consumer Applications                                       | 32 |

|    | 1.3 Overview State-of-the-art Electronics for Short-Reach Optical |    |

|    | Interconnect                                                      | 34 |

|    | 1.4 Optical access and Fibre to the home                          | 35 |

| 2  | Components of Short Reach Optical Interconnect                    | 39 |

|    | 2.1 optical link                                                  | 39 |

|    | 2.1.1 optical fibre                                               | 41 |

|    | 2.1.1.1 Multi-mode Fibre                                          | 42 |

|    | 2.1.1.2 Single mode fibre                                         | 44 |

|    | 2.1.1.3 Multi-mode vs Single Mode                                 | 44 |

|   | While current systems mainly use multimode fibre, a shift      |    |

|---|----------------------------------------------------------------|----|

|   | towards single-mode fibre for short-reach optical              |    |

|   | interconnect is being debated in the industry. It is not clear |    |

|   | what the choices will be                                       | 46 |

|   | 2.1.2 Light Sources                                            | 46 |

|   | 2.1.2.1 Transmitters                                           | 46 |

|   | 2.1.2.1.1 VCSEL Parameters                                     | 48 |

|   | The parameters of the VCSEL light source which are used in the |    |

|   | design are based upon the devices received by the partners in  |    |

|   | the VISIT project tested at Tyndall National Institute and are |    |

|   | listed in Table 2.3                                            | 48 |

|   | 2.1.2.2 Receivers or Photo Detectors                           | 53 |

|   | 2.2 Transimpedance amplifiers                                  | 54 |

|   | 2.3 design in deep submicron CMOS technology                   | 56 |

|   | 2.3.1 Advantages of designing circuits in deep sub-micron      |    |

|   | technologies                                                   | 58 |

|   | 2.3.2 Challenges faced while designing circuits in deep sub-   |    |

|   | micron CMOS technologies                                       | 60 |

|   | 2.4 Summary                                                    | 62 |

| 3 | 40G NRZ VCSEL Driver                                           | 63 |

|   | 3.1 introduction and overview of state-of-the-art              | 63 |

|   | 3.2 General description                                        |    |

|   | 3.2.1 Pulse-Width Adjustment block                             | 70 |

|   | 3.2.2 Pre-Driver Block                                         | 74 |

|   | 3.2.3 Rising and Falling Edge Detector                         | 76 |

|   | 3.2.4 Main Driver with Emphasis                                | 80 |

|   | 3.3 Simulated results                                          | 83 |

|   | 3.4 Packaging and testing                                      | 91 |

|   | 3.5 Summary                                                    | 93 |

| 4 | 56G PAM-4 VCSEL Dri       | ver                                     | 94  |

|---|---------------------------|-----------------------------------------|-----|

|   | 4.1 Introduction and Stat | e-of-the-art                            | 94  |

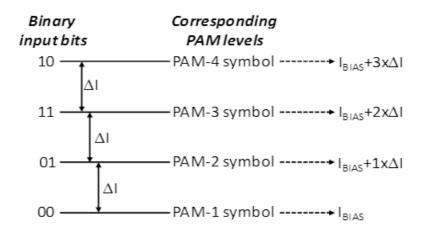

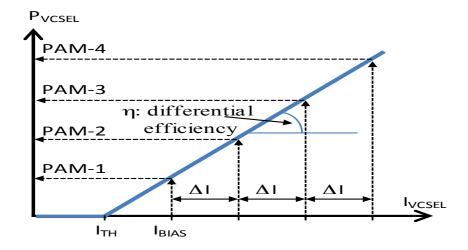

|   | 4.2 PAM Signalling        |                                         | 98  |

|   | 4.3 PAM-4 VCSEL Drive     | r                                       | 99  |

|   | 4.3.1 Binary to The       | rmometer/Gray Encoding                  | 100 |

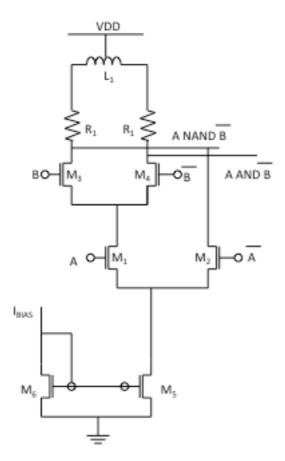

|   | 4.3.1.1 MCML (            | OR GATE                                 | 102 |

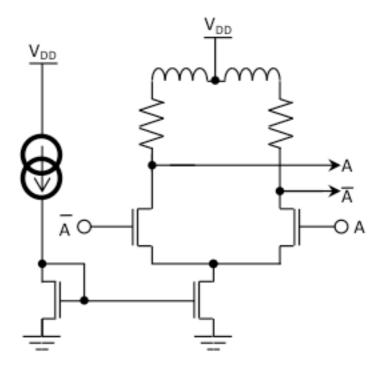

|   | 4.3.1.2 MCML I            | NVERTER                                 | 104 |

|   | 4.3.1.3 MCML A            | AND GATE                                | 104 |

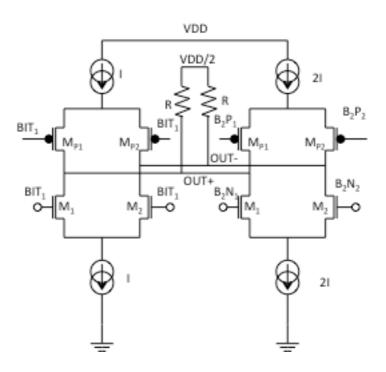

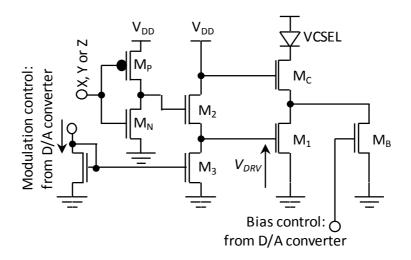

|   | 4.3.2 The VCSEL [         | Priver Circuit                          | 108 |

|   | 4.3.2.1 Modulat           | ion Current Control                     | 115 |

|   | 4.3.2.1.1 Inv             | erter Stage Modulation Current Control  | 116 |

|   | 4.3.2.1.2 Co              | mmon Source Stage Modulation Current    |     |

|   | Control 11                | 9                                       |     |

|   | 4.3.2.1.3 Hig             | h Frequency analysis of Common Source   |     |

|   | Stage 12                  | 2                                       |     |

|   | 4.3.2.1.4 So              | urce-Follower Stage                     | 123 |

|   | 4.3.2.1.5 Hig             | h Frequency Analysis of Common Drain    |     |

|   | stage 12                  | 5                                       |     |

|   | 4.4 Simulated Results     |                                         | 126 |

|   | 4.5 Conclusion            |                                         | 128 |

| 5 | An Inductorless Linear    | Optical Receiver for 20Gbaud PAM-4      |     |

| _ |                           | n CMOS                                  | 131 |

|   |                           |                                         |     |

|   |                           | near Receiver                           |     |

|   |                           | nce Amplifier                           |     |

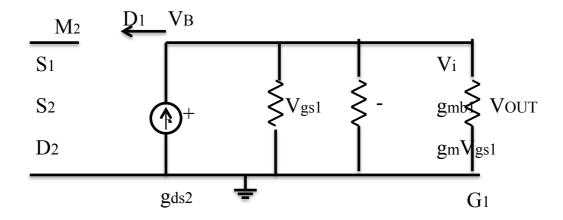

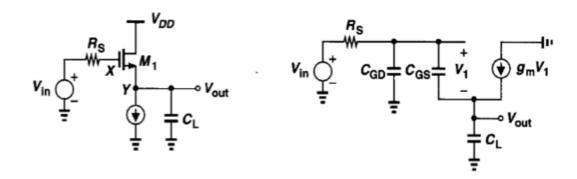

|   |                           | gnal Analysis of Regulated Gate Cascode |     |

|   |                           | gran randy or or regulated Gate Gaeseas | 137 |

|   | _                         | Amplifier                               |     |

|   |                           | of Variable gain amplifier              |     |

|   | )                         | J 1 -                                   |     |

|              | 5.3 Extracted simulation Results                | 143 |

|--------------|-------------------------------------------------|-----|

|              | 5.4 Conclusion                                  | 147 |

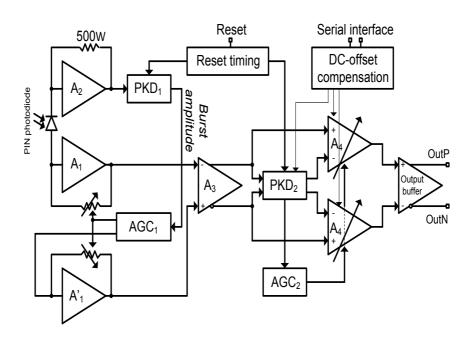

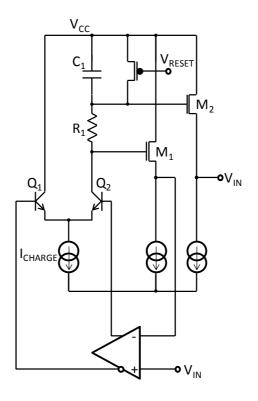

| 6            | Support Circuits for Linear Burst Mode Receiver | 149 |

|              | 6.1 Introduction                                | 149 |

|              | 6.2 Top Level Architecture                      | 152 |

|              | 6.3 Auxilliary transimpedance amplifier         | 155 |

|              | 6.4 Peak Detector                               | 156 |

|              | 6.5 LBMRX Measurement results                   | 161 |

| 7            | Conclusions and Future Work                     | 169 |

| Bibliography |                                                 | 173 |

| Αı           | Appendix A1                                     |     |

### **ACKNOWLEDGEMENTS**

First and foremost my thanks goes to the Almighty Allah Subhanu Wa Taala, The Most Merciful, The Most Beneficent, The most Compassionate whose remembrance helped me in being focussed all through the four years of this research work.

The success of this thesis is largely and greatly attributed to Dr. Peter Ossieur for his continuous support and assistance. I would like to express my grateful gratitude and sincere appreciation to him for his guidance, valuable advice, supervision, encouragement and kindness to me throughout this study in spite of his very busy schedule. I am also extremely grateful to Dr. Paul Tonwsend for providing continuous suggestions for improvement and encouragement during my time here

I would further like to thank all the colleagues in Photonics systems group, especially to Anil Jain, Asfandyar Khan and Vamshi Manthena for the number of technical discussions that we had and not forgetting the great insights into the layout skills. A warm thanks to Martina for helping me with countless administrative jobs. Great thanks is also extended to all my friends of Cork and to my house mates, Benzir, Tanim, Shahidul, Mohan, Abdul Razzaq and Tanveer for their cheerful encouragement, help, support and enjoyment and not to forget the delicious meals that they cooked for me. A special thank to Dr. Zubair Kabir and Cork DII team for introducing me to things which will always be beneficial for me.

A special thanks to my parents and my in-laws for providing care and support for my wife and kids in my absence. And in the end all the accolades goes to my wife Hijab Jamil and to my two beautiful kids for their patience and encouragement.

I would also like to acknowledge Science foundation Ireland (SFI) funding this project.

Nasir Abdul Quadir

Cork, Ireland

### **ABSTRACT**

In the last decade, we have witnessed the emergence of large, warehouse-scale data centres which have enabled new internet-based software applications such as cloud computing, search engines, social media, e-government etc. Such data centres consist of large collections of servers interconnected using short-reach (reach up to a few hundred meters) optical interconnect. Today, transceivers for these applications achieve up to 100Gb/s by multiplexing 10x 10Gb/s or 4x 25Gb/s channels. In the near future however, data centre operators have expressed a need for optical links which can support 400Gb/s up to 1 Tb/s. The crucial challenge is to achieve this in the same footprint (same transceiver module) and with similar power consumption as today's technology. Straightforward scaling of the currently used space or wavelength division multiplexing may be difficult to achieve: indeed a 1Tb/s transceiver would require integration of 40 VCSELs (vertical cavity surface emitting laser diode, widely used for short-reach optical interconnect), 40 photodiodes and the electronics operating at 25Gb/s in the same module as today's 100Gb/s transceiver. Pushing the bit rate on such links beyond today's commercially available 100Gb/s/fibre will require new generations of VCSELs and their driver and receiver electronics. This work looks into a number of state-of-theart technologies and investigates their performance restraints and recommends different set of designs, specifically targeting multilevel modulation formats.

Several methods to extend the bandwidth using deep submicron (65nm and 28nm) CMOS technology are explored in this work, while also maintaining a focus upon reducing power consumption and chip area. The techniques used were preemphasis in rising and falling edges of the signal and bandwidth extensions by inductive peaking and different local feedback techniques. These techniques have been applied to a transmitter and receiver developed for advanced modulation formats such as PAM-4 (4 level pulse amplitude modulation). Such modulation format can increase the throughput per individual channel, which helps to overcome the challenges mentioned above to realize 400Gb/s to 1Tb/s transceivers.

### STATEMENT OF ORIGINALITY

I hereby certify that I am the sole author of this thesis. Except where indicated, all the work presented in this thesis is solely attributed to the author. Precise details of collaborators may be ascertained from the list of co-authors in the *List of Publications*.

I declare that this is a true copy of my thesis and has not been submitted for another degree to any other University or Institution.

# LIST OF PUBLICATIONS

### **JOURNALS**

- J1. P. Ossieur, N.A. Quadir, S. Porto, C. Antony, W. Han, M. Rensing, P. O'Brien and P.D. Townsend, "A 10Gb/s linear burst-mode receiver in 0.25μm SiGe BiCMOS", *IEEE Journal of Solid State Circuits*, 2013. 48(2): p. 381-390.

- J2. P. Ossieur, N. A. Quadir, S. Porto, M. Rensing, C. Antony, P. O'Brien, Y (Frank) Chang, and P. D. Townsend, "A 10G Linear Burst-Mode Receiver Supporting Electronic Dispersion Compensation for Extended-Reach Optical Links," Optics Express, vol. 19, iss. 26, pp. 604–B10, Dec 2011.

- J3. M.V. Krishna, A. Jain, N.A. Quadir, P.D. Townsend and P. Ossieur, "Progammable multi-modulus frequency dividers using Low Power True Single-Phase Clocked CMOS 2/3 and 4/5 Dividers," in preparation for submission to *Transactions on Circuits and Systems-I*.

### CONFERENCES

- C1. N. A. Quadir, P. D. Townsend and P. Ossieur, "An inductorless linear optical receiver for 20Gbaud (40Gb/s) PAM-4 modulation using 28nm CMOS", submitted to *ISCAS 2014* Melbourne.

- C2. <u>N.A. Quadir</u>, P.D. Townsend and P. Ossieur, "Design of a 40Gb/s, 20Gbaud PAM-4 VCSEL Driver with Digitally Programmable Bias and Modulation Currents using 65nm CMOS", submitted to *ISCAS 2014* Melbourne.

- C3. P. Ossieur, S. Porto, C. Antony, A. Jain, D. Kelly, **N.A. Quadir**, G. Talli and P.D. Townsend "Burst-mode electronic dispersion compensation", (invited) in *Proceedings Optical Fiber Conference* (OFC'2014), San Francisco, USA, March 2014.

- C4. **N. Quadir**, P.D. Townsend and P. Ossieur, "Feasibility of a small footprint linear optical receiver for 50Gb/s PAM-4 using 28nm CMOS". *Photonics Ireland Conference*, Belfast 2013.

- C5. P. Ossieur, C. Antony, A. Naughton, S. Porto, <u>N.A. Quadir</u>, A.M. Clarke and P.D. Townsend, "Hybrid DWDM-TDMA PONs for Next Generation Access," (invited) in *Proceedings Optical Fiber Conference* (OFC'2012), Paper OW1B.7, Los Angeles, USA, March 2012.

- C6. N. Quadir, P. Ossieur and P. D. Townsend, "A 56Gb/s PAM-4 VCSEL driver circuit", ISSC 2012, NUI Maynooth, June 28-29.

- C7. P. Ossieur, N.A. Quadir, S. Porto, M. Rensing, C. Antony, W. Han, P. O'Brien and P.D. Townsend, "A 10Gb/s linear burst-mode receiver", Irish Systems and Signals Conference 2012, Maynooth, Ireland, June.

- C8. P. Ossieur, N.A Quadir, S. Porto, M. Rensing, C. Antony, W. Han, P.O. Brien, Y. (Frank) Chang and P.D. Townsend, "A 10G linear burst-mode receiver supporting electronic dispersion compensation for extended-reach optical links," European Conference on Optical Communication (ECOC'2011), Postdeadline Paper Th.13.B.4, Geneva, Switzerland, Sept. 2011.

- C9. P. Ossieur, M. Rensing, M. Mulcahy, W. Han, P. O'Brien, N. A Quadir, A. Jain and P. D. Townsend, "Packaging technology for a 10Gb/s burst-mode receiver", *Photonics Ireland* 2011 Conference, Dublin, Ireland.

- C10. N. A. Quadir, A. Jain, P. Ossieur and P.D. Townsend, "Low-power, high speed CMOS driver circuits for high-capacity, short-reach optical data-links", *Photonics Ireland 2011 Conference*, Dublin, Ireland.

# LIST OF ACRONYMS

| AC     | Alternating Current                             |

|--------|-------------------------------------------------|

| ADC    | analogue-to-digital converter                   |

| ADSL   | Asymmetric digital subscriber line              |

| AGC    | Automatic Gain Control                          |

| APD    | Avalanche Photo Diode                           |

| BiCMOS | Bipolar Complementary Metal Oxide Semiconductor |

| BIMMF  | Bend Insensitive Multi-Mode Fibre               |

| CAPEX  | Capital Expenditure                             |

| CATV   | Cable Television                                |

| СМ     | Common Mode                                     |

| CMFB   | Common Mode Feed Back                           |

| CML    | Current Mode Logic                              |

| CMOS   | Complementary Metal Oxide Semiconductor         |

| CATV   | Cable Television                                |

| CM     | Common Mode                                     |

| CMFB   | Common Mode Feed Back                           |

| D/A    | Digital/Analogue                                |

| DAC    | Digital to Analogue Converter                   |

| DC     | Direct Current                                  |

| DFB    | Distributed Feedback                            |

| DSLAM  | Digital Subscriber Line Access Multiplexer      |

| EDC    | Electronic Dispersion Compensation              |

| EDFA   | Erbium Doped Fiber Amplifier                    |

| EMI    | Electromagnetic Interference                         |

|--------|------------------------------------------------------|

| E/O    | Electrical/Optical                                   |

| ER     | Extinction Ratio                                     |

| ESD    | Electrostatic Discharge                              |

| FDSOI  | Fully Depleted Silicon On Insulator                  |

| FEC    | Forward Error Correction                             |

| FF     | Fast Fast                                            |

| FP     | Fabry Perot                                          |

| FR4    | Flame Retardant 4                                    |

| FS     | Fast Slow                                            |

| FTTH   | Fibre to the home                                    |

| GBPS   | Giga Bit Per Second                                  |

| Gbyte  | Giga Byte                                            |

| GHz    | Giga Hertz                                           |

| GPPO   | Gilbert Push On Connector for high speed application |

| HDTV   | High Definition Television                           |

| 1/0    | Input/Ouput                                          |

| 10     | Input Ouput                                          |

| LAN    | Local Area Network                                   |

| LBMRx  | Linear Burst Mode Receiver                           |

| LNA    | Low Noise Amplifier                                  |

| Mb/s   | Mega Bits per Second                                 |

| MCML   | Metal oxide semiconductor Current Mode Logic         |

| MoM    | Metal on Metal                                       |

| MOSFET | Metal-Oxide Semiconductor Field-Effect Transistor    |

| NA     | Numerical Aperture                                   |

| NMOS   | Negative Metal Oxide Semiconductor                   |

| NRZ   | Non Return to Zero                      |

|-------|-----------------------------------------|

| O/E   | Optical/Electrical                      |

| OLT   | Optical Line Termination                |

| ONU   | Optical Network Unit                    |

| OPEX  | Operative Expenditures                  |

| PAM   | Pulse Amplitude Modulation              |

| PC    | Personal Computer                       |

| РСВ   | Printed Circuit Board                   |

| PKD   | Peak Detector                           |

| PMOS  | Positive Metal-Oxide Semiconductor      |

| PON   | Passive Optical Network                 |

| PRBS  | Pseudo Random Bit Sequence              |

| PVT   | Process Voltage Temperature             |

| PWD   | Pulse Width Distortion                  |

| RGC   | Regulated Gate Cascode                  |

| SAN   | Storage Area Network                    |

| SCM   | Sub-Carrier Multiplexing                |

| SiGe  | Silicon Germanium                       |

| SF    | Slow Fast                               |

| SS    | Slow Slow                               |

| TDMA  | Time Division Multiple Access           |

| TIA   | Transimpedance Amplifier                |

| TIR   | Total Internal Reflection               |

| THD   | Total Harmonic Distortion               |

| VCSEL | Vertical Cavity Surface Emitting Laser  |

| VDSL  | Very High Speed Digital Subscriber Line |

| VGA   | Variable Gain Amplifier                 |

# LIST OF FIGURES

| Fig.1.1 Photonics is getting closer to the processor and memory                                                                                                                                   | 24       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Fig.1.2 Optical interconnects in the LAN and SAN networking arena.                                                                                                                                | 26       |

| Fig.1.3 A typical data centre network.                                                                                                                                                            | 27       |

| Fig.1.4 Conceptual view of a high-performance supercomputer (Blue Gene): the compute (containing the processors with memory) and IO cards are assembled into "node cards are basically backplanes | s" which |

| Fig.1.5 Insertion loss (dB/m) of a 100 Ωmatched differential transmission line versus frequen (Avago application note AN5362)                                                                     | •        |

| Fig.1.6 Electrical and optical cabling in supercomputers                                                                                                                                          | 31       |

| Fig.1.7 Optical to Optical communication between chips externally                                                                                                                                 | 31       |

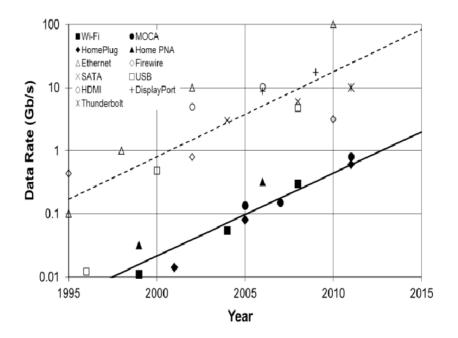

| Fig.1.8 Data rate evolutions of various protocols commonly used in "backbone" homenet (closed symbols) and for device-to-device direct communication (open symbols)                               |          |

| Fig.1.9 Thunderbolt technology by Intel                                                                                                                                                           | 33       |

| Fig.1.10 Present day communication network                                                                                                                                                        | 35       |

| Fig.1.11 A typical PON system                                                                                                                                                                     | 37       |

| Fig.2.1 A basic Fibre optic communication system (non-return to zero modulation)                                                                                                                  | 40       |

| Fig.2.2 Makeup of an optical fibre.                                                                                                                                                               | 42       |

| Fig.2.3 light travelling in multi-mode fibre                                                                                                                                                      | 43       |

| Fig.2.4 light travelling in Multi-mode graded index fibre.                                                                                                                                        | 43       |

| Fig.2.5 light propagating through single mode Fibre                                                                                                                                               | 44       |

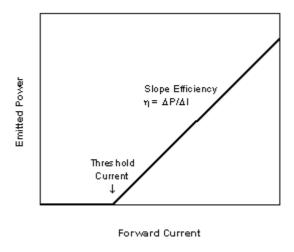

| Fig.2.6 Emitted power as a function of current.                                                                                                                                                   | 50       |

| Fig.2.7 Understanding slope effeciency                                                                                                                                                            | 50       |

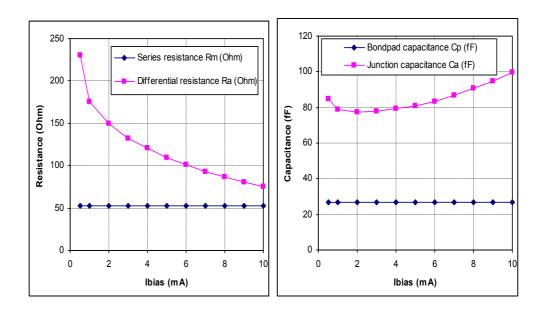

| Fig.2.8 Series resistance and Junction Capacitance with Ibias of VCSEL                                                                                                                            | 51       |

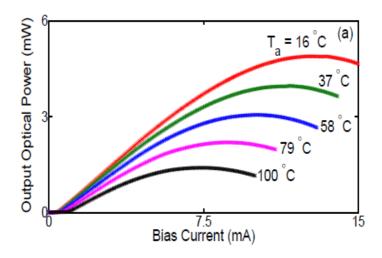

| Fig.2.9 Thermal rollover phenomena of VCSEL                                                                                                                                                       | 52       |

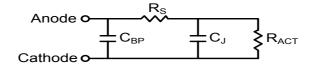

| Fig.2.10 VCSEL parasitics.                                                                                                                                                                        | 52       |

| Fig.2.11 Complete VCSEL model.                                                                                                                                                                    | 53       |

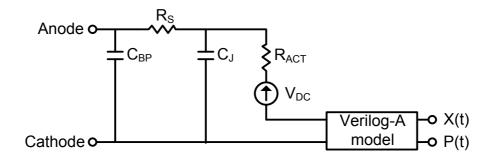

| Fig.2.12 Input current for THD testing                                                                                                                                                            | 54       |

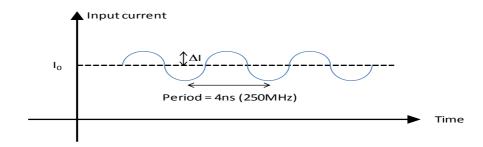

| Fig2.13 Circuit Design Flow Chart.                                                                                                                                                                | 57       |

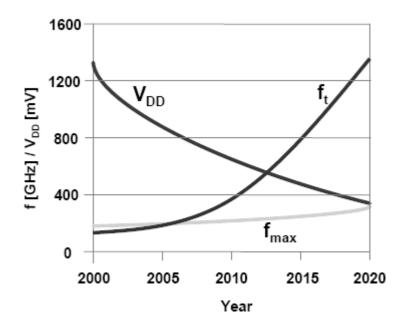

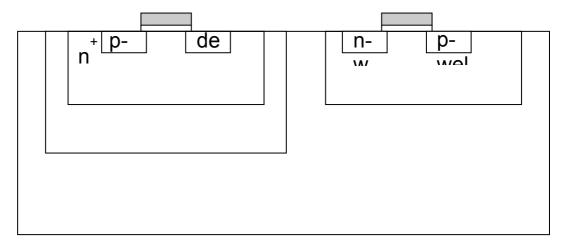

| Fig.2.14 Trends of the MOSFET scaling                                                                                                                                                             | 59       |

| Fig.2.15 Triple N-well Process                                                                                                                                                                    | 60       |

| Fig.3.1 Emphasis operation at rising and falling edge                                                                                                                                                                                                                                                                                                                                            | . 64 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

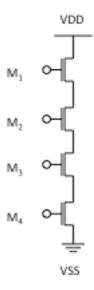

| Fig.3.2 Stack of four transistors                                                                                                                                                                                                                                                                                                                                                                | . 65 |

| Fig.3.3 Common-Anode Connection                                                                                                                                                                                                                                                                                                                                                                  | . 66 |

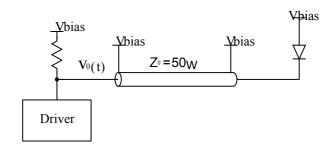

| Fig.3.4 VCSEL driver with termination resistor                                                                                                                                                                                                                                                                                                                                                   | . 67 |

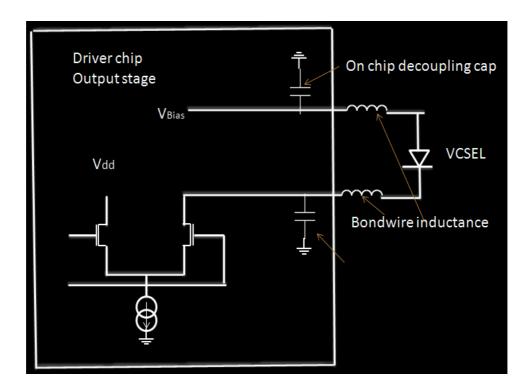

| Fig.3.5 Driver Connection with VCSEL                                                                                                                                                                                                                                                                                                                                                             | . 67 |

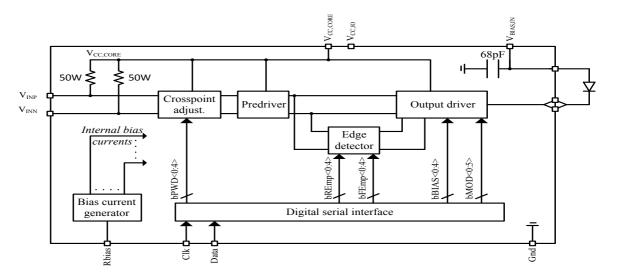

| Fig.3.6 Functional block diagram of the VCSEL driver.                                                                                                                                                                                                                                                                                                                                            | . 68 |

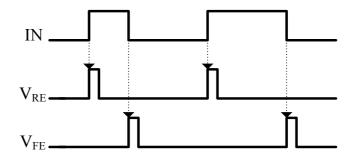

| Fig.3.7 Functionality of the edge detector.                                                                                                                                                                                                                                                                                                                                                      | . 69 |

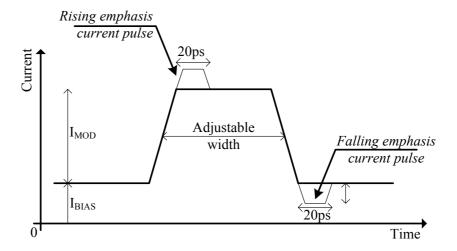

| Fig.3.8 Shape of the output current waveform.                                                                                                                                                                                                                                                                                                                                                    | . 69 |

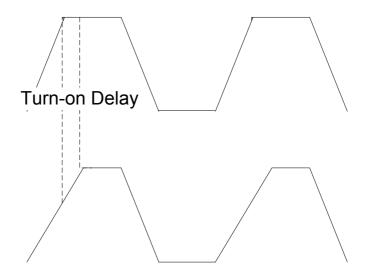

| Fig.3.9 Optical pulse shortening due to turn- on delay in VCSEL                                                                                                                                                                                                                                                                                                                                  | . 71 |

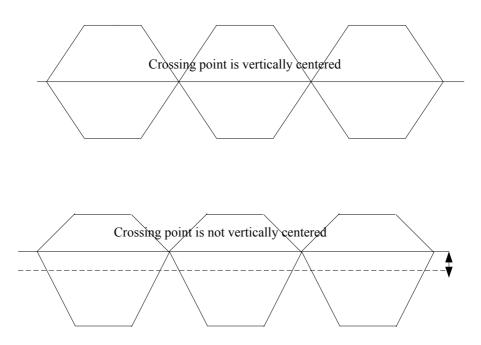

| Fig.3.10 Pulse Width Distortion due to pulse lengthening or shortening                                                                                                                                                                                                                                                                                                                           | . 71 |

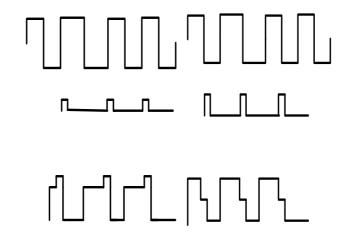

| Fig.3.11 Cross-point adjustment block                                                                                                                                                                                                                                                                                                                                                            | . 72 |

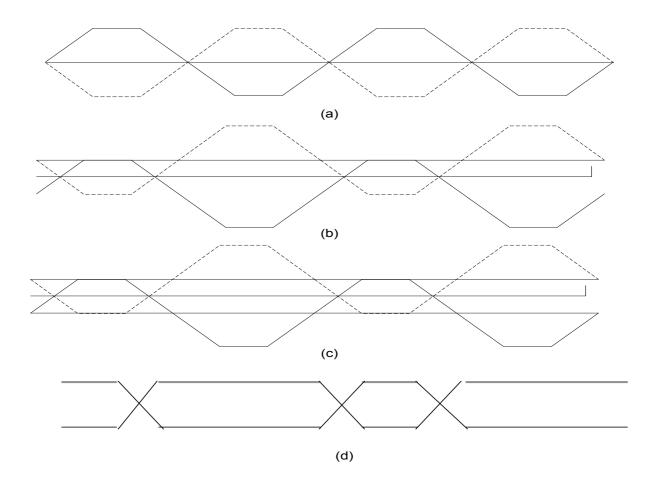

| Fig.3.12 Pulse-Width adjustment signal flow. (a) Signal at the output of the differential amplifier M and $M_2$ . (b) Signal at the output of the differential amplifier after applying the dc offset through the second differential amplifier $M_3$ and $M_4$ by varying VPWD. (c) Amplitude limitin function of the next stage (Pre-Driver Block). (d) Final signal with modified pulse-width | ng   |

| Fig.3.13 Pre-Driver                                                                                                                                                                                                                                                                                                                                                                              | . 74 |

| Fig.3.14 Active feedback structure                                                                                                                                                                                                                                                                                                                                                               | . 75 |

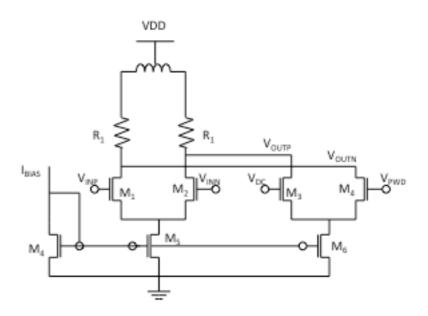

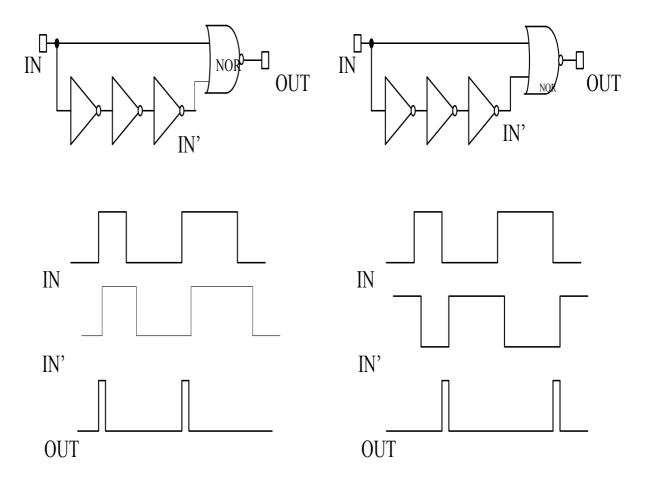

| Fig.3.15 Pulse Generator schematic                                                                                                                                                                                                                                                                                                                                                               | . 77 |

| Fig.3.16 Rising and falling edge detector                                                                                                                                                                                                                                                                                                                                                        | . 78 |

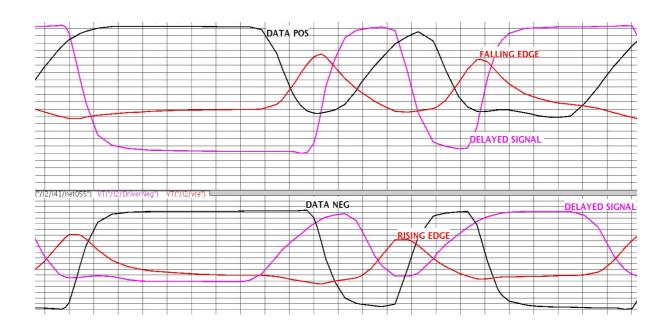

| Fig.3.17 Rising and Falling edge generated from Pulse Generator block                                                                                                                                                                                                                                                                                                                            | . 79 |

| Fig.3.18 Main driver circuit                                                                                                                                                                                                                                                                                                                                                                     | . 80 |

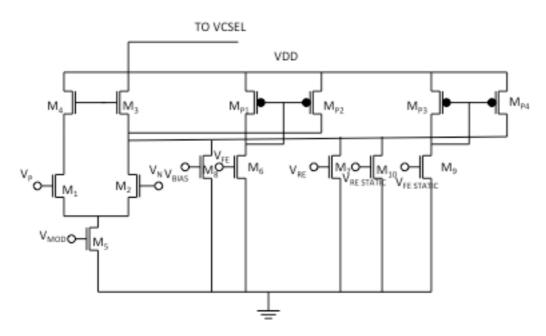

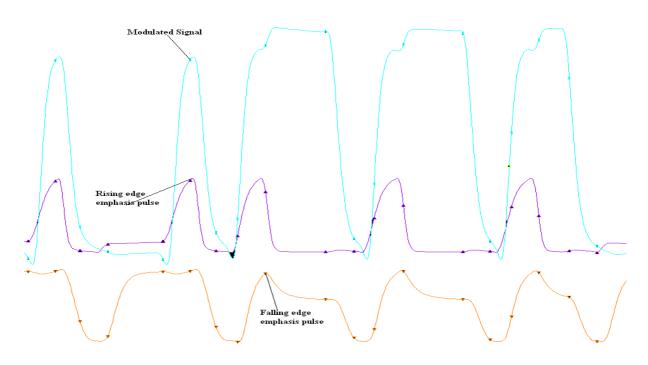

| Fig.3.19 Rising and Falling edge emphasis pulses                                                                                                                                                                                                                                                                                                                                                 | . 81 |

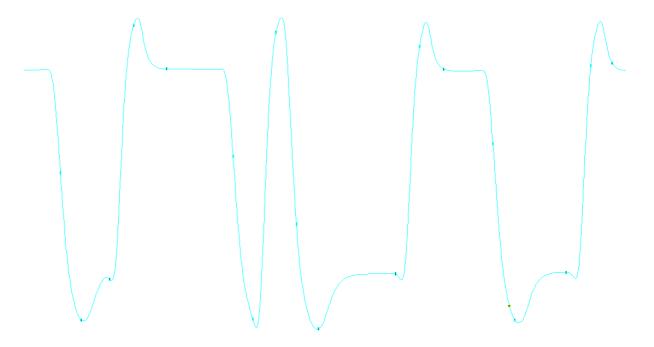

| Fig.3.20 Modulated signal after the addition of pre-emphasis pulses                                                                                                                                                                                                                                                                                                                              | . 82 |

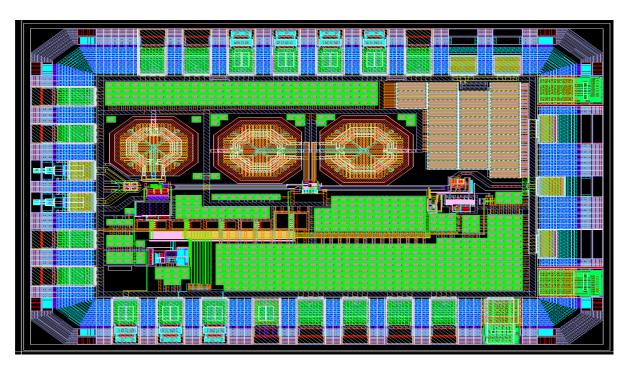

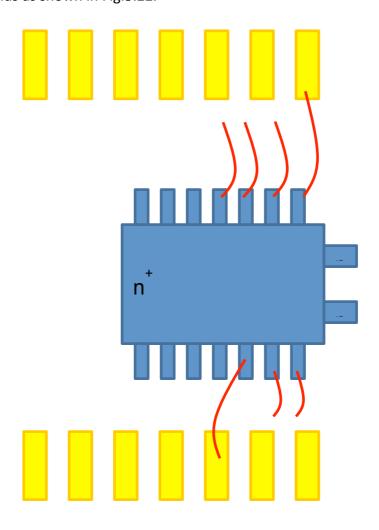

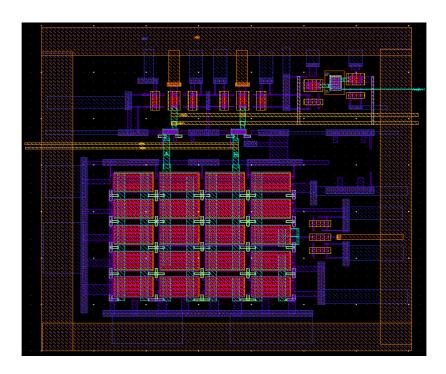

| Fig.3.21 Layout of the complete 40Gbps VCSEL Driver for NRZ modulation                                                                                                                                                                                                                                                                                                                           | . 82 |

| Fig.3.22 Chip Connections with PCB                                                                                                                                                                                                                                                                                                                                                               | . 83 |

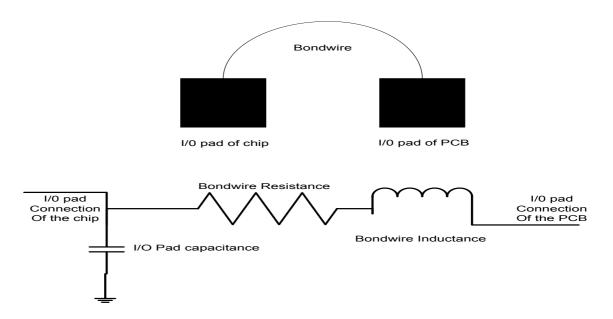

| Fig.3.23 Modelling of I/O pads and Bondwires                                                                                                                                                                                                                                                                                                                                                     | . 84 |

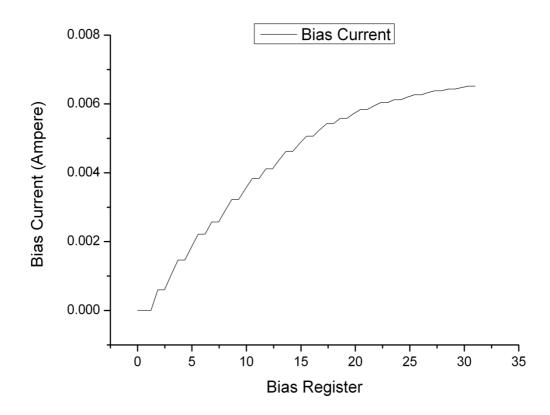

| Fig.3.24 Bias current as a function of the bias register value                                                                                                                                                                                                                                                                                                                                   | . 85 |

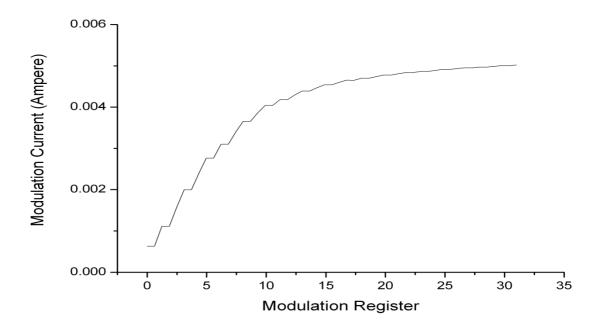

| Fig.3.25 Modulation current as function of the modulation register value                                                                                                                                                                                                                                                                                                                         | . 86 |

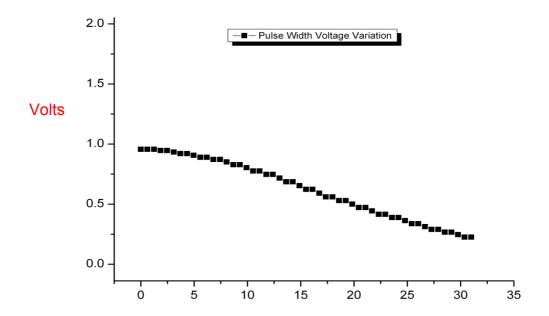

| Fig.3.26 Pulse Width Voltage versus register value                                                                                                                                                                                                                                                                                                                                               | . 87 |

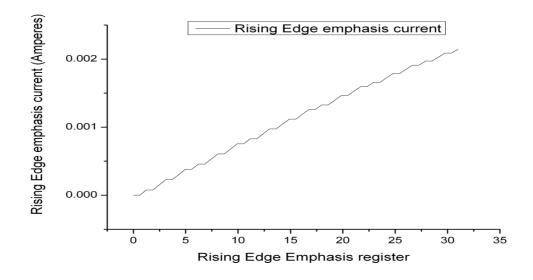

| Fig.3.27 Rising edge emphasis current versus register value.                                                                                                                                                                                                                                                                                                                                     | . 87 |

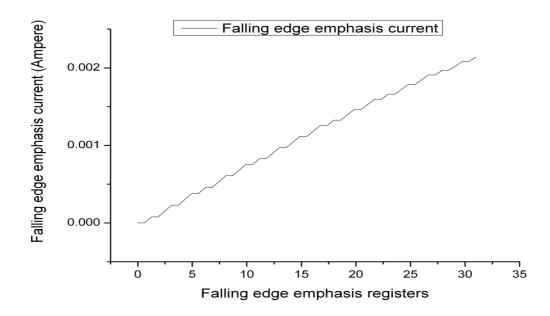

| Fig.3.28 Falling edge emphasis current versus register value.                                                                                                                                                                                                                                                                                                                                    | . 88 |

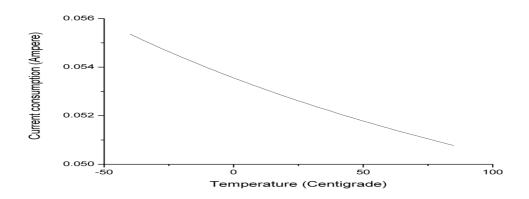

| Fig.3.29 Maximum Current Consumption with Bias, Modulation, Falling and Rising edge emphasis currents set at maximum                                                                                                                                                                                                                                                                             |      |

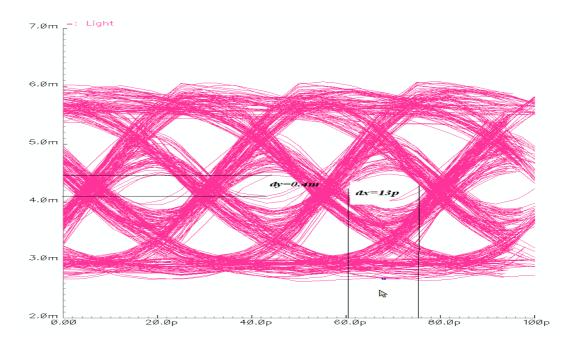

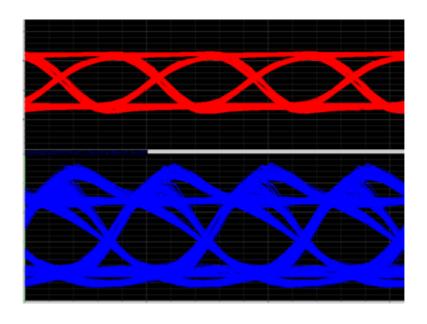

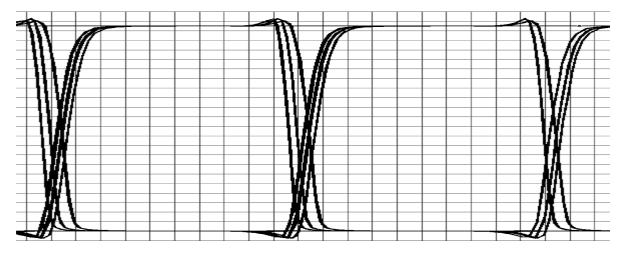

| Fig.3.30 Eye diagram before emphasis                                                                                                                                                                                                                                                                                                                                                             | . 89 |

| Fig. 3.31 Eve diagram after emphasis has been applied                                                                                                                                                                                                                                                                                                                                            | . 90 |

| Fig.3.32 Simulated eye diagram electrical (red) and optical (blue)                                     | 90  |

|--------------------------------------------------------------------------------------------------------|-----|

| Fig.3.33 Connection of VCSEL and the driver                                                            | 91  |

| Fig.3.34 Butterfly Package                                                                             | 92  |

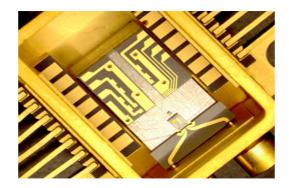

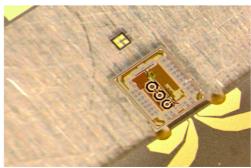

| Fig.3.35 VCSEL Driver mounted on butterfly module                                                      | 92  |

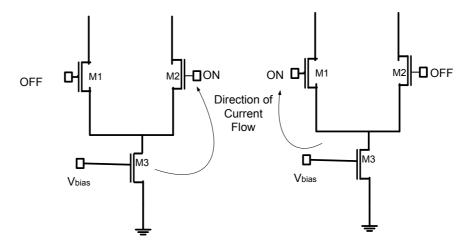

| Fig.4.1 Tail current always flowing whether modulation signal is present or not                        | 95  |

| Fig.4.2 Bipolar topology presented to switch the current from ±RI to ±2RI                              | 96  |

| Fig.4.3 PAM-4 modulation and Gray encoding of binary input bits.                                       | 98  |

| Fig.4.4 VCSEL Power vs. Current Relationship                                                           | 99  |

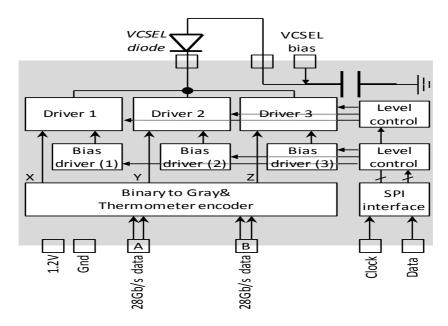

| Fig.4.5 PAM-4 VCSEL driver diagram (SPI = serial peripheral interface)                                 | 100 |

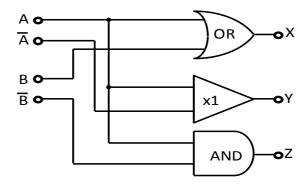

| Fig.4.6 Binary to Thermometer Encoder                                                                  | 101 |

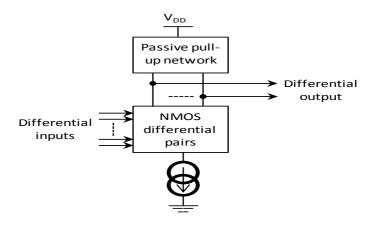

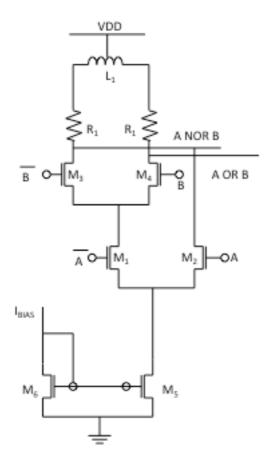

| Fig.4.7 MCML gates.                                                                                    | 102 |

| Fig.4.8 MCML OR/NOR gate                                                                               | 103 |

| Fig.4.9 MCML inverter/buffer gate                                                                      | 104 |

| Fig.4.10 MCML AND gate                                                                                 | 105 |

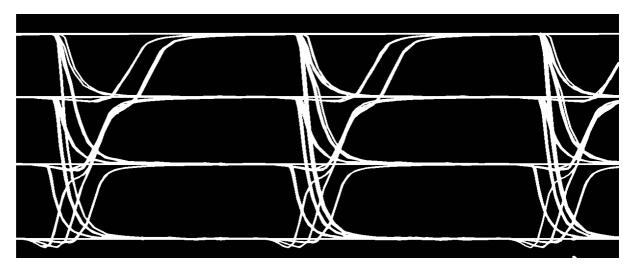

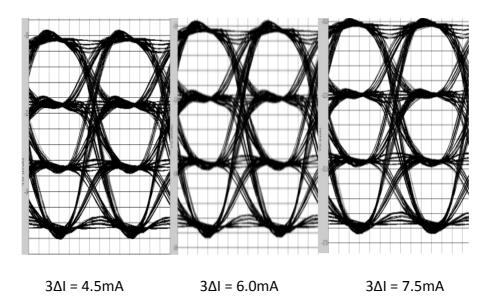

| Fig.4.11 PAM4 VCSEL eye distorted due to different delays of MCML gates operating at 56 gbps           | 106 |

| Fig.4.12 Synchronized data after inverters are placed.                                                 | 106 |

| Fig.4.13 PAM-4 eye diagram at various temperature and corner variations                                | 107 |

| Fig.4.14 100 Monte-Carlo simulations to ensure that delays of all the MCML gates are the same a 56gbps |     |

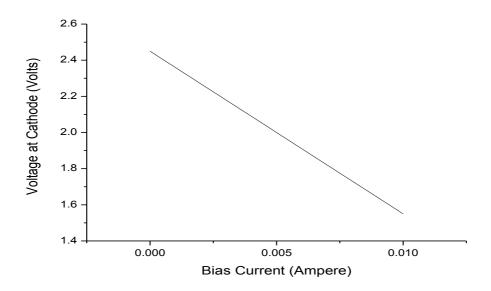

| Fig.4.15 V-I curve of the VCSEL used in the design                                                     | 109 |

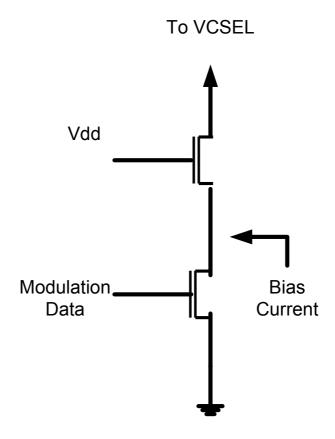

| Fig.4.16 Conceptual view of VCSEL driver                                                               | 110 |

| Fig.4.17 Differential structure for VCSEL driver                                                       | 111 |

| Fig.4.18 Simple common-source based driver from [82].                                                  | 112 |

| Fig.4.19 Binary weighted output transistor [84, 85]                                                    | 113 |

| Fig.4.20 Proposed Driver Slice.                                                                        | 113 |

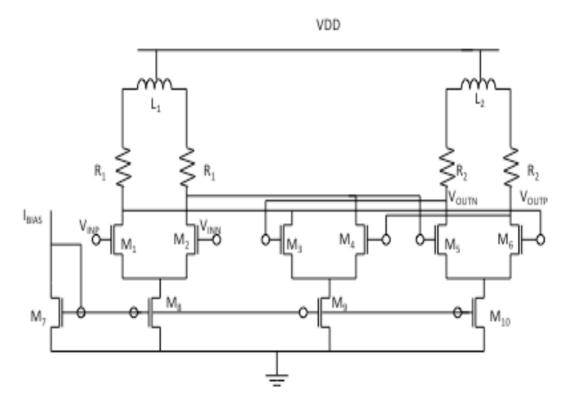

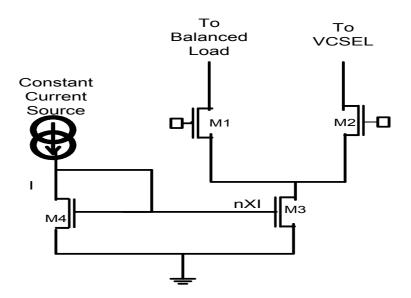

| Fig.4.21 Modulation current control in Differential VCSEL driver.                                      | 115 |

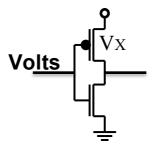

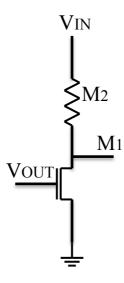

| Fig.4.22 Inverter                                                                                      | 116 |

| Fig.4.23 Small-Signal Model of Inverter                                                                | 117 |

| Fig.4.24 Simplified Small-Signal model of Inverter                                                     | 118 |

| Fig.4.25 Pulse-Width Distortion in the eye diagram of inverter                                         | 118 |

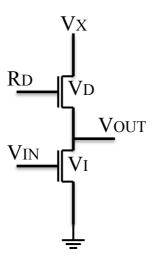

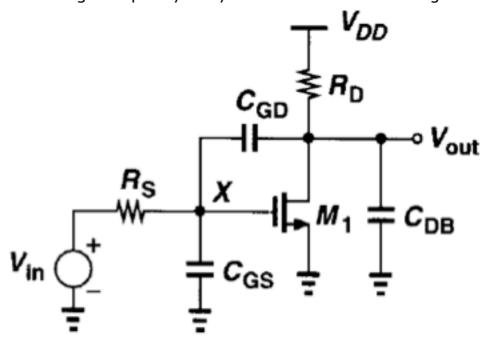

| Figure 4.26 Common Source with Resistive load                                                          | 119 |

| Fig.4.27 Common Source with NMOS transistor as a load                                                  | 120 |

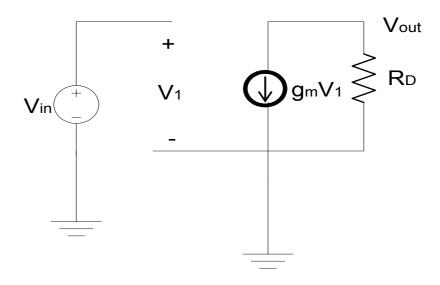

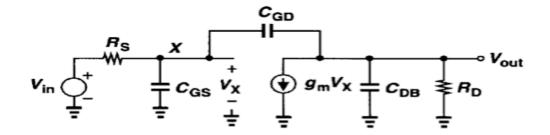

| Fig.4.28 Small Signal model of a Common Source with resistor as a load                                 | 120 |

|                                                                                                        | 120 |

| Fig.4.30 Equivalent Circuit of Common Source high frequency model                                                                                        | . 123 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

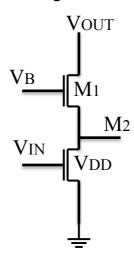

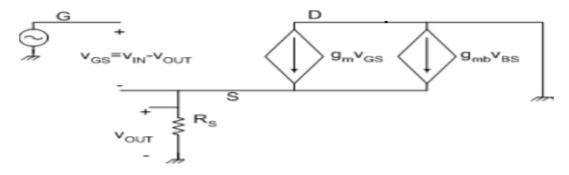

| Fig. 4.31 Source Follower with NMOS transistor as a load                                                                                                 | . 123 |

| Fig. 4.32 Small Signal Model of a source follower stage                                                                                                  | . 124 |

| Fig. 4.33 Simplified small signal model of source follower                                                                                               | . 124 |

| Fig. 4.34 High frequency model of Common Drain Stage                                                                                                     | . 125 |

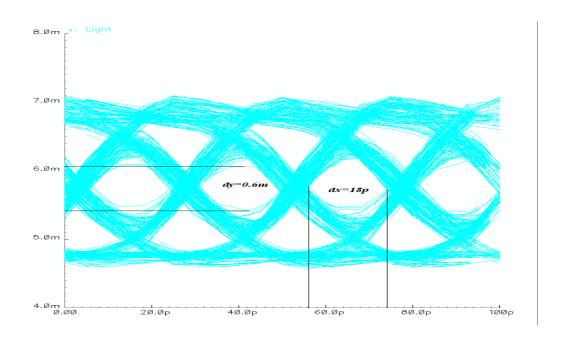

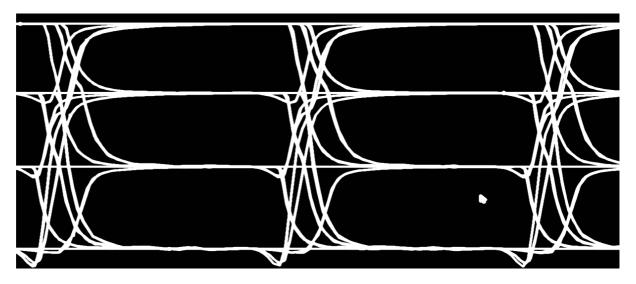

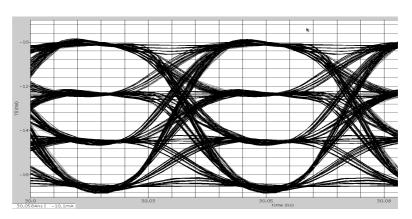

| Fig. 4.35 Eye diagram of the VCSEL current at 56Gb/s (28Gbaud)                                                                                           | . 126 |

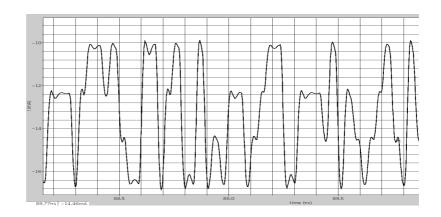

| Fig. 4.36 Time trace the of VCSEL current at 56Gb/s (28Gbaud)                                                                                            | . 127 |

| Fig. 4.37 Eye diagram of VCSEL current @ 56Gb/s for different modulation levels                                                                          | . 127 |

| Fig.4.38 Post Layout eye diagram at 56Gb/s (28Gbaud).                                                                                                    | . 128 |

| Fig. 4.39 Mask Layout of PAM4-VCSEL driver                                                                                                               | . 128 |

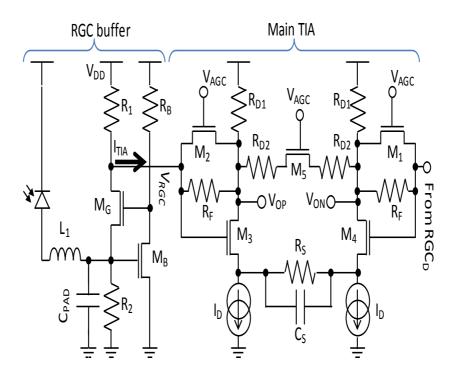

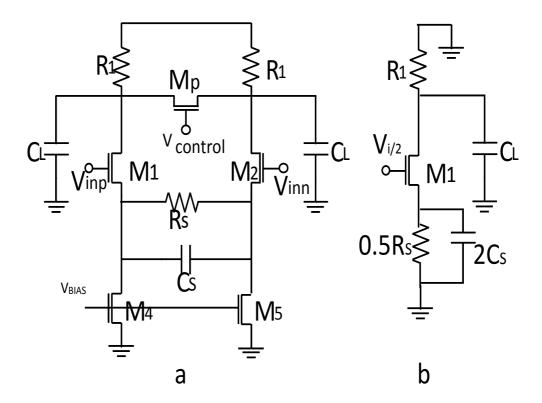

| Fig.5.1 Top-level diagram of the linear optical receiver                                                                                                 | . 133 |

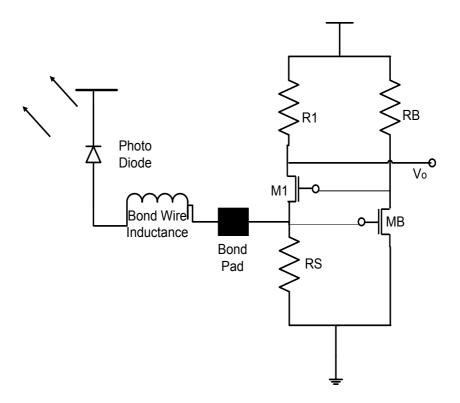

| Fig.5.2 Regulated gate cascode TIA.                                                                                                                      | . 135 |

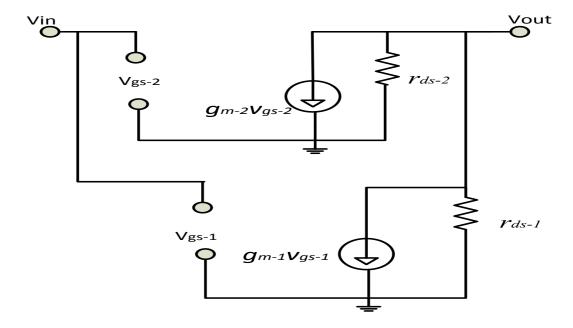

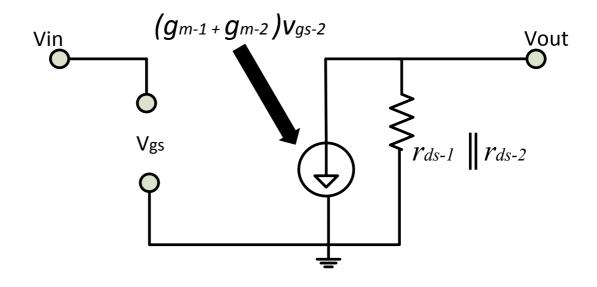

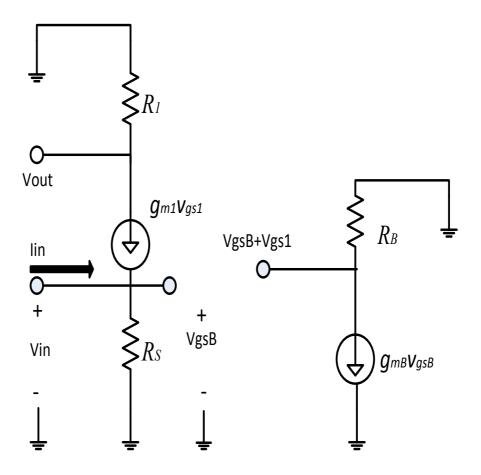

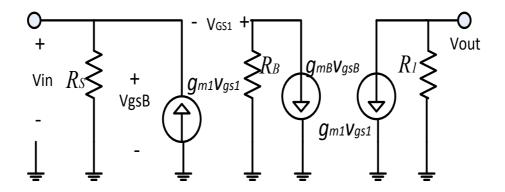

| Fig. 5.3 RGC input stage of the transimpedance amplifier.                                                                                                | . 137 |

| Fig. 5.4 Small signal Diagram of RGC input stage.                                                                                                        | . 138 |

| Fig. 5.5 Redrawn structure of Fig. 5.4                                                                                                                   | . 139 |

| Fig. 5.6 Replacing the current source with an equivalent resistor                                                                                        | . 140 |

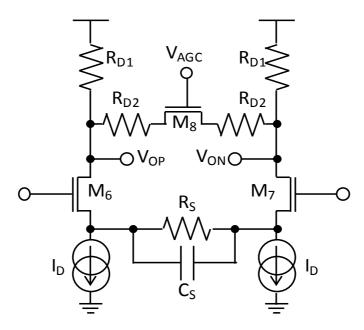

| Fig.5.7 Variable Gain Amplifier                                                                                                                          | . 141 |

| Fig. 5.8 (a) Wide band Amplifier (b) Half circuit of Wide band amplifer                                                                                  | . 142 |

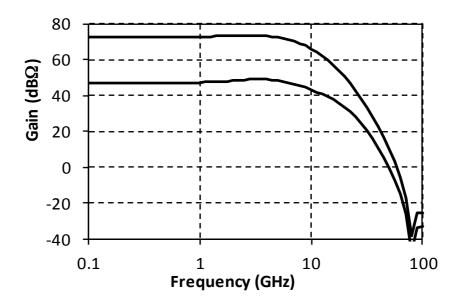

| Fig. 5.9 Frequency transfer curves for lowest and highest gain.                                                                                          | . 143 |

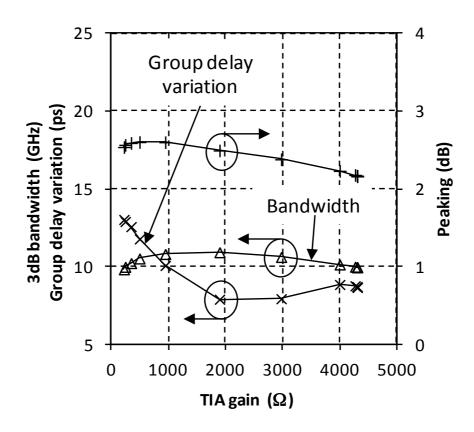

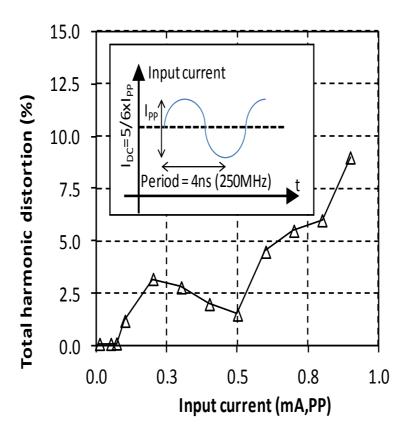

| Fig.5.10 Bandwidth (GHz), peaking (dB) and group delay variation (ps) vs. optical receiver gain (                                                        |       |

| Fig.5.11 Total harmonic distortion versus input current amplitude                                                                                        |       |

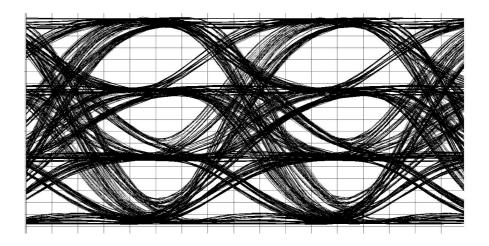

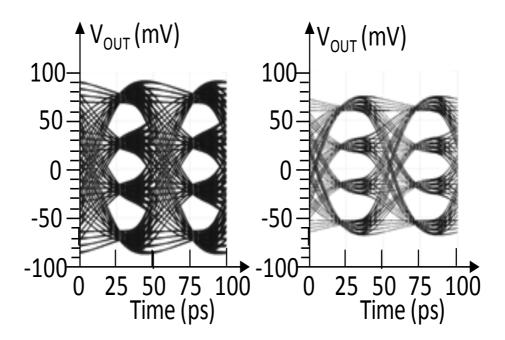

| Fig.5.12 PAM-4 eye diagrams at 20Gbaud (40Gb/s): 20μA <sub>PP</sub> (left), 500μA <sub>PP</sub> (right)                                                  | . 146 |

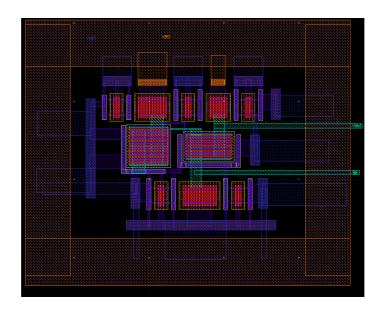

| Fig.5.13 Layout of Transimpedance Amplifier                                                                                                              | . 146 |

| Fig.5.14 Layout of Variable Gain Amplifier                                                                                                               | . 147 |

| Fig. 6.1 FTTh Access Network                                                                                                                             | . 149 |

| Fig. 6.2 input signal of a BMRx consisting of bursts                                                                                                     | . 150 |

| Fig. 6.3 Receiver classification.                                                                                                                        | . 152 |

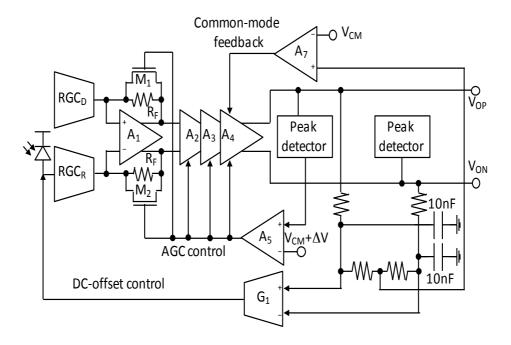

| Fig. 6.4 Block Diagram of LBMRx                                                                                                                          | . 152 |

| Fig. 6.5 Circuit Diagram of Auxiliary TIA                                                                                                                | . 155 |

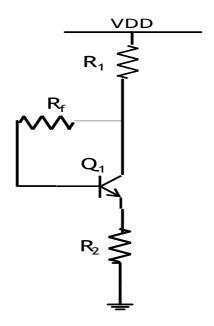

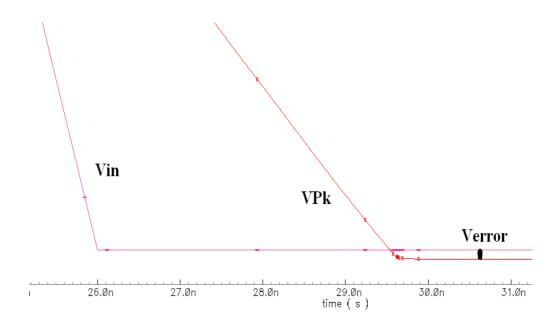

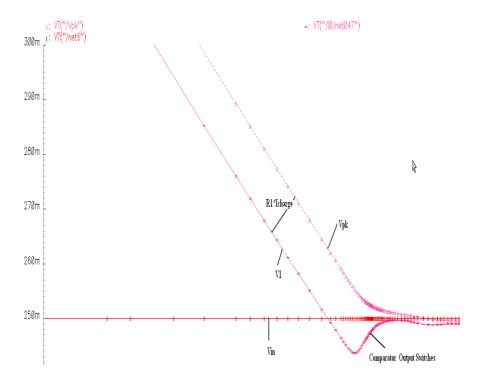

| Fig. 6.6 Peak Detector                                                                                                                                   | . 157 |

| Fig. 6.7 Output of Peak detector having small offset error due to delay of comparator (pink trace peak detector input, red trace: peak detector output). |       |

| Fig. 6.8 Use of R1 to reduce the error                                                                                                                   | . 159 |

| Fig. 6.9 Peak Detector Output                                                                                                                            | . 160 |

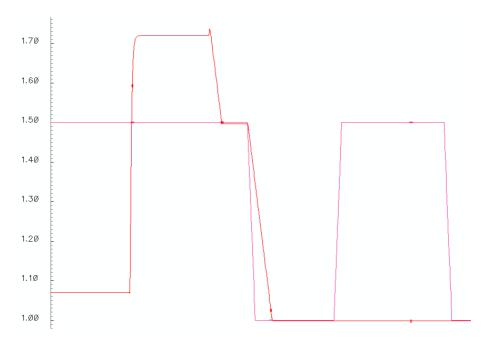

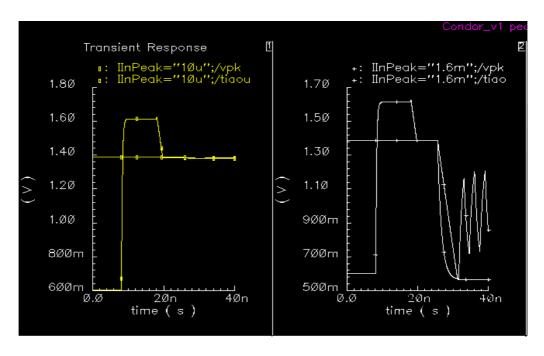

| Fig.6.10 PKD output @minimum input current (10uA) and at maximum input current (1.6                                                                                                                                                                    | 5mA) 160    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

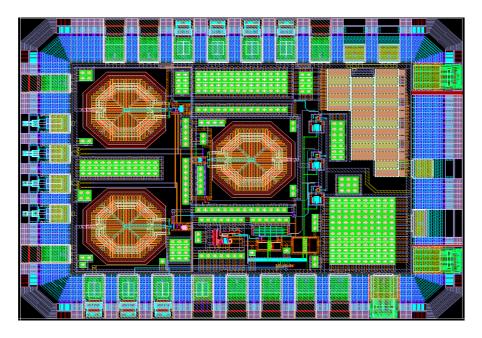

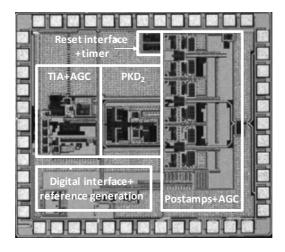

| Fig.6.11 Die micrograph (2.4 x 2.1mm²)                                                                                                                                                                                                                 | 161         |

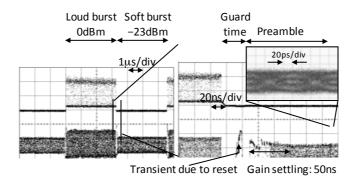

| Fig.6.12 Input (upper traces) and output (lower traces) of the LBMRx + eye diagram after (inset)                                                                                                                                                       | -           |

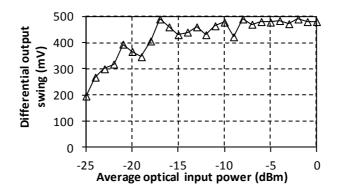

| Fig.6.13 Output amplitude vs. average optical input power (dBm)                                                                                                                                                                                        | 162         |

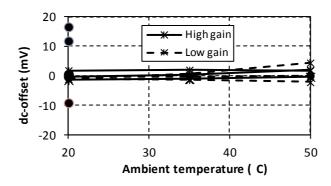

| Fig.6.14. dc-offset (difference between both the output phases of the post-amplifiers for differential input signal at the output of the post-amplifiers A <sub>3P</sub> ,A <sub>3N</sub> ) vs. temperatur 20°C are the dc-offsets before calibration) | re (dots at |

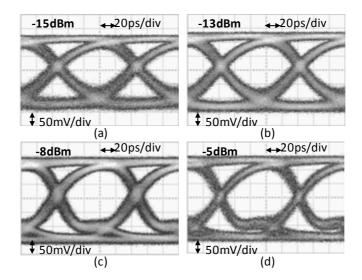

| Fig.6.15 Output eye diagrams for various input powers                                                                                                                                                                                                  | 163         |

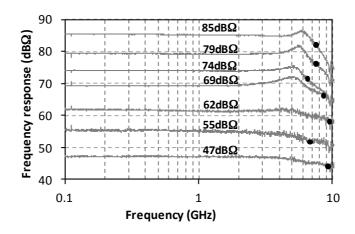

| Fig.6.16 Opto-electronic response at various gain settings                                                                                                                                                                                             | 164         |

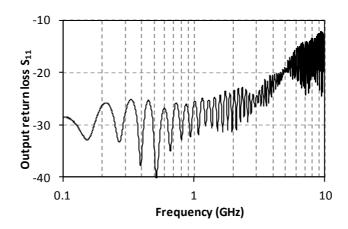

| Fig.6.17 Output return loss                                                                                                                                                                                                                            | 165         |

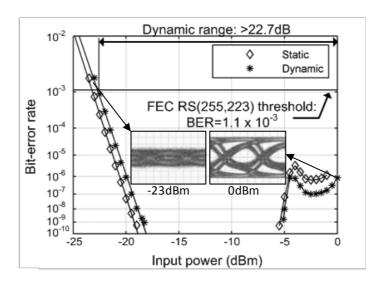

| Fig.6.18 Bit-error rate vs. optical input power (insets: eye diagrams, horizontal scale: 20; vertical: 50mV/div)                                                                                                                                       |             |

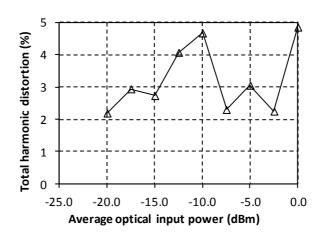

| Fig.6.19 Total harmonic distortion vs. optical input power                                                                                                                                                                                             | 166         |

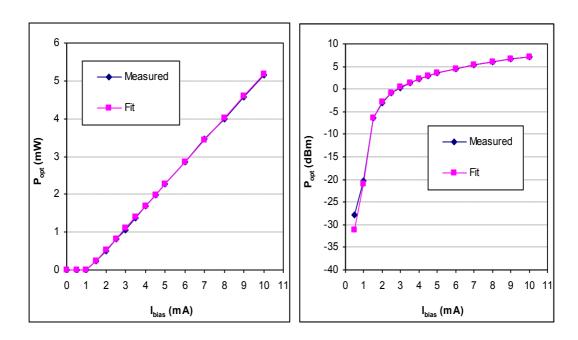

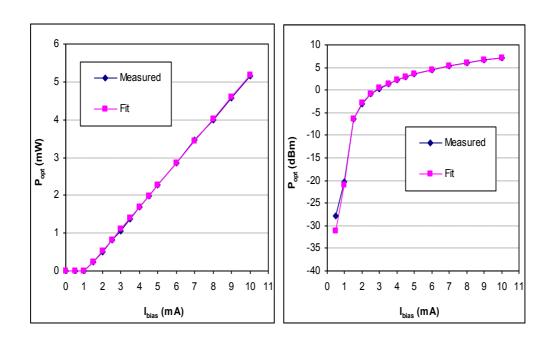

| Fig.0.1 Measured and fitted (L,I) curves.                                                                                                                                                                                                              | 183         |

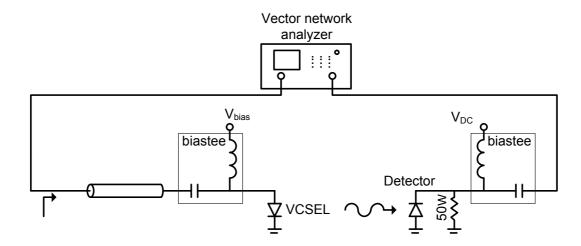

| Fig. 0.2 Measurement setup for measuring the VCSEL frequency response                                                                                                                                                                                  | 185         |

# 1

# INTRODUCTION

The world that we live in today has an endless demand for huge amounts of information travelling to and fro at a rapid rate. For this transmission, optical fibre networks have been and are being deployed world-wide ranging from long-haul networks (connecting continents and countries) over metro networks (linking cities), and now even down to access networks (connecting individual users using optical fibre technology)[1]. Until recently, fibre-optic communication was reserved for long-reach, high-capacity links between cities (metro networks), countries and continents (long-haul and submarine). Such high-end systems require transmitters and receivers where the ultimate performance in terms of capacity is of overriding importance. As this infrastructure is shared amongst millions of users, the cost of the required transponders is of secondary importance. Furthermore, volumes are relatively low, especially when compared to consumer products.

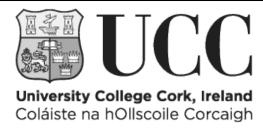

However, for some years now we are witnessing fibre-optic communication is moving into high-volume, consumer-oriented applications as shown in Fig. 1.1 [2] (short-reach interconnect such as the Thunderbolt link developed by Intel and Apple [3], or interconnect for local-area networks (LANs) and Fibre-to-the-Home applications), as well as high-end applications but requiring very high volumes of fibre-optic transceivers (short-reach interconnect for data centres and supercomputers, requiring millions of units). Traditionally, all these applications used copper-based interconnection technology. However, physical limitations (bandwidth and crosstalk in twisted pair cabling, bandwidth and physical space in coaxial based cabling) [4, 5] are increasingly pushing system integrators and operators towards fibre-optics as an alternative.

Fig.1.1 Photonics is getting closer to the processor and memory.

### 1.1 MOTIVATION

Today, data centres which support e.g. cloud computing, search engines, etc. make massive use of short-reach optical links to connect their servers together. State-of-the-art transceivers for these applications achieve up to 100Gb/s by multiplexing 10x 10Gb/s or 4x 25Gb/s channels [6]. Over the next few years, data centre operators have expressed a need for optical links which can support 400Gb/s up to 1Tb/s. Such transceivers should occupy the same physical footprint and have similar power consumption as today's 100Gb/s transceivers. Short-reach optical links for these applications are typically based on a directly modulated, short-wavelength (e.g. 850nm) vertical cavity surface emitting laser (VCSEL) and multimode fibres. Straightforward scaling of the currently used space or wavelength division multiplexing may be difficult to achieve: indeed a 1 Tb/s transceiver would require

integration of 40 VCSELs (vertical cavity surface emitting laser diode, widely used for short-reach optical interconnect), 40 photodiodes and the electronics operating at 25 Gb/s in the same module as today's 100 Gb/s transceiver.

This research is based upon developing high speed electronics with lower power consumption, small footprint and better performance. This research is also focussed in developing receiver and transmitter electronics for more advanced modulation formats such PAM-4 (4-level pulse amplitude modulation) as one runs into several physical limitations that will make further increase of the serial link speed using simple non-return to zero modulation difficult:

- The need for higher bandwidth VCSELs: higher modulation bandwidths can

be achieved by making the active region of the VCSEL smaller (smaller

diameter). However to maintain the same output power, this implies the

current density increases, which has a detrimental effect on the reliability of

the device. While 40GHz VCSEL devices have been demonstrated, their

reliability is still a matter of research. Further scaling beyond 40GHz will

prove even more challenging.

- Dispersion (modal in multi-mode or chromatic in single-mode) in the fibres: the bandwidth x distance product scales inversely proportional to the square of the bit rate.

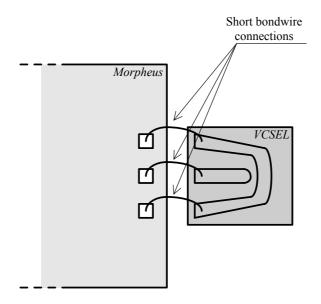

- Packaging: scaling to very high bandwidths (>40GHz) requires exotic and expensive packaging technology (e.g. ceramic substrates) with high mechanical precision which is expensive and not compatible with high volume production.

#### 1.2 SHORT REACH OPTICAL INTERCONNECT APPLICATIONS

### 1.2.1 LAN (LOCAL AREA NETWORKS) AND SAN (STORAGE AREA NETWORKS)

In local area networks (LAN) and storage area networks (SAN) (which connect computers, servers and storage devices together inside e.g. company sites) copper had the competitive edge from a lower cost perspective, however the increase of data rates, largely driven by consumer internet video, digital television and

enterprise backup applications, are pushing the industry to deploy optical interconnect within their own LAN and SAN infrastructure [6] as can be seen in fig. 1.2 [7].

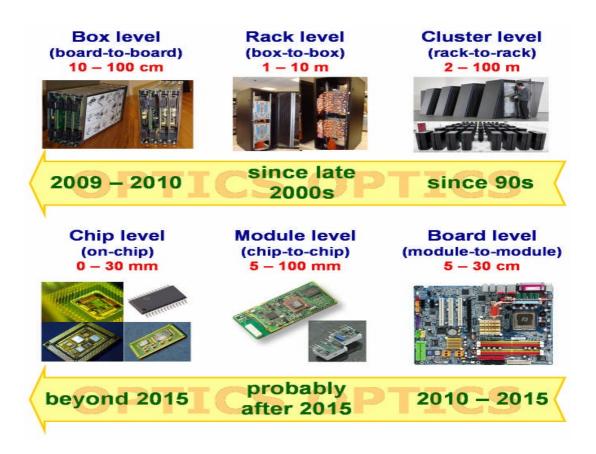

Fig.1.2 Optical interconnects in the LAN and SAN networking arena.

### 1.2.2 DATA CENTRES

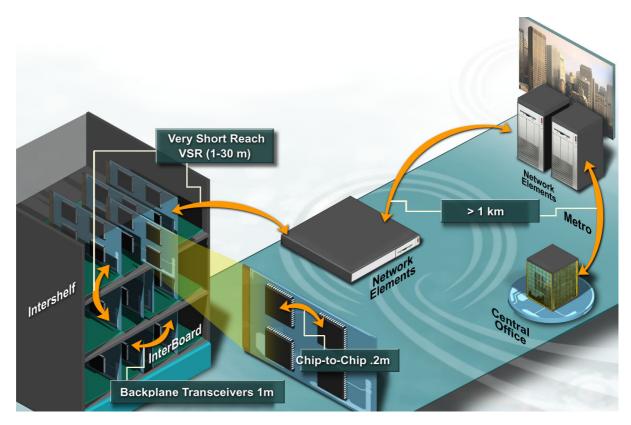

In the last few years, we've witnessed the rapid emergence of huge data centres, also sometimes called 'warehouse scale computers'. These data centres underpin applications such as cloud computing, internet search engines, video-on-demand, social media etc. A diagram of a typical data centre shown in Fig. 1.3: such a data centre consists of thousands (some rumoured to contain hundreds of thousands of servers) of servers, arranged in racks, connected together with high-speed switches. Today, data centres face continuous pressure to expand their capacity to handle

more data from a growing user group, new data-intensive applications and bandwidth hungry applications. Already, today's data centres make massive use optical links.

Fig.1.3 A typical data centre network.

The most challenging issue in the design and deployment of a data centre is its power consumption. However as data rates and number of lanes per I/O (Input/Output) port increase, the size of electrical connectors and the power dissipation in copper traces is difficult to keep in control[8]. To meet the demands of high throughput, reduced latency and low power consumption optical networks are now being used in such systems [9, 10].

#### 1.2.3 HIGH PERFORMANCE COMPUTING

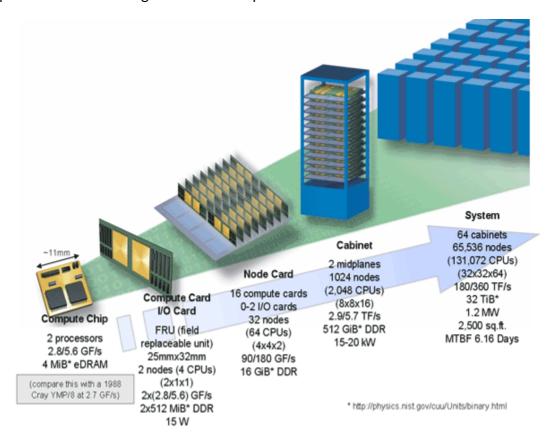

In a simplified view, a high performance computer consists of racks of servers, all tightly interconnected together. As shown conceptually on Fig. 1.4, each

such server consists of processor and memory cards; connected together using parallel busses running across the backplane.

Fig. 1.4 Conceptual view of a high-performance supercomputer (Blue Gene): the compute cards (containing the processors with memory) and IO cards are assembled into "node cards" which are basically backplanes.

To overcome limitations in the number of IO (Input Output) pins per chip, the interconnect between processor and memory cards is implemented using serial links and SerDes (Serializer/Deserializer) chips, which serialize the data prior to sending it across the backplane. In high-end servers which contain several processor and memory cards per backplane, such a backplane can easily have an area of ~1m². With ever increasing IO bandwidths between the processing units and the memory banks, this server technology faces two significant bottlenecks for

further upscaling (which requires more IO pins per processor and memory chip, increasing bus widths and higher throughput per individual bus link):

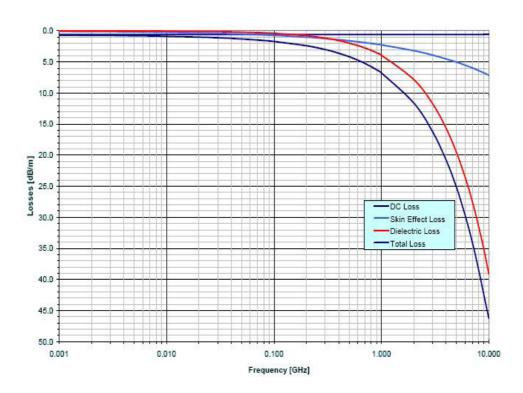

1) Conventionally, backplanes are manufactured using FR4 (flame retardant – 4) material (a glass reinforced epoxy composite material widely used for fabricating printed circuit boards), onto which copper traces are etched. While this manufacturing process is very well established, unfortunately it is not very well suited for high-speed data transfer. Indeed for example, Fig. 1.5 shows the insertion loss of a 1 meter long (impedance matched) trace on an FR4 board: an insertion loss of 25 dB at 5 GHz can be observed.

Fig. 1.5 Insertion loss (dB/m) of a 100  $\Omega$ matched differential transmission line versus frequency (Avago application note AN5362).

Using sophisticated equalization techniques, these losses can be overcome and transmission speeds up to 25 Gb/s have been demonstrated across such links. However, how to scale up beyond 25 Gb/s is currently an open question. Signal integrity across backplanes is further compromised by

- crosstalk and electromagnetic interference, all of which become worse with increasing bandwidths.

- 2) The amount of IO pins that can be placed around the core circuitry of eg. multicore processors and memory chips. The ever increasing integration density (set to continue for at least another decade despite numerous claims that Moore's law has ended) allows to place more and more transistors on a given chip area, thus increasing its functionality. This requires higher IO bandwidths to and from the processor and memory chips. However, the size of IO pins does not scale accordingly. 3D integration is set to become the answer to this, however even then connections with ever increasing bandwidth will be required.

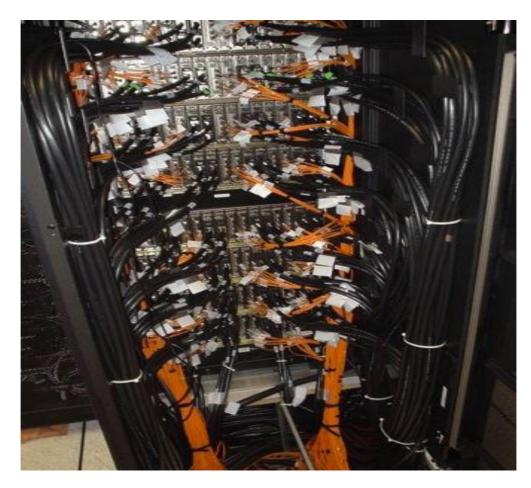

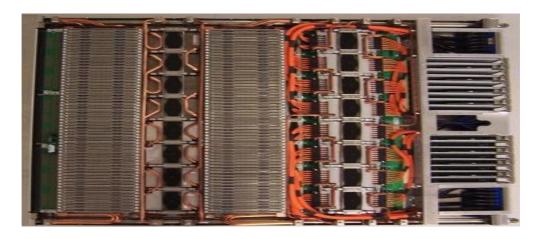

One option to overcome these problems is an optical bus: this can solve the problem of cross-talk and signal loss[11]. Such an optical bus consists of serializers/deserizalizers, O/E (Optical/Electrical) and E/O (Electrical/Optical) converters connected together using e.g. optical waveguides in a PCB (Printed Circuit Board). Fig. 1.6 shows a combination of electrical and optical cabling in IBM (International Business Machines) supercomputers and in Fig. 1.7 optical to optical connection is shown[12].

Fig.1.6 Electrical and optical cabling in supercomputers

Fig.1.7 Optical to Optical communication between chips externally

#### 1.2.4 CONSUMER APPLICATIONS

In modern homes increasing number of consumer electronic devices for communication and entertainment needs need to be interconnected and connected to the outside content providers, thus requiring the home networking solutions to have higher bandwidths as shown in Fig. 1.8[13].

Fig.1.8 Data rate evolutions of various protocols commonly used in "backbone" homenetworks (closed symbols) and for device-to-device direct communication (open symbols).

For example, if a conventional USB link is used to transfer high definition files, a complete transfer requires 6-8minutes assuming a Blu Ray file of 30 GByte and an USB 2.0 link having a throughput of 480 Mb/s. Transferring such a file in a matter of seconds will require short-reach links with multi-Gb/s capacity. As with other applications mentioned above the classical copper based interconnect is again losing out here due to its high-power consumption (due to the use of extensive signal processing to counter the cable attenuation at high frequencies), and greater EMI (electro-magnetic interference) issues. Low-cost fibres (such as Plastic Optical

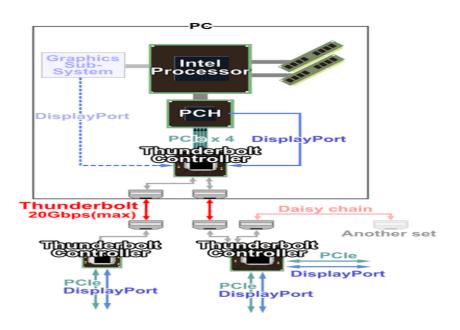

Fibre) and VCSEL's (Vertical Cavity self Emitting Lasers) can give optical links an edge in terms of cost and performance benefits [14]. The importance of POF is not just that it is easy to handle (e.g. a sharp knife is sufficient to cut it to length) and is cheap, but also that its large core significantly relaxes the tolerance on mechanical alignment of the transceiver optics. This is usually a significant fraction of the overall transceiver production cost. An example of such technology is shown in Fig. 1.9: this link is known as Thunderbolt link which offers the customers to connect their devices to PC's and transfer the data at speeds up to 10 Gbps[3].

Fig.1.9 Thunderbolt technology by Intel

As discussed above optical links are replacing electrical links in local-area networks, and may now also become the prime choice for even shorter links in consumer applications. As usual, the optical transceiver design needs to consider three major criteria: low power consumption, low cost and small size, in order to allow the integration of parallel optical interconnects. With the advent of VCSEL's [15](Vertical cavity surface emitting lasers) having lower threshold current and higher bandwidth, it provides an attractive solution in such design dominated by power, cost and size. The challenge in these links is to maximize the data rate per pin as the number of pins will remain constant across future technologies [16].

CMOS (Complementary Metal Oxide Semiconductor) front end-circuitry becomes then an interesting choice as it provides the highest possible level of integration [17]. Low-cost can be achieved once high sales volumes are realized.

### 1.3 OVERVIEW STATE-OF-THE-ART ELECTRONICS FOR SHORT-REACH OPTICAL INTERCONNECT

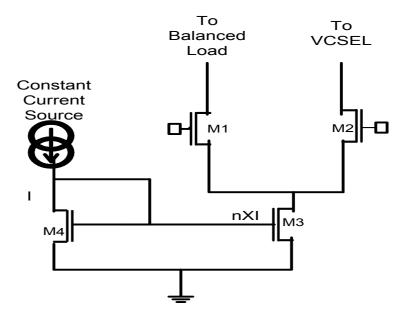

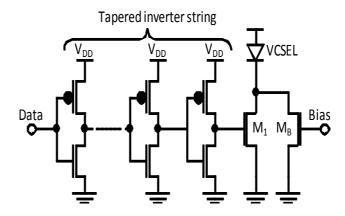

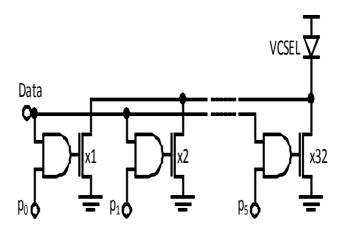

VCSEL driver circuitry operating up to 10 Gb/s (non-return to zero) have been demonstrated in [18-21]. In [18-20], these drivers were part of 1-dimensional arrays for parallel interconnects. In [21], a 2D driver was demonstrated with a total throughput of 250 Gb/s (48 x 5.21 Gb/s) More recently, VCSEL drivers operating up to 25 Gb/s and 40 Gb/s have been described [22] by VI Systems, without disclosing performance details however. In [23] and [24], 18 Gb/s and 20 Gb/s VCSEL drivers were reported respectively. High single channel bandwidth is achieved by implementing various emphasis techniques which overcomes bandwidth limitations due the parasitic capacitance (of both IO cell and VCSEL itself) and non-linear response of VCSEL by introducing some pre-distortion in the output driver waveform. Scaling beyond 20 Gb/s using CMOS technology is difficult without peaking inductors. Additionally, VCSELs face severe reliability issues when scaling beyond 10 Gb/s due to high current density (which becomes higher for increased speed, as increased VCSEL bandwidth is achieved by pushing the same VCSEL current through a smaller cross-section). The use of inductors increases the chip size, thus making it undesirable for optical interconnects as a small size is a critical requirement for optical interconnects. Clearly, pushing bit-rates beyond 25 Gb/s as standard bodies are now doing [25, 26] is challenging. An alternative solution is then Pulse Amplitude Modulation (PAM) in which the information is encoded in the amplitude of a series of signal pulses decreasing the constraints on the bandwidth of the single channel and increasing the spectral efficiency. A PAM-4 VCSEL driver is reported in [27] operating at 10 Gb/s; at 32 Gb/s in [28] and a 25 Gb/s PAM4 transmitter in [29].

Chapter 3 of this work describe in detail the design of a single channel 40 Gbps VCSEL driver using rising and falling edge emphasis and chapter 4 describes a PAM4 VCSEL driver operating at 56 Gbps achieved by using MCML gates and low power

techniques for the driver stage. Both the drivers are designed using 65 nm pure CMOS technology.

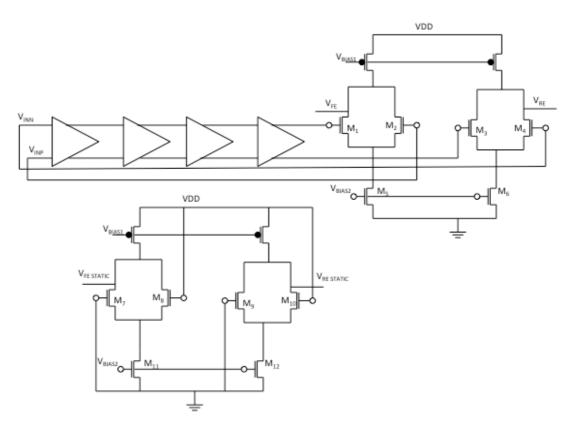

Very high speed receivers are also reported in [30-33] using various SiGe (Silicon Germanium) and sub micron CMOS technologies operating at 40 gbps and a four channel 25 gbps receiver is reported in [34] for NRZ modulation. All the receivers reported above are limiting in nature which works fine for NRZ modulation but they do not provide equal gain to all the levels of signals if the modulation is multilevel PAM. A receiver for multilevel PAM needs a linear response over its entire dynamic range which uses a VGA (variable gain amplifier) instead of a limiting amplifier [35]. Chapter 5 presents a 20 GHz linear receiver designed using 28 nm CMOS technology having a linear response for its entire dynamic range of 20  $\mu$ A to 500  $\mu$ A.

### 1.4 OPTICAL ACCESS AND FIBRE TO THE HOME

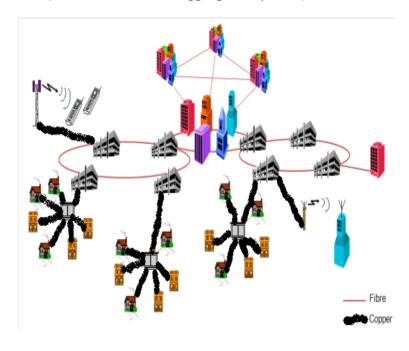

A simplified view of the present day communication network is shown in Fig. 1.10: it consists of long-haul or core networks (between countries and continents), metro networks (from exchanges to local aggregation points, linking together cities) and access networks (from home to local aggregation points).

Fig.1.10 Present day communication network

Today, copper (under the form of the twisted pair carrying both telephony and broadband internet using digital subscriber line technology (VDSL, ADSL, etc) and coaxial cable for CATV) is still the dominant technology in the access networks. However, ever increasing bandwidth demands are pushing the fibre closer "to the home": for example many operators nowadays would use technologies such as "fibre-to-the-cabinet" or "fibre-to-the-curb", in which the data to and from the DSLAMs (digital subscriber line access multiplexers) and local access points are carried using optical fibres. In the future it is anticipated that optical fibre will eventually run right into the homes of the individual subscribers. For example, in Japan the number of fibre-to-the-home users has exceeded the number of VDSL lines since [36]. This was achieved through government subsidized schemes.

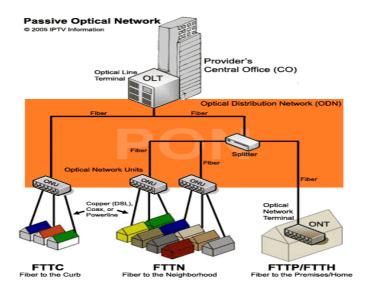

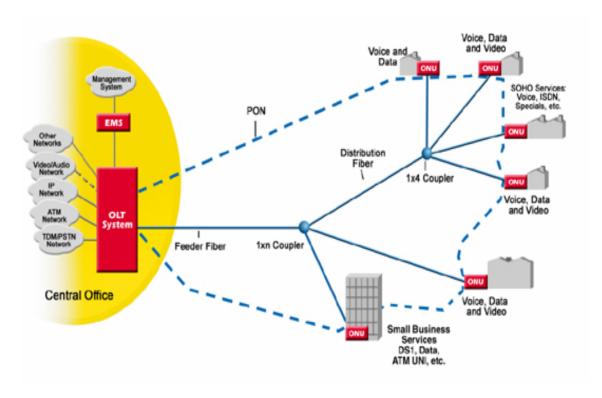

Technology in access networks needs to be low cost, especially the modems in the subscriber's house, as the cost of this infrastructure is not shared by many customers [37, 38]. Over the last five years, we have witnessed an overwhelming development of new access networks based on Fibre-to-the-home (FTTH) technology especially in the Far East (Japan, China and S. Korea) and the US. One of the means of implementing FTTH is a passive optical network (PON) which is very cost effective as it shares the cost of the fibre plant and fibre-optic transceivers over many customers and it doesn't have any active component between the central office or exchange and the customer[39, 40]. PONs have a tree like fibre plant structure which is used to connect a number of subscribers (which have optical networks units or ONU) to a central office (or optical line termination – OLT) as shown in Fig. 1.11. Note that by using this tree like fibre plant, N customers can be connected full duplex to a central office using N+1 transmitters (N transmitters in the ONUs and a single transmitter in the OLT) and N+1 receivers (N receivers in the ONUs and a single receiver in the OLT). This almost halves the amount of required transceiver modules, this significantly reducing capital investment and cost for the subscriber. As a common transmission medium is shared between the subscribers and the central office, a multiplexing scheme is required to send data downstream (from the OLT to the ONUs) as well as upstream (from the ONUs to the OLT). In the downstream direction, time division multiplexing can be used. In the upstream direction, an access protocol is required to avoid interference of data between different subscribers. Time division multiple access (TDMA) is widely used in PONs as it provides very low cost. In such systems exclusive, non-overlapping time slots are allocated to each subscriber in which their data can be transferred in upstream direction.

Fig.1.11A typical PON system

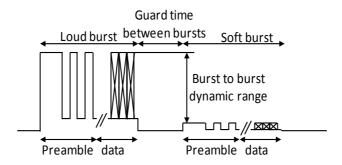

This means that the central office receiver and the subscriber transmitter need to operate in burst mode where they are switched on only during their designated time slot. The receiver in the central office needs to be a burst-mode receiver (BMRx). The BMRx in such a system is a very critical component as its sensitivity (optical power that is required for a given bit-error-rate) and dynamic range determine the reach and split (amount of subscribers connected to central office) of the system. The burst-mode receiver needs to be able to handle a signal which consists of a quick sequence of bursts. These bursts exhibit a wide dynamic range from burst to burst due to two main reasons. One is the distance between the subscribers and the central office may vary resulting in different attenuation in the fibre path and second is the launched power from the subscriber's transmitter may vary as well. Which makes the requirement of the receiver very stringent as it need to be able to quickly change its gain and decision threshold (distinction between 1 and 0 transmitted) from one burst to the next. As no data is received when the BMRx is changing its gain settings, which could lower the traffic efficiency, the quick

adjustment (within a few tens of nanoseconds to hundreds of nanoseconds) is very vital for the operation of the whole system.

Chapter 6 presents the details of the designed burst mode receiver which is to be used for the application explained above.

# COMPONENTS OF SHORT REACH OPTICAL INTERCONNECT

This chapter provides a brief theoretical background of components that are used in the short reach optical interconnects which includes the types of fibre used, explanation of various types of light sources (lasers and photo-diodes), their properties detailing their advantages and disadvantages. It briefly touches the electronics that is used in designing such type of transceivers and also outlines the challenges faced in such designs.

#### 2.1 OPTICAL LINK

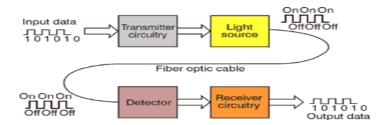

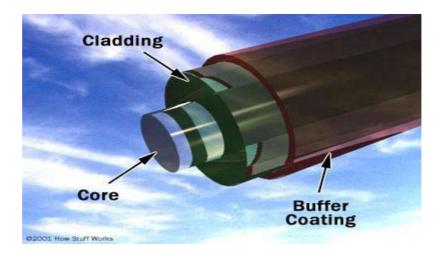

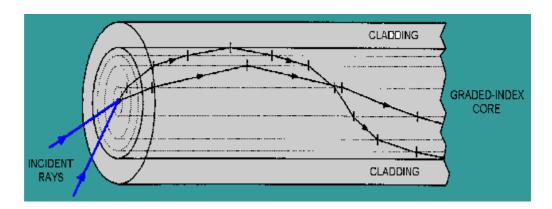

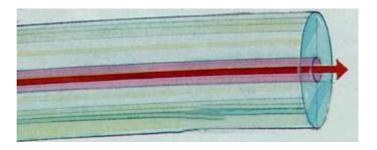

An optical link is a part of an optical fibre based communication network which transmits and receives data between two points. It is essentially made up of a transmitter which converts electrical current pulses into light pulses (usually generated by a laser diode) where it is converted into light and transmitted to the receiver through fibre. At the receiver it is detected by a detector (PIN or APD diode) converting it back into current from light which is then further processed by the receiver circuitry as shown in Fig 2.1.

Fig.2.1 A basic Fibre optic communication system (non-return to zero modulation).

The advantages [41] of using optical links for communication for long distances (several kilometres up to thousands of kilometres) as well as smaller distances are listed below

- 1. Enormous bandwidth: large amounts of data can be transferred through an optical fibre compared to e.g. wireless or copper-based cables [42].

- 2. Small size and weight: Optical fibres are small in size and are lighter than corresponding copper cables [43].

- 3. Electrical isolation: Optical fibres are fabricated from glass or sometimes a plastic polymer and the light signals are guided inside a core, hence signals travelling in separate fibre are electrically insulated which makes them ideal for communication in hazardous environment [44, 45].

- 4. Signal Security: lack of significant radiation makes an optical link ideally suited for military, banking and general data transmission by providing a high degree of signal security[46].

- 5. Low transmission loss: Optical cables which are fabricated now a days have very low attenuation or transmission loss in comparison to copper: this characteristic of optical fibre is indeed the fundamental reason for its wide deployment

Optical fibre based communication of course also have some disadvantages, which even today make application of optical fibre links in e.g. mass-market consumer applications quite challenging:

- 1. Highly specialized mechanical assembly techniques (splicing, fibre welding with submicron accuracy): (single-mode) optical fibres have a very small core (8 µm diameter) which requires very tight tolerances when aligning these with active optical components such as lasers or modulators. Mechanical assembly still requires substantial manual effort. This is to be contrasted with the highly established (solder-based and pick-and-place) technologies required for assembling electrical links. It means that optical links can be quite expensive.

- 2. Complex fabrication and material systems: manufacturing of lasers, modulators, photo-detectors require complex material systems (e.g. III-V materials) and sophisticated fabrication flows, unlike electronics where e.g. integration in monolithic Silicon chips has been hugely successful. The result is relatively low yields, requiring manual cherry picking of devices, with obvious impact on cost.

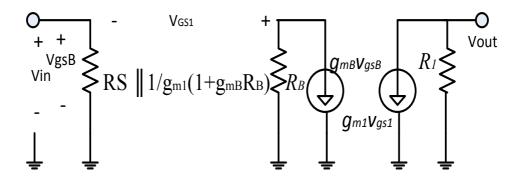

#### 2.1.1 OPTICAL FIBRE