| Title                          | Architectures for maximum-sequence-length digital delta-sigma modulators                                                                                                                                                                                                                                                                                       |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Authors                        | Hosseini, Kaveh;Kennedy, Michael Peter                                                                                                                                                                                                                                                                                                                         |  |

| Publication date               | 2008-04                                                                                                                                                                                                                                                                                                                                                        |  |

| Original Citation              | Hosseini, K., Kennedy, M.P., 2008. Architectures For Maximum-<br>Sequence-Length Digital Delta-Sigma Modulators. IEEE<br>Transactions On Circuits and Systems II - Express Briefs, 55(11),<br>pp.1104-1108.                                                                                                                                                    |  |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                        |  |

| Link to publisher's<br>version | 10.1109/TCSII.2008.2004537                                                                                                                                                                                                                                                                                                                                     |  |

| Rights                         | ©2008 IEEE. Personal use of this material is permitted. However,<br>permission to reprint/republish this material for advertising<br>or promotional purposes or for creating new collective works<br>for resale or redistribution to servers or lists, or to reuse any<br>copyrighted component of this work in other works must be<br>obtained from the IEEE. |  |

| Download date                  | 2024-05-03 13:04:26                                                                                                                                                                                                                                                                                                                                            |  |

| Item downloaded<br>from        | https://hdl.handle.net/10468/134                                                                                                                                                                                                                                                                                                                               |  |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# Architectures for Maximum-Sequence-Length Digital Delta-Sigma Modulators

Kaveh Hosseini, Student Member, IEEE, and Michael Peter Kennedy, Fellow, IEEE

Abstract—In this paper, we extend the idea developed in some of our earlier works of using output feedback to make the quantization step in a digital delta-sigma modulator (DDSM) appear prime. This maximizes the cycle lengths for constant inputs, spreading the quantization error over the maximum number of frequency terms, and consequently, minimizing the power per tone. We show how this concept can be applied to multibit higher order error-feedback modulators (EFMs). In addition, we show that the idea can be implemented in a class of single-quantizer DDSMs (SQ-DDSM) where STF  $(z) = z^{-L}$  and NTF  $(z) = (1 - z^{-1})^{L}$ .

*Index Terms*—Digital delta-sigma modulator (DDSM), error-feedback modulator (EFM), maximum sequence length, multibit quantizer, noise shaping, quantization noise, single-quantizer DDSM (SQ-DDSM).

# I. INTRODUCTION

**Q** UANTIZATION noise shaping is widely used in the fields of data converter [3], [4] and fractional-N frequency synthesizer design [5]–[9]. Digital delta-sigma modulators (DDSMs) are a class of noise shaping modulators that process discrete-amplitude discrete-time signals. The DDSM is a discrete-time deterministic dynamical system with a digital input and a digital output. It includes one or more quantizers, depending on its architecture. It represents an  $n_0$ -bit narrowband digital input signal as a wider band m-bit digital output signal. Generally, m is significantly less than  $n_0$ , resulting in a quantization error that is commonly modeled by additive white noise. The spectrum of the quantization noise is filtered (shaped) by the modulator such that its power is concentrated toward high frequencies, leaving relatively little quantization noise power in the signal band.

For many important applications, such as unmodulated fractional-*N* frequency synthesizers, the DDSM input is a constant digital word. For simplicity, in this paper, we consider DDSMs only with constant inputs.

A ditherless DDSM is a deterministic finite-state machine with a unique rule for transitioning from each state to the next. If the input is constant, the most complex behavior the DDSM can exhibit is a trajectory that visits each state once before repeating. In fact, the solution will always be constant or periodic: in particular, a DDSM with a constant input produces a periodic quantization noise signal (a cycle). In some cases, the period of

Manuscript received February 03, 2008; revised May 16, 2008. Current version published December 10, 2008. This work was supported in part by the Science Foundation Ireland under Grant 02/IN.1/I45. This paper was recommended by Associate Editor P. Malcovati.

The authors are with the Department of Microelectronic Engineering and Tyndall National Institute, University College Cork, Cork, Ireland (e-mail: kaveh.hosseini@ue.ucc.ie).

Digital Object Identifier 10.1109/TCSII.2008.2004537

this signal is short, resulting in a small number of large (spurious) tones in the output spectrum.

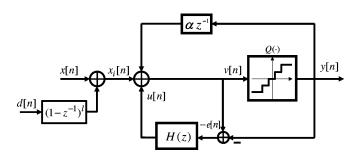

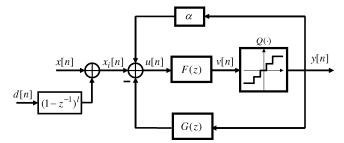

Fig. 1. Generic block diagram of a higher order EFM with a multilevel quan-

tizer, shaped additive input LSB dither, and a novel output feedback path  $\alpha z^{-1}$

that deterministically maximizes the number of spectral tones.

By maximizing the period (cycle length) of the error signal, the number of tones in the spectrum can be maximized, causing the quantization power per tone to be minimized.

There are two classes of techniques to maximize the sequence length: stochastic and deterministic. Stochastic techniques use a "random" signal to perturb the system, thereby disturbing short cycles. Deterministic techniques introduce changes in the underlying architecture of the modulator that inherently prevent short cycles forming.

The most popular stochastic technique to reduce the spurs is to break up the patterns in the quantization noise signal by dithering [3, Ch. 3]. The disadvantage of even the best stochastic techniques is that they inherently add noise that later shows up in the output spectrum, albeit small and shaped.

In [1] and [2], we introduced a deterministic modification to the DDSM architecture (an additional output-feedback path) that maximizes the sequence length without dither. This technique allows one to realize the ideal spur-free output spectrum predicted by assuming a modulator with additive white quantization noise.

In this paper, we show how the idea described in [1] can be extended to two classes of multibit modulators: higher order error-feedback modulators (EFMs) and single-quantizer DDSMs (SQ-DDSMs) [3], [4]. In Section II, we give the background on EFMs and review the state of the art. In Section III, simulation results are presented for maximum-sequence-length multibit EFMs, and in Section IV, simulation results are presented for maximum-sequence-length SQ-DDSMs. We discuss implementation issues briefly in Section V. The main contributions of this paper are summarized in Section VI.

#### II. BACKGROUND

The generic block diagram of a digital multibit EFM is shown in Fig. 1. The modulator contains an optional additive input

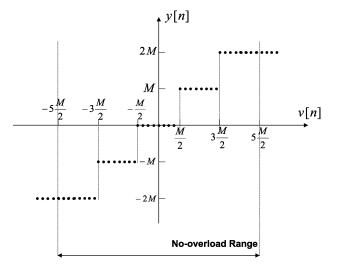

Fig. 2. Input--output characteristic of the multilevel quantizer with  $N_{\min} = 2$  and  $N_{\max} = 2$ .

dither signal d, an optional filter (denoted  $(1 - z^{-1})^l$ ) to shape the dither, and an output-feedback path (denoted  $\alpha z^{-1}$ ) that we will use to maximize the sequence length in a deterministic way. The quantizer [denoted by  $Q(\cdot)$ ] provides a coarse approximation y of the digital signal v.

Fig. 2 shows the input-output characteristic of the multilevel midtread quantizer that we consider in this paper. Each quantization step is of length M, there are  $(N_{\text{max}} + N_{\text{min}} + 1)$  output levels, and the no-overload range is defined by  $-(N_{\text{min}}M + M/2) \le v \le (N_{\text{max}}M + M/2 - 1)$ .

The difference between the quantized output y and the input v is called the quantization error, defined by e = y - v. For ease of implementation, we assume that the step size M of the quantizer is a power of two  $(M = 2^{n_0})$ . Choosing  $H(z) = 1 - (1 - z^{-1})^L$ , the signal transfer function STF  $(z) = Y(z)/X_i(z)$  and noise transfer function NTF (z) = Y(z)/E(z) become

$$STF(z) = \frac{1}{1 - \alpha z^{-1}}$$

$NTF(z) = \frac{(1 - z^{-1})^L}{1 - \alpha z^{-1}}$ . (1)

#### A. Conventional Architecture

When  $\alpha = 0$ , we obtain a conventional DDSM, where the EFM has an all-pass signal transfer function STF (z) = 1 and a high-pass noise transfer function NTF  $(z) = (1 - z^{-1})^L$  that rejects the quantization noise at low frequencies.

The quantizer error e is usually assumed to be white noise. With this assumption, its spectrum is smooth, and the noise is concentrated toward high frequencies, away from the signal band.

The digital modulator is a finite-state machine (FSM) that always produces a *periodic* output signal (a cycle) when the input is a constant. In this case, the quantization noise sequence is also periodic. In general, the period depends on the input, the initial conditions, and the architecture of the DDSM. When the period is short, the power of the sequence is distributed among a limited number of undesirable tones (so-called spurious tones) that appear in the DDSM output spectrum. The powers of the spurious tones (spurs) can be significantly higher than the noise-

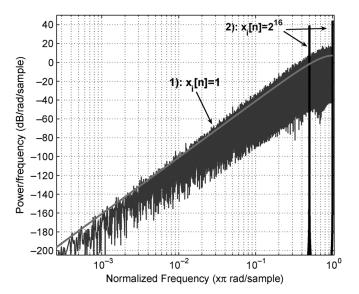

Fig. 3. Effect of short nonwhite sequences in a third-order multibit EFM ( $M = 2^{17}$ ) for two different constant inputs: 1)  $x_i[n] = 1$  and 2)  $x_i[n] = 2^{16}$ . The solid curve shows shaped white quantization noise.

shaping curve predicted by the simplifying assumption that the quantizer can be modeled as an additive white noise source.

To illustrate this problem, we refer to Fig. 3 that shows MATLAB simulation results for the EFM shown in Fig. 1 ( $\alpha = 0$  and d[n] = 0). The quantizer step size is  $M = 2^{17}$ ,  $N_{\min} = 4$ ,  $N_{\max} = 3$ , the filter is third order (L = 3), and all initial conditions are set to zero. All simulations have been performed using signed integer arithmetic.

Plot 1 shows the simulation result when the input is 1. Plot 2 shows the spectrum of the output sequence when  $x = 2^{16}$ . Note that plot 1 can be approximated by a smooth curve, shown solid, which results from assuming that the quantizer adds uniformly distributed white noise. By contrast, the spectrum shown in plot 2 contains only two high-power tones because the quantization noise is far from white. This example shows how the modulator can fail catastrophically to perform proper noise shaping, depending on the input value.

Using a stochastic approach, one can apply a pseudorandom binary dither sequence d[n] (shown in Fig. 1) to the input [10], [11]. This breaks up the cycles and increases the effective sequence length, resulting in a smoother noise-shaped spectrum. While it increases the sequence length, as required, dithering inherently adds noise to the spectrum, as we will see in Section III; care must be taken to minimize the contribution of this additional noise.

An alternative (deterministic) approach is to avoid known short sequences by setting the initial conditions of the internal registers of the EFM [12].

Another deterministic way of increasing the sequence length is to modify the architecture [1] in such a way that the sequence length inherently attains the maximum possible value. In [1], a first-order EFM that has the maximum sequence length for *all* inputs and for *all* initial conditions has been developed. In this paper, we show empirically that the same concept introduced in [1] (adding a specially chosen output-feedback path

<sup>1</sup>The dc term (corresponding to x) has been removed from the output y before plotting, yielding y'; all plots show y'/M.

TABLE I CORRESPONDING VALUES OF a WITH RESPECT TO  $n_0$  in the Range 5 to 25 Where  $M = 2^{n_0}$

| $n_0$                        | a  |

|------------------------------|----|

| 5, 7, 13, 17, 19             | 1  |

| 6, 9, 10, 12, 14, 20, 22, 24 | 3  |

| 8, 18, 25                    | 5  |

| 11, 21                       | 9  |

| 16, 23                       | 15 |

| 15                           | 19 |

| <b>N</b>                     |    |

$\alpha z^{-1}$ , as shown in Fig. 1) maximizes the sequence lengths of higher order EFMs with a multibit quantizer, thereby achieving a smooth power spectrum.

# B. HK Architecture

Consider again the EFM shown in Fig. 1. Let  $\alpha = a/M$ , where M is a power of 2  $(M = 2^{n_0})$ , and  $H(z) = z^{-1}$ . Assume that the quantizer output y produces two levels: 0 and M. This corresponds to a first-order EFM with a two-level quantizer and our additional output-feedback path.

We proved in [1] that the cycle length (and hence the number of tones in the spectrum) in this case is defined by

$$N = M - a$$

for *all* constant inputs and for *all* initial conditions, where *a* is chosen according to Table I such that M - a is the largest prime number less than M.

Qualitatively, when M is a power of two and the input takes on specific (worst case) values, the quantizer output can overflow periodically, leading to very short cycles of lengths 2, 4, 8, etc. (divisors of M) [13]. The idea of the HK output-feedback path is effectively to add an offset to the state so that when the quantizer overflows, it does not reset to zero, but to a. This makes the effective quantization step equal to M - a instead of M. If a is chosen to make M - a prime, then *every* cycle is of length M - a.

In [1], we also proved that the cycle length is  $(M-a)^L$  in the case of an *L*th-order multistage noise shaping (MASH) structure comprising first-order EFMs with two-level quantizers. In this paper, we consider higher order EFMs and SQ-DDSMs with multilevel quantizers. The operating principle is the same as in [1]: an "overflow" at the quantizer output (in this case, a level change) causes an offset to be added to the state so that the quantization interval appears to be prime.

# III. MAXIMUM-SEQUENCE-LENGTH ERROR-FEEDBACK MODULATORS

#### A. Architecture

In this section, we consider the HK concept applied to a higher order EFM with a multilevel quantizer. For stability reasons, multibit quantizers are usually used in higher order EFMs [4]. We consider the architecture shown in Fig. 1, where  $\alpha = a/M$  and  $H(z) = 1 - (1 - z^{-1})^L$  [4]. With this filter, we obtain the STF and NTF of (1). Compared to a conventional modulator ( $\alpha = 0$ ), a pole at  $z = \alpha$  is added to both the STF and the NTF. If  $\alpha$  is sufficiently small, this pole is very close to the origin in the z plane; equivalently, it is a distant pole

TABLE II COMPARISON OF MINIMUM CYCLE LENGTHS OF OUR EFM STRUCTURE AND THE CONVENTIONAL EFM [12]

| Modulator | [12]                          | This work                            |

|-----------|-------------------------------|--------------------------------------|

| Order     | presetting initial conditions | all initial conditions               |

| L         |                               | all constant digital inputs          |

| 1         | $2^{n_0}$                     | $(2^{n_0} - a)$                      |

| 2         | $2^{(n_0-1)}$                 | $(2^{n_0} - a)^2 \approx (2^{2n_0})$ |

| 3         | $2^{(n_0+1)}$                 | $(2^{n_0} - a)^3 \approx (2^{3n_0})$ |

| 4         | $2^{(n_0+1)}$                 | $(2^{n_0} - a)^4 \approx (2^{4n_0})$ |

| 5         | $2^{(n_0+2)}$                 | $(2^{n_0} - a)^5 \approx (2^{5n_0})$ |

that does not significantly affect the overall operation of the modulator [1]. Simulation shows that the effect of this pole is negligible from the stability standpoint for  $n_0 \ge 5$ .

# B. Cycle Lengths

In order to determine the cycles lengths, we have performed exhaustive brute force MATLAB simulations for  $n_0 = 3, 4, 5$ for all combinations of constant inputs and initial conditions, and for modulator orders L = 1, 2, 3. Our simulations confirm that the sequence length is  $(M - a)^L$  in all cases. Simulating the modulators for all possible combination of inputs and initial conditions for orders higher than two with  $n_0 \ge 6$  is almost impractical as the length of the sequences become very large. In this case, all initial conditions were set to zero and the modulators with  $n_0 = 6, 7$  were simulated for all constant inputs. Moreover, sample simulations were performed for L = 4, 5, and all confirmed the results in Table II.

Table II compares the results of this study with the state-of-the-art results in [12]. Note that increasing the order of the HK-EFM by 1 increases the cycle length by a factor of approximately  $2^{n_0}$  compared to a factor of no more than 4 in the conventional case.

Although we have not yet been able to prove this result mathematically, exhaustive simulations suggest that the sequence length is  $(M - a)^L$  for an *L*th-order no-overload EFM for *all* constant inputs and for *all* initial conditions, where *a* is determined from Table I. This result is consistent with the theoretical result for the *L*th-order HK-MASH structure with a constant input incorporating one-bit quantizer first-order EFMs (L = 1) [1].

# C. Spectral Investigation

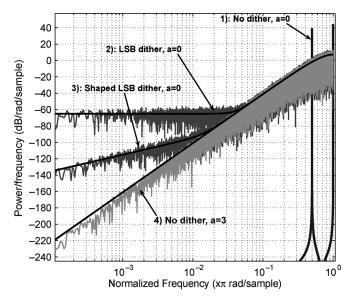

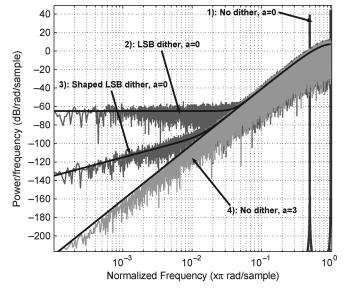

1) Ditherless: In order to illustrate the effect of the maximized sequence length, Fig. 4 shows the simulation results for a third-order modulator (L = 3) with a step size M equal to  $2^9 (n_0 = 9)$ , a constant input 256, and zero initial conditions. In this case, the modulator with nonzero normalized input 0.5 (x[n] = 256) yields a cycle of length 4. The effect of its short length is evident in the spectrum (see "1): No dither, a = 0"), which consists of just two high-power tones in the frequency range 0 to  $\pi$  (equivalently, 0 to  $f_s/2$ ). The modulator fails to perform proper quantization noise shaping because the white noise assumption is not valid.

2) With Dither: A pseudorandom binary sequence is generated and is added to the LSB of the modulator input. As shown in the figure, the dither randomizes the sequences effectively. However, it degrades the low-frequency part of the noise

Fig. 4. Spectra of a third-order multibit EFM with input decimal 256,  $M = 2^9$ . The solid curves represent the shaped white quantization noise including the dither contribution in the case of the dithered EFM.

shaping spectrum by bringing up the noise floor. This is shown in the figure (see 2): "LSB dither, a = 0").

3) With Noise-Shaped Dither: In order to combat this effect, one can pass the dither sequence through a high-pass filter such as  $(1 - z^{-1})^l$ , and then add the resulting signal to the input of the modulator. First-order shaped LSB dither (l = 1) can improve the low-frequency part of the spectrum because it randomizes the error sequences effectively (see "3): Shaped LSB dither and a = 0"). Higher order shaped dither does not guarantee a spike-free spectrum.

4) Ditherless HK-EFM: By turning off the dither and applying the feedback path  $\alpha z^{-1}$  to the system with a = 3 chosen from Table I, a smooth spike-free noise-shaping spectrum with the slope of 60 dB/decade is achieved, corresponding to the idealized prediction obtained in the literature by assuming additive white noise for the quantizer error [3]. In this case, the low-frequency part of the spectrum is not degraded and the HK-EFM outperforms the shaped LSB dithering technique.

# IV. MAXIMUM-SEQUENCE-LENGTH SINGLE-QUANTIZER DDSMs

# A. Architecture

The idea described in Section III and in [1] can be applied to another class of digital modulators with similar STF and NTF. The generic block diagram of the single-quantizer DDSM (SQ-DDSM) with our output-feedback path  $\alpha$  and with noise-shaped LSB dither is shown in Fig. 5. In this case, there is already delay in the forward path so we do not have to introduce delay in the  $\alpha$ -feedback path.

In the forward path, the block F(z) filters the signal u and delivers v to the input of the multibit quantizer. The output of the multibit quantizer y, which is an integer multiple of M, is fed back to the input summing node via filter block G(z). As in the case of the maximum-sequence-length HK-EFM, the block  $\alpha$  has been added to the modulator as a deterministic alternative

Fig. 5. Generic block diagram of SQDDSM with the feedback coefficient  $\alpha$  and with shaped LSB dither.

to dithering in order to randomize the quantizer error sequence e.

For this modulator, STF (z) and NTF (z) can be written in terms of F(z), G(z), and  $\alpha$  as follows:

$$STF(z) = \frac{F(z)}{1 + F(z)G(z) - \alpha F(z)}$$

$$NTF(z) = \frac{1}{1 + F(z)G(z) - \alpha F(z)}.$$

(2)

F(z) and G(z) are chosen such that STF has a low-pass or all-pass characteristic (passing the low-frequency input signal) and the NTF has a high-pass characteristic, rejecting the quantization noise at low frequencies. We consider in this paper a case [11] where F(z) and G(z) are of the form

$$F(z) = z^{-L}(1 - z^{-1})^{-L} \qquad G(z) = z^{L} - (z - 1)^{L} \quad (3)$$

giving

STF(z) =

$$\frac{z^{-L}}{1 - \alpha z^{-L}}$$

NTF(z) =  $\frac{(1 - z^{-1})^L}{1 - \alpha z^{-L}}$ . (4)

In the following, we demonstrate the improvement in the spectral performance of the modulator resulting from the feedback block  $\alpha$ .

# B. Simulation Results

Similar to the cases of the HK-EFM and the HK-MASH [1], extensive simulations suggest that the sequence length is  $(M - a)^L$  for an *L*th -order no-overload modulator for all constant inputs and for all initial conditions.

Fig. 6 shows the simulation results for a third-order modulator (L = 3) with the step size M equal to  $2^9$ , a constant input 256, and zero initial conditions on the internal registers.

1) Ditherless: In this case, the modulator with nonzero normalized input 0.5 (x[n] = 256) yields a cycle of length 4. This effect is clear in the spectrum (see: 1): "No dither, a = 0"). Once again, there are only two high-power tones in the frequency range 0 to  $\pi$ .

2) With White Dither: A one-bit pseudorandom dither is added to the LSB of the modulator input [11]. The low-frequency part of the spectrum is degraded due to the noise floor introduced by the dither (see 2): "LSB dither, a = 0").

3) With Noise-Shaped Dither: In order to improve the situation, the dither is passed through a filter, such as  $(1 - z^{-1})^l$ . Simulations suggest that first-order shaped LSB dither can improve the low-frequency part of the spectrum (see 3): "Shaped

Fig. 6. Spectra of a third-order multibit SQ-DDSM with input decimal 256 and  $M = 2^9$ . The solid curves represent the shaped white quantization noise including the dither contribution in the case of the dithered SQ-DDSM with higher order noise shaping.

LSB dither, a = 0"). However, higher order shaped dither again does not guarantee a spike-free spectrum.

4) Ditherless HK-SQDDSM: By turning off the dither and applying the feedback path  $\alpha$  to the system with a = 3, a smooth spike-free noise-shaping spectrum with a slope of 60 dB/decade is achieved, as predicted by the additive white noise assumption for the quantizer error. In this case, the low-frequency part of the spectrum is not degraded and it outperforms the shaped LSB dithering technique (see 4): "No dither, a = 3").

# V. IMPLEMENTATION ISSUES

When the modulator is implemented digitally, the step size of the quantizer is usually chosen, for simplicity, to be a power of two. The coefficient  $\alpha$  should be chosen such that M - a is the largest prime number less than M, where M is the step size of the quantizer and a is a small integer reported in Table I. With this selection, only a small fraction of the output signal y is fed back to the input. The effect of the coefficient  $\alpha$  on the noise and signal transfer functions is negligible for both HK-EFMs and HK-SQ-DDSMs for  $M > 2^4$ .

In terms of hardware complexity, the output y can be scaled by 1/M to significantly reduce the number of output bits; this corresponds to discarding zeroed LSBs when M is a power or 2. The additional feedback path requires a multiplication by multiples of small integers from Table I; this could be implemented by a multiplexer. An additional adder is required at the input summing node, but the number of bits is small; it is similar in complexity to that required for noise-shaped LSB dither. Overall, the

<sup>2</sup>The range of  $n_0$  given in the table can be extended beyond 25 by choosing M - a as the closest prime integer to M.

complexity of each modified structure is marginally less than the corresponding dithered conventional solution because neither the PRBS generator nor the filter is required.

The stable dynamic range in a higher order multibit modulator is determined primarily by the quantizer. Since the effect of the additional feedback path is equivalent to a minor perturbation of the quantization step, the effect on the stable dynamic range is also negligible. In other words, the stable dynamic range is approximately equivalent to that of the conventional (a = 0)modulator.

# VI. CONCLUSION

In this paper, we have extended the idea of using an additional output-feedback path to maximize the sequence lengths of DDSMs. The effect of this path is to make the effective quantization step prime. We have shown how the concept can be applied in multibit higher order EFMs. In addition, we have shown that the idea can be implemented in a special subclass of SQ-DDSMs with higher order noise shaping.

#### REFERENCES

- K. Hosseini and M. P. Kennedy, "Maximum sequence length MASH digital delta sigma modulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 12, pp. 2628–2638, Dec. 2007.

- [2] K. Hosseini and M. P. Kennedy, "A sigma-delta modulator," Irish Patent NATI82/P/IE, Oct. 4, 2006.

- [3] S. R. Norsworthy, R. Schreier, and G. C. Temes, *Delta-Sigma Data Converters: Theory, Design, and Simulaion*. New York: IEEE Press, 1997.

- [4] R. Schreier and G. C. Temes, Understanding Delta-Sigma Data Converters. Piscataway, NJ: IEEE Press, 2004.

- [5] B. Miller and R. J. Conley, "A multiple modulator fractional divider," *IEEE Trans. Instrum. Meas.*, vol. 40, no. 3, pp. 578–583, Jun. 1991.

- [6] T. A. D. Riley and M. A. Copeland, "Delta-sigma modulation in fractional-*N* frequency synthesis," *IEEE J. Solid-State Circuits*, vol. 28, no. 5, pp. 553–559, May 1993.

- [7] I. Galton, "Delta-Sigma Fractional-N Phase-Locked Loops," in *Phase-Locking in High-Performance Systems From Devices to Architectures*, B. Razavi, Ed. : IEEE Press, 2003.

- [8] B. D. Muer and M. Steyaert, CMOS Fractional-N Synthesizers: Design for High Spectral Purity and Monolithic Integration. : Kluwer Academic, 2003.

- [9] M. Kozak and I. Kale, Oversampled Delta-Sigma Modulators, Analysis, Applications and Novel Topologies. Boston, MA: Kluwer Academic, 2003.

- [10] S. Pamarti and I. Galton, "LSB dithering in MASH delta-sigma D/A converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 4, pp. 779–790, Apr. 2007.

- [11] S. Pamarti, J. Welz, and I. Galton, "Statistics of the quantization noise in 1-bit dithered single-quantizer digital delta-sigma modulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 3, pp. 492–503, Mar. 2007.

- [12] M. J. Borkowski, T. A. D. Riley, J. Hakkinen, and J. Kostamovaara, "A practical delta-sigma modulator design method based on periodical behavior analysis," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 52, pp. 626–630, Oct. 2005.

- [13] K. Hosseini and M. P. Kennedy, "Mathematical analysis of digital MASH Delta-Sigma modulators for fractional-*N* frequency synthesizers," in *in Proc. PRIME 2006*, Otranto, Italy, Jun., pp. 309–312.