| Title                       | Field-effect transistor figures of merit for vapor-liquid-solid-<br>grown Ge1-xSnx (x = 0.03–0.09) nanowire devices                                                                                                                                                                                                                                                            |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Galluccio, Emmanuele;Doherty, Jessica;Biswas, Subhajit;Holmes,<br>Justin D.;Duffy, Ray                                                                                                                                                                                                                                                                                         |

| Publication date            | 2020-04-08                                                                                                                                                                                                                                                                                                                                                                     |

| Original Citation           | Galluccio, E., Dohert, J., Biswas, S., Holmes, J. D. and Duffy, R. (2020) 'Field-Effect Transistor Figures of Merit for Vapor-Liquid-Solid-Grown Ge1-xSnx (x = 0.03-0.09) Nanowire Devices', ACS Applied Electronic Materials, 2(5), pp.1226-1234. doi: 10.1021/acsaelm.0c00036                                                                                                |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                        |

| Link to publisher's version | https://pubs.acs.org/doi/abs/10.1021/acsaelm.0c00036 - 10.1021/acsaelm.0c00036                                                                                                                                                                                                                                                                                                 |

| Rights                      | © 2020 American Chemical Society. This document is the Accepted Manuscript version of a Published Work that appeared in final form in ACS Applied Electronic Materials, copyright © American Chemical Society after peer review and technical editing by the publisher. To access the final edited and published work see https://pubs.acs.org/doi/abs/10.1021/acsaelm.0c00036 |

| Download date               | 2025-02-09 04:26:07                                                                                                                                                                                                                                                                                                                                                            |

| Item downloaded from        | https://hdl.handle.net/10468/10149                                                                                                                                                                                                                                                                                                                                             |

# Field-Effect Transistor Figures of Merit for VLS-Grown Ge1-xSnx (x = 0.03-0.09) Nanowire Devices

Emmanuele Galluccio†\*, Jessica Doherty†‡, Subhajit Biswas†‡, Justin D. Holmes†‡ and Ray Duffy†

† Tyndall National Institute, University College Cork, Lee Maltings, Cork, Ireland.

‡ School of Chemistry and AMBER Centre, University College Cork, Cork, Ireland.

**KEYWORDS** -  $Ge_{1-x}Sn_x$  nanowires, low temperature processing, contact resistance, carrier mobility, subthreshold slope, MOSFETs.

# **ABSTRACT**

Ge<sub>1-x</sub>Sn<sub>x</sub> alloys form a heterogeneous material system with high potential application in both optoelectronic and high speed electronics devices. The attractiveness of Ge<sub>1-x</sub>Sn<sub>x</sub> lies in the ability to tune the semiconductor bandgap and electronic properties as a function of Sn concentration. Advances in Ge<sub>1-x</sub>Sn<sub>x</sub> material synthesis have raised expectations recently, but there are considerable problems in terms of device demonstration. Although Ge<sub>1-x</sub>Sn<sub>x</sub> thin films have been previously experimentally explored, in-depth studies of the electrical properties of Ge<sub>1-x</sub>Sn<sub>x</sub> nanostructures are very limited, specifically nanowires grown via a bottom-up vaporliquid-solid (VLS) process using metal catalysts. In this study a detailed electrical investigation is presented of nominally undoped Ge<sub>1-x</sub>Sn<sub>x</sub> bottom-up-grown nanowire devices with different Sn percentages (3-9 at.%). The entire device fabrication process is performed at relatively low temperatures, the maximum temperature being 440 °C. Device current modulation is performed through backgating from a substrate electrode achieving impressive on-off current (I<sub>ON</sub>/I<sub>OFF</sub>) ratios of up to 10<sup>5</sup>, showing their potential for electronic and sensor-based applications. Through an extensive parameter extraction routine it is clear that contact resistance (R<sub>C</sub>) extraction is essential for proper VLS-grown nanowire device electrical evaluation. Once the R<sub>C</sub> contribution is extracted and removed, parameter values such as mobility, can change significantly, by up to 70 % in this work. When benchmarked against other Ge<sub>1-x</sub>Sn<sub>x</sub> electron devices, the VLS-grown nanowire devices have potential in applications where a high I<sub>ON</sub>/I<sub>OFF</sub> ratio is important, and where thermal budget and processing temperatures are required to be kept to a minimum.

## I. INTRODUCTION

Recently electronic miniaturization has reached fundamental physical constraints, therefore substantial efforts are being made in defining the performance limits and exploring new applications to overcome this, including the development of devices based on 3D nanostructures <sup>1-3</sup>, many fabricated from bottom-up grown nanowires <sup>4</sup>. In recent decades advances in nanowire synthesis and fabrication have led to the development of devices such as field effect transistors <sup>5-6</sup>, logic circuits <sup>7</sup>, sensing devices <sup>8-9</sup> and solar cells <sup>10</sup>. Nevertheless, despite the great achievements reached with Si <sup>5</sup> continual semiconductor innovation has encouraged the exploration of new frontiers, such as developing III-Vs or other group IV semiconductors nanowires.

Although remarkable results for Ge <sup>11</sup>, GaN <sup>12</sup> and InAs <sup>1</sup> have been reported in the literature, nowadays GeSn, a relatively immature group IV semiconductor alloy, appears to be a very attractive material due to its fundamental properties. Several key factors have contributed to the advancement of Ge<sub>1-x</sub>Sn<sub>x</sub>, such as the ability to tune its bandgap as a function of Sn concentration <sup>13-14</sup>, higher electron and hole mobility compared to Si and Ge <sup>15</sup> and easy integration into the already well-established Si manufacturing technology platforms. Ge<sub>1-x</sub>Sn<sub>x</sub> alloys enable a heterogeneous material system, usable both for optoelectronic purposes, *e.g.* lasers <sup>16-17</sup> and photodetectors <sup>18-19</sup>, or for high speed electronics devices <sup>20-21</sup>.

Recently, chemically synthesized nanomaterials and bottom-up methodologies have been proposed to sustain the relentless progress in the development of new concepts for future electronics. These procedures may present advantages over the already consolidated top-down lithography process, such as the higher degree of structural and surface perfection even as the gate length is scaled, or the lower manufacturing cost. Specifically in the case of novel alloys such as Ge<sub>1-x</sub>Sn<sub>x</sub>, to date, Ge<sub>1-x</sub>Sn<sub>x</sub> nanowires have been developed in two different ways, either by using Ge nanowires as a template material in order to obtain Ge/GeSn anisotropic single

crystalline core-shell nanowires <sup>22</sup>, or through metal-seed growth via gas phase <sup>23-25</sup> or solution-based synthesis <sup>26-27</sup>.

In parallel, the modelling community have extracted parameters and models for  $Ge_{1-x}Sn_x$  of various compositions  $^{28-31}$ , for device design and have provided valuable insights into the physics of this complex alloy system  $^{32-34}$ . Improving the processing aspects, coupled with simulation analysis might lead to breakthrough results in future for  $Ge_{1-x}Sn_x$  nanowires devices.

However, despite the extensive studies and the continuous improvement of  $Ge_{1-x}Sn_x$  there are only few reports on the electronic properties of the  $Ge_{1-x}Sn_x$  nanostructures <sup>35</sup>. In the context of a bottom-up approach, there are limited reports on the implementation of bottom-up grown nanowires in FET-like devices. Only recently,  $Ge_{0.81}Sn_{0.19}$  nanowires were shown to have higher conductivity compared to pure Ge nanowires by fabricating simple two and four terminal devices to individual nanowires <sup>35</sup>. In contrast, top-down fabricated  $Ge_{1-x}Sn_x$  nanostructures, based on the etching and doping of thin films, show promise as fin-like FET devices <sup>36-37</sup>.

Finally, the lack of literature concerning the electronic characterization of bottom-up grown GeSn nanowires, with different Sn concentrations, prevents us from benchmarking the performance of  $Ge_{1-x}Sn_x$  nanostructures in various forms. In this article we report for the first time some of the most important FET electronic figures of merit for nominally undoped, VLS-grown  $Ge_{1-x}Sn_x$  nanowires, such as mobility,  $I_{ON}/I_{OFF}$  ratio, subthreshold swing (SS) and transconductance (gm) as a function of Sn content (x = 0.03, 0.06 and 0.09).

## II. EXPERIMENTAL

# A. $Ge_{1-x}Sn_x$ nanowire synthesis

Ge<sub>1-x</sub>Sn<sub>x</sub> nanowires (with x ranging from 0.03 to 0.09) were grown via a liquid-injection chemical vapor deposition (LICVD) technique, as previously described  $^{23-24}$ . A continuous-flow reaction was adopted for nanowire growth on Si (001) substrates, coated with AuAg (90:10 and 80:20) nanoparticle seeds, in a toluene medium using a LICVD technique. Solutions of diphenylgermane (DPG), the Ge precursor, and different Sn precursors (allyltributylstannane (ATBS) and tetraethyltin (TET)) in anhydrous toluene were injected into the metal reaction cell using a syringe pump at a constant rate of 0.025 ml min<sup>-1</sup> with a parallel flow of H<sub>2</sub>/Ar at a rate of 0.5 sccm. The growth temperature was set at 440 °C. Post-grown nanowires were washed with dry toluene and dried under N<sub>2</sub> flow for further characterization.

# B. $Ge_{1-x}Sn_x$ nanowire device processing

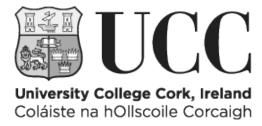

A schematic representation of the process flow used to contact Ge<sub>1-x</sub>Sn<sub>x</sub> nanowires is shown in Figure 1. Nanowires with different mean Sn contents (Ge<sub>0.97</sub>Sn<sub>0.03</sub>, Ge<sub>0.94</sub>Sn<sub>0.06</sub>, and Ge<sub>0.91</sub>Sn<sub>0.09</sub>) were transferred onto a highly p-doped Si substrate with a thermally grown SiO<sub>2</sub> layer (250 nm thick) and with predefined macroscopic Ti-Au metal bonding pads. The Si/SiO<sub>2</sub> pre-patterned wafer was cleaned using a dip it for 30 sec in acetone, 30 sec in isopropyl alcohol and subsequently rinsed it under deionised (DI) water for another 30 sec. After the cleaning stage the nanowires were dropped onto the substrate and prior to electron beam lithography (EBL) processing, each sample was analyzed with a scanning electron microscope (SEM), to detect the nanowire spreading density on the wafer surface. After inspection, source-drain (S/D) contacts were fabricated; each sample was covered by a polymethyl methacrylate (PMMA) photoresist layer and subsequently exposed at 10 keV to create patterned structures. Directly after the S/D contacts exposure the samples underwent native oxide removal from the

unmasked surface; they were dipped for 10 sec in a buffered oxide etch (BOE) solution (6 parts  $40 \% \text{ NH}_4\text{F}$  and 1 part in 4 of 9 % HF), 30 sec in DI and subsequently dried with a nitrogen gun. Metallisation of the contacts (25 nm of Ni and 35 nm of Au) was deposited in a FC2000 electron beam evaporator at a pressure of  $6.6 \times 10^{-5}$  Pa. Finally, the devices were inspected by SEM and electrical measurements was carried out at room temperature to extract the electrical performance of the  $\text{Ge}_{1-x}\text{Sn}_x$  nanowires.

**Figure 1:** (a) Illustrative image of the contacting scheme for the bottom-up grown nanowires. (b) A schematic representation of the  $Ge_{1-x}Sn_x$  nanowire device process flow used in this study. (c) A close-up schematic and finally (d) and (e) are representative SEM images of  $Ge_{1-x}Sn_x$  nanowire device.

# C. $Ge_{1-x}Sn_x$ nanowire device characterisation

Bottom-up grown  $Ge_{1-x}Sn_x$  nanowires were imaged on a FEI Helios NanoLab 600i SEM and the devices developed were investigated on the Zeiss Supra55VP SEM. All energy-dispersive X-ray (EDX) measurements for Sn content determination were recorded in high-

angle annular dark-field mode in the FEI Helios NanoLab 600i operating at 30 kV and 0.69 nA with an attached Oxford X-Max 80 detector. The error in the EDX measurements was a standard error of ±0.5 at. %. High-resolution scanning transmission electron microscope (STEM) imaging and electron energy loss spectroscopy (EELS) mapping was performed using a Nion UltraSTEM100 microscope, operated at 100 kV. Electrical measurements at room temperature were carried out with a Cascade semiautomatic prober station and an Agilent (HP) 4156C Parameter Analyser. To minimize the influence of the light the measurements were made in a dark ambient with a detected leakage current in the range of pico Amperes.

#### III. RESULTS AND DISCUSSION

# A. Structural analysis

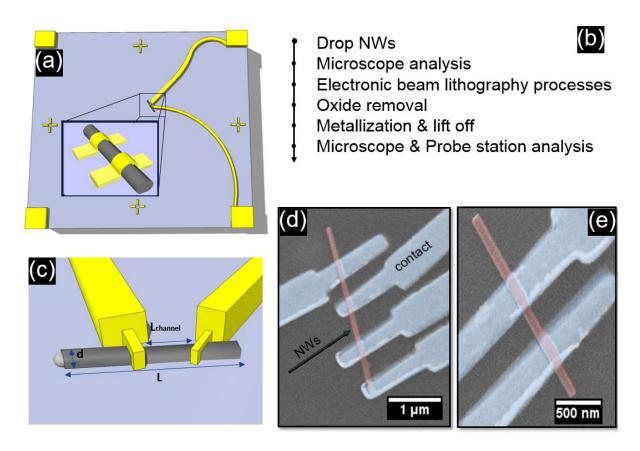

Ge<sub>1-x</sub>Sn<sub>x</sub> nanowires were synthesized using a VLS procedure employing a gold-silver (AuAg) alloy as metal seeds. Variation of different growth parameters, *e.g.* precursors, temperature, stoichiometry of the AuAg alloy catalyst *etc.*, resulted in Ge<sub>1-x</sub>Sn<sub>x</sub> alloy nanowires with different mean Sn contents ranging from 3 - 9 at.%. We have detailed the fabrication process and influence of growth parameters on the morphology, crystal structure and stoichiometry of the Ge<sub>1-x</sub>Sn<sub>x</sub> nanowires in previous publications <sup>23-24</sup>. Most importantly, the morphological quality, *e.g.* uniform diameter, minimal Sn clustering *etc.*, of the nanowires was intact for all the three nanowires concentration investigated <sup>38</sup>. An SEM image of Ge<sub>1-x</sub>Sn<sub>x</sub> (x = 0.09) nanowires grown at 440 °C using a Au<sub>0.80</sub>Ag<sub>0.20</sub> catalyst and TET as the precursor can be seen in Figure 2(a). Sn incorporation was confirmed via EDX point analysis on the nanowires, which showed a typical standard deviation of 0.6-1.2 at.% from the average Sn content <sup>38</sup>. EDX maps were also generated to confirm the homogenous distribution of Sn in the nanowires, which is crucial to verify the accurate electrical performance of the nanowires (see Figure 2(b)). Determining the structural quality of the Ge<sub>1-x</sub>Sn<sub>x</sub> nanowires is also imperative

for its device implementation. Generally, the crystal structure of the alloy nanowires, with various Sn incorporation, exhibited a 3C lattice arrangement without any stacking faults and twin boundaries. A representative dark field STEM image and corresponding fast Fourier transformation (FFT), shown in Figure 2(c), confirmed the single crystalline nature of the Ge<sub>1</sub>.  $_x$ Sn<sub>x</sub> (x = 0.09) nanowires with a <111> crystal growth direction.

**Figure 2:** (a) Representative SEM image of  $Ge_{1-x}Sn_x$  (x=0.09) nanowires. (b) EDX mapping and corresponding high-angle annular dark-field (HAADF) image for Ge and  $Ge_{1-x}Sn_x$  nanowire with 9 at.% of Ge of Ge n. (c) Lattice-resolved STEM HAADF image recorded from the core of an alloy nanowire showing its single crystalline nature. Corresponding FFT is shown in the inset.

## B. Electrical analysis and parameter extraction

The electrical field effect characteristics of the nominally undoped  $Ge_{1-x}Sn_x$  nanowires were determined; thus the transfer characteristics ( $I_d$ - $V_g$ ) obtained highlight the electrical properties of these nanowires as a function of Sn concentration. Prior to electrical testing nanowire was imaged by SEM to confirm the morphological quality of the devices and to determine the device geometry, *e.g.* channel length and nanowire diameter.

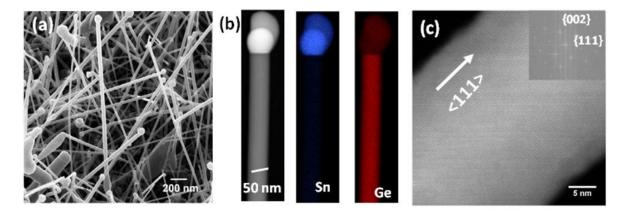

Firstly, each device was analyzed for current conduction using top contacts (see Figure 1) with the backgate electrode set to 0 V. As expected, since the material is unintentionally doped  $I_{ds}$ - $V_{ds}$  characteristics with  $V_{bg}=0$ , show close to linear behavior through the origin, as seen Figure 3. The quasi-linear electrical features from most of the nanowires indicates non-ideal contacts between the electrode and the nanowires, possibly due to the presence of an

oxide layer at the contact point and/or the relatively low dopant concentrations within the nanowires themselves.

**Figure 3**: Representative  $I_d$ - $V_d$  inspection ( $V_{bg} = 0$  V) for the three different nanowire samples; (a) is  $Ge_{0.97}Sn_{0.03}$ , (b) is  $Ge_{0.94}Sn_{0.06}$  (c)  $Ge_{0.91}Sn_{0.09}$ .

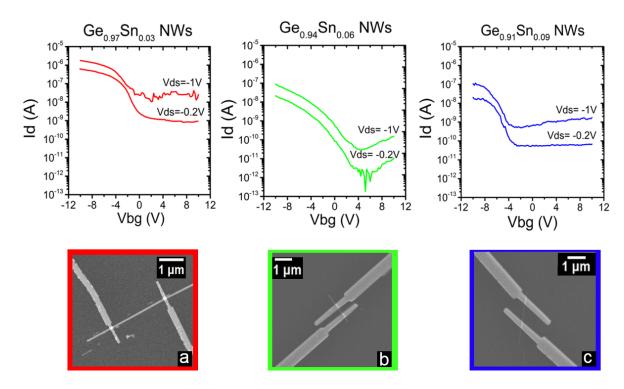

After the preliminary inspection of the contact behavior, transfer characteristic measurements were performed by sweeping the backgate voltage between -10 V to 10 V and setting the S/D bias voltage as -0.2 or -1 V. The measurement range was carefully selected to prevent damage of nanowires from high current densities and subsequent partial degradation of the devices. Figure 4 shows representative I<sub>ds</sub>-V<sub>bg</sub> transfer characteristics of the nanowires as a function of the Sn content and highlights their ability to modulate the current at all Sn concentrations investigated, even without intentional doping. Although the nanowires were nominally undoped, Figure 4 shows that they all display p-type semiconductor features. These characteristics are similar to those previously observed for undoped VLS-grown Ge nanowires, which tend to accumulate holes due to the formation of a negative trapped charge layer at the semiconductor surface <sup>39</sup>. Furthermore, defects in bulk Ge tend to produce p-type charges, for example Romano *et al.* <sup>40</sup> showed that damage from Ge ion implants into Ge created p-type carriers. Even though our nanowires were not ion implanted, intrinsic point defects within the GeSn crystal structures here are likely to be p-type in nature.

**Figure 4:** (Top row) Representative room temperature  $I_d$ - $V_{bg}$  characteristics for  $Ge_{0.97}Sn_{0.03}$ ,  $Ge_{0.94}Sn_{0.06}$  and  $Ge_{0.91}Sn_{0.09}$  nanowires with two different  $V_d$  values (-0.2V and -1V). (Bottom row) Representative SEM images of typical nanowire devices with 3, 6, and 9 at.% of Sn in (a), (b), and (c) respectively.

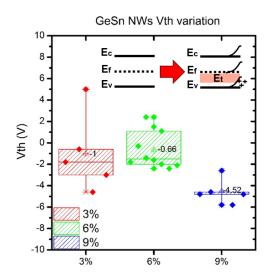

Extraction of threshold voltages (V<sub>th</sub>) was carried out using the transconductance derivative methodology at low drain voltages <sup>41</sup>. V<sub>th</sub> variation as a function of Sn concentration in the nanowire is shown in Figure 5. Mean V<sub>th</sub> values were calculated in order to compare alloy nanowires with different Sn incorporation. We speculated that the V<sub>th</sub> variation might derive from the negative surface charge layer given by the GeSn oxides or from the underlying SiO<sub>2</sub> layer. The overlying GeSn oxide layers, being a source of traps, might lead to a more negative flat band potential and consequently to a V<sub>th</sub> shift (see inset of Figure 5).

**Figure 5:** Box plot for the  $V_{th}$  extracted as a function of the Sn % in the  $Ge_{1-x}Sn_x$  nanowires. The black text shows the mean number per data set, while all the values measured are presented as scatter points.

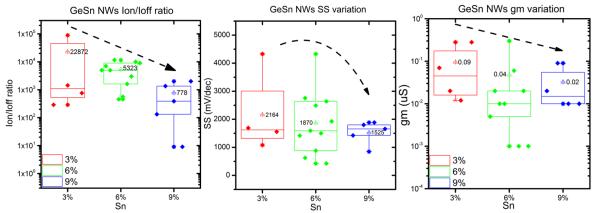

In addition, the  $I_{ON/I_{OFF}}$  ratio, sub-threshold slope (SS), and  $g_m$  have also been extracted from the electrical characteristics considering 30 % of the  $V_{gs}$  swing, below  $V_{th}$ , is assigned to the off state while the remaining 70 % is assigned to the on state  $^1$ . Since all of the devices fabricated show very wide variations, as was shown for  $V_{th}$  in Figure 5, a mean value has been estimated for each extracted electrical parameter. This methodology allows us to obtain trends based on the Sn concentration, as shown in Figure 6. The highest individual device  $I_{ON/I_{OFF}}$  ratio of  $10^5$  was observed for  $Ge_{0.97}Sn_{0.03}$  nanowires, with this ratio decreasing with increasing Sn content; due to the relative increase in  $I_{OFF}$  resulting from a reduction in the bandgap of the nanowires.

Concerning SS, values were extracted at the midpoint of the subthreshold characteristic. As expected, using a back-biasing device architecture, the values reported are quite large compared with a typical top-gate biasing FET device. The mean value of the SS varied from 2164 mV/dec, obtained for Ge<sub>0.97</sub>Sn<sub>0.03</sub> nanowires, to 1525 mV/dec for Ge<sub>0.91</sub>Sn<sub>0.09</sub> nanowires. The minimum SS values obtained for individual nanowires were 1081 mV/dec for Ge<sub>0.97</sub>Sn<sub>0.03</sub>, 426 mV/dec for Ge<sub>0.94</sub>Sn<sub>0.06</sub> and 829 mV/dec for Ge<sub>0.91</sub>Sn<sub>0.09</sub> respectively. Despite the

magnitude of the SS variation for each set of nanowires, it was possible to observe a mean decrease in SS with increasing Sn content. Top-gating and a gate-all-around device architecture would be necessary to further reduce these SS values.

Conversely, mean transconductance values  $(g_m = \delta_{Id}/\delta_{Vbg})$  decreased with increasing Sn content in the nanowires. The mean value varied between 0.02-0.09  $\mu$ S with the maximum value of 0.28  $\mu$ S obtained for Ge<sub>0.97</sub>Sn<sub>0.03</sub> nanowires. All of the mean values extracted are summarised in Table 1.

**Figure 6:**  $I_{ON}/I_{OFF}$ , SS, and  $g_m$  extracted from  $Ge_{1-x}Sn_x$  nanowire FET devices, as a function of the Sn concentration.

**Table 1:** Summary of the mean values obtained for  $Ge_{1-x}Sn_x$  nanowire FET devices as a function of the Sn concentration.

| $Ge_{1-x}Sn_x$                        | Electrical parameters                   |             |                |             |  |  |  |  |

|---------------------------------------|-----------------------------------------|-------------|----------------|-------------|--|--|--|--|

| nanowires                             | I <sub>ON</sub> /I <sub>OFF</sub> ratio | SS (mV/dec) | $g_{m}(\mu S)$ | $V_{th}(V)$ |  |  |  |  |

| Ge <sub>0.97</sub> Sn <sub>0.03</sub> | 2.28×10 <sup>4</sup>                    | 2164        | 0.095          | -1          |  |  |  |  |

| $Ge_{0.94}Sn_{0.06}$                  | $5.32 \times 10^3$                      | 1870        | 0.047          | -0.66       |  |  |  |  |

| $Ge_{0.91}Sn_{0.09}$                  | $7.80 \times 10^2$                      | 1525        | 0.032          | -4.52       |  |  |  |  |

The trends shown in Figure 6 and in Table 1 can be understood by taking into account gate electrostatic effects. Generally, in a p-type device for  $V_g > 0$  holes are depleted from the channel. This effect leads to a decrease in the conductivity while the opposite behavior will happen for  $V_g < 0$ . However, in our case, since the devices shows p-type behavior, by reducing  $V_g$  we observe a remarkable off current increment due to band bending in the channel. The off current increment and the theoretical reduction of the bandgap with increasing Sn content

explains the good electrical performance for the  $Ge_{1-x}Sn_x$  nanowires, with a Sn content up to 6 at.%. Beyond 6 at.%, based on our data, the  $Ge_{1-x}Sn_x$  alloys become difficult to control, due the small bandgap expected, for electronic applications particularly in a back-gate device architecture, due to the lower electrostatic control compared to a top-gate or gate-all-around architecture.

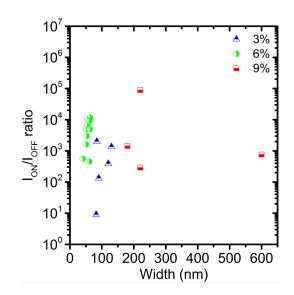

Figure 7 shows a plot of  $I_{ON}/I_{OFF}$  ratios as a function of nanowire width for all three different Sn compositions. There appears to be little or no correlation between  $I_{ON}/I_{OFF}$  ratios and nanowire diameter, although the nanowires are relatively large for such a junctionless transistor design. Also the nanowires are undoped, meaning they are likely to be fully depleted when off, and in accumulation when on.

**Figure 7:** Scatter plot of  $I_{ON}I_{OFF}$  as a function of nanowire width for the three different Sn compositions.

Considering the linear region of the I-V curves obtain for the nanowires carrier mobilities were extracted from the transfer characteristics using equation 1:

$$\mu = g_m L / (WCV_{sd}) \tag{1}$$

where L and W are respectively the nanowire length and width,  $V_{sd}$  is the bias between source and drain; C is the capacitance for a backgated nanowire device <sup>6</sup> obtained using equation 2:

$$C = 2\pi\varepsilon\varepsilon_0 L(\cosh^{-1}(\frac{d+2h}{d}))^{-1}$$

(2)

with  $\varepsilon$  as the dielectric constant of the SiO<sub>2</sub> layer of h thickness, and d is nanowire diameter. Taking into consideration nanowire diameters the carrier mobility was extracted for all of the devices using the maximum  $g_m$  value. The mean carrier mobility was evaluated for the three different Sn compositions, with values of 2.67, 8.51 and 11.87 cm<sup>2</sup>/Vs obtained for Ge<sub>0.97</sub>Sn<sub>0.03</sub>, Ge<sub>0.94</sub>Sn<sub>0.06</sub> and Ge<sub>0.91</sub>Sn<sub>0.09</sub> nanowires respectively.

# C. Contact resistance evaluation and subsequent parameter extraction

The values obtained using this methodology tend to underestimate  $V_{th}$  and carrier mobility due to the non-negligible contribution of the contact resistance. Therefore to take into account the contact resistivity contribution, the Y function method was used  $^{42}$  to extract both  $V_{th}$  and carrier mobility. We utilised the Y function shown in equation 3:

$$Y = \frac{I_{ds}}{am^{\frac{1}{2}}} = (\frac{W}{L}\mu_0 C_{0x} V_{ds})(V_{gs} - V_{th})$$

(3)

to extract the carrier mobility and the  $V_{th}$  from the slope and the intercept of the curve, as shown in Figure 8. In addition, using the Y-function methodology we estimated the contact resistance ( $R_C$ ) of the backgate MOSFET device using the mobility degradation parameter, shown in equation 4:

$$\theta = \left[ \left( \frac{I_{ds}}{g_m (V_{gs} - V_{th})} \right) - 1 \right] / (V_{gs} - V_{th})$$

(4)

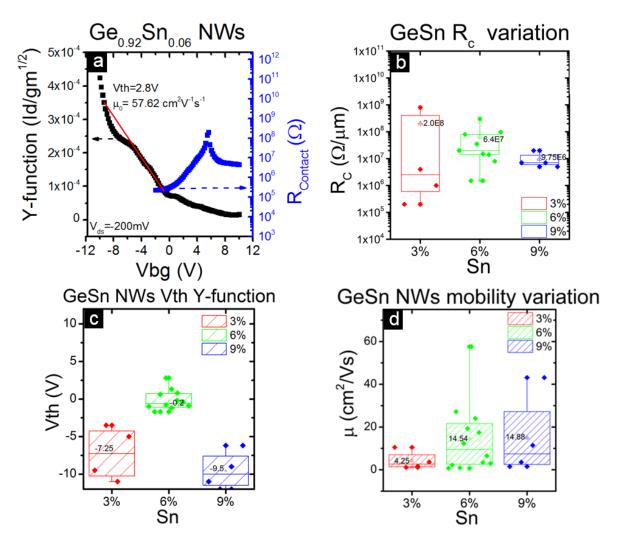

After extraction, the parameter values were inserted in the following equation  $\theta = \theta_0 + R_c C_{ox} \mu_0 \frac{W}{L}$  considering that at large values of  $V_{gs}$  ( $V_{gs} - V_{th} = 10V$ )  $\theta_0$  the mobility degradation factor related to the channel scattering is negligible <sup>43</sup> and the major contribution comes from the second term; see Figure 8(a) and (b). Figure 8(c) shows the  $V_{th}$  variation after the removal of the  $R_C$  contribution. It is possible to see that the  $V_{th}$  decreases drastically

compared with previous data in Figure 5 for  $Ge_{0.97}Sn_{0.03}$  and  $Ge_{0.91}Sn_{0.09}$  nanowires respectively, changing from -1 to -7.25 V and from -4.25 to -9.25 V; while for  $Ge_{0.94}Sn_{0.06}$  V<sub>th</sub> shows a different trend moving from -0.66 to -0.25 V. This highlights the importance of extracting and removing the  $R_C$  contribution when estimating electrical parameters from these type of nanowire devices.

Figure 8(d) shows the mobility extracted considering the Y function in equation 3; it is noteworthy that mobility data reported earlier do not take into account the contribution of the contact resistance (2.67 cm²/Vs for Ge<sub>0.97</sub>Sn<sub>0.03</sub>, 8.51 cm²/Vs for Ge<sub>0.94</sub>Sn<sub>0.06</sub> and 11.87 cm²/Vs for Ge<sub>0.91</sub>Sn<sub>0.09</sub>). With the contribution of R<sub>C</sub> accounted for, the μ values become 4.25 cm²/Vs for Ge<sub>0.97</sub>Sn<sub>0.03</sub>, 14.54 cm²/Vs for Ge<sub>0.94</sub>Sn<sub>0.06</sub> and 14.80 cm²/Vs for Ge<sub>0.91</sub>Sn<sub>0.09</sub> respectively. Therefore from Figure 8(d) it is evident that for all nanowires the mean carrier mobility increases by 60, 70, and 25 % for Ge<sub>0.97</sub>Sn<sub>0.03</sub>, Ge<sub>0.94</sub>Sn<sub>0.06</sub> and Ge<sub>0.91</sub>Sn<sub>0.09</sub> respectively on average, again highlighting the importance of removing the R<sub>C</sub> contribution.

**Figure 8:** (a) Y function and contact resistance extraction for a representative 6 at.% Sn nanowire device. (b)  $R_C$  extracted as a function of the Sn concentration, (c) and (d) show respectively  $V_{th}$  and mobility trends after the Y function application. In red there are data related to 3 at.% Sn, in green data related to 6 at.% Sn and in blue data related to 9 at.% Sn.

Data extracted are in accordance with previous results <sup>44</sup>, where the carrier mobility increases as a function of the Sn concentration due to the proportional increment of the channel compressive strain which boosts the hole mobility; whilst the major mobility limitations are the phonons and alloy scattering. Note, as expected in a structure like a nanowire, with surfaces on all sides, and consequently enhanced surface carrier scattering, the mobility values are lower than those extracted in thick-films which have minimal surface scattering effects <sup>37, 45-49</sup>.

# D. Figures of merit comparison for different $Ge_{1-x}Sn_x$ architectures and devices

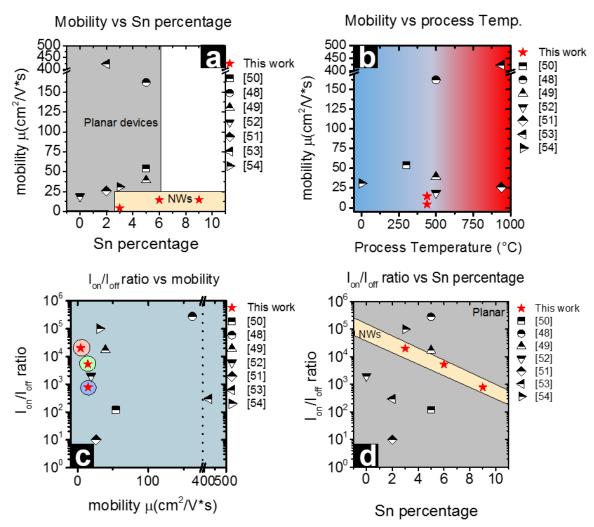

Table 2 and Fig. 9 shows the comparison among the most common electrical parameters obtained to date with different device architectures and GeSn channel compositions considering process temperatures below 1000 °C <sup>48-54</sup>.

**Table 2:** Electrical parameters comparison for the most important figures of merit extracted from different  $Ge_{1-x}Sn_x$  device structures. Data related to this work has been highlighted with red, green and blue as a function of the different Sn concentrations, namely 3, 6, and 9 at.%.

| Year                                    | 2019, this work         |                          |                          | 2019 50              | 2019 48               | 2018 49                 | 2017 52              | 2016 51              | 2015 53                 | 2014 54                |

|-----------------------------------------|-------------------------|--------------------------|--------------------------|----------------------|-----------------------|-------------------------|----------------------|----------------------|-------------------------|------------------------|

| Sn%                                     | 9                       | 6                        | 3                        | 4                    | 5                     | 5                       | 2                    | 0                    | 2                       | 3                      |

| Proc.<br>T.                             | <440°C                  | <440°C                   | <440°C                   | <300°C               | 500°C                 | 500°C                   | >938°C               | 500°C                | >938°C                  | 300°C                  |

| Dev.<br>Struc                           | NWs<br>(bot. gate)      | NWs<br>(bot. gate)       | NWs<br>(bot. gate)       | Planar<br>(top gate) | Planar<br>(top gate)  | Planar<br>(bot. gate)   | Planar<br>(top gate) | Planar<br>(top gate) | Planar<br>(top gate)    | Tri gate               |

| Peak<br>µ                               | $\mu$ =4.25 $(cm^2/Vs)$ | $\mu$ =14.54 $(cm^2/Vs)$ | $\mu = 14.9$ $(cm^2/Vs)$ | $\mu=54$ $(cm^2/Vs)$ | $\mu=162$ $(cm^2/Vs)$ | $\mu$ =39.3 $(cm^2/Vs)$ | $\mu=26$ $(cm^2/Vs)$ | $\mu=19$ $(cm^2/Vs)$ | $\mu = 423$ $(cm^2/Vs)$ | $ \mu=31 $ $(cm^2/Vs)$ |

| I <sub>on</sub> /I <sub>off</sub> ratio | 2.3×10 <sup>4</sup>     | 5.3×10³                  | 7.8×10 <sup>2</sup>      | 1.2×10 <sup>2</sup>  | 2.8×10 <sup>5</sup>   | 1.7×10 <sup>4</sup>     | ≈ 10¹                | 2 ×10 <sup>3</sup>   | 3×10 <sup>2</sup>       | ≈ 10 <sup>5</sup>      |

Of note, all the documents data shown in Table 2, except for this work, refers to top or bottom gated planar FET devices. Nevertheless, it is possible to see that the data obtained from our study are comparable. Figure 9(a) shows the mobility data obtained as a function of Ge<sub>1-x</sub>Sn<sub>x</sub> channel composition; most of data-points are located between 0 to 50 cm<sup>2</sup>/Vs with the exception of <sup>48</sup> and <sup>53</sup> which show mobility values of 162 and 423 cm<sup>2</sup>/Vs respectively. Moreover, considering the extreme sensitivity of the material with respect to temperature, Figure 9(b) reports I<sub>ON</sub>/I<sub>OFF</sub> ratio as a function of the maximum process temperature used, where it is possible to observe decreasing I<sub>ON</sub>/I<sub>OFF</sub> at temperatures approaching 1000 °C. Figure 9(c) shows I<sub>ON</sub>/I<sub>OFF</sub> ratio data versus mobility for our nanowires benchmarked against planar structures previously reported in the literature. Figure 9(d) highlights how our VLS-grown nanowires compare with planar device architectures, in terms of I<sub>ON</sub>/I<sub>OFF</sub> ratios versus Sn concentration. Overall, considering Sn content, processing temperature and device figures of merit our bottom-up grown Ge<sub>1-x</sub>Sn<sub>x</sub> nanowires have potential in applications where a high on-

to-off current ratio is important, and in particular where the thermal budget and processing temperature are needed to be kept to a minimum.

**Figure 9:** Electrical parameter comparison with previous works found in literature (a) mobility as a function of different Sn concentration, (b)  $I_{ON}I_{OFF}$  ratio as a function of the process temperature, (c)  $I_{ON}I_{OFF}$  ratio versus mobility for  $Ge_{1-x}Sn_x$  nanowires and planar structures, (d)  $I_{ON}I_{OFF}$  ratio as a function of Sn content.

A concluding remark from this study is that for high speed device applications Ge<sub>0.97</sub>Sn<sub>0.03</sub> VLS-grown nanowires appear to be the best material candidate. Nevertheless considering the data variability; as pointed out beforehand; further studies on the surface states and on the metal-semiconductor contacts <sup>55-56</sup> should be addressed in order to reduce the data distribution and to improve the performance of the material that shows high potential for future applications.

## IV. CONCLUSIONS

A comprehensive investigation has been made on the electrical performance of Ge<sub>0.97</sub>Sn<sub>0.03</sub>, Ge<sub>0.94</sub>Sn<sub>0.06</sub> and Ge<sub>0.91</sub>Sn<sub>0.09</sub> VLS-grown nanowires which were fabricated using a relatively low-temperature process; with a maximum temperature of only 440 °C. From the transfer characteristics, obtained by sweeping the backgate at low V<sub>ds</sub> voltage, several electrical parameters such as the I<sub>ON</sub>/I<sub>OFF</sub> ratio, SS, g<sub>m</sub> and mobility were extracted. Comparing the different Sn content in the nanowires it appears that the best electrical performance was obtained for Ge<sub>0.97</sub>Sn<sub>0.03</sub> nanowires, due to the intrinsic characteristic of the material. The data extracted in this study represents one of the first in depth electrical investigations of Ge<sub>1-x</sub>Sn<sub>x</sub> nanowires which could potentially be used to calibrate on-going modelling studies, *e.g.* quantisation phenomena as a function of channel length reduction. Finally, in comparing Ge<sub>1-x</sub>Sn<sub>x</sub> device figures of merit, the VLS bottom-up grown have a clear advantage over other fabrication routes, in that the maximum process temperature is only 440 °C, which is relatively low, and thus compatible with back-end-of-line integration schemes in nanoelectronic chip production.

## **ACKNOWLEDGEMENTS**

We acknowledge the financial support from Science Foundation Ireland (Grant 14/IA/2513). EG acknowledges Georgios Fagas for his help during the writing and Dan O'Connell and Carmel Murphy for assistance with sample processing.

# **Corresponding Author**

emmanuele.galluccio@tyndall.ie;

#### **REFERENCES**

- 1. Lu, W.; Xie, P.; Lieber, C. M., Nanowire transistor performance limits and applications. *IEEE transactions on Electron Devices* **2008**, *55* (11), 2859-2876.

- 2. Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T. In *A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors*, 2012 Symposium on VLSI Technology (VLSIT), IEEE: 2012; pp 131-132.

- 3. Schuegraf, K.; Abraham, M. C.; Brand, A.; Naik, M.; Thakur, R., Semiconductor Logic Technology Innovation to Achieve Sub-10 nm Manufacturing. *IEEE Journal of the Electron Devices Society* **2013**, *I* (3), 66-75.

- 4. Lieber, C. M., The incredible shrinking circuit. *Scientific American* **2001**, *285* (3), 58-64.

- 5. Cui, Y.; Zhong, Z.; Wang, D.; Wang, W. U.; Lieber, C. M., High performance silicon nanowire field effect transistors. *Nano letters* **2003**, *3* (2), 149-152.

- 6. Wang, D.; Wang, Q.; Javey, A.; Tu, R.; Dai, H.; Kim, H.; McIntyre, P. C.; Krishnamohan, T.; Saraswat, K. C., Germanium nanowire field-effect transistors with SiO 2 and high-κ HfO 2 gate dielectrics. *Applied Physics Letters* **2003**, *83* (12), 2432-2434.

- 7. Huang, Y.; Duan, X.; Cui, Y.; Lauhon, L. J.; Kim, K.-H.; Lieber, C. M., Logic gates and computation from assembled nanowire building blocks. *Science* **2001**, *294* (5545), 1313-1317.

- 8. Cui, Y.; Wei, Q.; Park, H.; Lieber, C. M., Nanowire nanosensors for highly sensitive and selective detection of biological and chemical species. *Science* **2001**, *293* (5533), 1289-1292.

- 9. Hrachowina, L.; Domènech-Gil, G.; Pardo, A.; Seifner, M. S.; Gràcia, I.; Cané, C.; Romano-Rodríguez, A.; Barth, S., Site-Specific Growth and in Situ Integration of Different Nanowire Material Networks on a Single Chip: Toward a Nanowire-Based Electronic Nose for Gas Detection. *ACS sensors* **2018**, *3* (3), 727-734.

- 10. Yun, J.; Park, Y.; Kim, J.; Lee, H.; Anderson, W.; Park, J., Nanoscale Res. Lett. 6, 287 (2011).

- 11. Greytak, A. B.; Lauhon, L. J.; Gudiksen, M. S.; Lieber, C. M., Growth and transport properties of complementary germanium nanowire field-effect transistors. *Applied Physics Letters* **2004**, *84* (21), 4176-4178.

- 12. Stern, E.; Cheng, G.; Young, M.; Reed, M., Specific contact resistivity of nanowire devices. *Applied physics letters* **2006**, *88* (5), 053106.

- 13. Zhang, D.-L.; Cheng, B.-W.; Xue, C.-L.; Zhang, X.; Cong, H.; Liu, Z.; Zhang, G.-Z.; Wang, Q.-M., Theoretical study of the optical gain characteristics of a Ge1- xSnx alloy for a short-wave infrared laser. *Chinese Physics B* **2015**, *24* (2), 024211.

- 14. Fujisawa, T.; Saitoh, K., Material gain analysis of GeSn/SiGeSn quantum wells for mid-infrared Si-based light sources based on many-body theory. *IEEE journal of quantum electronics* **2015**, *51* (5), 1-8.

- 15. Gupta, S.; Vincent, B.; Yang, B.; Lin, D.; Gencarelli, F.; Lin, J.-Y.; Chen, R.; Richard, O.; Bender, H.; Magyari-Köpe, B. In *Towards high mobility GeSn channel nMOSFETs: Improved surface passivation using novel ozone oxidation method*, 2012 International Electron Devices Meeting, IEEE: 2012; pp 16.2. 1-16.2. 4.

- 16. Wirths, S.; Geiger, R.; von den Driesch, N.; Mussler, G.; Stoica, T.; Mantl, S.; Ikonic, Z.; Luysberg, M.; Chiussi, S.; Hartmann, J.-M., Lasing in direct-bandgap GeSn alloy grown on Si. *Nature photonics* **2015**, *9* (2), 88.

- 17. von den Driesch, N.; Stange, D.; Rainko, D.; Povstugar, I.; Zaumseil, P.; Capellini, G.; Schröder, T.; Denneulin, T.; Ikonic, Z.; Hartmann, J. M., Advanced GeSn/SiGeSn Group IV Heterostructure Lasers. *Advanced Science* **2018**, *5* (6), 1700955.

- 18. Conley, B. R.; Margetis, J.; Du, W.; Tran, H.; Mosleh, A.; Ghetmiri, S. A.; Tolle, J.; Sun, G.; Soref, R.; Li, B., Si based GeSn photoconductors with a 1.63 A/W peak responsivity and a 2.4 μ m long-wavelength cutoff. *Applied Physics Letters* **2014**, *105* (22), 221117.

- 19. Wang, W.; Lei, D.; Huang, Y.-C.; Lee, K. H.; Loke, W.-K.; Dong, Y.; Xu, S.; Tan, C. S.; Wang, H.; Yoon, S.-F., High-performance GeSn photodetector and fin field-effect transistor (FinFET) on an advanced GeSn-on-insulator platform. *Optics express* **2018**, *26* (8), 10305-10314.

- 20. Lei, D.; Lee, K. H.; Bao, S.; Wang, W.; Masudy-Panah, S.; Yadav, S.; Kumar, A.; Dong, Y.; Kang, Y.; Xu, S. In *The first GeSn FinFET on a novel GeSnOI substrate achieving lowest S of 79 mV/decade and record high Gm, int of 807 μS/μm for GeSn P-FETs*, 2017 Symposium on VLSI Technology, IEEE: 2017; pp T198-T199.

- 21. Liu, T.-H.; Chiu, P.-Y.; Chuang, Y.; Liu, C.-Y.; Shen, C.-H.; Luo, G.-L.; Li, J.-Y., High-Mobility GeSn n-Channel MOSFETs by Low-Temperature Chemical Vapor Deposition and Microwave Annealing. *IEEE Electron Device Letters* **2018**, *39* (4), 468-471.

- 22. Assali, S.; Dijkstra, A.; Li, A.; Koelling, S.; Verheijen, M.; Gagliano, L.; Von Den Driesch, N.; Buca, D.; Koenraad, P.; Haverkort, J., Growth and optical properties of direct band gap Ge/Ge0. 87Sn0. 13 core/shell nanowire arrays. *Nano letters* **2017**, *17* (3), 1538-1544.

- 23. Doherty, J.; Biswas, S.; McNulty, D.; Downing, C.; Raha, S.; O'Regan, C.; Singha, A.; O'Dwyer, C.; Holmes, J. D., One-Step Fabrication of GeSn Branched Nanowires. *Chemistry of Materials* **2019**.

- 24. Biswas, S.; Doherty, J.; Saladukha, D.; Ramasse, Q.; Majumdar, D.; Upmanyu, M.; Singha, A.; Ochalski, T.; Morris, M. A.; Holmes, J. D., Non-equilibrium induction of tin in germanium: towards direct bandgap Ge 1– x Sn x nanowires. *Nature communications* **2016**, *7*, 11405.

- 25. Biswas, S.; Barth, S.; Holmes, J. D., Inducing imperfections in germanium nanowires. *Nano Research* **2017**, *10* (5), 1510-1523.

- 26. Seifner, M. S.; Biegger, F.; Lugstein, A.; Bernardi, J.; Barth, S., Microwave-Assisted Ge1–x Sn x Nanowire Synthesis: Precursor Species and Growth Regimes. *Chemistry of Materials* **2015**, *27* (17), 6125-6130.

- 27. Barth, S.; Seifner, M. S.; Bernardi, J., Microwave-assisted solution—liquid—solid growth of Ge 1– x Sn x nanowires with high tin content. *Chemical Communications* **2015**, *51* (61), 12282-12285.

- 28. Eales, T. D.; Marko, I. P.; Schulz, S.; O'Halloran, E.; Ghetmiri, S.; Du, W.; Zhou, Y.; Yu, S.-Q.; Margetis, J.; Tolle, J., Ge 1-x Sn x alloys: Consequences of band mixing effects for the evolution of the band gap  $\Gamma$ -character with Sn concentration. *Scientific reports* **2019**, 9 (1), 1-10.

- 29. O'Halloran, E. J.; Broderick, C. A.; Tanner, D. S.; Schulz, S.; O'Reilly, E. P., Comparison of first principles and semi-empirical models of the structural and electronic properties of Ge1-xSnx alloys. *Optical and Quantum Electronics* **2019**, *51* (9), 314.

- 30. Broderick, C. A.; Dunne, M. D.; Tanner, D. S.; Kirwanv, A. C.; O'Halloranl, E. J.; Schulz, S.; O'Reilly, E. P. In *Atomistic analysis of localisation and band mixing effects in Gel-xSnx group-IV alloys*, 2018 IEEE 18th International Conference on Nanotechnology (IEEE-NANO), IEEE: 2018; pp 1-4.

- 31. Broderick, C. A.; O'Halloran, E. J.; O'Reilly, E. P. In *Comparative analysis of electronic structure evolution in Ge 1-x Sn x and Ge 1- x Pb x alloys*, 2019 International Conference on Numerical Simulation of Optoelectronic Devices (NUSOD), IEEE: 2019; pp 117-118.

- 32. Sant, S.; Schenk, A., Band-offset engineering for GeSn-SiGeSn hetero tunnel FETs and the role of strain. *IEEE Journal of the Electron Devices Society* **2015**, *3* (3), 164-175.

- 33. Sant, S.; Schenk, A., Pseudopotential calculations of strained-GeSn/SiGeSn heterostructures. *Applied Physics Letters* **2014**, *105* (16), 162101.

- 34. Sant, S.; Lodha, S.; Ganguly, U.; Mahapatra, S.; Heinz, F. O.; Smith, L.; Moroz, V.; Ganguly, S., Band gap bowing and band offsets in relaxed and strained Si1– xGex alloys by employing a new nonlinear interpolation scheme. *Journal of Applied Physics* **2013**, *113* (3), 033708.

- 35. Sistani, M.; Seifner, M.; Bartmann, M.; Smoliner, J.; Lugstein, A.; Barth, S., Electrical characterization and examination of temperature-induced degradation of metastable Ge 0.81 Sn 0.19 nanowires. *Nanoscale* **2018**, *10* (41), 19443-19449.

- 36. Huang, Y.-S.; Lu, F.-L.; Tsou, Y.-J.; Ye, H.-Y.; Lin, S.-Y.; Huang, W.-H.; Liu, C., Vertically Stacked Strained 3-GeSn-Nanosheet pGAAFETs on Si Using GeSn/Ge CVD Epitaxial Growth and the Optimum Selective Channel Release Process. *IEEE Electron Device Letters* **2018**, *39* (9), 1274-1277.

- 37. Lei, D.; Lee, K. H.; Huang, Y.-C.; Wang, W.; Masudy-Panah, S.; Yadav, S.; Kumar, A.; Dong, Y.; Kang, Y.; Xu, S., Germanium-Tin (GeSn) P-Channel Fin Field-Effect Transistor Fabricated on a Novel GeSn-on-Insulator Substrate. *IEEE Transactions on Electron Devices* **2018**, *65* (9), 3754-3761.

- 38. Doherty, J.; Biswas, S.; Saladukha, D.; Ramasse, Q.; Bhattacharya, T. S.; Singha, A.; Ochalski, T. J.; Holmes, J. D., Influence of growth kinetics on Sn incorporation in direct band gap Ge 1– x Sn x nanowires. *Journal of Materials Chemistry C* **2018**, *6* (32), 8738-8750.

- 39. Bardeen, J.; Coovert, R.; Morrison, S.; Schrieffer, J.; Sun, R., Surface conductance and the field effect on germanium. *Physical Review* **1956**, *104* (1), 47.

- 40. Romano, L.; Impellizzeri, G.; Grimaldi, M., p-type conduction in ion-implanted amorphized Ge. *Materials Science in Semiconductor Processing* **2012**, *15* (6), 703-706.

- 41. Schroder, D. K., *Semiconductor material and device characterization*. John Wiley & Sons: 2015.

- 42. Ghibaudo, G., New method for the extraction of MOSFET parameters. *Electronics Letters* **1988**, *24* (9), 543-545.

- 43. Joo, M.-K.; Huh, J.; Mouis, M.; Park, S. J.; Jeon, D.-Y.; Jang, D.; Lee, J.-H.; Kim, G.-T.; Ghibaudo, G., Channel access resistance effects on charge carrier mobility and low-frequency noise in a polymethyl methacrylate passivated SnO2 nanowire field-effect transistors. *Applied Physics Letters* **2013**, *102* (5), 053114.

- 44. Gupta, S. Germanium-tin (GeSn) technology. Stanford University, 2013.

- 45. Han, G.; Su, S.; Zhan, C.; Zhou, Q.; Yang, Y.; Wang, L.; Guo, P.; Wei, W.; Wong, C. P.; Shen, Z. X. In *High-mobility germanium-tin (GeSn) p-channel MOSFETs featuring metallic source/drain and sub-370 C process modules*, 2011 International Electron Devices Meeting, IEEE: 2011; pp 16.7. 1-16.7. 3.

- 46. Gong, X.; Han, G.; Bai, F.; Su, S.; Guo, P.; Yang, Y.; Cheng, R.; Zhang, D.; Zhang, G.; Xue, C., Germanium—Tin (GeSn) p-Channel MOSFETs Fabricated on (100) and (111) Surface Orientations With Sub-400\$^{\circ}\hbox {C}\\hbox {Si} \_ {2}\\hbox {H} \_ {6} \$ Passivation. *IEEE Electron Device Letters* **2013**, *34* (3), 339-341.

- 47. Liu, Y.; Yan, J.; Wang, H.; Cheng, B.; Han, G., Strained germanium—tin (GeSn) P-Channel metal-oxide-semiconductor field-effect transistors featuring high effective hole mobility. *International Journal of Thermophysics* **2015**, *36* (5-6), 980-986.

- 48. Chou, C.-P.; Lin, Y.-X.; Hsieh, K.-Y.; Wu, Y.-H., Poly-GeSn junctionless P-TFTs featuring a record high I ON/I OFF ratio and hole mobility by defect engineering. *Journal of Materials Chemistry C* **2019**, *7* (17), 5201-5208.

- 49. Chou, C.-P.; Lin, Y.-X.; Wu, Y.-H., Implementing P-Channel Junctionless Thin-Film Transistor on Poly-Ge 0.95 Sn 0.05 Film Formed by Amorphous GeSn Deposition and Annealing. *IEEE Electron Device Letters* **2018**, *39* (8), 1187-1190.

- 50. Zhang, L.; Hong, H.; Yu, C.; Li, C.; Chen, S.; Huang, W.; Wang, J.; Wang, H., Poly-GeSn Junctionless Thin Film Transistors on Insulators Fabricated at Low Temperature via Pulsed Laser Annealing. *physica status solidi (RRL)–Rapid Research Letters* **2019**.

- 51. Hara, A.; Nishimura, Y.; Ohsawa, H., Self-aligned metal double-gate junctionless p-channel low-temperature polycrystalline-germanium thin-film transistor with thin germanium film on glass substrate. *Japanese Journal of Applied Physics* **2016**, *56* (3S), 03BB01.

- 52. Oka, H.; Amamoto, T.; Koyama, M.; Imai, Y.; Kimura, S.; Hosoi, T.; Shimura, T.; Watanabe, H., Fabrication of tensile-strained single-crystalline GeSn on transparent substrate by nucleation-controlled liquid-phase crystallization. *Applied Physics Letters* **2017**, *110* (3), 032104.

- 53. Liu, Z.; Wen, J.; Zhang, X.; Li, C.; Xue, C.; Zuo, Y.; Cheng, B.; Wang, Q., High hole mobility GeSn on insulator formed by self-organized seeding lateral growth. *Journal of Physics D: Applied Physics* **2015**, *48* (44), 445103.

- 54. Kurosawa, M.; Kamata, Y.; Ikenoue, H.; Taoka, N.; Nakatsuka, O.; Tezuka, T.; Zaima, S. In Sub-300° C fabrication of poly-GeSn junctionless tri-gate p-FETs enabling sequential 3D integration of CMOS circuits, Proc. SSDM, 2014; pp 684-685.

- 55. Hanrath, T.; Korgel, B. A., Influence of surface states on electron transport through intrinsic Ge nanowires. *The Journal of Physical Chemistry B* **2005**, *109* (12), 5518-5524.

- 56. Zhao, Y.; Candebat, D.; Delker, C.; Zi, Y.; Janes, D.; Appenzeller, J.; Yang, C., Understanding the impact of Schottky barriers on the performance of narrow bandgap nanowire field effect transistors. *Nano letters* **2012**, *12* (10), 5331-5336.