| Title                          | Analysis of effective mobility and hall effect mobility in high-k<br>based In0.75Ga0.25As metal-oxide-semiconductor high-electron-<br>mobility transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                        | Negara, Muhammad A.;Veksler, D.;Huang, J.;Ghibaudo, G.;Hurley,<br>Paul K.;Bersuker, G.;Goel, N.;Kirsch, P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Publication date               | 2011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Original Citation              | Negara, M. A., Veksler, D., Huang, J., Ghibaudo, G., Hurley,<br>P. K., Bersuker, G., Goel, N. and Kirsch, P. (2011) 'Analysis<br>of effective mobility and hall effect mobility in high-k based<br>In0.75Ga0.25As metal-oxide-semiconductor high-electron-<br>mobility transistors', Applied Physics Letters, 99(23), pp. 232101.<br>doi: 10.1063/1.3665033                                                                                                                                                                                                                                                                     |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Link to publisher's<br>version | http://aip.scitation.org/doi/abs/10.1063/1.3665033 -<br>10.1063/1.3665033                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Rights                         | © 2011 American Institute of Physics.This article may be<br>downloaded for personal use only. Any other use requires prior<br>permission of the author and AIP Publishing. The following article<br>appeared in Negara, M. A., Veksler, D., Huang, J., Ghibaudo,<br>G., Hurley, P. K., Bersuker, G., Goel, N. and Kirsch, P. (2011)<br>'Analysis of effective mobility and hall effect mobility in high-<br>k based In0.75Ga0.25As metal-oxide-semiconductor high-<br>electron-mobility transistors', Applied Physics Letters, 99(23),<br>pp. 232101 and may be found at http://aip.scitation.org/doi/<br>abs/10.1063/1.3665033 |

| Download date                  | 2024-05-13 16:31:33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Item downloaded<br>from        | https://hdl.handle.net/10468/4309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

## Analysis of effective mobility and hall effect mobility in high-k based In<sub>0.75</sub>Ga<sub>0.25</sub>As metal-oxide-semiconductor high-electron-mobility transistors

M. A. Negara', D. Veksler, J. Huang, G. Ghibaudo, P. K. Hurley, G. Bersuker, N. Goel, and P. Kirsch

Citation: Appl. Phys. Lett. **99**, 232101 (2011); doi: 10.1063/1.3665033 View online: http://dx.doi.org/10.1063/1.3665033 View Table of Contents: http://aip.scitation.org/toc/apl/99/23 Published by the American Institute of Physics

## Analysis of effective mobility and hall effect mobility in high-*k* based In<sub>0.75</sub>Ga<sub>0.25</sub>As metal-oxide-semiconductor high-electron-mobility transistors

M. A. Negara,<sup>1,2,3,a)</sup> D. Veksler,<sup>1</sup> J. Huang,<sup>1</sup> G. Ghibaudo,<sup>2</sup> P. K. Hurley,<sup>3</sup> G. Bersuker,<sup>1</sup> N. Goel,<sup>1</sup> and P. Kirsch<sup>1</sup>

<sup>1</sup>SEMATECH, 257 Fuller Road, Albany, New York 12203 and 2706 Montopolis Drive, Austin,

Texas 78741, USA

<sup>2</sup>*IMEP*, *ENSERG*, *BP* 257, 38016 Grenoble, France

<sup>3</sup>Tyndall National Institute, University College Cork, Lee Maltings, Cork, Ireland

(Received 13 July 2011; accepted 9 November 2011; published online 5 December 2011)

We report an In<sub>0.75</sub>Ga<sub>0.25</sub>As metal-oxide-semiconductor high-electron-mobility transistor with a peak Hall mobility of 8300 cm<sup>2</sup>/Vs at a carrier density of  $2 \times 10^{12}$  cm<sup>-2</sup>. Comparison of split capacitance-voltage (CV) and Hall Effect measurements for the extracted electron mobility have shown that the split-CV can lead to an overestimation of the channel carrier concentration and a corresponding underestimation of electron mobility. An analysis of the electron density dependence versus gate voltage allows quantifying the inaccuracy of the split-CV technique. Finally, the analysis supported by multi-channel conduction simulations indicates presence of carriers spill over into the top InP barrier layer at high gate voltages. © 2011 American Institute of Physics. [doi:10.1063/1.3665033]

In recent years, significant research efforts have focused on exploring the use of high mobility materials such as III-V, Ge, and graphene as replacements for Si channels in future complementary metal-oxide-semiconductor (CMOS) technology nodes. In the case of III-V channel materials there has been a growing interest in quantum well fieldeffect transistors (QW-FETs) or metal-oxide-semiconductor high-electron-mobility transistors (MOSHEMTs) due to the high intrinsic electron mobility of III-V materials.<sup>1–5</sup> The use of In<sub>0.7</sub>Ga<sub>0.3</sub>As MOSFETs with an Al<sub>2</sub>O<sub>3</sub> gate oxide and InP/In<sub>0.52</sub>Al<sub>0.48</sub>As double-barrier layer structures have been reported with a peak channel mobility of 4729 cm<sup>2</sup>/Vs at a density of  $1.5 \times 10^{12} \,\mathrm{cm}^{-2}$  and capacitance equivalent thickness (CET)  $\sim 3 \text{ nm.}^1$  High-k InGaAs MOSFETs employing a flat band architecture, with a GaAs/AlGaAs barrier layer and bottom Si- $\delta$  doping, exhibited a peak mobility reaching 5500 cm<sup>2</sup>/Vs, at density of  $2-3 \times 10^{12}$  cm<sup>-2</sup> for a CET around 5 nm.<sup>2</sup> The electron mobilities reported were extracted using the split capacitance-voltage (CV) technique,<sup>6</sup> which assumes that the integral of the gate-to-channel capacitance (Cgc) yields the charge density contributing to conduction. However, for device structures that exhibit high interface state densities  $(D_{it})$ , the interface states can affect the calculated mobility,<sup>7</sup> which must be taken into account when using the split CV method. When the energies of interface defects in the high-k/InGaAs system align with the InGaAs conduction band, the evaluation of true effective mobility  $(\mu_{eff})$  from the split CV is further complicated.<sup>8,9</sup> As the Hall voltage is developed by mobile charges only, the Hall Effect technique can yield values for the conduction charge density and the carrier mobility that are *not* impacted by the interface states/defects. This study applied both techniques to extract and compare the carrier density and mobility values determined using the split CV method and the gated Hall bar approach for InGaAs MOSHEMT devices.

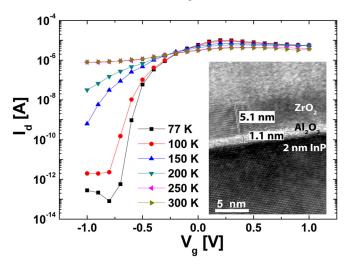

Lattice-matched buffer layers of InAlAs were grown on a semi-insulating InP substrate using molecular beam epitaxy. The channel was 10 nm In<sub>0.75</sub>Ga<sub>0.25</sub>As. Carriers in the channel were separated from the dopants to reduce Coulomb scattering due to ionized impurities. This was achieved by placing a  $3 \times 10^{12} \text{ cm}^{-2}$  silicon delta-doped layer into the lower InAlAs barrier and by introducing an undoped spacer layer between the delta-doped layer and the channel. The channel was then buried using a 2 nm thin undoped large band gap InP barrier layer and thick n<sup>+</sup> InGaAs capping layer. After growth, an active region was patterned, the n<sup>+</sup> capping layer was etched out in the active region, and 1 nm  $Al_2O_3/5$  nm ZrO<sub>2</sub>/TiN films were deposited by atomic layer deposition (ALD). The use of  $Al_2O_3/high-k$  bilayers has been shown to reduce gate leakage and interface defect density in In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS systems.<sup>10</sup> A high resolution cross-sectional transmission electron microscopy (HRTEM) image through the gate stack region of the high-kIn<sub>0.75</sub>Ga<sub>0.25</sub>As MOSHEMT is shown in the inset to Fig. 1. The n<sup>+</sup> InGaAs cap remained in the source-drain junctions, and a metal was used for making ohmic contacts. After device lithography, Hall bar-type MOSHEMTs with a gate length (L) = 170  $\mu$ m and width (W) = 20  $\mu$ m were used for electrical measurements. A long channel device was chosen to minimize the effect of series resistance.

Fig. 1 shows the temperature dependence of the MOSH-EMT transfer characteristics at a drain voltage  $(V_{ds}) = 50 \text{ mV}$  over a range of temperatures (77 K to 300 K). The gate leakage current was found to be less than  $3 \times 10^{-9}$ A at a gate voltage  $(V_g) = 1 \text{ V}$ , which is negligible compared to the drain current (I<sub>d</sub>). The drain current for  $V_g > 0$  is reduced at higher temperatures, and the influence of temperature on the drain current tends to diminish as the gate voltage increases. This effect could be associated with the carriers spilling over into the InP barrier layer, which is more effective at elevated temperatures, and preventing the channel carrier concentration from increasing at higher gate voltages. Such population of the barrier layer may result in

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: adi.negara@tyndall.ie.

the formation of a parallel channel, and is considered later in this letter.

The off-current ( $I_{off}$ ) is significantly reduced at lower temperatures, whereas  $I_{gate}$  is much less than  $I_{off}$  at all temperatures. At  $V_g = -1$  V, the activation energy of ~0.14 eV was extracted, similar to that reported for trap assisted tunneling (TAT) in an InP film,<sup>11</sup> suggesting a defect-related conduction through the InP barrier layer may be the source of the high  $I_{off}$ current. From the high resolution TEM inset in Figure 1, no interfacial layer between the Al<sub>2</sub>O<sub>3</sub> and III-V substrate or between TiN and ZrO<sub>2</sub> was observed within the resolution limits. However,  $D_{it}$  in the lower band gap region is on the order of  $10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup> (not shown), which degrades the subthreshold slope (SS) and could also contribute to the  $I_{off}$ .

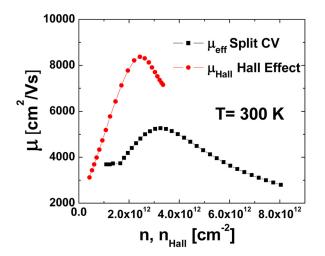

To delineate contributions from gate stack defects and/ or carrier spill over into the barrier layer to electron mobility, the  $\mu_{eff}$  is compared to the Hall mobility ( $\mu_{Hall}$ ) extracted using the Hall Effect measurement at room temperature.<sup>12,13</sup> For the Hall Effect measurements, a magnetic field (B) up to 0.58 T was applied. A linear relationship between V<sub>Hall</sub> and B for various V<sub>g</sub> was observed, and the Hall carrier density (n<sub>Hall</sub>) values were extracted. The  $\mu_{Hall}$  values deduced from the conductance measurements along the channel using the extracted n<sub>Hall</sub> are presented in Fig. 2.

In agreement with previous reports in Refs. 1, 4, and 5, high- $k/In_{0.75}Ga_{0.25}As$  devices with an InP barrier layer exhibit a high peak channel mobility ( $\mu_{eff} \sim 5300 \text{ cm}^2/\text{Vs}$  and  $\mu_{\text{Hall}} \sim 8300 \text{ cm}^2/\text{Vs}$  at room temperature), mainly due to: (1) charge transport occurring primarily at the epitaxial InP/ In<sub>0.75</sub>Ga<sub>0.25</sub>As interface as opposed to an high- $k/In_xGa_{1-x}As$ interface, (2) better interface passivation using a composite high- $k/Al_2O_3$  bilayer structure<sup>10,14</sup> and the use of an undoped InP barrier, and (3) separation of the channel carriers from the scattering centers in the high-k dielectric and/or along the high-k/III-V interface due to the barrier layer (InP) with a large band gap.

The maximum difference between  $\mu_{\text{Hall}}$  and  $\mu_{\text{eff}}$  (as measured by the split CV method) is typically less than 10%-20% for Si MOSFETs,<sup>12</sup> while the measurements on our devices exhibited a much greater difference (~56%).

FIG. 1. (Color online) Typical transfer characteristics of high-k/ In<sub>0.75</sub>Ga<sub>0.25</sub>As MOSHEMTs for L = 170  $\mu$ m and W = 20  $\mu$ m for various temperatures and V<sub>ds</sub> = 50 mV with a TEM image of the gate stack region shown in the inset.

This could be related to a significant capacitance contribution to the measured  $C_{gc}$  from immobile charges when using the split CV technique and/or to the presence of parallel conduction channels in the In<sub>0.75</sub>Ga<sub>0.25</sub>As channel and the InP capping layer. Considering first the case of mobile and immobile charges, the carrier density extracted from the split CV measurements consists of the total charges: in the channel, barrier layers, and charge trapping sites at the high-*k*/InP interface. The split CV method, when employed at room temperature, can lead to an overestimation of the channel carrier density, which, in turn, leads to an underestimation of the extracted electron mobility values.

Considering next the case of parallel transport, at higher gate voltages carriers can spill into the low mobility InP barrier layer, the parallel conduction channels should then be taken into account on the mobility extraction. The difference in the measured  $\mu_{\text{Hall}}$  and  $\mu_{\text{eff}}$  mobilities, described by the Eqs. (1) and (2), respectively, can be understood when multi-channel transport is assumed.<sup>15</sup> With two parallel transport channels (m = 2), the higher mobility layer (an intended channel =  $\mu_1$ ) dominates the Hall mobility due to the  $\mu^2$  dependency in the numerator of Eq. (1). The unintended parallel channel (a conducting layer with relatively lower mobility =  $\mu_2$ ) provides only a small contribution to the total  $\mu_{\text{Hall}}$  compared to  $\mu_{\text{eff}}$ .

$$\mu_{Hall} = \frac{\sum_{i=1}^{m} \mu_i \times \sigma_i}{\sum_{i=1}^{m} \sigma_i}, \text{ for } m = 2 \quad \mu_{Hall} = \frac{n_1 \times \mu_1^2 + n_2 \times \mu_2^2}{n_1 \times \mu_1 + n_2 \times \mu_2}, \quad (1)$$

$$\mu_{eff} = \frac{\sum_{i=1}^{m} \mu_i \times n_i}{\sum_{i=1}^{m} n_i}, \text{ for } m = 2 \quad \mu_{eff} = \frac{n_1 \times \mu_1 + n_2 \times \mu_2}{n_1 + n_2}, \quad (2)$$

$$n_{Hall} = \frac{I_d L}{Wq\mu_{Hall}V_{ds}}, \quad (3)$$

where m = the number of parallel transport channels, n = the number of carriers, and  $\sigma = qn\mu$  represents the conductivity

FIG. 2. (Color online) Comparison of  $\mu_{Hall}$  and  $\mu_{eff}$  (f = 1 MHz) versus the corresponding carrier density (n,  $n_{Hall}$ ) at room temperature for a high-k/In<sub>0.75</sub>Ga<sub>0.25</sub>As MOSHEMT with 2 nm InP top barrier layer, L = 170  $\mu$ m, W = 20  $\mu$ m, V<sub>g</sub> = -1 V to 1 V range, and V<sub>ds</sub> = 50 mV.

inside each device layer,  $I_d = drain$  current, L = device length, W = device width, and  $V_{ds} = drain$  source voltage.

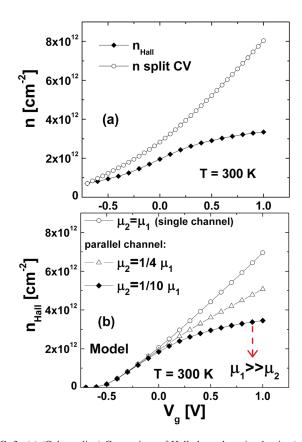

The carrier density extracted by these two methods is shown in Fig. 3(a). For the same  $V_g$ , the maximum channel carrier density obtained from the Hall Effect measurement is ~3.4 × 10<sup>12</sup> cm<sup>-2</sup> compared to 8 × 10<sup>12</sup> cm<sup>-2</sup> obtained using the split CV technique. Earlier, we hypothesized that at higher gate voltages, the channel confinement is lost and that carriers can spill into the low mobility InP barrier layer over the channel region. This suggestion finds support in the n and n<sub>Hall</sub> dependencies on the gate voltage, Fig. 3(a). A plateau in the n<sub>Hall</sub>-V<sub>g</sub> plot observed at higher gate voltages might be caused by screening of the channel when charges spill over into the barrier layer. These charges may form a parallel channel for carrier transport.

When there are trapped charges (m = 3), an additional term of  $n_3$  is added to Eqs. (1) and (2) with a mobility  $\mu_3 = 0$ . From inspection of Eqs. (1) and (2), this has no impact on  $\mu_{hall}$ , due to the product of  $n_3$  and  $u_3$ . However, it will reduce  $\mu_{eff}$  as there is an additional term in the denominator of Eq. (2). The influence of the trapped charges should be detected experimentally as a shift in the electron density versus vs V<sub>g</sub> characteristics obtained from the split CV approach when compared to the electron density obtained from the Hall mobility and Eq. (3). A shift (~0.2 V) is observed experimentally in Fig. 3(a) corresponding to a charge density of  $1.23 \times 10^{12} \text{ cm}^{-2}$ . This alone is not sufficient to explain the difference in the electron density

FIG. 3. (a) (Color online) Comparison of Hall channel carrier density ( $n_{Hall}$ ) and split CV carrier density (n) at room temperature in a high- $k/In_{0.75}Ga_{0.25}As$  MOSHEMT with L = 170  $\mu$ m and W = 20  $\mu$ m and V<sub>ds</sub> = 50 mV (b) Simulated  $n_{Hall}$  with a constant InP/In<sub>0.75</sub>Ga<sub>0.25</sub>As barrier offset = 0.2 eV for three cases of  $\mu_2 = \mu_1 = 7000$  cm<sup>2</sup>/Vs (comparable to single channel),  $\mu_2 = 1/4 \mu_1$  and  $\mu_2 = 1/10 \mu_1$  in bilayer semiconductors (see Ref. 15).

from split CV  $(3.4 \times 10^{12} \text{ cm}^{-2})$  and from the Hall measurements  $(8.0 \times 10^{12} \text{ cm}^{-2})$ .

Eqs. (1)–(3) and Fig. 3(b) illustrate the  $n_{Hall}$  vs.  $V_g$  characteristics solved using classical Poisson equation with a constant InP/In<sub>0.75</sub>Ga<sub>0.25</sub>As barrier offset = 0.2 eV for three cases of  $\mu_2 = \mu_1 = 7000 \text{ cm}^2/\text{Vs}$  (comparable to single channel),  $\mu_2 = 1/4 \mu_1$  and  $\mu_2 = 1/10 \mu_1$  in bilayer semiconductors.<sup>15</sup> The  $n_{Hall}$  characteristics in Fig. 3(a) compared to the simulations in Fig. 3(b) suggest carrier spill over into the InP barrier does occurs in the devices for  $V_g > 0$  and that the total measured  $n_{Hall}$  is dominated by the high mobility channel with  $\mu_1 \gg \mu_2$ .

Comparison of electron density and mobility obtained from the gated Hall effect measurements versus split-CV indicates that the split CV method results in significant (by a factor of x2) overestimation of the channel carrier concentration and a corresponding underestimation of the electron mobility. Gated channel devices designed for Hall Effect measurements allow for more confident extraction of the electron density and mobility. It was also confirmed that the real space transfer of charge carriers from the channel into the top barrier takes place at  $V_g > 0 V$  (Figs. 3(a) and 3(b)). However, even with parallel conduction channels, the average Hall effect mobility is still dominated by the high mobility channel. The spill over may be suppressed by choosing the barrier layers with the higher band offset. These findings should be considered in the design of the III-V quantum well structure and the gate stack.

This work is supported by the Irish Research Council for Science, Engineering and Technology (IRCSET)-Marie Curie International Mobility Fellowship in Science, Engineering and Technology, and Science Foundation Ireland under Grant No. 08/US/I1546.

- <sup>1</sup>H. Zhao, Y. T. Chen, J. H. Yum, Y. Wang, F. Zhou, F. Xue, and J. C. Lee, Appl. Phys. Lett. **96**, 102101 (2010).

- <sup>2</sup>M. Passlack, P. Zurcher, K. Rajagopalan, R. Droopad, J. Abrokwah, M. Tutt, Y. B. Park, E. Johnson, O. Hartin, A. Zlotnicka *et al.*, Tech. Dig. Int. Electron Devices Meet. **2007**, 621.

- <sup>3</sup>S. Bentley, M. Holland, X. Li, G. Paterson, H. Zhou, O. Ignatova, D. Macintyre, S. Thoms, A. Asenov, B. Shin *et al.*, IEEE Electron Device Lett. **32**, 494 (2011).

- <sup>4</sup>H. Zhao, Y. T. Chen, J. H. Yum, Y. Wang, N. Goel, and J. C. Lee, Appl. Phys. Lett. **94**, 193502 (2009).

- <sup>5</sup>M. Radosavljevic, B. Chu-Kung, S. Corcoran, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, W. Rachmady *et al.*, Tech. Dig. - Int. Electron Devices Meet. **2009**, 319.

<sup>6</sup>J. Koomen, Solid-State Electron. **16**, 801 (1973).

- <sup>7</sup>C. L. Hinkle, A. M. Sonnet, R. A. Chapman, and E. M. Vogel, IEEE Electron Device Lett. **30**, 316 (2009).

- <sup>8</sup>G. Brammertz, H. C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, Appl. Phys. Lett. **95**, 202109 (2009).

- <sup>9</sup>E. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb *et al.*, Appl. Phys. Lett. **94**, 102902 (2009).

- <sup>10</sup>A. O'Mahony, S. Monaghan, G. Provenzano, I. M. Povey, M. G. Nolan, E. Oconnor, K. Cherkaoui, S. B. Newcomb, F. Crupi, and P. K. Hurley, Appl. Phys. Lett. **97**, 052904 (2010).

- <sup>11</sup>A. Tosi, A. D. Mora, F. Zappa, and S. Cova, J. Mod. Opt. 56, 299 (2009).

- <sup>12</sup>D. K. Schroder, *Semiconductor Material and Device Characterization* (Wiley, New York, 2006).

- <sup>13</sup>D. Shahrjerdi, J. Nah, B. Hekmatshoar, T. Akyol, M. Ramon, E. Tutuc, and S. K. Banerjee, Appl. Phys. Lett. 97, 213506 (2010).

- <sup>14</sup>H. Zhao, Y. Chen, J. Yum, Y. Wang, and J. C. Lee, in *Proceedings of the 67th IEEE Device Research Conference* (IEEE, New York, 2009), p. 89.

- <sup>15</sup>G. Ghibaudo and G. Kamarinos, Rev. Phys. Appl. 17, 133 (1982).