| Title                          | A combined capacitance-voltage and hard x-ray photoelectron spectroscopy characterisation of metal/Al2O3/In0.53Ga0.47As capacitor structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Authors                        | Lin, Jun;Walsh, Lee A.;Hughes, Gregory;Woicik, Joseph C.;Povey,<br>Ian M.;O'Regan, Terrance P.;Hurley, Paul K.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Publication date               | 2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Original Citation              | Lin, J., Walsh, L., Hughes, G., Woicik, J. C., Povey, I. M., O'Regan,<br>T. P. and Hurley, P. K. (2014) 'A combined capacitance-voltage and<br>hard x-ray photoelectron spectroscopy characterisation of metal/<br>Al2O3/In0.53Ga0.47As capacitor structures', Journal of Applied<br>Physics, 116(2), 024104 (8pp). doi: 10.1063/1.4887517                                                                                                                                                                                                                                                                             |  |  |  |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Link to publisher's<br>version | http://aip.scitation.org/doi/10.1063/1.4887517 - 10.1063/1.4887517                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Rights                         | © 2014 AIP Publishing LLC. This article may be downloaded for<br>personal use only. Any other use requires prior permission of the<br>author and AIP Publishing. The following article appeared in Lin,<br>J., Walsh, L., Hughes, G., Woicik, J. C., Povey, I. M., O'Regan, T.<br>P. and Hurley, P. K. (2014) 'A combined capacitance-voltage and<br>hard x-ray photoelectron spectroscopy characterisation of metal/<br>Al203/In0.53Ga0.47As capacitor structures', Journal of Applied<br>Physics, 116(2), 024104 (8pp). doi: 10.1063/1.4887517 and may be<br>found at http://aip.scitation.org/doi/10.1063/1.4887517 |  |  |  |

| Download date                  | 2024-05-21 01:14:23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Item downloaded<br>from        | https://hdl.handle.net/10468/4717                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

## A combined capacitance-voltage and hard x-ray photoelectron spectroscopy characterisation of metal/Al<sub>2</sub>O<sub>3</sub>/ $In_{0.53}Ga_{0.47}As$ capacitor structures

Jun Lin, Lee Walsh, Greg Hughes, Joseph C. Woicik, Ian M. Povey, Terrance P. O'Regan, and Paul K. Hurley

Citation: Journal of Applied Physics **116**, 024104 (2014); doi: 10.1063/1.4887517 View online: http://dx.doi.org/10.1063/1.4887517 View Table of Contents: http://aip.scitation.org/toc/jap/116/2 Published by the American Institute of Physics

### AIP Journal of Applied Physics

Save your money for your research. It's now FREE to publish with us no page, color or publication charges apply. Publish your research in the Journal of Applied Physics to claim your place in applied physics history.

# A combined capacitance-voltage and hard x-ray photoelectron spectroscopy characterisation of metal/ $Al_2O_3/In_{0.53}Ga_{0.47}As$ capacitor structures

Jun Lin,<sup>1</sup> Lee Walsh,<sup>2</sup> Greg Hughes,<sup>2</sup> Joseph C. Woicik,<sup>3</sup> Ian M. Povey,<sup>1</sup> Terrance P. O'Regan,<sup>4</sup> and Paul K. Hurley<sup>1</sup> <sup>1</sup>*Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland*

<sup>2</sup>School of Physical Sciences, Dublin City University, Glasnevin, Dublin 9, Ireland <sup>3</sup>National Institute of Standards and Technology, Gaithesburg, Maryland 20899, USA

<sup>4</sup>U.S. Army Research Laboratory, Adelphi, Maryland 20899

(Received 19 May 2014; accepted 26 June 2014; published online 10 July 2014)

Capacitance-Voltage (C-V) characterization and hard x-ray photoelectron spectroscopy (HAXPES) measurements have been used to study metal/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As capacitor structures with high (Ni) and low (Al) work function metals. The HAXPES measurements observe a band bending occurring prior to metal deposition, which is attributed to a combination of fixed oxide charges and interface states of donor-type. Following metal deposition, the Fermi level positions at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface move towards the expected direction as observed from HAXPES measurements. The In<sub>0.53</sub>Ga<sub>0.47</sub>As surface Fermi level positions determined from both the C-V analysis at zero gate bias and HAXPES measurements are in reasonable agreement. The results are consistent with the presence of electrically active interface states at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As valence band edge. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4887517]

#### I. INTRODUCTION

The innovation and scaling of complementary metal oxide semiconductor field effect transistors (CMOS) at the heart of integrated circuits has been on-going for the last four decades. The semiconductor and dielectric materials, which constitute the MOS transistors, are now becoming the limit to the further reduction of device dimensions required by future scaling. For instance, the scaling of the conventional Si/SiO<sub>2</sub> metal oxide semiconductor field effect transistor (MOSFET) has effectively come to its limit as any further reductions in the ultra thin SiO<sub>2</sub> layers will result in unacceptably large leakage currents via direct electron tunnelling. High mobility materials (e.g., Ge and III-V compound semiconductors) and high dielectric constant (high-k) gate materials (e.g.,  $HfO_2$ ,  $Al_2O_3$ , and  $ZrO_2$ ) are being intensively investigated as alternative semiconductor channel materials and insulators for future devices with minimum dimensions below 22 nm. The high-k gate materials increase the physical thickness of the oxide while maintaining or increasing the oxide capacitance, thus effectively reducing the leakage current. Meanwhile the use of the high mobility channel materials has the added benefit of a high speed of switching of the MOSFET and reducing the supply voltage while maintaining the same drive current. Therefore, such high-k/high-mobility based MOSFETs are expected to have improved performance/power consumption ratio. To realise this potential for an improved performance/power consumption ratio it is necessary to study the high-k/III-V gate stack from the perspective of electrically active defect states, which include interface states, fixed charges within the highk oxide and border traps near/at the high-k/III-V interface transition layer.<sup>1-3</sup> These defects affect MOSFET performance in a range of detrimental ways,<sup>4,5</sup> and possible methods to remove these defects from high-k/III–V MOS system have been extensively studied.<sup>6–9</sup>

Interface properties are of particular interest due to the relatively high density of electrically active interface defects present at this interface, which restricts efficient III-V surface Fermi level movement. One of the main issues associated with the accurate extraction of interface state concentrations (interface state density distribution as a function of energy in the III-V bandgap, i.e., D<sub>it</sub>(E)) for the high-k/III-V MOS system is the question of how each gate voltage  $(V_g)$  is related to the corresponding surface Fermi level position (E<sub>f</sub>) relative to the valence band edge  $(E_v)$ . For a  $D_{it}(E)$ , which changes density exponentially with  $E_f-E_v$ , this is clearly a potential source of error and variation between research groups. Moreover, the relationship of  $E_{f}$ - $E_{v}$  to  $V_{g}$  is further complicated in the case of high D<sub>it</sub> and for MOS systems where the semiconductor has a low conduction band density of states, such as In<sub>0.53</sub>Ga<sub>0.47</sub>As. This combined effect results in difficulty with the accurate extraction of the oxide capacitance, which is required when relating  $V_{\sigma}$  to a corresponding  $E_{f}-E_{v}$ .

As a traditional method, C-V analysis is widely used to investigate the high-k/III-V electrically active defects.<sup>3,10</sup> In this study, In<sub>x</sub>Ga<sub>1-x</sub>As with a 53% indium concentration, i.e., In<sub>0.53</sub>Ga<sub>0.47</sub>As, (the term "InGaAs" is used to represent In<sub>0.53</sub>Ga<sub>0.47</sub>As in the following discussion) was chosen as the channel material due to the fact that it has a high electron mobility (14 000 cm<sup>2</sup>/Vs at low doping levels), a suitable bandgap (~0.75 eV) for low voltage applications and the fact that it can be grown lattice matched on InP. The high-k/InGaAs MOS system is known to have a relatively high interface state density (D<sub>it</sub>); however, the InGaAs surface Fermi level is generally not fully pinned as compared to the high-*k*/GaAs MOS system, where the movement of GaAs surface Fermi level is strongly restricted.<sup>11,12</sup>

In this paper, C-V analysis was performed on MOS capacitors fabricated using both high (Ni 5.01 eV) and low (Al 4.08 eV) work function metal gates on atomic layer deposition (ALD) Al<sub>2</sub>O<sub>3</sub> on InGaAs.<sup>13</sup> On the premise that a true high frequency C-V can be obtained, the surface potential is determined and so is the Fermi level position at the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface. Hard x-ray photoelectron spectroscopy (HAXPES) measurements on the same MOS structures with a much thinner metal gate have also been performed. HAXPES is emerging as a technique that has the capability of providing chemical and electronic information on much larger depth scales than conventional x-ray photoelectron spectroscopy.<sup>12,14–16</sup> The main objective of this study is to compare the surface Fermi level positions (at room temperature) analysed by C-V characteristics at zero gate bias  $(V_g = 0 V)$  and HAXPES measurements without applying a gate bias, and furthermore, to investigate the Fermi level movement at the Al2O3/InGaAs interface and the change in potential drop across the dielectric layer, resulting from the deposition of metals with different work functions. It has recently been shown that good agreement can be obtained for  $E_f-E_v$  at  $V_g = 0V$  in the SiO<sub>2</sub>/Si MOS system<sup>16</sup> and strongly pinned case of the Al<sub>2</sub>O<sub>3</sub>/GaAs<sup>12</sup> MOS using a similar C-V and HAXPES comparative study. The aim of this work is to extend on the studies reported in Refs. 12 and 16 to the case of the Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS system. These studies provide more certainty on D<sub>it</sub>(E) extractions and also bridge the gap between interface chemistry and electrical properties at a buried interface.

#### **II. EXPERIMENTAL DETAILS**

The samples studied in this work were heavily *n*-doped (S at  $\sim 2 \times 10^{18}$  cm<sup>-3</sup>) and heavily *p*-doped (Zn at  $\sim 2 \times 10^{18}$ cm<sup>-3</sup>) InP(100) substrates with  $2 \,\mu m$  *n*-type (S at  $\sim 4 \times 10^{17}$ cm<sup>-3</sup>) and *p*-type (Zn at  $\sim 4 \times 10^{17}$  cm<sup>-3</sup>) InGaAs epitaxial layers, respectively, grown by metal organic vapour phase epitaxy (MOVPE). The InGaAs surfaces were initially degreased by sequentially rinsing for 1 min each in acetone, methanol, and isopropanol. Prior to the ALD of high-k oxide, the samples were immersed in a (NH<sub>4</sub>)<sub>2</sub>S solution (10% in deionized H<sub>2</sub>O) for 20 min at room temperature ( $\sim$ 295 K), which was found to be the optimum approach to suppress the formation of InGaAs native oxides and to reduce the high-k/ InGaAs interface state density as reported previously.<sup>9</sup> Samples were then introduced to the ALD chamber load lock after the removal from the 10% (NH<sub>4</sub>)<sub>2</sub>S surface passivation solution. The transfer time from the aqueous  $(NH_4)_2S$ solution to the ALD chamber was kept to a minimum ( $\sim 3$ min) in order to minimise the formation of InGaAs native oxides resulting from air exposure. The Al<sub>2</sub>O<sub>3</sub> dielectric layer, which had a nominal thickness of 8 nm, was deposited by ALD at 300 °C using trimethylaluminum (TMA) Al(CH<sub>3</sub>)<sub>3</sub> and H<sub>2</sub>O as precursors.

For C-V analysis, either Al (160 nm) or Ni (70 nm)/Au (90 nm) were used as the metal gate electrodes, which were formed by electron beam evaporation and a lift-off process.

The C-V measurements were recorded using a semiconductor device analyser following an open correction and performed in a probe station in a dry air, dark environment. Multi-frequency (1 kHz–1 MHz) and 1 MHz C-V measurements were carried out at both room temperature and -50 °C. The C-V characteristics measured at both temperatures at 1 MHz were compared in order to rule out the possible contribution of an interface state capacitance to the overall measured capacitance of the MOS capacitors at room temperature. The oxide capacitance and flatband capacitance used for C-V analysis are calculated using a dielectric constant value of 8.6 for Al<sub>2</sub>O<sub>3</sub><sup>17</sup> and accurate oxide thicknesses were obtained from high-resolution cross-sectional transmission electron microscopy (HR-TEM).

For HAXPES analysis, one *n*-type and one *p*-type Al<sub>2</sub>O<sub>3</sub>/InGaAs sample were left without a metal gate. The other HAXPES samples were capped with either Al (5 nm) or Ni (5 nm) blanket films formed by electron beam evaporation. HAXPES measurements were carried out on the X24A beamline at the National Synchrotron Light Source (NSLS) at Brookhaven National laboratory (BNL). A double Si (111) crystal monochromator allowed for photon energy selection in the range of 2.1–5.0 keV. An electron energy analyser was operated at a pass energy of 200 eV giving an overall instrumental energy resolution of  $\sim 0.52 \,\text{eV}$  at the photon energy of 4150 eV. Samples were fixed on a grounded Al sample holder with stainless steel clips, which connected the front of the samples to the sample holder. In order to ensure correct energy calibration throughout the experiment, metallic Ni Fermi edge reference spectra were acquired immediately before and after the acquisition of the Al<sub>2</sub>O<sub>3</sub> and InGaAs substrate core level peaks. The resultant error associated with this photon energy correction procedure is estimated to be no more than  $\pm 50 \text{ meV}$ . The calculated depletion region width for the  $4 \times 10^{17}$  cm<sup>-3</sup> doped InGaAs substrate is 51 nm and the total sampling depth of the HAXPES measurements for the metal capped samples is estimated to be  $\sim 23 \text{ nm}$  at 4150 eV (Ref. 18) for the substrate Ga 2p and As 2p which have kinetic energies of 3033 eV and 2827 eV, respectively.<sup>19</sup> This means that for a 5 nm thick metal capping layer and an 8nm Al<sub>2</sub>O<sub>3</sub> layer, the sampling depth into the InGaAs is  $\sim 10$  nm. Therefore, the acquired peaks directly reflect the binding energy (BE) of the core levels with respect to the Fermi level near the top of the depletion region adjacent to the dielectric interface. All core level peaks were curve fitted in order to increase the accuracy of locating the peak centre positions.

#### **III. RESULTS AND DISCUSSION**

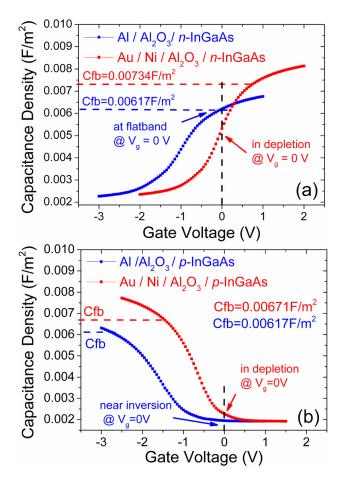

The C-V characteristics at 1 MHz and 295 K for Al (160 nm) or Au (90 nm)/Ni (70 nm) metal gate MOS capacitors are shown in Figures 1(a) and 1(b) for Al<sub>2</sub>O<sub>3</sub>/*n*-InGaAs and Al<sub>2</sub>O<sub>3</sub>/*p*-InGaAs, respectively. If interface states can respond at these measurement conditions, the measured capacitance (C<sub>m</sub>) will have a contribution from interface states (C<sub>it</sub>), which is frequency and temperature dependent, and can be suppressed at a higher frequency and/or lower temperature.<sup>4,5,11</sup> This will especially affect the C-V responses

FIG. 1. C-V responses at 1 MHz and 295 K for Al gate and Au/Ni gate over (a)  $Al_2O_3/n$ -InGaAs and (b)  $Al_2O_3/p$ -InGaAs MOS capacitors.

in terms of frequency dispersion in the accumulation region at different temperatures. Therefore, a significantly lower level of accumulation frequency dispersion and a decrease in the 1 MHz  $C_m$  are expected at a lower temperature when compared to the measurements at room temperature. It is believed that a true high frequency C-V is achieved at 1 MHz and room temperature as the multi-frequency (1 kHz to 1 MHz) and 1 MHz C-V measured at room temperature have very similar characteristics when compared to the C-V measured at -50 °C (not shown) for the Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS capacitors under investigation. Based on this observation we take the 1 MHz room temperature response to be an accurate representation of a high frequency C-V for the InGaAs structures examined in this study.

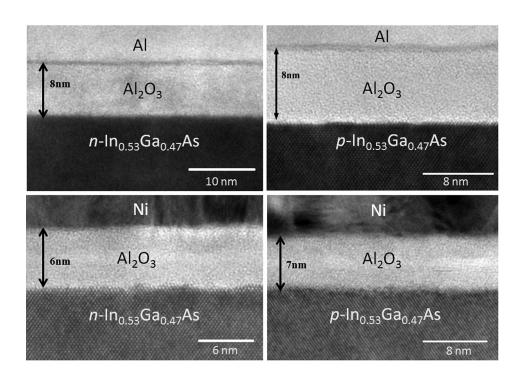

As observed in the TEM images in Figure 2, a thicker Al<sub>2</sub>O<sub>3</sub> film is formed under the Al gate due to a more reactive Al/Al<sub>2</sub>O<sub>3</sub> interface compared to a non-reactive Ni/Al<sub>2</sub>O<sub>3</sub> interface. This is consistent with the lower oxide capacitance and thus the lower measured capacitance in accumulation for the Al gate samples as observed in Figures 1(a) and 1(b). Using the oxide thickness measured by HR-TEM in Figure 2, the oxide capacitance (Cox) is calculated and used to determine the flatband capacitance (C<sub>fb</sub>). Furthermore, the calculated C<sub>fb</sub> can be used to determine the region of operation of the MOS capacitor, and to establish if at  $V_g = 0$  V, the surface Fermi level position can be determined using the depletion capacitance. From the C-V for n-InGaAs in Figure 1(a), the measured capacitance for the Ni gate sample is below the calculated  $C_{fb}$  (~0.00734 F/m<sup>2</sup>) and is thus operating in depletion at  $V_g = 0 V$ . The corresponding InGaAs depletion capacitance (Cs) can be calculated using the measured capacitance  $C_m \; (C_{it} \!=\! 0)$  and an oxide capacitance value of  $1.27 \times 10^{-6}$  F/cm<sup>2</sup>. The C<sub>s</sub> value can be used to calculate the surface Fermi level position with respect to valence band maximum (VBM) energy level and for Ni gate *n*-InGaAs yielding a value of  $\sim 0.71 \text{ eV}$  above VBM. For the Al gate n-InGaAs sample shown in Figure 1(a), the  $C_{\rm m}$  at  $V_{\rm g} = 0 V$  approximately equals the  $C_{\rm fb}$  value  $(\sim 0.00617 \text{ F/m}^2)$ , which indicates that the sample is near the flatband condition and its surface potential is approximately

FIG. 2. Transmission electron microscopy images of the MOS capacitors under investigation. Note that there is no clear evidence of InGaAs native oxides at the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface, which is consistent with the (NH<sub>4</sub>)<sub>2</sub>S treatment prior to the ALD process<sup>9</sup> and the reported "self-cleaning" process of ALD of Al<sub>2</sub>O<sub>3</sub>.<sup>20,30</sup>

zero at  $V_g = 0$  V. Thus the Fermi level position for this sample is ~0.76 eV above the VBM at the flatband condition for Al gate *n*-type InGaAs. From the C-V for Ni gate and Al gate over *p*-InGaAs shown in Figure 1(b), both samples are operating in depletion region at  $V_g = 0$  V. Using the same method of surface Fermi level calculation for Ni gate over *n*-InGaAs (Figure 1(a)), the Fermi level is determined to be ~0.55 eV and ~0.73 eV above VBM with Ni and Al gates, respectively.

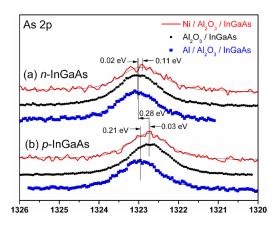

Figure 3 shows the HAXPES As 2p core levels acquired at 4150 eV photon energy for both *n*- and *p*-InGaAs with an Al<sub>2</sub>O<sub>3</sub> dielectric layer with and without the presence of the metal gate. For the unmetallised samples, the binding energy position for the *p*-InGaAs peaks was found to be ~0.28 eV lower than the *n*-InGaAs substrate consistent with the *p*-type sample Fermi level residing closer to the VBM. The difference is however less than the expected difference of 0.68 eV, which is calculated from the difference in Fermi level position for *n*- and *p*-InGaAs for a doping level of  $4 \times 10^{17}$  cm<sup>-3</sup>,<sup>4,5</sup> indicating that there is band bending present at the Al<sub>2</sub>O<sub>3</sub>/ InGaAs interface prior to metal contact.

In order to establish the absolute position of the Fermi level in the band gap with respect to the valence band edge, valence band spectra were acquired at the same photon energy for the unmetallised Al<sub>2</sub>O<sub>3</sub>/n-InGaAs sample. An extrapolation of the InGaAs valence band to a zero signal intensity yields the approximate position of the valence band edge.<sup>20</sup> Although more accurate methods have been recently employed,<sup>12,21</sup> this method is sufficient to provide an accuracy of approximately 0.1 eV in these studies. Reference spectra of the nickel metallic edge were subsequently acquired in order to establish the Fermi level position. The value of E<sub>f</sub>-E<sub>v</sub> is thus determined for the Al<sub>2</sub>O<sub>3</sub>/n-InGaAs sample with no metal gate. On the same sample, the As 2p spectra are recorded. These measurements provide the necessary reference for all the other samples to allow the value of  $E_{f}-E_{v}$  to be evaluated. The energy separation between the core level and the InGaAs valence band maxima is a

FIG. 3. Normalised and fitted As 2p core level spectra acquired at a photon energy of 4150 eV for the uncapped Al<sub>2</sub>O<sub>3</sub>/InGaAs (black), Ni (5 nm) capped (red), and Al (5 nm) capped Al<sub>2</sub>O<sub>3</sub>/InGaAs (blue) samples, showing the shifts in the core level BE after metal for (a) *n*-, and (b) *p*-InGaAs substrates. The energy separation between the *n*- and *p*-InGaAs without metal gates is 0.28 eV. The biggest BE shift occurs in the *p*-InGaAs sample with an Al gate. This is consistent with lower D<sub>it</sub> distribution in the upper bandgap which allows for a more efficient Fermi level movement.

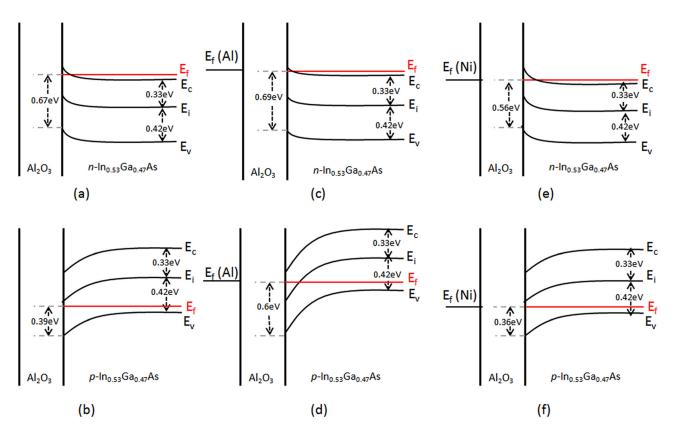

constant; therefore, any changes in the As 2p spectra in Figure 3 are a consequence of changes in  $E_{f}$ - $E_{v}$ . From the valence band spectra of the uncapped  $Al_2O_3/n$ -InGaAs sample (not shown), the Fermi level is 0.67 eV above the VBM and the equivalent measurement for the *p*-type Fermi level position is 0.39 eV above the VBM. Therefore, the Fermi level is  $\sim 0.09 \,\mathrm{eV}$  below flatband position for *n*-InGaAs and is  $\sim 0.31 \text{ eV}$  above flatband position (i.e., near mid-gap) for the p-InGaAs, indicating that the n-InGaAs surface is slightly depleted and the *p*-InGaAs surface is strongly depleted. Figures 4(a) and 4(b) schematically illustrates the band bending occurring for the unmetallised samples and the respective Fermi level positions (E<sub>f</sub>) determined by HAXPES. The depletion of both the n- and p-type surface cannot be explained by one net oxide charge type. Therefore, the band bending occurring at the InGaAs surface in the absence of metal gates is attributed to a combination of fixed charge in the Al<sub>2</sub>O<sub>3</sub> layer and the interface states with energy levels within the InGaAs bandgap, which deplete both the *n*-type and *p*-type surface. Based on the work by Long *et al.*<sup>8</sup> the fixed oxide charge in ALD deposited Al<sub>2</sub>O<sub>3</sub> is comprised of negative interface fixed charge that exists near the Al<sub>2</sub>O<sub>3</sub>/ InGaAs interface and positive fixed charge distributed through the bulk of Al<sub>2</sub>O<sub>3</sub>. For a relatively thin oxide of 8 nm, the net fixed oxide charge (Q<sub>f</sub>) could be negative as discussed in Ref. 8. In addition, Refs. 8, 22, and 23 have reported the evidence that the net interface states type for  $Al_2O_3$  on InGaAs is donor type (+/0). If this is the case, for an *n*-type sample at flatband where the  $E_f$  is close to conduction band edge and the interface state energy levels in the bandgap are occupied, the interface defects (Qit) are neutral. The combination of negatively charged Q<sub>f</sub> and neutral Q<sub>it</sub> is a negative charge, which slightly depletes the *n*-type surface as shown in Figure 4(a). For a *p*-type sample at flatband where  $E_f$  is close to valence band edge, the donor-type interface defects have a net associated positive charge as their energy levels in the bandgap are empty. The positively charged interface states plus the negatively charged Qf can result in the depletion of *p*-type surface as shown in Figure 4(b). Confirming the sign of  $Q_f$  and  $Q_{it}$  requires an  $Al_2O_3$ thickness series as described in Ref. 8, which is beyond the scope of this work.

In order to determine whether the band bending displayed at the interface reflects Fermi level pinning, both high (Ni) and low (Al) work function metals of 5 nm in thickness were deposited on the dielectric. By ensuring electrical contact between the metal overlayer and the InGaAs substrate, Fermi level equalisation across the MOS structure resulting from the differences in work functions occurs. If the Fermi level at the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface is free to move, it would be expected to align with the metal Fermi level, resulting in an increase in BE with the low work function Al contact and a reduction in BE with the high work function Ni contact for both the n- and p-InGaAs. HAXPES measurements in Figure 3 show that, for the *p*-InGaAs sample, the core level peaks shifts by 0.21 eV, and for the n-InGaAs sample, the peaks shifts by 0.02 eV, both to higher BE, following the deposition of Al contact. Following the deposition of Ni contact, the peak positions shift 0.11 eV for *n*-InGaAs and

FIG. 4. Band diagrams of (a) unmetallised Al<sub>2</sub>O<sub>3</sub>/*n*-InGaAs, (b) unmetallised Al<sub>2</sub>O<sub>3</sub>/*p*-InGaAs, (c) Al<sub>2</sub>O<sub>3</sub>/*n*-InGaAs following Al deposition, (d) Al<sub>2</sub>O<sub>3</sub>/*p*-InGaAs following Al deposition, (e) Al<sub>2</sub>O<sub>3</sub>/*n*-InGaAs following Ni deposition, and (f) Al<sub>2</sub>O<sub>3</sub>/*p*-InGaAs following Ni deposition MOS capacitors. The band bending occurring in the absence of a metal contact shown in (a) and (b) is due to a combined effect of fixed oxide charges and interface states.  $E_f$  represents the Fermi level position,  $E_c$  represents the conduction band edge,  $E_v$  represents the valance band edge and  $E_i$  represents the InGaAs midgap energy level. The surface  $E_{\Gamma}E_v$  values shown in this figure are determined from HAXPES.

0.03 eV for *p*-InGaAs to lower BE. It should be noted that the small shifts of 0.02 eV and 0.03 eV, measured for the Al on *n*-InGaAs and Ni on *p*-InGaAs respectively, are within the experimental error ( $\pm 50 \text{ meV}$ ) of this technique; therefore, these shifts are negligible. The directions of all the BE shifts observed in the HAXPES spectra are consistent with the differences in the Fermi level positions for the InGaAs substrates and metals. The changes in InGaAs surface Fermi level when the metal contacts are present can be visualized using the schematic band diagrams and the Fermi levels presented in Figures 4(c)-4(f).

The corresponding Fermi level positions in the InGaAs bandgap following either Al or Ni deposition are calculated from the HAXPES to be 0.69 eV above VBM for the Al gate, and 0.56 eV above VBM for Ni gate, over *n*-InGaAs. Both of these Fermi level positions are in agreement with the C-V measurements at  $V_g = 0$  V shown in Figure 1(a) where the sample is in the near flatband condition for the Al gate and in depletion for the Ni gate. For the HAXPES *p*-InGaAs samples, the Fermi levels are determined to be 0.6 eV above VBM with the Al gate and 0.36 eV above VBM with the Ni gate, which are consistent with the C-V measurements at  $V_g = 0$  V in Figure 1(b) where both the samples are in depletion with the Al gate sample being more depleted (near inversion) than the Ni gate sample.

In the HAXPES measurements, any large degree of band bending at the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface may lead to an error in the surface Fermi level measurement, as HAXPES has a sampling depth into the substrate of  $\sim 10 \,\mathrm{nm}$  so the Fermi level is being measured up to 10 nm below its surface position. In order to assess the magnitude of this error in determining the Fermi level position from the HAXPES measurement, a simulation of the band bending for  $4 \times 10^{17}$  cm<sup>-3</sup> doped *p*-InGaAs resulting from a 0.31 eV surface potential was performed by numerically solving Poisson's equation. The resulting band bending diagram (not shown) indicates that for a sampling depth into the InGaAs substrate of  $\sim 10$  nm, the error in determining the VBM position is a maximum of 0.1 eV. However, due to the exponential fall off in the weighting of the photoemitted electron contribution with depth, the actual error will be less than this value. This error can thus be taken into account when comparing the results of the approximate Fermi level position of each sample in the InGaAs bandgap.

A comparison between the Fermi level positions at the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface derived from C-V analysis at  $V_g = 0$  V and the HAXPES measurements shown in Table I displays a reasonable agreement is achieved between the two techniques. The difference between the Fermi level position of Al and Ni obtained from C-V analysis are also consistent with that determined by HAXPES measurements. The difference between the C-V and HAXPES values for  $E_f-E_v$  are in the range of 0.1–0.2 eV. This is comparable to the results obtained in the case of the GaAs/Al<sub>2</sub>O<sub>3</sub> MOS system,<sup>12</sup> but in the case of the InGaAs, this error represents a larger percentage of the energy gap.

TABLE I. Surface Fermi level positions obtained from C-V analysis at  $V_g = 0 V$  and HAXPES measurements for uncapped, Al gate and Ni gate Al<sub>2</sub>O<sub>3</sub>/InGaAs samples.

| Sample                  | $E_{f}$ - $E_{v}$ (uncapped) | E <sub>f</sub> -E <sub>v</sub> (Al gate) | E <sub>r</sub> -E <sub>v</sub> (Ni gate) | $\Delta E_{f}$ (Al-Ni shift) |

|-------------------------|------------------------------|------------------------------------------|------------------------------------------|------------------------------|

| <i>n</i> -type (C-V)    | N/a                          | 0.76 eV                                  | 0.71 eV                                  | 0.05 eV                      |

| <i>n</i> -type (HAXPES) | $0.57 \rightarrow 0.67eV$    | $0.59 \rightarrow 0.69  eV$              | $0.46 \rightarrow 0.56eV$                | $0.03 \rightarrow 0.23  eV$  |

| <i>p</i> -type (C-V)    | N/a                          | 0.73 eV                                  | 0.55 eV                                  | 0.18 eV                      |

| <i>p</i> -type (HAXPES) | $0.39 \rightarrow 0.49eV$    | $0.6 \to 0.7  eV$                        | $0.36 \rightarrow 0.46eV$                | $0.14 \rightarrow 0.34eV$    |

Further insight into the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface properties can be obtained from the HAXPES measurements in relation to the extent of the Fermi level movements at InGaAs surface when a metal layer is deposited. Following the deposition of the Al gate, the surface Fermi level position of n-InGaAs moves towards the conduction band edge. For the p-InGaAs following Al deposition, the Fermi level moves towards conduction band edge residing slightly below the conduction band minimum. These experimental observations confirm the ability of the Fermi level in the InGaAs bandgap to move towards the conduction band edge attempting to align with the Al Fermi level (see Figure 4). The fact that the surface Fermi level does not move significantly into the low density of states InGaAs conduction band is also consistent with the reported high interface state density located within the InGaAs conduction band where the Fermi level can be strongly pinned at energies above E<sub>c</sub>.<sup>3,24,25</sup> When the Ni gate is in contact, the InGaAs Fermi level movement is more restricted. The inability to move the n-InGaAs Fermi level to the lower bandgap and the slight Fermi level movement of only 0.03 eV towards VBM for the p-InGaAs suggest a peak Dit distribution where the density increases in the lower half of the bandgap, consistent with previous publications.<sup>26-28</sup>

Fermi level alignment between the metal and the InGaAs is achieved by not only the movement of InGaAs Fermi level but also a change in the potential drop across the oxide layer. The change in the oxide potential following

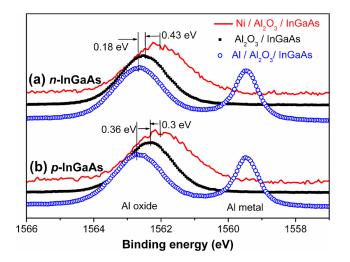

FIG. 5. Al 1s spectra showing BE shift due to the the changes in the potential across the  $Al_2O_3$  layer caused by different work function metals and also the Fermi level movement in the InGaAs for (a) *n*-InGaAs and (b) *p*-InGaAs. The presence of a metallic Al 1s signal at ~1559.5 eV binding energy originates from the metal cap.

metal deposition will result in a binding energy shift of the associated Al 1s dielectric core levels, and the total potential drop across the oxide will result in an energy broadening of the peak.<sup>12,14,16</sup> Note that the shift resulting from Fermi level movement in the bulk InGaAs is also present in the oxide core level, so any shift in the oxide peaks is a combination of the InGaAs Fermi level movement and the change in the potential difference across the oxide. Based on the difference in metal and InGaAs Fermi levels, the change in the Al 1s oxide binding energies would be expected to be more apparent in the *p*-type sample than in the *n*-type sample than in the *n*-type with Al as the metal gate, and more apparent in the *n*-type sample than in the *n*-type with Ni as metal gate.

Figure 5 shows the changes in binding energy of the Al 1s oxide peak (at 1562 eV) for the *n*- and *p*-InGaAs substrate resulting from metal deposition. For *n*-InGaAs, the deposition of the low work function Al only results in a small increase in the Al 1s peak binding energy in the Al<sub>2</sub>O<sub>3</sub> ( $\sim$ 0.18 eV), while for the p-InGaAs the deposition of Al results in a more significant increase in the binding energy ( $\sim 0.36 \,\text{eV}$ ) reflecting the larger Fermi level difference between p-InGaAs and Al gate. For *n*-InGaAs, the deposition of Ni results in a decrease in the Al 1s peak binding energy ( $\sim 0.43 \,\text{eV}$ ), while for the p-InGaAs the deposition of high work function Ni results in a lower decrease in the binding energy ( $\sim 0.3 \,\mathrm{eV}$ ), consistent with the larger Fermi level difference between n-InGaAs and Ni compared to the case of *p*-InGaAs. All of these changes are consistent with the expected shifts and polarity of the band bending in the dielectric layer caused by the low and high work function metals.

The Al 1s peak widths for the metal capped samples broaden when compared to the samples without metal gates reflecting the gradient in the potential across the dielectric layer. The change in the Al 1s binding energy of 0.18 eVmeasured for the Al gate on *n*-type InGaAs sample results in broadening of 0.09 eV (compared to the no metal gate sample) while a full width half maximum (FWHM) increase of 0.62 eV is measured for Ni on *n*-type InGaAs sample. This infers a larger potential drop across the Al<sub>2</sub>O<sub>3</sub> layer for the Ni *n*-type compared to the Al *n*-type samples. In the case of the *p*-type sample, a negligible difference in FWHM was measured for the Al contact, but a 0.46 eV FWHM increase was found for the Ni capped sample, indicating a larger potential drop across the Al<sub>2</sub>O<sub>3</sub> layer for the Ni capped *p*-type sample.

#### **IV. CONCLUSION**

In summary, C-V analysis and HAXPES measurements have been made on metal/Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS capacitors

with both high (Ni) and low (Al) work function metal gates. The HAXPES measurements reveal the presence of band bending prior to metal deposition, resulting from a combination of fixed oxide charges and possible donor-type interface states. Following the deposition of metal, the substrate core level BE shift in the expected directions. A reasonable agreement in Fermi level positions for the InGaAs MOS structures is obtained between C-V analysis and HAXPES measurements at zero gate bias. The results point to a partially pinned Al<sub>2</sub>O<sub>3</sub>/InGaAs interface and suggest a higher interface state density in the lower half of the bandgap. There is a shift in binding energy of the oxide core levels following metal deposition, which is caused by the InGaAs surface Fermi level movement and a change in the potential drop across the Al<sub>2</sub>O<sub>3</sub> layer, and the shifts are in the expected directions. The broadening of the oxide peak widths indicates a higher potential drop across the Al<sub>2</sub>O<sub>3</sub> layer with Ni gate than that with Al gate.

#### ACKNOWLEDGMENTS

The authors from Tyndall National Institute and Dublin City University acknowledge Science Foundation Ireland for financial support of the research work through the INVENT Project (SFI/09/IN.1/I2633). The central fabrication facility at Tyndall is acknowledged for the fabrication of the experimental samples used in this work. Ian Povey from Tyndall is acknowledged for the ALD growth of the Al<sub>2</sub>O<sub>3</sub> layers. Dan O'Connell from Tyndall is acknowledged for the metallisation. Patrick Carolan from Tyndall is acknowledged for the TEM analysis. Access to the X24A HAXPES beamline at Brookhaven National Laboratory was obtained through a General User Proposal. Use of the National Synchrotron Light Source, Brookhaven National Laboratory, was supported by the U.S. Department of Energy, Office of Science, Office of Basic Energy Sciences, under Contract No. DE-AC02-98CH10886.

- <sup>1</sup>B. Shin, J. R. Weber, R. D. Long, P. K. Hurley, C. G. Van de Walle, and P. C. McIntyre, "Origin and passivation of fixed charge in atomic layer deposited aluminum oxide gate insulators on chemically treated InGaAs substrates," Appl. Phys. Lett. **96**, 152908 (2010).

- <sup>2</sup>J. Lin, Y. Y. Gomeniuk, S. Monaghan, I. M. Povey, K. Cherkaoui, É. O'Connor, M. Power, and P. K. Hurley, "An investigation of capacitance-voltage hysteresis in metal/high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor capacitors," J. Appl. Phys. **114**, 144105 (2013).

- <sup>3</sup>G. Brammertz, H. C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, "On the interface state density at In<sub>0.53</sub>Ga<sub>0.47</sub>As/oxide interfaces," Appl. Phys. Lett. **95**, 202109 (2009).

- <sup>4</sup>E. H. Nicollian and J. R. Brews, *MOS Physics and Technology* (Wiley, New York, 2003).

- <sup>5</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices* (Wiley, NJ, 2007).

- <sup>6</sup>É. O'Connor, R. D. Long, K. Cherkaoui, K. K. Thomas, F. Chalvet, I. M. Povey, M. E. Pemble, P. K. Hurley, B. B. Brennan, G. Hughes, and S. Newcomb, "*In situ* H<sub>2</sub>S passivation of  $In_{0.53}Ga_{0.47}As/InP$  metal-oxide-semiconductor capacitors with atomic-layer deposited HfO<sub>2</sub> gate dielectric," Appl. Phys. Lett. **92**, 022902 (2008).

- <sup>7</sup>R. D. Long, É. O'Connor, S. B. Newcomb, S. Monaghan, K. Cherkaoui, P. Casey, G. Hughes, K. K. Thomas, F. Chalvet, I. M. Povey, M. E. Pemble, and P. K. Hurley, "Structural analysis, elemental profiling, and electrical characterization of HfO<sub>2</sub> thin films deposited on In<sub>0.53</sub>Ga<sub>0.47</sub>As surfaces by atomic layer deposition," J. Appl. Phys. **106**, 084508 (2009).

- <sup>8</sup>R. D. Long, B. Shin, S. Monaghan, K. Cherkaoui, J. Cagnon, S. Stemmer, P. C. McIntyre, and P. K. Hurley, "Charged defect quantification in Pt/ Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitors," J. Electrochem. Soc. **158**, G103 (2011).

- <sup>9</sup>É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, "A systematic study of (NH4)<sub>2</sub>S passivation (22%, 10%, 5%, or 1%) on the interface properties of the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP system for n-type and p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial layers," J. Appl. Phys. **109**, 024101 (2011).

- <sup>10</sup>R. Engel-Herbert, Y. Hwang, and S. Stemmer, "Comparison of methods to quantify interface trap densities at dielectric/III–V semiconductor interfaces," J. Appl. Phys. **108**,124101 (2010).

- <sup>11</sup>P. K. Hurley, É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, J. MacHale, A. J. Quinn, and G. Brammertz, "Structural and Electrical Properties of HfO<sub>2</sub>/n-In<sub>x</sub>Ga<sub>1-x</sub>As structures (x: 0, 0.15, 0.3 and 0.53)," Electrochem. Soc. Trans. **25**(6), 113–127 (2009).

- <sup>12</sup>L. A. Walsh, G. Hughes, J. Lin, P. K. Hurley, T. P. O'Regan, E. Cockayne, and J. C. Woicik, "Hard x-ray photoelectron spectroscopy and electrical characterization study of the surface potential in metal/Al<sub>2</sub>O<sub>3</sub>/GaAs(100) metal-oxide-semiconductor structures," Phys. Rev. B 88(4), 045322 (2013).

- <sup>13</sup>D. R. Lide, CRC Handbook of Chemistry and Physics (CRC, Boca Raton, 2007).

- <sup>14</sup>K. Kakushima, K. Okamoto, K. Tachi, J. Song, S. Sato, T. Kawanago, K. Tsutsui, N. Sugii, P. Ahmet, T. Hattori, and H. Iwai, "Observation of band bending of metal/high-k Si capacitor with high energy x-ray photoemission spectroscopy and its application to interface dipole measurement," J. Appl. Phys. **104**, 104908 (2008).

- <sup>15</sup>K. Kobayashi, "Hard x-ray photoemission spectroscopy," Nucl. Instrum. Methods Phys. Res., Sect. A 601(1–2), 32–47 (2009).

- <sup>16</sup>L. A. Walsh, G. Hughes, P. K. Hurley, J. Lin, and J. C. Woicik, "A combined hard x-ray photoelectron spectroscopy and electrical characterisation study of metal/SiO<sub>2</sub>/Si(100) metal-oxide-semiconductor structures," Appl. Phys. Lett. **101**, 241602 (2012).

- <sup>17</sup>Y. Y. Gomeniuk, A. N. Nazarov, S. Monaghan, K. Cherkaoui, E. O'Connor, I. Povey, V. Djara, and P. K. Hurley, "Electrical Properties of High-k Oxide in Pd/Al<sub>2</sub>O<sub>3</sub>/InGaAs Stack," in *Proceedings of the International Conference on Nanomaterials: Applications and Properties* (2012), Vol. 1, No. 3, p. 03TF16.

- <sup>18</sup>S. Tanuma, C. J. Powell, and D. R. Penn, "Calculations of electron inelastic mean free paths. IX. Data for 41 elemental solids over the 50 eV to 30 keV range," Surf. Interface Anal. **43**(3), 689–713 (2011).

- <sup>19</sup>J. Chastain and J. F. Moulder, Handbook of X-ray Photoelectron Spectroscopy: A Reference Book of Standard Spectra for Identification and Interpretation of XPS Data (Physical Electronics, Eden Prairie, Minnesota, 1995).

- <sup>20</sup>A. Bahari, P. Morgen, and Z. S. Li, "Valence band studies of the formation of ultrathin pure silicon nitride films on Si(100)," Surf. Sci. 600(15), 2966–2971 (2006).

- <sup>21</sup>M. Gaowei, E. M. Muller, A. K. Rumaiz, C. Weiland, E. Cockayne, J. Jordan-Sweet, J. Smedley, and J. C. Woicik, "Annealing dependence of diamond-metal Schottky barrier heights probed by hard x-ray photoelectron spectroscopy," Appl. Phys. Lett. **100**, 201606 (2012).

- <sup>22</sup>G. Brammertz, H. C. Lin, K. Martens, A. Alian, C. Merckling, J. Penaud, D. Kohen, W.-E. Wang, S. Sioncke, A. Delabie, M. Meuris, M. Caymax, and M. Heyns, "Electrical properties of III–V/oxide interfaces," Electrochem. Soc. Trans. 19(5), 375–386 (2009).

- <sup>23</sup>D. Varghese, Y. Xuan, Y. Q. Wu, T. Shen, P. D. Ye, and M. A. Alam, "Multi-probe interface characterization of In<sub>0.65</sub>Ga<sub>0.35</sub>As/Al<sub>2</sub>O<sub>3</sub> MOSFET," in *Proceedings of International Electron Devices Meeting Technical Digest* (2008), pp. 379–382.

- <sup>24</sup>É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev, and P. K. Hurley, "Temperature and frequency dependent electrical characterization of HfO<sub>2</sub>/In<sub>x</sub>Ga<sub>1-x</sub>As interfaces using capacitance-voltage and conductance methods," Appl. Phys. Lett. **94**, 102902 (2009).

- <sup>25</sup>N. Taoka, M. Yokoyama, S. H. Kim, R. Suzuki, R. Iida, S. Lee, T. Hoshii, W. Jevasuwan, T. Maeda, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, "Impact of Fermi level pinning inside conduction band on electron mobility of InxGa1–xAs MOSFETs and mobility enhancement by pinning modulation," in *Proceedings of the IEEE International Electron Devices Meeting (IEDM)* (IEEE, 2001), p. 610.

- <sup>26</sup>H. C. Lin, W. E. Wang, G. Brammertz, M. Meuris, and M. Heyns, "Electrical study of sulfur passivated In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitor and transistor with ALD Al<sub>2</sub>O<sub>3</sub> as gate insulator," Microelectron. Eng. **86**(7–9), 1554–1557 (2009).

- <sup>27</sup>C. A. Lin, H. C. Chiu, T. H. Chiang, T. D. Lin, Y. H. Chang, W. H. Chang, Y. C. Chang, W. E. Wang, J. Dekoster, T. Y. Hoffmann, M. Hong, and J. Kwo, "Attainment of low interfacial trap density absent of a large midgap peak in In<sub>0.2</sub>Ga<sub>0.8</sub>As by Ga<sub>2</sub>O<sub>3</sub>, Gd<sub>2</sub>O<sub>3</sub> passivation," Appl. Phys. Lett. **98**, 062108 (2011).

- <sup>28</sup>W. Melitz, J. Shen, S. Lee, J. S. Lee, A. C. Kummel, R. Droopad, and E. T. Yu, "Scanning tunneling spectroscopy and Kelvin probe

force microscopy investigation of Fermi energy level pinning mechanism on InAs and InGaAs clean surfaces," J. Appl. Phys. **108**, 023711 (2010).

- <sup>(2)</sup>A. O'Mahony, S. Monaghan, G. Provenzano, I. M. Povey, M. G. Nolan, E. O'Connor, K. Cherkaoui, S. B. Newcomb, F. Crupi, P. K. Hurley, and M. E. Pemble, "Structural and electrical analysis of the atomic layer deposition of HfO<sub>2</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As capacitors with and without an Al<sub>2</sub>O<sub>3</sub> interface control layer," Appl. Phys. Lett. **97**, 052904 (2010).

- <sup>30</sup>S. Klejna and S. D. Elliott, "First-principles modeling of the "clean-up" of native oxides during atomic layer deposition onto III–V substrates," J. Phys. Chem. C 116(1), 643–654 (2012).