| Title                   | Investigation and design of key circuit blocks in a 10 bit SAR ADC at 100 MS/s                                                                   |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                 | O'Sullivan, Gerald                                                                                                                               |

| Publication date        | 2020-07-10                                                                                                                                       |

| Original Citation       | O'Sullivan, G. 2020. Investigation and design of key circuit blocks<br>in a 10 bit SAR ADC at 100 MS/s. MRes Thesis, University College<br>Cork. |

| Type of publication     | Masters thesis (Research)                                                                                                                        |

| Rights                  | © 2020, Gerald O'Sullivan https://creativecommons.org/<br>licenses/by-nc-nd/4.0/                                                                 |

| Download date           | 2025-09-06 09:49:13                                                                                                                              |

| Item downloaded<br>from | https://hdl.handle.net/10468/10609                                                                                                               |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# Investigation and Design of Key Circuit Blocks in a 10 bit SAR ADC at 100 MS/s

A thesis presented to the

National University of Ireland, Cork

for the degree of Masters

by

### Gerald O' Sullivan, B.Eng.

Supervisors: Dr. Ivan O' Connell, Dr. Daniel O' Hare

Head of Department: Prof. Liam Marnane

Tyndall National Institute,

National University of Ireland, Cork

July, 2020

#### Abstract

The work in this thesis is based on the investigation and design of key circuit blocks in a high speed, high resolution SAR ADC in TSMC's 28nm technology. The research carried out analyses the circuit limitations of the switched capacitor DAC and the settling problems of the reference voltage associated with a switched capacitor scheme.

The switched capacitor DAC is a critical block for overall ADC performance and various tradeoffs are weighed up before discussing the layout of the split capacitor DAC implemented in the project, from unit capacitor up to top level routing. It also investigates the main sources of error using this topology and implements effective ways of mitigating these errors. The schematic design of DAC switches is also carried out and the results section discusses the top level linearity performance of the DAC.

This work also focuses on detailed analysis and implementation of a reference buffer circuit solution that is capable of supplying a reference voltage that is highly accurate and can settle in enough time for the high speed and high resolution specifications required by the SAR ADC. Various solutions were comprehensively investigated for this problem and the design of the chosen flipped voltage follower topology was implemented in schematic and layout. It was subsequently simulated at schematic and extracted parasitics level to verify its functionality and determine its overall performance. Finally, the work done in each block is verified in the context of the whole ADC by top level schematic and extracted layout simulation.

# Table of Contents

| Table of Contentsiii                   |

|----------------------------------------|

| Declarationvii                         |

| Acknowledgements                       |

| Acronyms ix                            |

| List of Tables x                       |

| List of Figures xi                     |

| 1 Introduction                         |

| 1.1 SAR ADC Background                 |

| 1.2 Capacitive DAC                     |

| 1.3 Sources of Error on Capacitor DACs |

| 1.3.1 Static Errors                    |

| 1.3.2 Dynamic Error Sources            |

| 1.4 Voltage Reference Buffer           |

| 2 Switched Capacitor DAC Design        |

| 2.1 DAC Topology17                     |

| 2.2 Causes of Static Errors in a DAC   |

| 2.3 DAC Capacitor Sizing               |

| 2.4 Unit Capacitor Design              |

| 2.5 Bridge Capacitor                   |

| 2.6 Redundancy                         |

| 2.7 Capacitor Routing                  |

| 2.8 DAC Schematic                      |

| 2.9 DAC Layout Structure               |

|   | 2.10Top Level DAC Layout                 | 37 |

|---|------------------------------------------|----|

|   | 2.11Break Before Make (BBM) Circuit      |    |

|   | 2.12Summary                              |    |

| 3 | 3 Reference Buffer Design                |    |

|   | 3.1 Voltage Reference Loading            |    |

|   | 3.2 Reference Ringing Problem            |    |

|   | 3.3 Reference Buffer Solution            |    |

|   | 3.4 Settling Requirements Specifications |    |

|   | 3.5 Buffer Amplifier Design              | 59 |

|   | 3.6 Buffer DC Bias Design                |    |

|   | 3.7 Loop-gain Stability Analysis         |    |

|   | 3.8 Buffer Output Stage                  |    |

|   | 3.9 Buffer Test & Simulation Modes       |    |

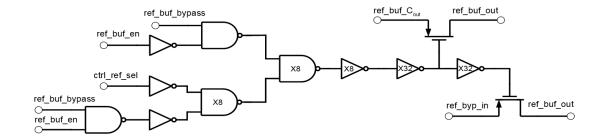

|   | 3.10Buffer Switching Logic               |    |

|   | 3.11Reference Buffer Schematic           |    |

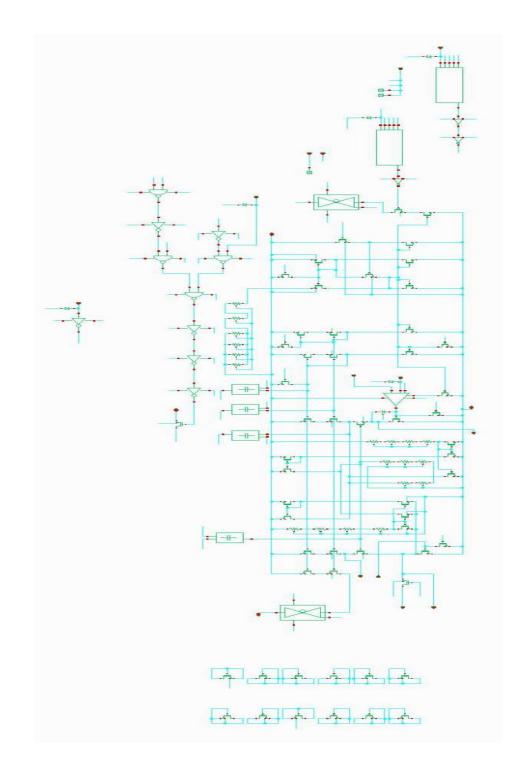

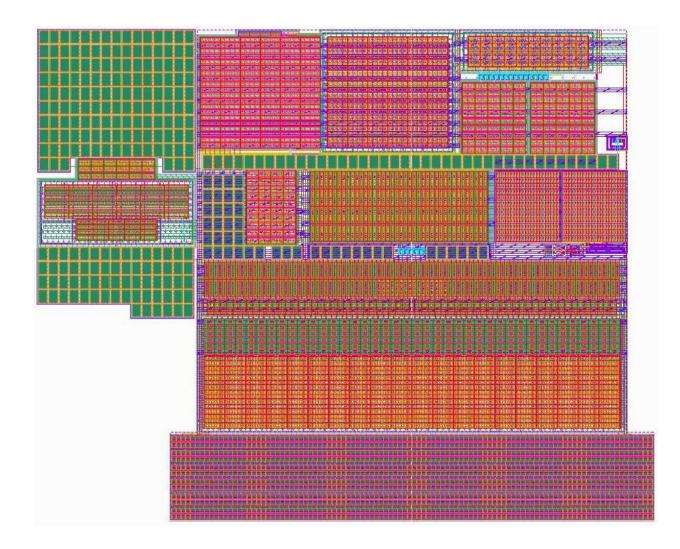

|   | 3.12Reference Buffer Layout              |    |

|   | 3.13Summary                              |    |

| 4 | 4 Results                                | 71 |

|   | 4.1 Capacitive DAC Results               | 71 |

|   | 4.1.1 Introduction                       | 71 |

|   | 4.1.2 Capacitive Matching                | 71 |

|   | 4.1.3 DNL                                |    |

|   | 4.1.4 INL                                | 74 |

|   | 4.1.5 Monte Carlo Analysis               |    |

|   | 4.2 Reference Buffer Results             |    |

|   |     | 4.2.1    | Introduction                         | 77  |

|---|-----|----------|--------------------------------------|-----|

|   |     | 4.2.2    | Buffer Specifications                | 77  |

|   |     | 4.2.3    | DC Analysis                          | 78  |

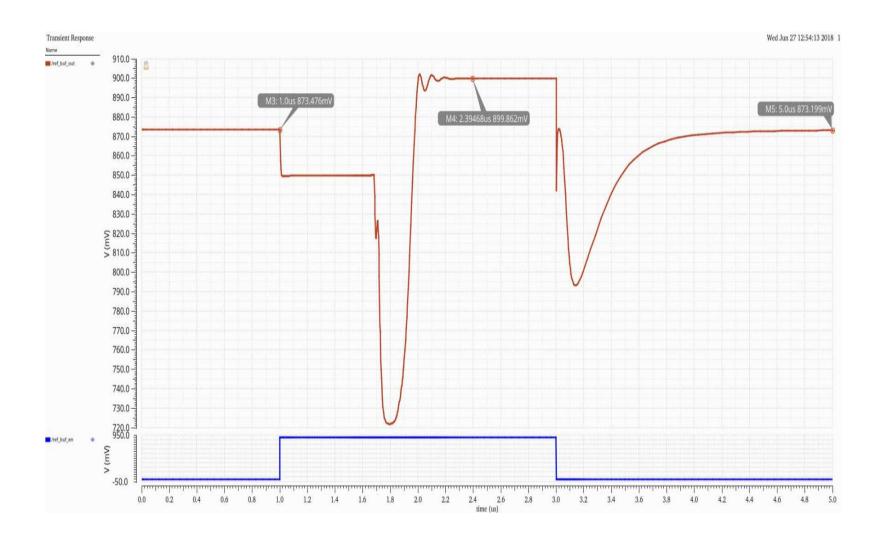

|   |     | 4.2.4    | DAC Step Settling                    | 81  |

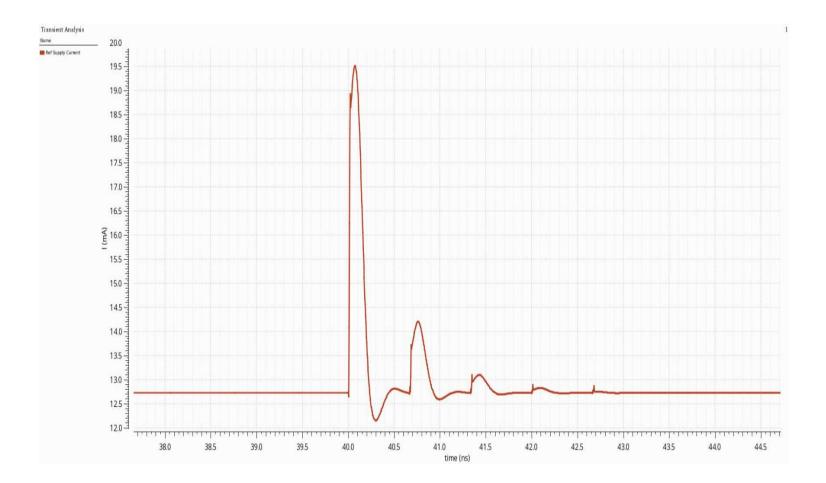

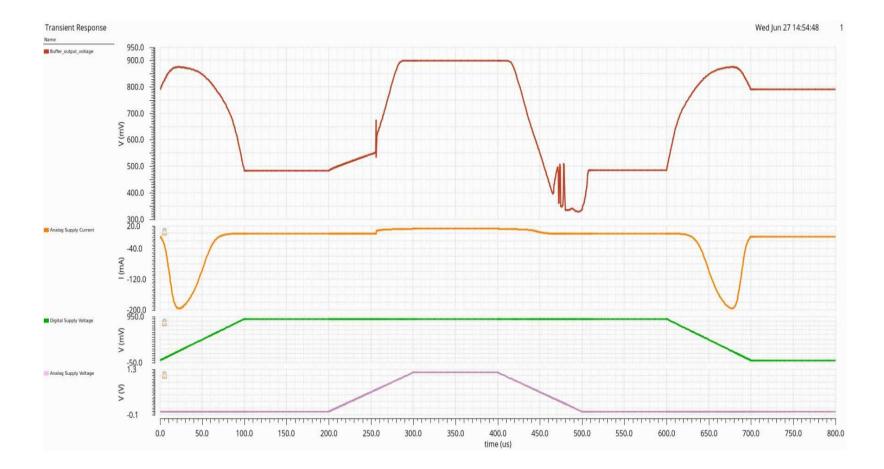

|   |     | 4.2.1    | Supply Current Transient             | 83  |

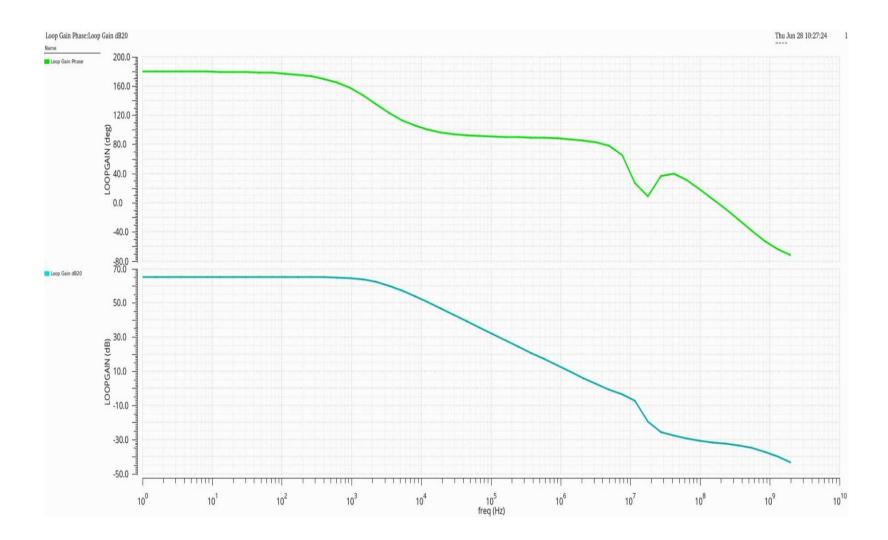

|   |     | 4.2.2    | Loop-gain Analysis                   | 85  |

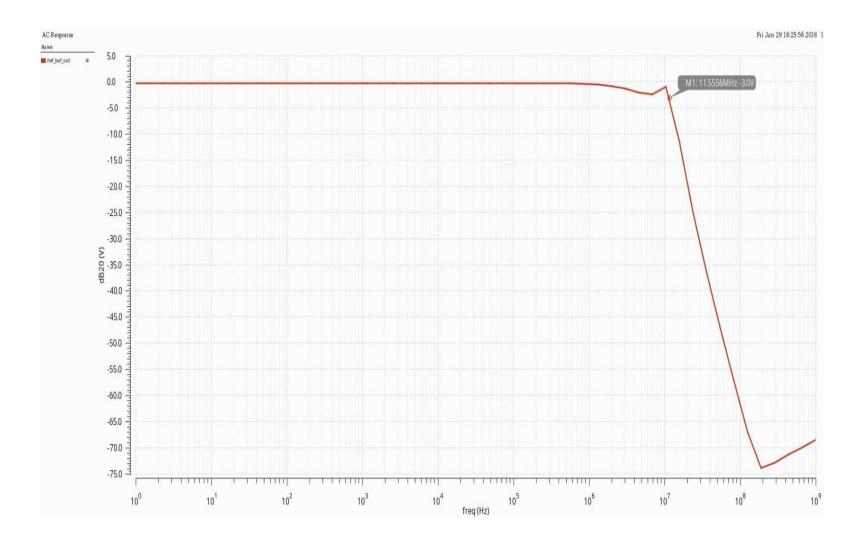

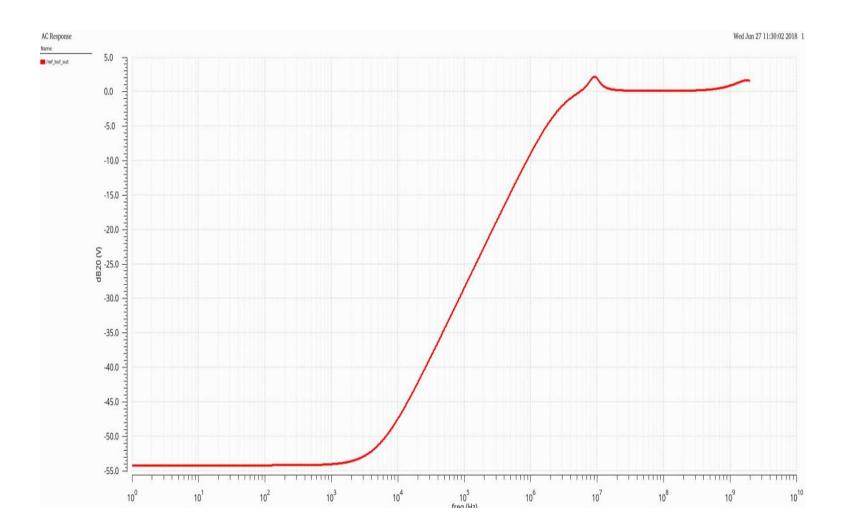

|   |     | 4.2.3    | AC Analysis                          | 87  |

|   |     | 4.2.4    | PSRR                                 | 89  |

|   |     | 4.2.5    | Power Consumption                    | 91  |

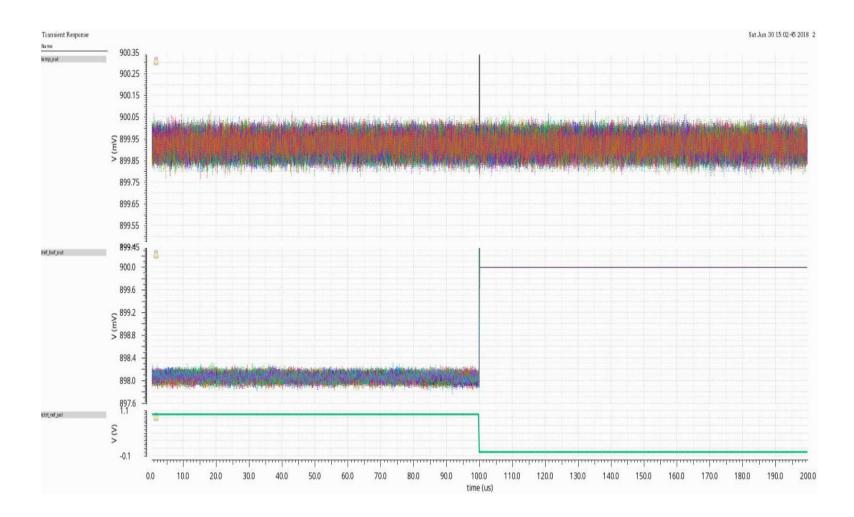

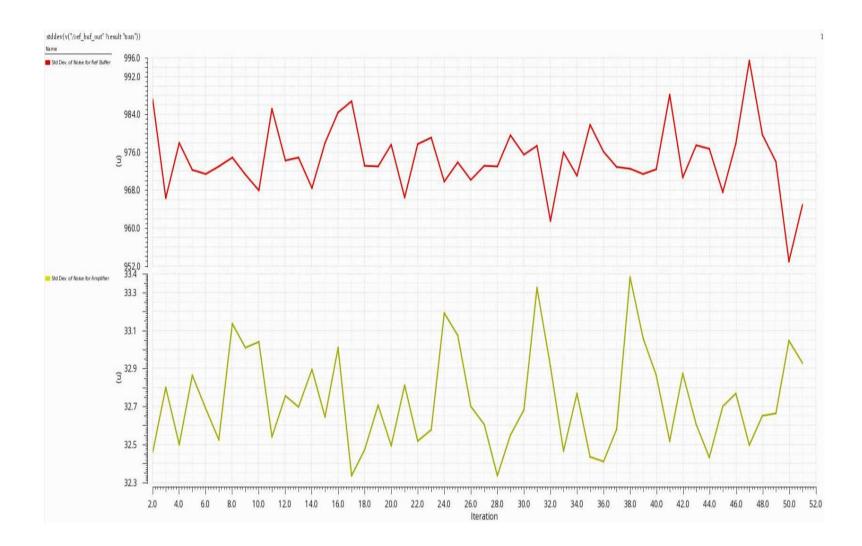

|   |     | 4.2.6    | Transient Noise                      | 91  |

|   |     | 4.2.7    | Output Integrated Noise              | 94  |

|   |     | 4.2.8    | Buffer Enable/Disable Test           | 96  |

|   |     | 4.2.9    | Buffer Power Up/Down Supply Voltages | 98  |

|   |     | 4.2.10   | Summary of Buffer Results            | 100 |

|   | 4.3 | ADC 7    | Гор Level Results                    | 101 |

|   |     | 4.3.1    | Introduction                         | 101 |

|   |     | 4.3.2    | SAR + Reference Buffer Performance   | 101 |

|   | 4.4 | Summ     | ary                                  | 106 |

| 5 | Cor | nclusion | 18                                   | 107 |

|   | 5.1 | Discus   | sion                                 | 107 |

|   | 5.2 | Future   | Work                                 | 109 |

|   |     | 5.2.1    | Reference Error Calibration          | 109 |

|   |     | 5.2.2    | Dynamic Element Matching             | 109 |

|   |     | 5.2.3    | DAC Digital Calibration              | 110 |

|   |     | 5.2.4    | Switching Schemes                    | 110 |

| 5.2.5 Asynchronous Timing                       | 110 |

|-------------------------------------------------|-----|

| Appendix A                                      |     |

| A.1 Derivation of CDAC Equivalent Voltage Model |     |

| References                                      |     |

## Declaration

This is to certify that the work I am submitting is my own and has not been submitted for another degree, either at University College Cork or elsewhere. All external references and sources are clearly acknowledged and identified within the contents. I have read and understood the regulations of University College Cork concerning plagiarism.

Name: Gerald O' Sullivan

*Date: July 2018*

### Acknowledgements

I would like to thank my supervisor, Dr. Ivan O' Connell, for giving me the opportunity to undertake this Masters with MCCI and for all his generous support and guidance along the way.

Kind thanks also to Dr. Daniel O' Hare, who supported me through the design of the project and gave great advice for tackling each problem that arose over the course of the design. His expert technical knowledge and great supervision always kept the project moving forward.

I would like to sincerely thank Gerry McGlinchey for all his great technical advice and discussions over the last few months of the project. I greatly appreciated his experience and pragmatic approach to circuit design.

Many thanks to Dr. Gerardo Salgado who helped get my involvement in the project off the ground and gave invaluable insights throughout the project.

Thanks to Subhash Chevella for his help with every simulation issue that popped up and Cian O' Mahony for helping with any technical problem I had when I first started.

I would like to thank Catherine Walsh for being so kind and helpful over the last two years and everyone in the MCCI office for all the great lunchtime chats.

Finally, I would like to thank my family, particularly my parents, for all their love and support throughout my studies.

# Acronyms

| ADC  | Analogue to Digital Converter           |

|------|-----------------------------------------|

| BBM  | Break-Before-Make                       |

| CDAC | Capacitive DAC                          |

| CMOS | Complementary Metal Oxide Semiconductor |

| DAC  | Digital to Analogue Converter           |

| DEM  | Dynamic Element Matching                |

| DNL  | Differential Non-Linearity              |

| ENOB | Effective Number of Bits                |

| INL  | Integral Non-Linearity                  |

| MIM  | Metal-Insulator-Metal                   |

| МОМ  | Metal-Oxide-Metal                       |

| NMOS | N-type Metal Oxide Semiconductor        |

| PMOS | P-type Metal Oxide Semiconductor        |

| SAR  | Successive Approximation Register       |

## **List of Tables**

| Table 1.1 ADC Target Specifications                                 | 2    |

|---------------------------------------------------------------------|------|

| Table 1.2 Comparison of recent State of the Art High Precision ADCs | 6    |

| Гable 3.1 Source Follower vs. Flipped Voltage Follower              | . 50 |

| Fable 3.2 Truth Table for Switching Logic Circuit                   | . 67 |

| Fable 4.1 Capacitive Matching                                       | . 72 |

| Table 4.2 Reference Buffer Specifications                           | . 77 |

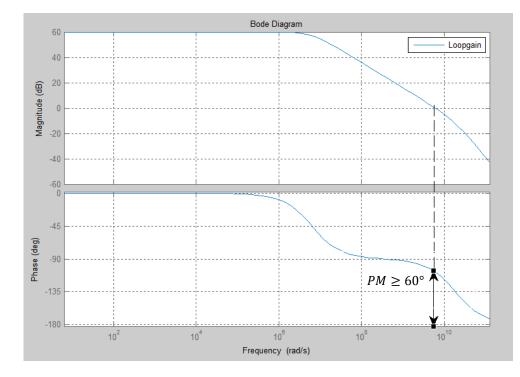

| Гable 4.3 Loop-gain Analysis                                        | . 85 |

| Table 4.4 Power Consumption                                         | . 91 |

| Table 4.5 Top 20 Noise Sources in the Reference Buffer              | . 94 |

| Table 4.6 Reference Buffer Schematic Results Summary    1           | 100  |

# **List of Figures**

| Figure 1.1 DNL Error of an ADC                                      | 3  |

|---------------------------------------------------------------------|----|

| Figure 1.2 INL Error of an ADC                                      | 3  |

| Figure 1.3 Signal to Noise Ratio Illustration                       | 4  |

| Figure 1.4 Sampled Signal                                           | 5  |

| Figure 1.5 Quantised Signal                                         | 5  |

| Figure 1.6 SAR ADC Functional Diagram [9]                           | 8  |

| Figure 1.7 SAR ADC Successive Approximation Timing Diagram (5 bits) | 8  |

| Figure 1.8 Charge Redistribution DAC Architecture                   | 9  |

| Figure 1.9 RC Settling Time Error                                   | 13 |

| Figure 2.1 Differential CDAC & Switches                             | 17 |

| Figure 2.2 MIM Capacitor Structure                                  | 21 |

| Figure 2.3 Plan View of MOM Capacitor Structure                     | 22 |

| Figure 2.4 Cross-Section of MOM Capacitor Structure                 | 22 |

| Figure 2.5 MOM Capacitor Parasitic Model                            | 23 |

| Figure 2.6 Unit Capacitor                                           | 24 |

| Figure 2.7 Metal 6 Layer in Unit Capacitor                       | .25 |

|------------------------------------------------------------------|-----|

| Figure 2.8 Unit Capacitor Showing Metal 6, Metal 1 & Metal 8     | 26  |

| Figure 2.9 Equivalent charge flow diagram of Split Capacitor DAC | 28  |

| Figure 2.10 Effect of MSB parasitics on V <sub>out</sub>         | 29  |

| Figure 2.11 Effect of LSB parasitics on V <sub>out</sub>         | 29  |

| Figure 2.12 Effect of Bridge Capacitor Offset on Vout            | 29  |

| Figure 2.13 Time Trellis of Bit Trials without Redundancy        | 31  |

| Figure 2.14 Time Trellis of Bit Trials with Redundancy           | 32  |

| Figure 2.15 Top plate and Bottom plate routing                   | 33  |

| Figure 2.16 Bridge Capacitor Routing                             | 34  |

| Figure 2.17 Single Ended CDAC Implemented in SAR ADC             | 35  |

| Figure 2.18 Illustration of CDAC Layout Structure                | 36  |

| Figure 2.19 Top Level Layout of CDAC                             | 37  |

| Figure 2.20 BBM Timing Diagram                                   | 38  |

| Figure 2.21 BBM circuit for MSB columns                          | 39  |

| Figure 2.22 BBM circuit for LSB columns                          | 39  |

| Figure 2.23 Layout of BBM and Switches                           | 40  |

| Figure 3.1 DAC Switching Induced Reference Currents                                | 42 |

|------------------------------------------------------------------------------------|----|

| Figure 3.2 SAR Sampling Network                                                    | 43 |

| Figure 3.3 Timing diagram for switch circuit                                       | 44 |

| Figure 3.4 Flip Chip Package Model                                                 | 45 |

| Figure 3.5 RLC Reference Voltage Response with Bond Wire Resistance of $5m\Omega$  | 48 |

| Figure 3.6 Zoomed in graph of Figure 3.4 showing decaying sinusoidal response      | 48 |

| Figure 3.7 RLC Reference Voltage Response with Bond Wire Resistance of $0.5\Omega$ | 49 |

| Figure 3.8 NMOS Source Follower Schematic                                          | 52 |

| Figure 3.9 Flipped Voltage Follower Schematic                                      | 53 |

| Figure 3.10 FVF Small Signal Equivalent Circuit for Rout                           | 54 |

| Figure 3.11 Source Follower Small Signal Equivalent Circuit for Rout               | 56 |

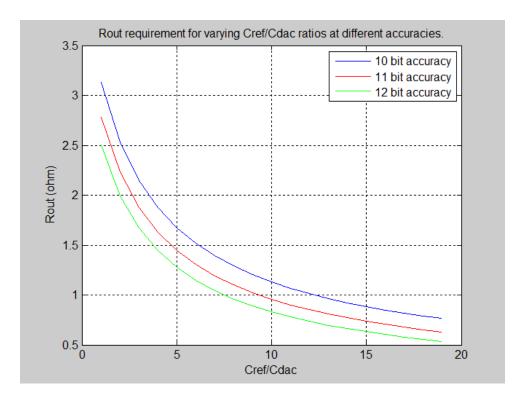

| Figure 3.12 Rout Buffer Specifications for Different Capacitance Ratios            | 58 |

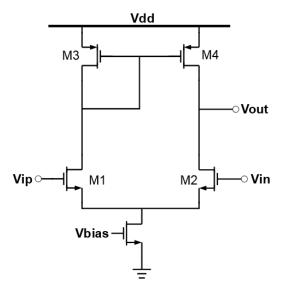

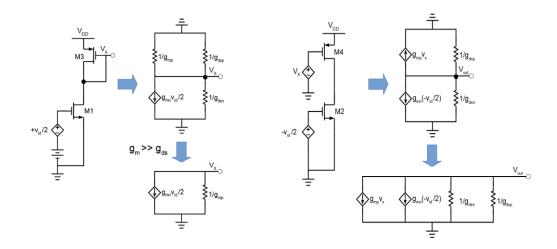

| Figure 3.13 Amplifier Circuit Schematic                                            | 59 |

| Figure 3.14 LHS Amplifier Gain Derivation                                          | 60 |

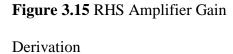

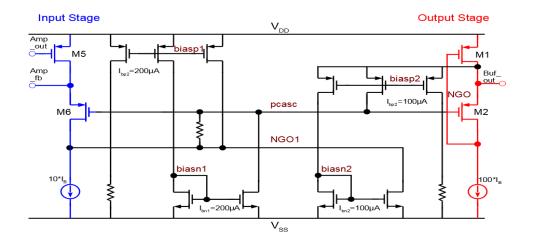

| Figure 3.15 RHS Amplifier Gain Derivation                                          | 60 |

| Figure 3.16 FVF Current Biasing Circuit                                            | 61 |

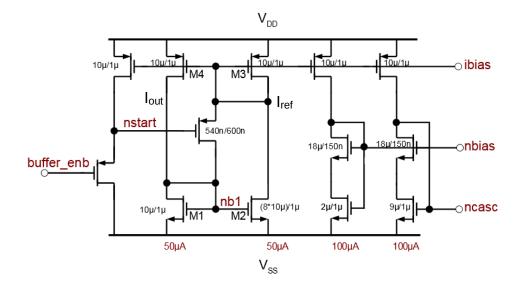

| Figure 3.17 NGO1 and pcasc Voltage Drop Biasing Circuit                            | 62 |

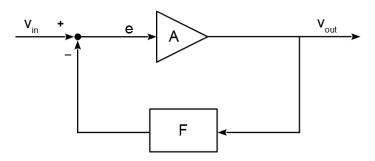

| Figure 3.18 Amplifier Closed Loop Gain                                                   | 63    |

|------------------------------------------------------------------------------------------|-------|

| Figure 3.19 Amplifier Loop-gain plots for finding stability margins                      | 65    |

| Figure 3.20 Buffer Switching Logic Circuit                                               | 67    |

| Figure 3.21 Reference Buffer Schematic                                                   | 68    |

| Figure 3.22 Reference Buffer Layout                                                      | 69    |

| Figure 4.1 Schematic of Capacitive Array                                                 | 71    |

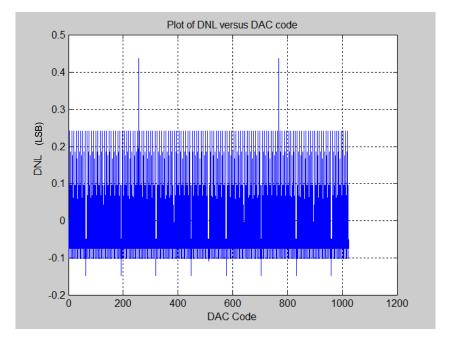

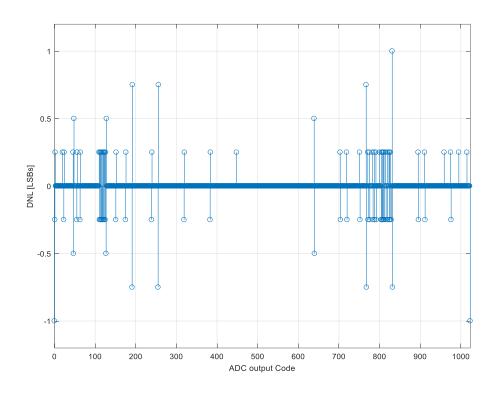

| Figure 4.2 Capacitive DAC DNL                                                            | 73    |

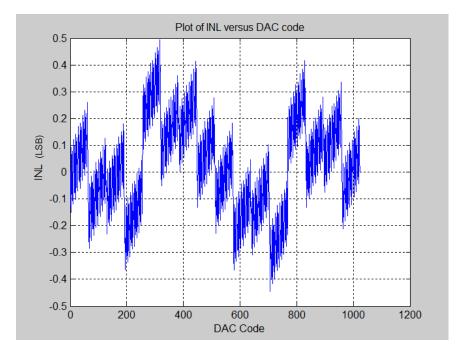

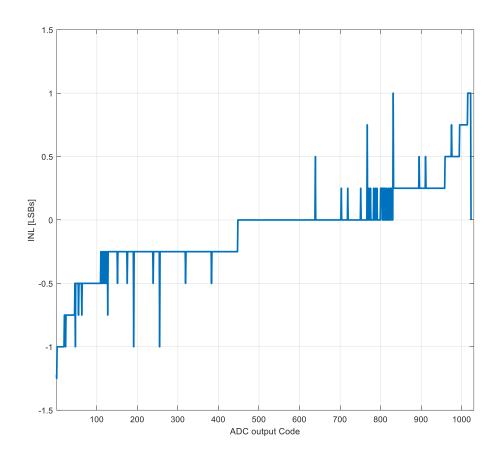

| Figure 4.3 Capacitive DAC INL                                                            | 74    |

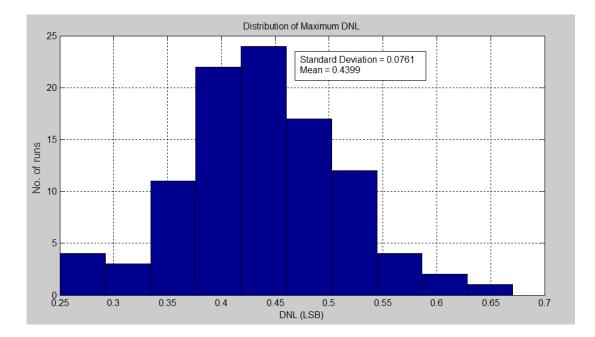

| Figure 4.4 Monte Carlo Distribution of Max. DNL for 100 ramp tests                       | 75    |

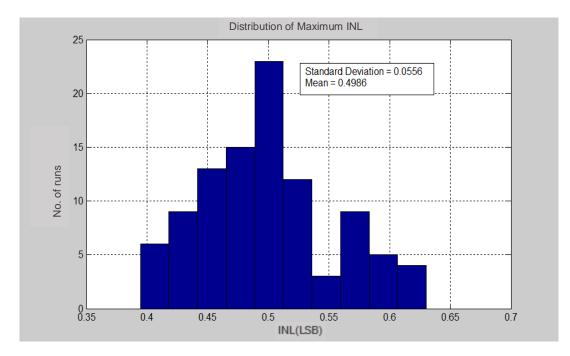

| Figure 4.5 Monte Carlo Distribution of Max. INL for 100 ramp tests                       | 76    |

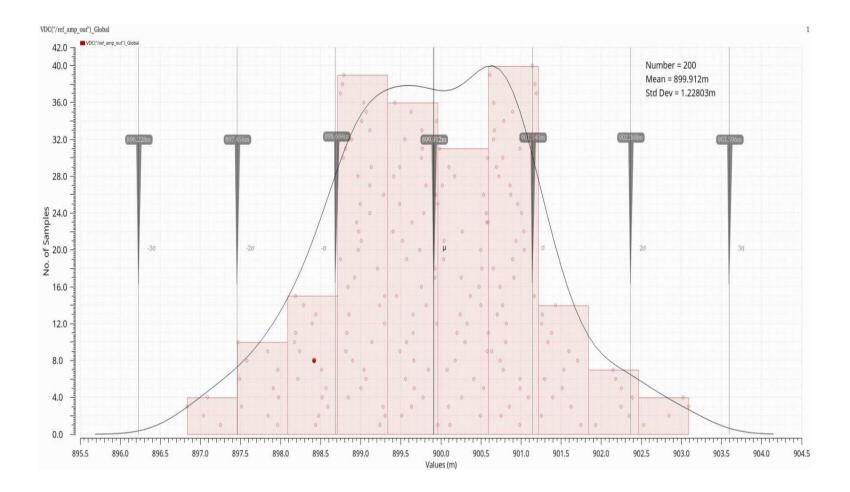

| Figure 4.6 Monte Carlo DC Analysis of Amplifier Output Voltage                           | 79    |

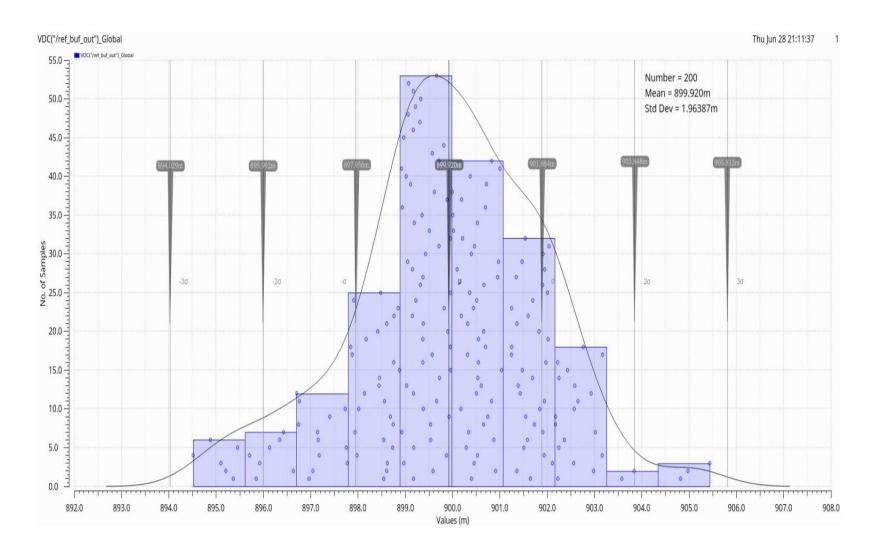

| Figure 4.7 Monte Carlo DC Analysis of Buffer Output Voltage                              | 80    |

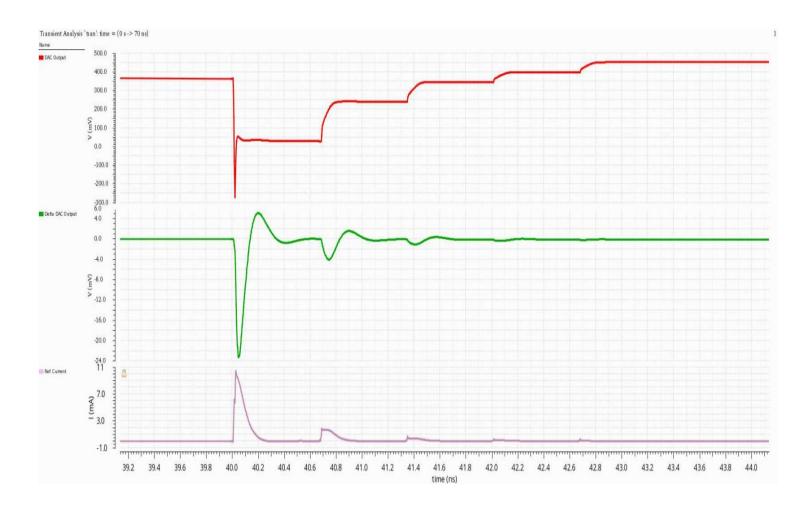

| Figure 4.8 DAC step settling and difference between settling with ideal reference and be | uffer |

| reference                                                                                | 82    |

| Figure 4.9 Buffer Supply Current Transient                                               | 84    |

| Figure 4.10 Loop-gain Analysis for Amplifier Schematic                                   | 86    |

| Figure 4.11 AC Response of Buffer                                                        | 88    |

| Figure 4.12 Buffer Schematic PSRR                                                  | 90   |

|------------------------------------------------------------------------------------|------|

| Figure 4.13 Transient Noise of Amplifier & Buffer Non-Bypass Bypass Mode           | 92   |

| Figure 4.14 Standard Deviation of Amplifier and Buffer Noise across 100 Iterations | 93   |

| Figure 4.15 Buffer Disabled - Enabled - Disabled                                   | 97   |

| Figure 4.16 Power up/down of Analog & Digital Supplies                             | 99   |

| Figure 4.17 DNL for Top Level SAR with Reference Buffer and Redundancy Enabled     | 102  |

| Figure 4.18 INL for Top Level SAR with Reference Buffer and Redundancy Enabled     | 103  |

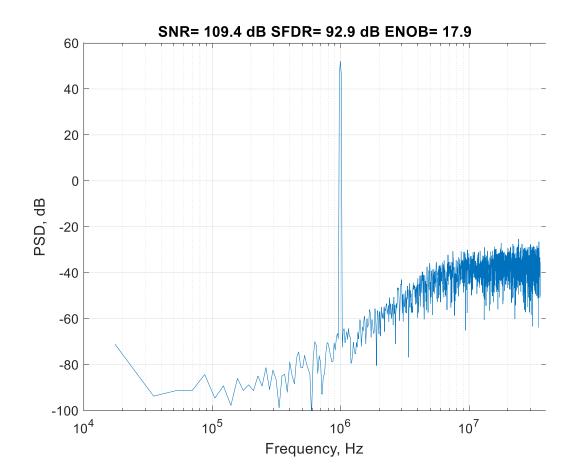

| Figure 4.19 Power Spectral Density using Sine Wave Input with Non-Redundancy SA    | AR & |

| Reference Buffer (trnoise) with NS                                                 | 104  |

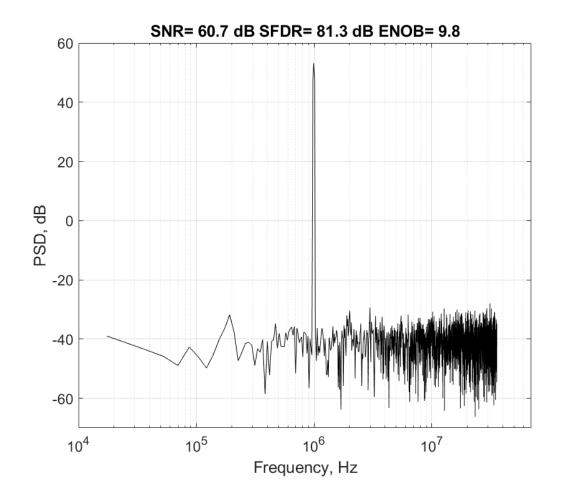

| Figure 4.20 Power Spectral Density using Sine Wave Input with Non-Redundancy SA    | AR & |

| Reference Buffer (trnoise) without NS                                              | 105  |

| Figure A.1 Equivalent charge flow diagram of Split Capacitor DAC                   | 111  |

### **1** Introduction

The purpose of this thesis is to investigate the various challenges faced in the design of a Successive Approximation Register (SAR) Analogue to Digital Converter (ADC). The work done on this project was carried out as a part of a high resolution noise-shaping ADC on 28 nm silicon. The objective of this project was to achieve at least 15 bit resolution for a 1 MHz input signal at a sampling rate of 70 MS/s. Using a lower resolution DAC (Digital to Analogue Converter), the noise shaping circuits shape or High Pass filter the quantization noise of the DAC and the comparator noise to obtain a higher resolution than the resolution of the SAR core.

There are many challenges faced in the design of a SAR ADC due to the complexity of the design and the tight design constraints that are necessary to ensure optimum performance. Various trade-offs, such as resolution, speed, power and area must be made in order to meet these specifications and this adds to the challenge of choosing the right solution to each problem faced over the course of the design. This Masters project involved designing the Capacitor DAC, corresponding switches and the provision of a stable reference voltage in order to help achieve the defined specifications of the overall SAR ADC. These challenges and their corresponding solutions will be discussed in depth throughout this thesis. The main target specifications of the ADC are summarized in Table 1.1 below:

| Specification                     | Target Value |  |  |

|-----------------------------------|--------------|--|--|

| Technology                        | TSMC 28nm    |  |  |

| Resolution without shaping (ENOB) | 10 bits      |  |  |

| SAR clock rate (synchronous)      | 1.5 GS/s     |  |  |

| Sample Rate                       | 100 MS/s     |  |  |

| Input Signal Bandwidth            | 1 MHz        |  |  |

| SNDR @100kHz                      | 90 dB        |  |  |

| Supply Voltage                    | 0.9 V        |  |  |

| Resolution with shaping (ENOB)    | >15 bits     |  |  |

| Power without ref. buffer (mW)    | 5            |  |  |

| Power with ref. buffer (mW)       | 15           |  |  |

Table 1.1 ADC Target Specifications

The performance of a SAR ADC is defined by its static (low frequency) and dynamic (high frequency) behaviour:

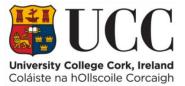

• **Differential Non-Linearity (DNL):** In an ADC, it is the difference between an actual step width and the ideal LSB width.

Figure 1.1 DNL Error of an ADC

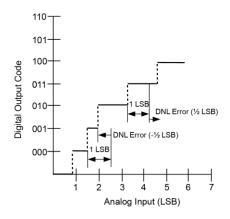

• Integral Non-Linearity (INL): In an ADC, it is the deviation of the values of the actual transfer function from a straight line. This straight line is either the line of best fit or from the first and last point in the ramp, with offset and gain removed.

Figure 1.2 INL Error of an ADC

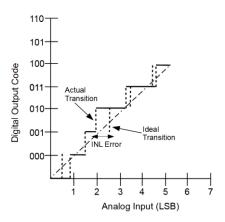

• Signal to Noise Ratio (SNR): It is the ratio of the amplitude of the desired signal to the amplitude of all the noise signals. In a low power ADC it is usually dominated by thermal noise. It is calculated from the frequency spectrum of the ADC output for a coherent tone input.

Figure 1.3 Signal to Noise Ratio Illustration

- Signal to Noise and Distortion (SINAD): This is a measure of the ratio of the RMS value of the sinewave to the RMS value of all the noise signals plus distortion.

- **Spurious Free Dynamic Range (SFDR):** It is the ratio of the RMS amplitude of the required signal to the RMS value of the next largest spurious component.

- Effective Number of Bits (ENOB): The resolution of the ADC denotes the number of bits used to represent the analog value, while the ENOB denotes the resolution of an ideal ADC that would give the same effective resolution. It is dependent on the total noise and distortion present in the ADC [1].

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

(1.1)

#### 1.1 SAR ADC Background

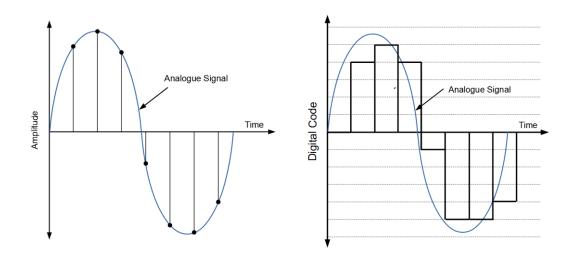

An ADC is one of the most important electronic devices in modern technology, in that it provides an interface between continuous signals in the real world and digital data storage and processing in the digital world. It does this by converting a continuous input voltage into a number of discrete steps, which are each assigned a digital code. The first step is sampling, where the signal is taken at periodic time intervals but still has continuous time amplitudes. The second step is quantization, where the signal is converted to discrete voltage levels [2]. Sampling involves switching an analogue signal onto a capacitor at a discrete time step. Quantization converts a discrete time analogue voltage signal into a discrete time, discrete voltage signal by successively comparing it to DAC digital outputs. This digital data can now be easily processed by micro-controllers and important information can be garnered and utilized for a wide range of applications.

Figure 1.4 Sampled Signal

Figure 1.5 Quantised Signal

The table below compares the State of the Art for high precision ADCs converting 1 MHz signals. Most of them use Sigma Delta architectures, either Continuous Time (SDCT) or Switched Capacitor (SDSC). The novel architecture used in this project implements a SAR core ADC to achieve state of the art precision at equal sampling speed.

| Reference                   | <b>Ho</b> [3] | Brewer [4] | Silva [5]        | Bannon [6]       | Bandyopadhyay [7] |

|-----------------------------|---------------|------------|------------------|------------------|-------------------|

|                             | 2015          | 2005       | 2006             | 2014             | 2014              |

| Architecture                | SDCT          | SDSC       | SDCT,<br>Complex | Pipeline,<br>SAR | SDCT              |

| Fs (MHz)                    | 140           | 20         | 41.7             | 5                | 57.5              |

| Fin (MHz)                   | 2.2           | 1          | 0.2              | 0.001            | 0.6               |

| OSR                         | 32            | 10         | 104              | 1                | 48                |

| SNDR (dB)                   | 90.4          |            | 90               | 98.6             |                   |

| SNR (dB)                    |               | 100        |                  | 99               | 97.3              |

| Power (mW)                  | 4.5           | 475        | 210              | 30.5             | 21                |

| Walden FOM<br>(pJ/con step) | 37.8          | 2905.2     | 20310.5          | 87.7             | 678.2             |

| Schreier FOM<br>(dB/J)      | 177.3         | 163.2      | 149.8            | 177.7            | 164.6             |

| Technology (nm)             | 55            | 250        | 180              | 180              | 180               |

| Area (mm <sup>2</sup> )     | 0.09          | 20.21      | 6                | 5.74             | 0.99              |

Table 1.2 Comparison of recent State of the Art High Precision ADCs

6

In the last ten years, SAR architecture has become a major design involved in advancing the state of the art in analog-to-digital conversion. One of the major reasons for this is that SAR ADCs rely on MOS switches and latches, which have greatly benefitted from technology scaling [8]. They also use switched capacitor DACs, which benefit from good matching and no static power consumption. SAR ADCs are frequently chosen as a viable architecture for medium to high resolution applications with sample rates under 5 MS/s. The resolution of these devices commonly range between 8-16 bits, with comparatively low power consumption as well as a small form factor [9]. Due to their sequential nature, the best performing SAR ADCs have around 10 bit resolution

Compared to other architectures, SAR ADCs are very power efficient for medium accuracies. This benefits from their simple design which can allow lower supply voltages to be used [10]. These obvious advantages and the flexibility they provide make this architecture very popular for a wide array of applications.

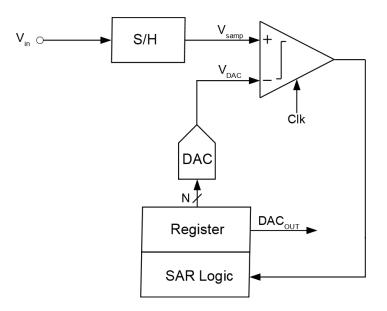

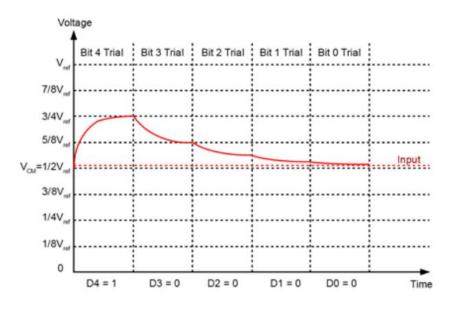

A SAR ADC consists of a sample and hold circuit, which samples the input voltage onto a capacitor, using switches. This allows a constant input voltage sample to be maintained during the conversion [2]. This is then followed by a comparator which compares an input signal with a reference voltage [11]. In this way, it generates the bits by successive approximation [2]. This comparator output is fed to the Successive Approximation Register, which functions to perform the binary search algorithm to sequentially determine the value of each bit based on the output of the comparator and supply the DAC with a digital approximation voltage. It takes N clock cycles to obtain all N bits of the digital code [12]. This is shown below in Figure 1.6 and the successive approximation of a 5 bit SAR ADC is illustrated in the timing diagram in Figure 1.7.

Figure 1.6 SAR ADC Functional Diagram [9]

Figure 1.7 SAR ADC Successive Approximation Timing Diagram (5 bits)

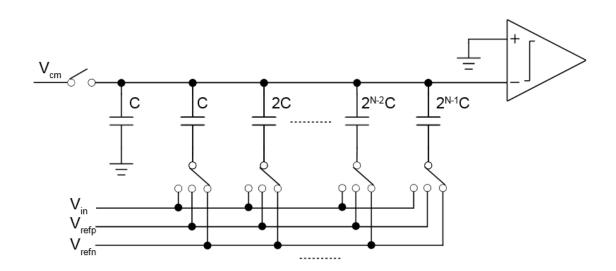

### 1.2 Capacitive DAC

A DAC is an integral part of a switched capacitor SAR ADC. It converts the digital code generated by the comparator to an analogue signal and this signal is compared with the analogue input signal during bit cycling to successively approximate the correct digital code. As a result, the accuracy of the overall ADC is very dependent on the accuracy of the DAC. The DAC can be implemented as a capacitor based, switched current or R-2R ladder DAC. The reasons for choosing the capacitive DAC were the zero quiescent current and better matching capabilities of capacitors over resistors [13]. Charge redistribution DACs set an output voltage proportional to the ratio of the capacitance switched to Vrefp and the total capacitance. Another advantage of using a capacitive charge redistribution DAC is that the input signal can be sampled onto the capacitive DAC, taking away the need for having a separate sample and hold circuit, saving area on chip [14].

Figure 1.8 Charge Redistribution DAC Architecture

#### 1.3 Sources of Error on Capacitor DACs

Error sources appear in two different forms on a DAC. These can be described as static error sources and dynamic error sources. Static errors determine the accuracy of the DAC and dynamic errors affect how consistent the DAC conversions will be. The impact of these errors is that an inaccurate charge distribution can occur during the conversion stage on the DAC and an incorrect analogue output voltage will be fed to the comparator.

#### 1.3.1 Static Errors

- *Offset Error:* This error can be defined in a DAC as the step value at the output when the digital input is zero. It is a linear error, so all codes are affected equally [15]. Offset errors manifest in a SAR from offsets in the comparator or reference voltage DC offsets.

- *Gain Error:* It is defined as the difference between the nominal and actual gain points on the transfer function after the offset error has been corrected to zero [15]. It has the same percentage error on each step. It can be caused by top plate parasitic capacitances to ground.

- *DNL*: Static error sources can manifest themselves as non-linearities in the output of the DAC. A common measurement of the linearity performance in a DAC is Differential Non-Linearity (DNL). DNL measures the deviation of each step from an ideal LSB [16]. It is defined mathematically in Equation 1.2:

$$DNL(i) = \frac{V_{out(i+1)} - V_{out(i)}}{V_{LSB\_IDEAL}} - 1, where \ 0 < i < 2^{N-2}$$

(1.2)

$V_{out(i)}$  is the DAC output code corresponding to the digital code input i, N is the number of bits of the DAC and  $V_{LSB_IDEAL}$  is the ideal step size between two adjacent analogue outputs [17]. A DAC is monotonic if the analog output always increases as the DAC code increases. A negative DNL causes nonmonotonicity in a DAC [1]. The impact of non-monotonicity in a DAC is missing codes in the output of the SAR ADC. DNL in the DAC output codes results in noise in the ADC, reducing the overall SNR [18].

*INL:* Another metric for non-linearity in a data converter is integral non-linearity. It is a measure of the deviation between the actual output value of the DAC and the ideal output value, essentially measuring the accumulation of errors in all the preceding codes. INL manifests itself as harmonic distortion in the SAR ADC output reducing the Spurious Free Dynamic Range (SFDR) [18]. INL is defined mathematically in Equation 1.3:

$$INL(i) = \sum_{j=0}^{i} DNL_{j}, where \ 0 < i < 2^{N-2}$$

(1.3)

#### 1.3.2 Dynamic Error Sources

Measuring static errors allows a designer to quantify the level of performance in their circuit under an ideal, fully settled, noise free environment. In reality dynamic errors, in the form of partially settled conversions and thermal noise, will limit the overall performance of a DAC. The dynamic performance of a DAC is quantified using the three metrics: Signal to Noise Ratio (SNR), Signal to Noise plus Distortion Ratio (SNDR) and Effective Number of Bits (ENOB).

• *Thermal Noise*: Thermal noise is a fundamental limitation of any analogue circuit design. Along with matching requirements, it sets the unit capacitor size of the DAC. It is a white random process, meaning that it is flat across the spectrum, giving it a random voltage signal, independent of frequency [19]. In any electrical conductor, the electrons present will experience random velocity fluctuations, caused by the thermal energy in the conductor. This will cause voltage variations across the conductor (resistor) [20]. This thermal noise power is defined mathematically as:

$$\overline{V_n^2} = 4kTR \cdot \Delta f \ V^2/Hz \tag{1.4}$$

Where *k* is Boltzmann constant, *T* is temperature in Kelvin, *R* is the resistance of the conductor and  $\Delta f$  is the bandwidth of the ADC system. The output thermal noise voltage of an RC circuit can then be defined as [20]:

$$\overline{v_n^2} = \frac{kT}{C} V^2 \tag{1.5}$$

12

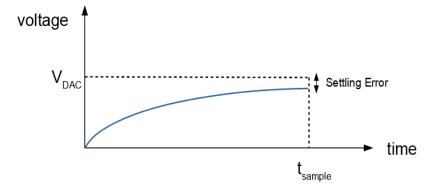

• *RC Settling*: The conversion period of the DAC will set the maximum RC settling time for each conversion. Conversion time is set by the comparator decision time, logic processing time and DAC settling time. DAC settling time sets the switch sizes for the DAC. Conversion time, along with power, area and resolution considerations will dictate the capacitor sizes and the architecture used in the design. Incomplete settling during the sampling stage will produce errors in the output and effect the accuracy of the overall ADC. The finite settling time constraints are defined by the sampling capacitance, the voltage difference and the total series switch resistance. Larger capacitors are more beneficial for matching requirements and thermal noise but increasing the RC settling time constant of the circuit [21]. The figure below illustrates the incomplete settling of an RC switched capacitor circuit.

Figure 1.9 RC Settling Time Error

#### 1.4 Voltage Reference Buffer

A stable reference voltage is one of the major requirements for an accurate SAR ADC. The reference voltage is a very precise voltage at which the input to an ADC is compared against or the output of a DAC is generated from. For a stable and repeatable data conversion it is necessary to have a non-varying reference voltage at the end of each sampling instance. This becomes an even greater requirement for higher resolution data converters, with ever smaller LSB step sizes requiring more precise reference voltages [22]. The absolute value of the reference is important for some applications where precise voltages need to be measured. For other applications the relative magnitude of different input signals is sufficient.

The biggest challenge of maintaining a stable reference voltage is the charge draw onto the capacitor after each switching instant, during conversion. This charge draw causes the reference voltage to drop and necessitates a finite time to allow the reference voltage to return to the stable and repeatable level. If an off-chip reference is supplied to the DAC, the settling is worsened due to parasitic inductances in the bond wires. The large current drawn by the capacitor array after a switching instant through this parasitic inductance causes ringing in the reference voltage which, in turn, provides an unstable reference voltage to the DAC and inconsistent output codes [23].

Decoupling capacitors are commonly used to dampen the oscillations on the reference voltage and short high frequency signals to ground. Large capacitors act as charge reservoirs for transient current and, therefore, effectively filter low frequency noise [24]. However, in order to provide a stable reference adequate for high resolution and high speed applications, the area/power demands of the capacitor become too great due to the capacitance needed to rectify the ringing problem. Possible solutions for this problem are reservoir capacitors used in [25] and sampling the reference as described in [26].

In the following two chapters the design process of the project will be discussed. Chapter 2 details the design and optimization of the capacitive DAC and Chapter 3 describes the design and optimization of the reference buffer. In Chapter 4 the results of the projects are illustrated and discussed and, finally, chapter 5 discusses the conclusions of the work and any future work that could be based off this project.

### 2 Switched Capacitor DAC Design

Although advanced CMOS processes are created to build highly complex digital circuits with millions of transistors, a benefit of these technologies with their fine wire spacing is that they can achieve good capacitor densities and raw (untrimmed/calibrated) matching greater than 10 bit [27]. They also make good switches for the switched CDAC because parasitic capacitance of switches reduces with scaling, helping to improve linearity [28]. Due to these reason CMOS SARs became very popular in the 2000s [29]. The Capacitive DAC is a very important element of a switched capacitor SAR ADC. It allows sampling to be carried out before conversion, without requiring an additional capacitor. It impacts directly on the resolution of the ADC and must be designed with sampling speed, thermal noise figure, area and power in mind.

## 2.1 DAC Topology

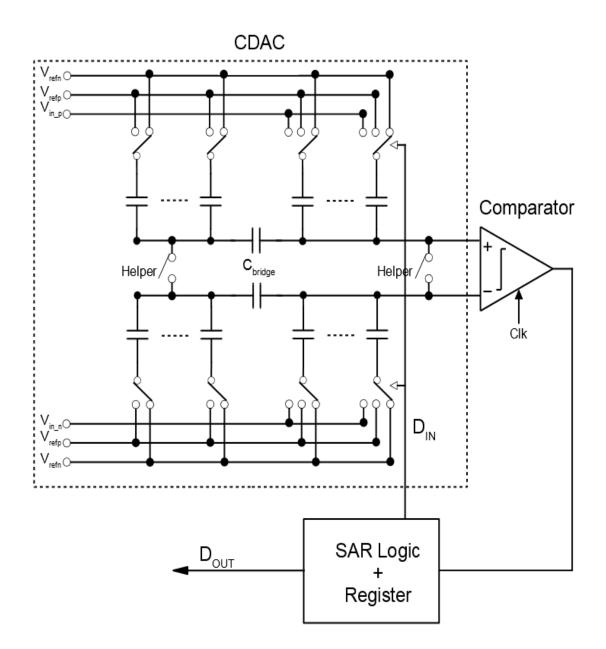

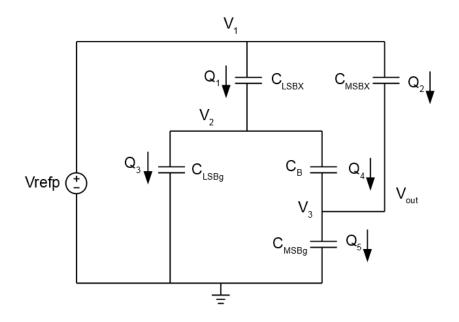

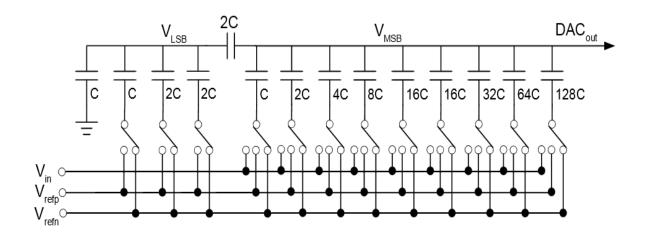

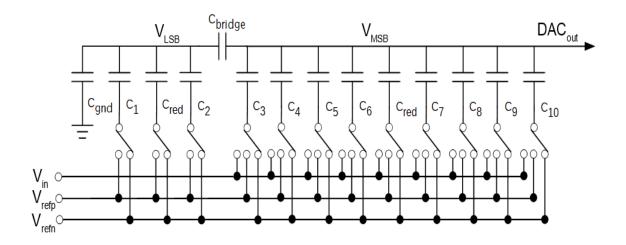

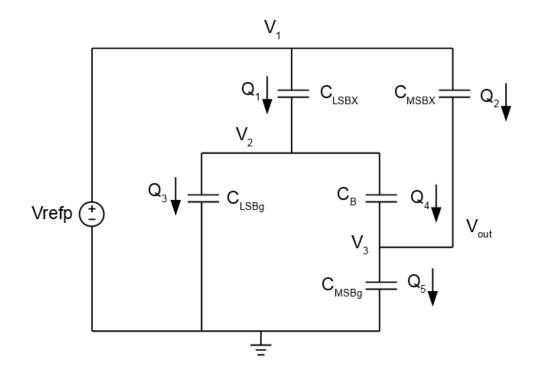

Figure 2.1 shows the type of DAC implemented in the overall SAR ADC.

Figure 2.1 Differential CDAC & Switches

#### 2.2 Causes of Static Errors in a DAC

- Systematic Offset: A systematic offset in the capacitor array will manifest itself as a gain error or as a DNL or INL error. The sources of systematic mismatches have the same effect on every device. Top plate parasitic capacitance to the substrate can cause a gain error or a linearity error if on the LSB side of a split capacitor array. This is explained further with diagrams in Section 2.5. If the layout of the device is precise with equal area on each capacitor and low level parasitic capacitance between each node, this problem can be mitigated with each device seeing the same percentage difference [30]. Systematic offset can also be caused by process gradients which affect each device differently and cause a mismatch between individual devices. This problem can be alleviated by ensuring that devices are close together or follow a common centroid layout so that each capacitor is affected proportionally by the process gradient [31]. The effect of systematic offsets can be largely eliminated by correct layout design procedures, minimizing inherent offsets in capacitances, bias currents, DC voltages, etc.

- Random Mismatch: This phenomenon occurs from random process variations, such as non-uniform dielectric thickness, edge variations and different doping concentrations on a device to device basis. It is a harder problem to deal with than systematic offset because they cannot be predicted before the chip has

been built. The effect of random mismatch is dependent on the device size and can be minimized by using larger devices [32].

$$\sigma\left(\frac{\Delta C}{C}\right) \propto \frac{1}{A_C} \tag{2.1}$$

Where  $A_C$  is capacitor area,  $\Delta C$  is the random variation of the unit capacitor (C) and the standard deviation of the unit capacitor mismatch is denoted as  $\sigma(\Delta C/C)$  [33].

This, of course, poses its own disadvantages by increasing area, power and, potentially, settling time requirements. Random mismatch causes linearity errors and reduces the ADC ENOB. Switch capacitors are the main error sources for smaller capacitors, with wiring and switches causing more fixed errors for larger capacitor values.

#### 2.3 DAC Capacitor Sizing

One of the biggest considerations to be made when designing a switched capacitor DAC for a SAR ADC is the sampled thermal noise. This sets the lower noise limit in the ADC. The total capacitance in the DAC determines the sampled thermal noise in the ADC as shown in the following equation:

$$V_{noise} = \sqrt{\frac{kT}{C_{DAC}}}$$

(2.2)

The limit of sampled thermal noise is determined as follows:

$$\sqrt{\frac{kT}{C_{DAC}}} = \frac{1}{2} \text{LSB}$$

(2.3)

To achieve 10 bit resolution in the DAC with  $V_{ref} = 0.9$  V, thermal noise must be limited to:

$$\sqrt{\frac{kT}{C_{DAC}}} = 440 \ \mu V \tag{2.4}$$

Solving for C<sub>DAC</sub> in the previous equation (at room temperature) gives:

$$C_{DAC} = 0.02 \text{ pF}$$

(2.5)

A DAC capacitance of 2 pF was ultimately used, meaning that it was not limited by thermal noise. Mismatch became the limiting factor, so the unit capacitor was sized at 15 fF to ensure static performance wasn't degraded by capacitor mismatch.

## 2.4 Unit Capacitor Design

The sizing of the unit capacitor is one of the most critical specifications for the CDAC because it determines the level of thermal noise and mismatch in the DAC as well as area and power consumption [34]. The area of the capacitor is also important with mismatch determined by Pelgrom's inverse-area mismatch model [35]. There are two main types of Capacitors that are used in the design of CDACs. These are Metal-Insulator-Metal (MIM) capacitors and Metal-Oxide-Metal (MOM) capacitors.

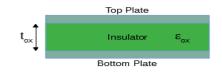

**MIM capacitors** have comparatively good area efficiency. They do suffer from strict layout rules, however, which limit the minimum MIM capacitance to several femtofarads or tens of femtofarads. They also require special dedicated metal layers and process steps. As a result they are not supported by all process technologies [33].

Figure 2.2 MIM Capacitor Structure

The equation below shows how the capacitance of a MIM capacitor relates to the permittivity of the dielectric, the oxide thickness and the area of each metal plate. Due to a thin, high permittivity dielectric used in MIM devices their area can be vastly reduced. As seen in the MIM model above, the capacitance is vertically between two metal layers, with the top plate protected by the bottom plate from the substrate, reducing top plate parasitic capacitance [36].

$$C = \frac{\varepsilon A}{t_{ox}} \tag{2.6}$$

21

**MOM capacitors**, in contrast, are built using standard metal interconnect layers. As a result they can be utilised in any CMOS process. They can also be custom made as parasitic elements in the layout, while only being limited in size by the metal width and metal spacing design rules of the interconnect layers [33].

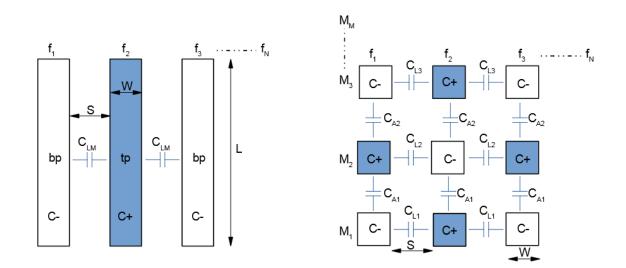

Figure 2.3 Plan View of MOM Capacitor

Figure 2.4 Cross-Section of MOM Capacitor

Structure

Structure

The two figures above show the mechanism by which capacitance is created in a MOM capacitor with most of the capacitance between the interdigitated fingers on each metal layer and a lesser amount vertically between the layers. A smaller spacing gives higher capacitance per unit area but increases mismatch according to Pelgrom's law and is also limited by design rule lower spacing limits. The total capacitance can also be increased by increasing the number of fingers, length of fingers or number of metal layers in the MOM capacitor. Using BSIM4 models for the MOM capacitor it was decided to use a finger spacing of 0.07  $\mu$ m and finger width of 0.08  $\mu$ m. These were chosen as a balance between lower mismatch and lower parasitic capacitance from the area of the device.

MOM capacitors were chosen as the unit capacitor design for the CDAC in this project because it was required to build the ADC with standard (digital) CMOS, without any extra process steps being required. It was decided against using MIM capacitors because of the dedicated metal layers required and the lower size limits imposed on them, with the intention of creating a 15 fF unit capacitor. Initially, a full custom MOM capacitor design was used because of the obvious advantages of having reduced sizing limitations. However, this was later changed to a TSMC supported MOM unit capacitor (layers 3-5) with customized outer layers because of matching concerns and less design complexity, with the advantage of being able to separate the capacitance of the MOM layers from the parasitic capacitance of the extra metal layers and the routing when running parasitic extractions. The MOM capacitor used metal 3, 4 & 5 with an interdigitated structure. Four MOM capacitors were instantiated in parallel to create the unit capacitor.

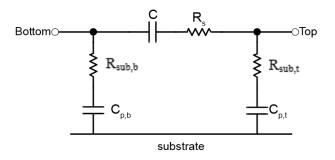

The model below shows the parasitic capacitance and resistance between the bottom and top plates to the substrate. The top plate is the sensitive node because the parasitic capacitance causes a gain error, while the bottom plate parasitic capacitance merely adds extra loading to the reference signal. It is, therefore, a priority to protect the top plate from the substrate to reduce top plate parasitic capacitance.

Figure 2.5 MOM Capacitor Parasitic Model

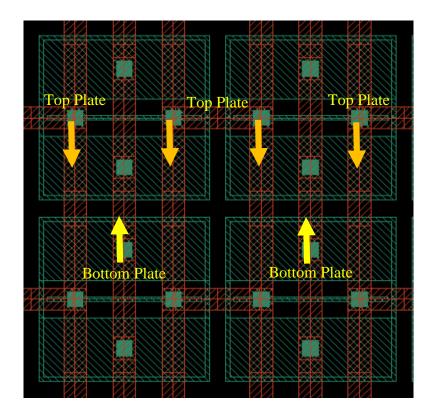

The figure below shows the interdigitated design of the unit capacitor for each metal layer with both plates of the capacitor clearly illustrated.

Figure 2.6 Unit Capacitor

The vias between the three MOM layers in the unit capacitors can clearly be seen as coloured boxes in the figure above. Having a large amount of them around the perimeter of the capacitor helps shield the charge on the capacitor by acting as a Faraday cage and decreases the inter-layer resistance by having multiple parallel conductive paths. Each MOM capacitor has 12 fingers, giving 24 fingers on the top and bottom half of the unit capacitor. The top plate runs along the middle of the unit capacitor, with fingers running vertically up and down. These interlink with the vertical fingers coming from the bottom plate, which surrounds the unit capacitor. In this configuration the top plate is protected

from all sides by the bottom plate and top plate parasitic capacitance is reduced. A solid metal 2 layer, connected to the bottom plate also shields the top plate of the capacitor from the substrate to minimize the parasitic capacitance between the top plate and the substrate.

Figure 2.7 Metal 6 Layer in Unit Capacitor

The metal 6 layer was added to the unit capacitor to provide additional layer-layer capacitance and, more importantly, to shield the top of the capacitor in the same way as the vias shield the sides. The top and bottom plates are brought up from metal 5 by the yellow vias in the figure above and the turquoise vias bring the top and bottom plates up to the metal 7 routing, which will be discussed in the following section.

Figure 2.8 Unit Capacitor Showing Metal 6, Metal 1 & Metal 8

The blue cross in the figure above is metal 1 and is placed in the unit capacitor for density purposes. A purple metal 8 square is placed on top of the capacitor for metal density purposes and as a shield to prevent coupling to the PCB (printed circuit board) in this flipchip design. It is disconnected electrically from the unit capacitor. Metal 8 couldn't be included in the unit capacitor because the minimum size is too big to use as a capacitor and it is placed too close to potential coupling sources to risk connecting to the capacitors. Metal 3-5, the MOM layers are hidden from this figure for clarity, as is the metal 2 layer. The metal 2 layer is the same shape as the M3-M5 layer, with the same interdigitated fingers but it is all connected together on the bottom plate node, which feeds up to metal 3 bottom plate using multiple vias. M6 and M7 are low resistance, thick metals which make them suitable for routing purposes.

# 2.5 Bridge Capacitor

A bridge capacitor carries out a very important function in a capacitive DAC. A capacitive array with a bridge capacitor is also known as a split capacitor array, due to the array being split into two parts. This design allows for larger unit capacitors, which improves matching. It increases speed, and has similar INL and decreased DNL in comparison to a regular binary-weighted capacitor array [37]. Implementing a split capacitor array has the benefit of decreasing the area and power consumption of the CDAC, while keeping the number of bits the same. This is implemented by using the same unit capacitor on each side of the bridge capacitor and doubling in size with each successive bit. Depending on where the bridge capacitor is located, the area can be vastly reduced, in an exponential relationship going from one end of the array to the middle of the array.

Ultimately, the size of the MSB capacitor can be decreased massively without having to have an LSB so small that it suffers from mismatch [32] and thermal noise. For higher resolution DACs, this gives a great balance between greater accuracy, with lower power consumption and area. The bridge capacitor is also known as an attenuation capacitor because it attenuates the voltage from every capacitor on the LSB side of the CDAC. This is because it is in series with the LSB capacitors [38]. I was decided to incorporate a split capacitor DAC in this design because a non-split capacitor 10-bit DAC would not have been able to satisfy the area limitation of the chip, while providing adequate accuracy.

The equivalent charge model of the split capacitor DAC is shown below with the mathematical derivations showing the relationship between the output voltage on the DAC and the individual capacitor values.

Figure 2.9 Equivalent charge flow diagram of Split Capacitor DAC

Note  $C_{LSBx} + C_{LSBg} = C_{LSB}$  and  $C_{MSBx} + C_{MSBg} = C_{MSB}$

$$v_{out} = \frac{V_{refp} \left( C_{MSBx} + \frac{C_{LSBx} C_B}{C_{LSB} + C_B} \right)}{C_{MSB} + \frac{C_B C_{LSB}}{C_{LSB} + C_B}} , \qquad assuming \ V_{refn} = 0 \ V \tag{2.7}$$

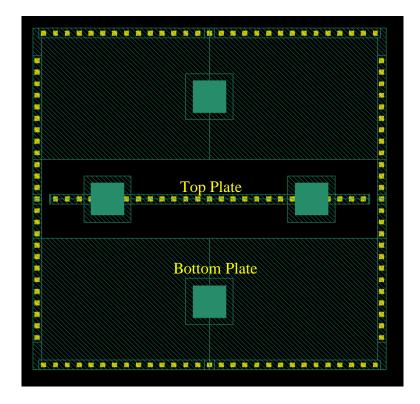

This general formula provides a useful way of modeling the effect of a badly sized bridge capacitor on MATLAB<sup>®</sup> and the effect of top plate parasitic capacitance to ground on both the LSB and MSB arrays. It enabled the decision to orientate the bridge capacitor with the bottom plate connected to the LSB side of the CDAC because the higher parasitic capacitance to the substrate on the bottom plate has less of an effect on the output voltage. This is due to the bridge capacitor attenuating the LSB gain error. See Appendix A, section 6.1 for the full mathematical derivation of the formula.

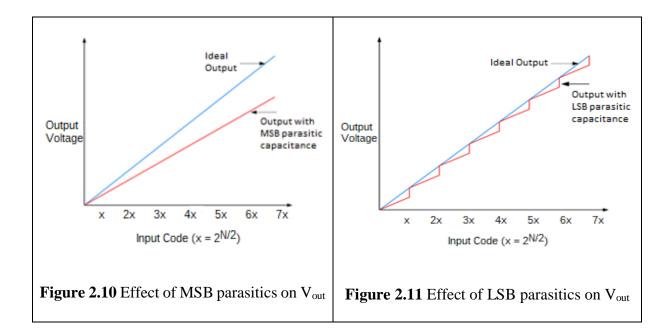

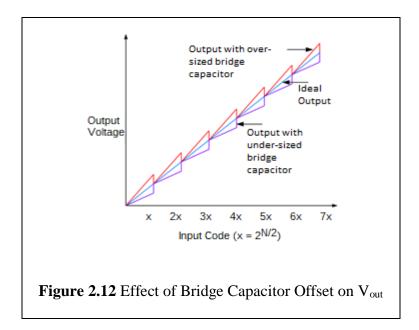

As seen on figure 2.10, MSB parasitic capacitance simply causes a gain error to the output voltage. However, as seen on figure 2.11 and 2.12 above, a common problem associated with the split capacitor design is that the top plate parasitic capacitance on the LSB side of the capacitor array and the fractional value of the bridge capacitor both add uncertainty

in the output voltage of the LSB array, which limits the overall accuracy of the CDAC [39]. It is therefore very important to minimize LSB top plate parasitic capacitance to ground and bridge capacitor offset. Initially a 12 bit split 6:6 capacitor DAC was implemented but it was later reduced to 10 bit with an 8:2 split. Having the two bits on the LSB side of the bridge capacitors minimized the effects described above. Interesting resolutions to the matching problem of the fractional bridge capacitors were described by Agnes et al. in [40] who replace the fractional bridge capacitor with a unit bridge capacitor (which suffers from constant gain error) and Chen et al. in [41] who pick a bridge capacitor that is slightly larger than the required value. This can then be compensated for by a tunable ballast capacitor on the LSB array. For layout matching purposes, it was decided to use a  $2*C_{unit}$  bridge capacitor. This didn't add a gain error because of the extra redundancy on the LSB array, which will be explained in the next section.

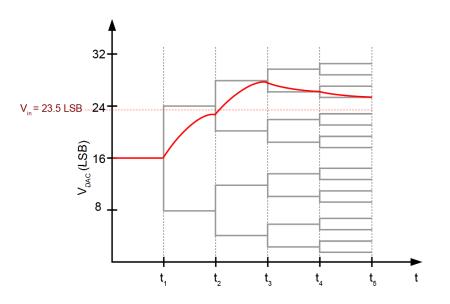

#### 2.6 Redundancy

Redundancy provides an alternative way of mitigating the impact of settling errors in a capacitive DAC [42]. The SAR algorithm uses the overlapping steps due to redundancy to allow comparison decision errors to be digitally corrected [43]. The sampling rate imposes strict time constraints on the settling time of the DAC designed in this project and redundancy aided in alleviating the settling requirements in the bit cycling up to the redundant capacitor present in the capacitive array. This is important because the redundancy was most effective for the larger capacitors which required the most time to settle and this factored in the decision to place a 16C redundant capacitor in the MSB array. The redundancy in the LSB array helped with the bit decisions for the smallest capacitors, which were critical decisions to the final accuracy of the CDAC. Without

redundancy MSB capacitors before the redundant capacitor would have to settle to 10 bit accuracy but with redundancy they only have to settle to 6 bit accuracy, while maintaining the same overall accuracy in the SAR ADC. This relaxes the buffer settling specifications discussed in section 3.4.

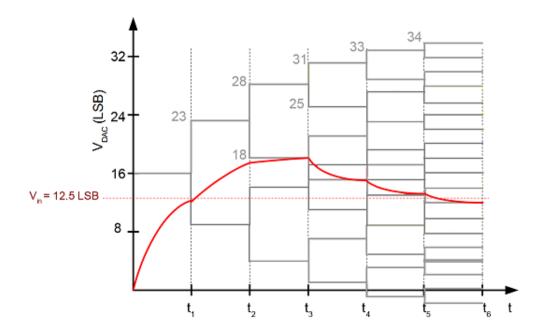

The time trellis diagrams for a SAR with and without redundancy shown below describe how redundancy accommodates for incomplete settling during the bit trials in a 5 bit DAC. Without redundancy, if the settled value is below its actual value an incorrect comparison will be made that cannot be resolved in later trials. The first diagram shows that there is no margin for settling errors without redundancy but the second diagram shows that subsequent cycles can correct for errors in previous cycles, due to overlap in later cycles [29].

Figure 2.13 Time Trellis of Bit Trials without Redundancy

Figure 2.14 Time Trellis of Bit Trials with Redundancy

An additional comparison cycle is required for redundancy compared to the number of bits in the ADC but, crucially, absorbs errors introduced in previous decisions by allowing multiple trajectories to arrive at the final decision, as shown in Figure 2.13 and 2.14. This will be critical in this design to help correct for incomplete settling in initial bit decisions, even with the extra time taken from an additional comparison cycle.

# 2.7 Capacitor Routing

The top plate and bottom plate routing was a critical design challenge, impacting crucially on the matching of the individual capacitors in the DAC. Routing between individual capacitor arrays was all done on metal 7. Initially, the top plate was routed through metal 8 but this ran the risk of coupling to the substrate, affecting the linearity of the DAC. The final routing layout on metal 7 is illustrated in the figure 2.15. One vertical strip runs down the middle, connecting the bottom plate of every unit capacitor in a column to the reference switches below the DAC. The top plate routing runs down every active capacitor in each column in two vertical strips. They are placed at either side of the bottom plate routing in order to connect each column horizontally as shown. Having a uniform routing network, with every capacitor having the same horizontal routing, minimized mismatch in the capacitor array.

Figure 2.15 Top plate and Bottom plate routing

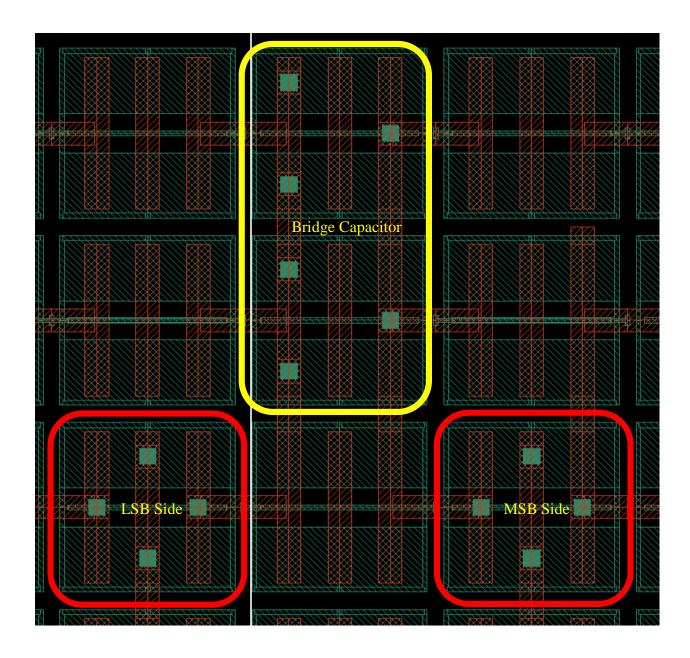

The placement and routing of the bridge capacitor was very important to ensure good matching and minimize gain errors due to parasitic capacitance. It was implemented as two unit capacitors with bottom plates connected in parallel to the top plate of LSB array and the top plate connected in parallel to the top plate of MSB array as shown in figure

2.16. It was placed above the 1C capacitors in both arrays to minimize extra parasitic capacitance and keep the matching at its optimum.

Figure 2.16 Bridge Capacitor Routing

#### 2.8 DAC Schematic

The specific design of the CDAC is then shown in a single ended format, for ease of explanation, in the following figure. The bridge capacitor used in the DAC and its exact placement in the array had a big effect on the overall performance of the DAC and had to be carefully placed to achieve the required specifications. Redundancy was used in this capacitive DAC array and implemented in the LSB side of the array as a 2C column and in the MSB side as an extra 16C column. This allowed a more relaxed settling requirement in the larger MSB decisions. The layout structure is explained in the next section, with emphasis on achieving optimum matching between individual capacitors in the capacitor array, to achieve the schematic implantation shown in the figure below. The signal is first sampled onto the capacitor bottom plates and then transferred to the top plate. Half of the capacitors are switched to  $V_{refp}$  or  $V_{refn}$  depending on the comparator decisions. By only having the top plate switch active during Reset mode to connect  $V_{cm}$  to the top plate and then connecting the bottom plate to  $V_{in}$  during sampling, noise from  $V_{cm}$  is eliminated.

Figure 2.17 Single Ended CDAC Implemented in SAR ADC

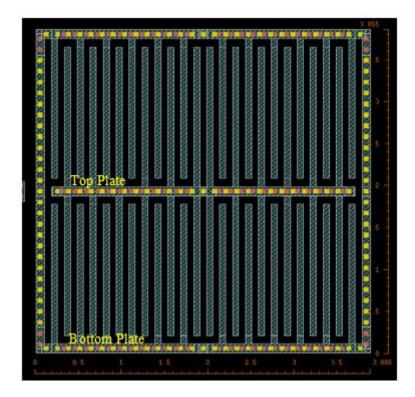

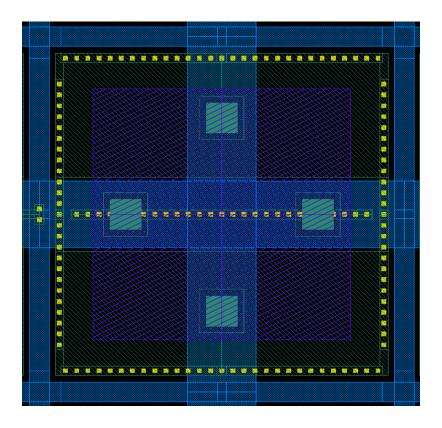

# 2.9 DAC Layout Structure

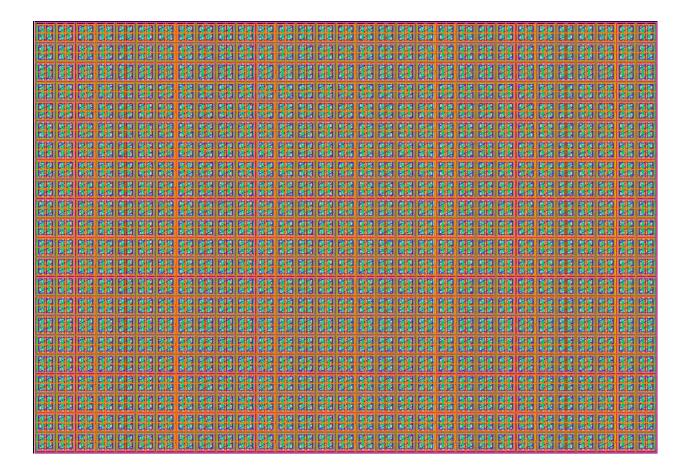

The layout structure is a very important consideration for capacitive matching and for routing logistics. The MSB capacitor was split into 8 16C columns for easier routing and to allow Dynamic Element Matching (DEM) [44] to be added. The Common Centroid is a popular approach used to mitigate systematic offsets due to process gradients [31]. This approach was trialed but didn't suit the particular design because the matching in the 16 columns of 16C capacitors was best when the devices were together in a block. Splitting them caused more 16C columns to experience less parasitic coupling capacitance due to being exposed to more dummy capacitance. In addition, the smaller capacitor columns, which were placed in the middle of the 16C columns, now had a disproportionate amount of extra coupling capacitance, increasing mismatch between the devices. The asymmetric split capacitor design also made it unsuited to a common centroid approach. The capacitor columns were all placed flat at the bottom to reduce mismatch caused by the coupling capacitance of the extra routing. Three layers of dummy capacitors were placed around the perimeter of the array to provide uniformity and reduce systematic mismatch.

|   |   |   |   |    |     |   |   | Bridge |   |    |    |    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |   |   |   |

|---|---|---|---|----|-----|---|---|--------|---|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|

| - | D | D | D | 2C | 2C  | С | С | 2C     | С | 2C | 4C | 8C | 16C | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | С   | С   | С   | С   | С   | С   | С   | С   | С   | С   | С   | с   | С   | С   | С   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | С   | С   | С   | С   | С   | С   | С   | С   | С   | С   | С   | с   | С   | С   | С   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | с   | С   | С   | С   | С   | с   | с   | С   | с   | с   | с   | с   | с   | с   | с   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | с   | С   | С   | С   | С   | с   | с   | С   | с   | с   | с   | с   | с   | с   | с   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | с  | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | с  | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | с   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | c  | c   | c   | c   | c   | с   | с   | с   | c   | c   | c   | c   | c   | c   | c   | c   | c   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | c  | c   | c   | c   | c   | с   | с   | с   | c   | c   | c   | c   | c   | c   | c   | c   | c   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | с  | с  | c   | c   | c   | c   | с   | с   | с   | c   | c   | c   | c   | c   | c   | c   | c   | c   | D | D | D |

|   | D | D | D | D  | D   | D | D | c      | D | D  | c  | c  | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | D | D | D |

|   | D | D | D | C  | C   | D | D | c      | D | C  | c  | c  | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | c   | D | D | D |

|   | D | D | D | c  | C C | C | 6 | D      | C | c  | c  | c  | c   | C C | c   | ĉ   | C C | c   | c   | c   | c   | c   | c   | c   | ć   | c   | C C | c   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D | D | D |

|   | D | D | D | D  | D   | D | D | D      | D | D  | D  | D  | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   | D | D | D |

| Ľ | U | J | U | U  | 0   | U | 0 | U      | U | J  | U  | J  | J   | J   | U   | J   | J   | J   | J   | U   | J   | J   | J   | J   | J   | J   | J   | J   | J | J | U |

Figure 2.18 Illustration of CDAC Layout Structure

# 2.10 Top Level DAC Layout

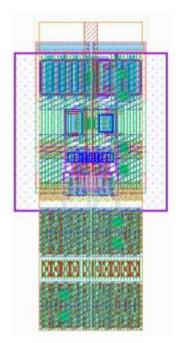

The figure below shows the top level layout of the DAC capacitive array.

Figure 2.19 Top Level Layout of CDAC

#### 2.11Break Before Make (BBM) Circuit

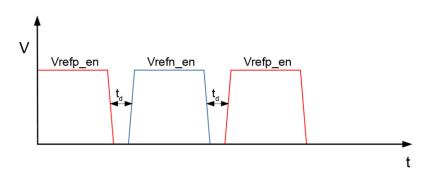

A BBM circuit is used when it is necessary to switch a signal path between two different sources. It enables the original signal path to be opened before closing the signal path of the new source. This prevents the signal sources from short circuiting across to each other. In the design of the CDAC it carries out an important function, preventing the positive and negative reference voltages, vrefn and vrefp respectively, from being connected to the bottom plate of the capacitors at the same time. If the positive and negative references happened to short circuit together the current spikes caused would increase the reference settling time. The figure below illustrates the function of the BBM for creating a delay between the switching of the positive and negative references.

Figure 2.20 BBM Timing Diagram

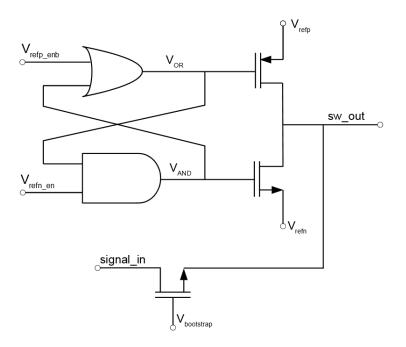

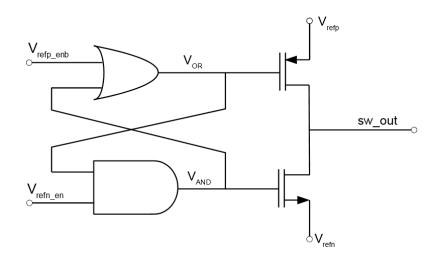

Figure 2.21 shows the BBM and switches circuit that is used for the MSB capacitors where sampling occurs. Due to the fact that the bottom plate of each capacitor column in the CDAC array is switched separately to the positive and negative references, this requires a separate BBM circuit for each column. No BBM is added to the input signals at the SAR controller ensuring that the DAC reference switches are open when this switch is closed.

Figure 2.21 BBM circuit for MSB columns

The BBM for the LSB capacitors in Figure 2.22 is similar but doesn't connect the input signal to the output of the switches because sampling doesn't take place on those capacitors.

Figure 2.22 BBM circuit for LSB columns

The BBM circuit was implemented using CMOS NAND and NOR gates in series with inverters to create the AND and OR gates shown above [45]. The output switches shown above are PMOS and NMOS switches, with the minimum possible length and width sized to have a maximum time constant of 50ps across all corners. This is because it takes 4 time constants to fully charge an RC load. With a sampling time of 200ps and a capacitance of about 250 fF on each of the biggest columns the ON resistance of each switch is calculated as follows:

$$R = \frac{\tau}{C} = \frac{50 \times 10^{-12}}{250 \times 10^{-15}} = 200 \ \Omega \tag{2.8}$$

The layout for the break before make circuit and switches is shown below in Figure 2.23:

Figure 2.23 Layout of BBM and Switches

## 2.12 Summary

This chapter discussed the 10-bit split capacitive DAC structure chosen for this design. It also addressed the issue of offset and mismatch and how it would be mitigated in this design. The decision to choose a MOM capacitor design and the unit capacitor sizing and design methodology was described, followed by the overall array with routing and the impact it had on capacitive mismatch. The benefits of redundancy were discussed for this particular design with its sampling time limits. Finally, the final schematic and layout designs were illustrated and the break before make circuits that interface with the DAC.

# **3** Reference Buffer Design

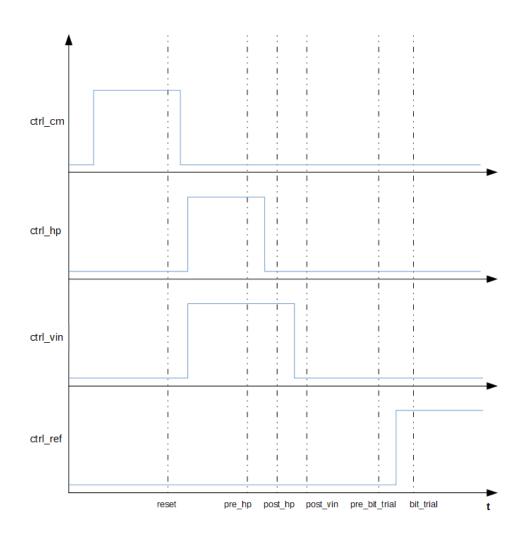

The role of the reference buffer is crucial in maintaining the accuracy of the SAR ADC. It is designed to provide a stable and repeatable voltage reference for the CDAC during conversion. The reference voltage is required to be  $0.9 \text{ V} \pm 1\%$ , with low noise levels.

# 3.1 Voltage Reference Loading

The switched capacitors in the DAC provide a dynamic load to the voltage reference, requiring the reference to handle time varying (transient) currents and to settle to a steady state value between each switching instant, during conversion. During sampling, the CDAC is connected to the input of the ADC, and a charge proportional to the voltage input is held on its capacitors. The DAC is disconnected from the input before conversion starts and the conversion algorithm then successively switches each bit to the voltage reference or ground. This switching causes current to be sourced from or sunk by the reference. The charge required, and therefore the current, is proportional to the size of the capacitor being switched in the array [46]. A decoupling capacitor is often placed before the DAC to source and sink the current during the conversion stage and to filter out any noise as well as the ripple of the reference voltage [47].

Figure 3.1 DAC Switching Induced Reference Currents

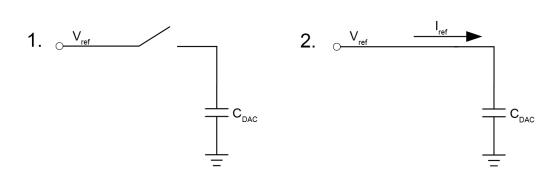

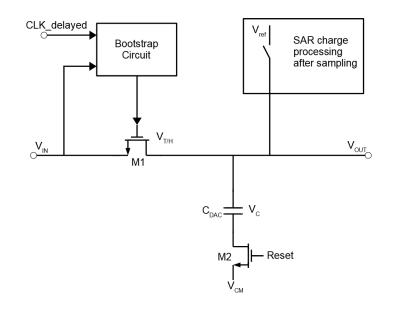

Top plate sampling is used in the SAR ADC in this project. The diagram below illustrates the circuit used to implement this design structure. It is drawn as a single ended circuit for illustration purposes but is mirrored in the real circuit to create a fully differential sampling network with a positive and negative reference voltage.

Figure 3.2 SAR Sampling Network

Initially the capacitors are reset, the top-plate is set to  $V_{cm}$  and, on the bottom plate, half of the total capacitance set to  $V_{refp}$  and the other half set to  $V_{refn}$ . Then the DAC switches open and the sampling switch closes. The signal is sampled onto the DAC top plates. Then the top plate switch opens so no more charge can be added to the capacitors as their top plate is floating. Finally, the bottom plates are set back to  $V_{cm}$ . Half the total capacitance is once again set to  $V_{refp}$  and the other half is set to  $V_{refn}$ . The largest current spike from the reference occurs when half the total capacitance is set to  $V_{refp}$  and half is set to  $V_{refn}$ . Figure 3.3 below illustrates the timing of the switches.

Figure 3.3 Timing diagram for switch circuit

Figure 3.3 shows the timing off switching states in switches for the DAC. The first stage is the reset stage, where all of the switches are inactive other than the top-plate switch (ctrl\_cm). The second stage is the sampling stage, where the helper switch (ctrl\_hp) and bottom plate  $v_{in}$  switch (ctrl\_vin) are active. After this, we see the MSB bit trial stage, where only the  $v_{ref}$  switch is active (ctrl\_ref).

### 3.2 Reference Ringing Problem

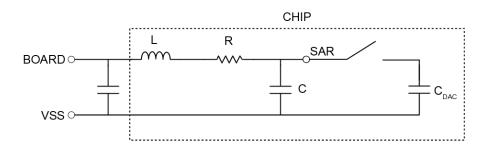

Finite settling limitations of the reference voltage caused by the switching transients of the DAC capacitance could be simply mitigated by having a low impedance from the reference supplies to the input of the DAC with a decoupling capacitor to filter high frequency noise. However another, larger problem is found by using an off-chip (external reference) to drive the DAC. The inherent inductance on the chip package bond wires causes ringing of the reference voltage in response to a current step. Due to the possible oscillations caused by the bond wire inductance, a large external capacitor is not a good solution to this problem [48]. Another option is to use a large on-chip capacitor, at the cost of a lot of area. A flip-chip design was used in this project, which reduced parasitic inductance in the bond wires but not enough to cater for the high levels of accuracy demanded by the project. The board to chip RLC model, which was used for modelling and simulation estimates, is shown in the figure below.

Figure 3.4 Flip Chip Package Model

Using the model in Figure 3.4, the current response over time for the reference was derived in order to characterize the reference response to a voltage step due to switching at the DAC. The voltage response was then found and this derivation allowed the effect of different model parameters on the step response to be determine on MATLAB.

Using Kirchoff's Voltage Law:  $V_{ref,in} - V_L - V_C - V_R = 0$  (3.1)

Assuming  $V_{ref,in}$  is constant in time,

$$V_{ref,in} - L\frac{dI}{dt} - IR - \frac{1}{C}\int Idt = 0$$

(3.2)

Differentiate with respect to time:  $-L\frac{d^2I}{dt^2} - R\frac{dI}{dt} - \frac{I}{C} = 0$

$$\frac{d^2I}{dt^2} + \frac{R}{L}\frac{dI}{dt} + \frac{I}{LC} = 0$$

(3.4)

Assuming a solution in the form,

$$\alpha^2 + \frac{R}{L}\alpha + \frac{1}{LC} = 0$$

(3.5)

$$I = I_0 e^{\alpha t}$$

:

Therefore:

$$\alpha = -\frac{R}{2L} \pm \frac{1}{2} \sqrt{\frac{R^2}{L^2} - \frac{4}{LC}}$$

(3.6)

But time constant,

$$au = \frac{L}{R}$$

(3.7)

And natural frequency,

$$\omega_0 = \frac{1}{\sqrt{LC}}$$

(3.8)

(3.3)

Therefore:

$$\alpha = -\frac{1}{2\tau} \pm i\omega$$

(3.9)

$$\omega = \sqrt{\frac{1}{LC} - \frac{R^2}{4L^2}} \tag{3.10}$$

Where,

The solution of the differential

$$I(t) = I_0 e^{-\frac{t}{2}\tau} \sin(\omega t)$$

(3.11)

equation is then:

But,

$$V_{ref}(t) = V_{ref0} + \Delta V_{ref}(t)$$

(3.12)

And initial current step is:

$$I_0 = \Delta V_{ref}(t)(\frac{1}{\omega C})$$

(3.13)

The transient voltage at the DAC input can be defined as:  $\Delta V_{ref}(t) = I(t)(\frac{1}{\omega C})$ (3.14)

Therefore:

$$V_{ref}(t) = V_{ref0} + I(t)(\frac{1}{\omega C})$$

(3.15)

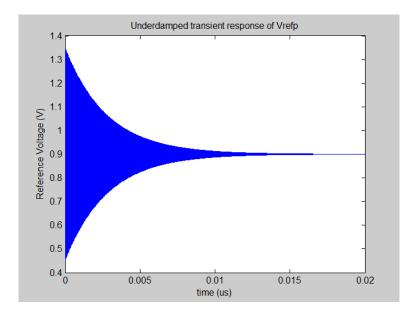

This equation shows the damped step response of the reference current in the RLC circuit, with initial current  $I_0$ , time constant  $\tau$  and damped frequency  $\omega$ . It shows an exponential decay with a sinusoidal oscillation to a step in the current, caused by capacitor switching. The reactive components in the circuit determine the damping coefficient, causing it to either be under-damped, critically damped or over-damped. The MATLAB plots below show the different solutions to this model, given an initial reference voltage of 0.9 V at the input to the DAC and a reference voltage step of 450 mV.

Figure 3.5 RLC Reference Voltage Response with Bond Wire Resistance of  $5m\Omega$

Figure 3.6 Zoomed in graph of Figure 3.4 showing decaying sinusoidal response

The figures above show the expected underdamped response of the reference current to a step on the flip-chip package, with expected parasitic inductance of 70 pH, parasitic resistance of 5 m $\Omega$  and internal decoupling capacitance of 2 pF.

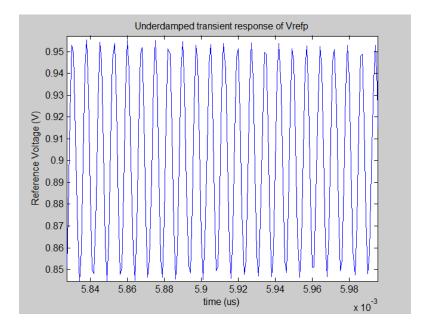

Figure 3.7 RLC Reference Voltage Response with Bond Wire Resistance of  $0.5\Omega$

The plot above shows the expected response of the reference current to a step if the bond wire resistance was increased by 2 orders of magnitude, to 0.5  $\Omega$ . It shows a much higher rate of decay. This illustrates the impact of a low Q, lossy bond wire inductance on the degradation of the reference voltage due to switching induced ringing.

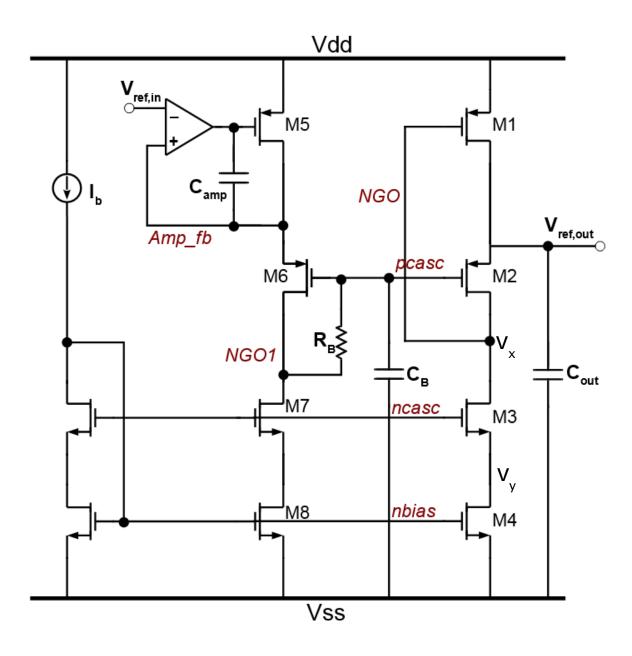

### 3.3 Reference Buffer Solution

Given the impracticality of designing an on-chip capacitance large enough to shunt the low frequency ringing to ground, and the fact that capacitors are not capable of bypassing both low and high frequencies because of the internal resonances in the capacitors themselves [49], it became apparent that a more robust solution was required. These internal resonances occur at high frequency due to the parasitic inductance becoming dominant. Large capacitors have been used as a solution but the charge taken from the capacitor is dependent on the SAR code [26]. A unity gain voltage buffer was chosen to resolve the reference ringing. In principle, it would receive a reference input voltage, and match that DC voltage level at the output. A high input impedance would block any transient signals arriving at the input and a low output impedance would allow a quick response to a switching transient at the output.

Two popular unity gain buffer topologies are compared below:

| Design Metric     | NMOS Source Follower<br>Buffer (Figure 3.8)         | Flipped Voltage Follower<br>(FVF) Buffer (Figure 3.9) |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| Output Impedance  | Higher                                              | Lower                                                 |  |  |  |  |  |  |

| Bandwidth         | Lower                                               | Higher                                                |  |  |  |  |  |  |

| Current Sourcing  | High                                                | Higher                                                |  |  |  |  |  |  |

| Current Sinking   | Limited                                             | Limited                                               |  |  |  |  |  |  |

| Voltage Gain      | Less than unity                                     | Unity                                                 |  |  |  |  |  |  |

| Complexity        | Simple                                              | Complex                                               |  |  |  |  |  |  |

| Voltage Headroom  | V <sub>DD</sub> =V <sub>OUT</sub> + V <sub>GS</sub> | V <sub>DD</sub> =V <sub>OUT</sub> + V <sub>DS</sub>   |  |  |  |  |  |  |

| Power Consumption | Higher                                              | Lower                                                 |  |  |  |  |  |  |

Table 3.1 Source Follower vs. Flipped Voltage Follower

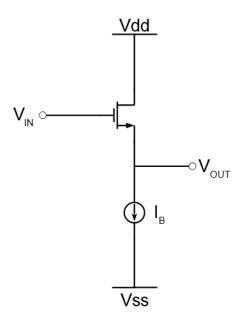

The NMOS source follower follows the input with a dc level shift and is able to source a large amount of current from the load. It is limited in its current sinking capabilities, however, by the biasing current mirror because a current mirror has fixed current and cannot adapt to a changing load. The PMOS source follower, however can sink a lot of current but its current sourcing is limited. The PMOS source follower is capable of a higher output voltage, while the NMOS source follower can set a lower output voltage at the same supply voltage. The FVF topology can source a large amount of current but its current sinking capabilities are limited by its biasing current source [50].

Two of the most important metrics in a voltage buffer are the input and output impedance. The input impedance needs to be as high as possible to block any perturbations at the buffer output, disturbing the reference input to the CDAC from feeding through, and a low output impedance is required to respond quickly to a load. Flipped voltage followers have a lower output impedance than regular source followers due to its shunt feedback dynamically reacting to the output load [51]. A basic source follower requires bigger devices to achieve the same output impedance as an FVF buffer because the output impedance is inversely related to the trans-conductance of the MOSFET and the aspect ratio and bias current must be increased more than the equivalent FVF design to achieve the necessary output impedance value [52].

The non-linearity in the basic source-follower is also worse than the corresponding FVF [51]. Power is directly proportional to supply voltage and an NMOS source follower needs a higher supply voltage than a PMOS source follower or an FVF to achieve the same output voltage.

Figure 3.8 NMOS Source Follower Schematic

Figure 3.9 Flipped Voltage Follower Schematic

The FVF architecture was chosen because of its very low output impedance, compared to a regular source follower buffer as shown on the next page. The amplifier shown in Figure 3.9 is described in Section 3.5.

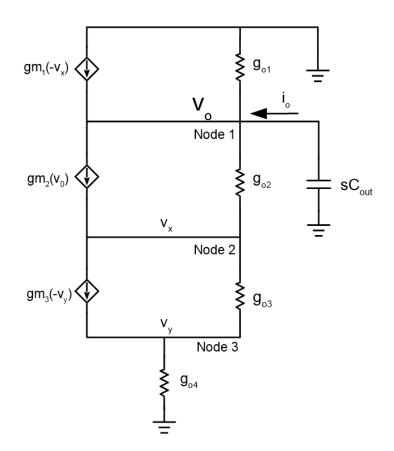

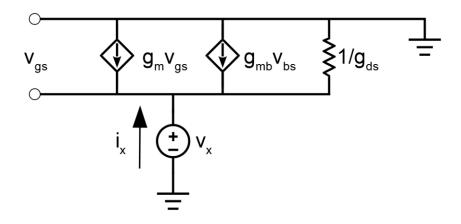

Figure 3.10 FVF Small Signal Equivalent Circuit for Rout

Small Signal Analysis of FVF output Stage to find output impedance:

At node 1:

$$i_o = v_o g_{o1} + (v_o - v_x) g_{o2} + g_{m1} v_x + g_{m2} v_o$$

(3.16)

At node 2:

$$(v_x - v_y)g_{o3} - v_yg_{m3} - v_og_{m2} + (v_x - v_o)g_{o2} = 0$$

(3.17)

At node 3: