| Title                       | Electrical characterization of top-gated molybdenum disulfide field-effect-transistors with high-k dielectrics                                                                                                                                                                           |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Bolshakov, Pavel;Zhao, Peng;Azcatl, Angelica;Hurley, Paul<br>K.;Wallace, Robert M.;Young, Chadwin D.                                                                                                                                                                                     |

| Publication date            | 2017-05-05                                                                                                                                                                                                                                                                               |

| Original Citation           | Bolshakov, P., Zhao, P., Azcatl, A., Hurley, P. K., Wallace, R. M. and Young, C. D. (2017) 'Electrical characterization of topgated molybdenum disulfide field-effect-transistors with high-k dielectrics', Microelectronic Engineering, 178, pp. 190-193. doi:10.1016/j.mee.2017.04.045 |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                  |

| Link to publisher's version | 10.1016/j.mee.2017.04.045                                                                                                                                                                                                                                                                |

| Rights                      | © 2017 Elsevier B.V. This manuscript version is made available under the CC-BY-NC-ND 4.0 license - http://creativecommons.org/licenses/by-nc-nd/4.0/                                                                                                                                     |

| Download date               | 2024-05-07 23:51:00                                                                                                                                                                                                                                                                      |

| Item downloaded from        | https://hdl.handle.net/10468/4062                                                                                                                                                                                                                                                        |

### Accepted Manuscript

Electrical characterization of top-gated molybdenum disulfide field-effect-transistors with high-k dielectrics

Pavel Bolshakov, Peng Zhao, Angelica Azcatl, Paul K. Hurley, Robert M. Wallace, Chadwin D. Young

PII: S0167-9317(17)30190-9

DOI: doi: 10.1016/j.mee.2017.04.045

Reference: MEE 10550

To appear in: Microelectronic Engineering

Received date: 23 February 2017 Revised date: 10 April 2017 Accepted date: 27 April 2017

This is a PDF file of an unedited manuscript that has been accepted for publication. As a service to our customers we are providing this early version of the manuscript. The manuscript will undergo copyediting, typesetting, and review of the resulting proof before it is published in its final form. Please note that during the production process errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

Electrical characterization of top-gated molybdenum disulfide field-effect-transistors with high-

k dielectrics

Pavel Bolshakov<sup>(1)\*</sup>, Peng Zhao<sup>(1)</sup>, Angelica Azcatl<sup>(1)</sup>, Paul K. Hurley<sup>(2)</sup>, Robert M. Wallace<sup>(1)</sup>,

and Chadwin D. Young<sup>(1)</sup>

$^{1}$ Department of Materials Science and Engineering, The University of Texas at Dallas,

800 West Campbell Road, Richardson, Texas 75080, USA

<sup>2</sup>Tyndall National Institute, University College Cork,

Lee Maltings Complex, Dyke Parade, Mardyke, Cork, Ireland

\*Corresponding author, pavel.bolshakov@utdallas.edu

**Abstract**

High quality HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> substrates are fabricated in order to study their impact on top-gate MoS<sub>2</sub>

transistors. Compared with top-gate MoS<sub>2</sub> FETs on a SiO<sub>2</sub> substrate, the field effect mobility decreased for

devices on HfO<sub>2</sub> substrates but substantially increased for devices on Al<sub>2</sub>O<sub>3</sub> substrates, possibly due to substrate

surface roughness. A forming gas anneal is found to enhance device performance due to a reduction in charge

trap density of the high-k substrates. The major improvements in device performance are ascribed to the

forming gas anneal. Top-gate devices built upon Al<sub>2</sub>O<sub>3</sub> substrates exhibit a near-ideal subthreshold swing (SS)

of ~69 mV/dec and a ~10× increase in field effect mobility, indicating a positive influence on top-gate device

performance even without any backside bias.

Keywords: MoS<sub>2</sub>; top-gated transistor; HfO<sub>2</sub>; Al<sub>2</sub>O<sub>3</sub>; high-k; substrate;

#### 1. Introduction

At the moment, transition metal dichalcogenides (TMDs) are one group of 2D materials that is being studied as a possible replacement for the semiconductor channel in future field-effect-transistor (FET) technology that require low power, high mobility devices[1][2][3][4]. Chief among them is molybdenum disulfide (MoS<sub>2</sub>)[5][6], which has some of the earliest studies that report high mobility values (>200 cm<sup>2</sup>/V·s), high  $I_{ON}/I_{OFF}$  ratios (~10<sup>8</sup>), and low subthreshold swing (~74 mV/dec) for top-gate, few-layer MoS<sub>2</sub> devices, usually fabricated on SiO<sub>2</sub>/Si substrates[7]. While recent studies have demonstrated back-gate devices with HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> dielectrics[8][9][10] with high mobility values as a result of the high-k screening effect[11], few have studied the effects of these high-k dielectric substrates ("substrate" = HfO<sub>2</sub>/Si or Al<sub>2</sub>O<sub>3</sub>/Si) on a top-gate devices structure akin to the silicon-on-insulator (SOI) technology in use today.

With high-k materials such as  $HfO_2$  being utilized in current CMOS technology, their integration with TMDs can be advantageous for future applications. One recent bottleneck that has been overcome is the functionalization treatment of the inactive  $MoS_2$  surface using a UV-ozone process that allows a uniform, high-k dielectric to be deposited[12]. With a proven top-gate  $MoS_2$  FET fabrication process[13], an understanding of the effects of the unbiased back-gate dielectric on top-gate device performance is needed. In this paper, we demonstrate and discuss the use of high-k dielectric substrates in conjunction with a forming gas ("FG":5% $H_2/95\%N_2$ ) anneal and their effect on top-gate  $MoS_2$  devices.

#### 2. Experimental

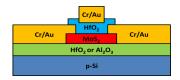

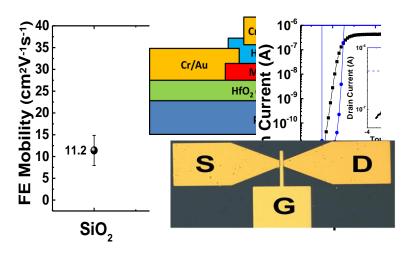

HfO<sub>2</sub> (~10nm) and Al<sub>2</sub>O<sub>3</sub> (~15nm) were deposited onto Si using an atomic layer deposition (ALD) process. Metal-oxide-semiconductor (MOS) capacitors were fabricated and an FG anneal study was performed to achieve an optimal annealing temperature of 400 °C (1 hour) in order to establish the anneal impact on interface traps and achieve high quality dielectric substrates for topgate devices. For the MoS<sub>2</sub> devices, high-k substrates used for the MOS capacitors had MoS<sub>2</sub> exfoliated onto them, with the source and drain patterned using photolithography and Cr/Au (20nm/150nm) deposited in a high-vacuum (10<sup>-6</sup> mbar) evaporation and lift-off process. Afterwards, these back-gate devices were FG annealed at 400 °C, with preand post-anneal I-V measurements. Both sets of MoS<sub>2</sub> devices (HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> substrates) were then functionalized using a 15 minute, in-situ UV-ozone treatment followed by a ALD of 4nm of HfO<sub>2</sub> at 200 °C. This combination of the FG anneal and UV-ozone treatment is done to reduce any residual, process induced contamination from lithography prior to top-gate dielectric formation[14][15][16]. The last step of the process involved the deposition of a Cr/Au top gate using the same process as the source/drain, converting back-gate devices into top-gate, 3-terminal FETs as shown in Fig. 1. C-V and I-V measurements were performed using a Cascade Microtech station in conjunction with a Keithley 4200 SCS and an Agilent E4980A LCR meter.

**Fig. 1.** Cross-section (left) and top-view (right) of the final top-gate device structure.

#### 3. Results and Discussion

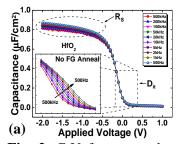

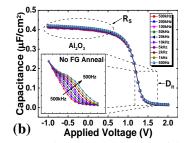

Frequency dependent C-V measurements were performed from 500Hz to 500kHz on  $HfO_2$  and  $Al_2O_3$  capacitors. Fig. 2 shows the low dispersion C-V curves after a 400 °C FG anneal, with the insets showing the high dispersion "hump" before annealing, which is typically attributed to interface traps ( $Q_{it}$ ). While the dispersion in accumulation, typically attributed to series resistance ( $R_s$ ), did reduce slightly after FG annealing, the  $Q_{it}$  was the most impacted by the FG annealing for both  $HfO_2$  and  $Al_2O_3$  as the dispersion is nearly non-existent in the depletion region post anneal.

**Fig. 2.** C-V frequency dependence for (a)  $HfO_2$  and (b)  $Al_2O_3$  capacitors post 400 °C FG anneal with the insets showing high dispersion before annealing.

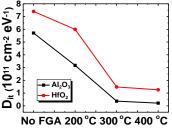

Initially, the FG annealing was performed at 200  $^{\circ}$ C, 300  $^{\circ}$ C, and 400  $^{\circ}$ C, and the C-V measurements were done preand post-anneal. Interface trap density ( $D_{it}$ ) was extracted using Low-High Frequency method[17] with Fig. 3 showing the trend of  $D_{it}$  reduction as a function of FG annealing temperature. While both high-k dielectrics show a major reduction in  $D_{it}$ , the  $Al_2O_3$  appears to have the lowest  $D_{it}$  of 2\*10 cm $^2$ eV $^{-1}$  post 400  $^{\circ}$ C anneal, suggesting an  $Al_2O_3$  substrate may yield a better interface than a  $HfO_2$  substrate for the deposition conditions used.

**Fig. 3.** Interface trap density  $(D_{it})$  extraction shows  $Al_2O_3$  substrates with lower  $D_{it}$  values than  $HfO_2$  substrates as a function of FG annealing temperature.

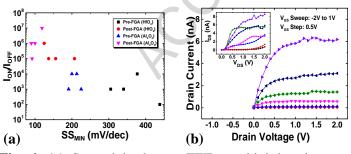

Using HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> substrates, several backgate MoS<sub>2</sub> FETs were fabricated in order to study the effect of the FG anneal on device performance and compare the substrates. As the MoS<sub>2</sub> flakes were untreated[18][19], their thickness was kept relatively the same (~4-5nm) in order to lower variability amongst devices. The I-V characteristics of the devices were measured pre- and postanneal at 400 °C, with the statistics of the SS<sub>MIN</sub> and  $I_{ON}/I_{OFF}$  shown in Fig. 4a. With an average  $I_{ON}/I_{OFF}$  of ~10<sup>3</sup> and  $SS_{MIN}$  of ~365 mV/dec pre-anneal, the performance of the HfO<sub>2</sub> devices improved in all instances with an average  $I_{ON}/I_{OFF}$  of ~10<sup>5</sup> and  $SS_{MIN}$  of ~156 mV/dec post-anneal. For the Al<sub>2</sub>O<sub>3</sub> devices, with an average  $I_{ON}/I_{OFF}$  of ~10<sup>3</sup> and SS<sub>MIN</sub> of ~207 mV/dec pre-anneal and an average I<sub>ON</sub>/I<sub>OFF</sub> of  $\sim 10^6$  and SS<sub>MIN</sub> of  $\sim 100$  mV/dec post-anneal, there was also significant device improvement. This increase in performance can be attributed not only to passivation as a result of the FG anneal, but also to a possible reduction in impurities at the backside MoS<sub>2</sub>/(HfO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub>) interface. It is worth noting that even though the net difference in device improvement was approximately the same, the postanneal performance for devices on Al<sub>2</sub>O<sub>3</sub> substrates was better than for devices on HfO<sub>2</sub> substrates. This may partly be as a result of better adhesion during MoS<sub>2</sub> exfoliation as the Al<sub>2</sub>O<sub>3</sub> substrate yielded a greater number of few-layer flakes than the HfO<sub>2</sub> substrate, possibly due to substrate surface roughness as discussed later in this section.

**Fig. 4.** (a) Several back-gate FETs on high-k substrates pre- and post-anneal indicating a beneficial trend in device performance. (b) I<sub>D</sub>-V<sub>D</sub> characteristics of a back-gate FET pre-(inset) and post-anneal indicates a beneficial effect on the contacts.

There was also a beneficial effect of the FG anneal on the contacts as (Fig. 4b) the  $I_D$ - $V_D$  shows Schottky behavior (inset) pre-anneal and Ohmic behavior post-anneal, potentially reducing the need for sulfur passivation treatments[20][21][22]. While these back-gate devices can be useful to study the effects of the FG anneal, full device evaluation is limited, especially since current CMOS technology does no use this device structure. To properly compare the effect of the  $HfO_2$  and  $Al_2O_3$  substrates, a top-gate FET structure is needed.

Converting from a back-gate to a top-gate FET allows for continuous study of the same  $MoS_2$  flake. The back-gate devices on  $HfO_2$  and  $Al_2O_3$  substrates, already FG annealed at  $400~^{\circ}C$ , all had UV-ozone functionalization treatment followed by in-situ  $HfO_2$  ALD, converting to a top-gate FET with a Cr/Au (20nm/150nm) gate (Fig. 1). These devices were electrically characterized without any back-gate bias and their field effect mobility ( $\mu_{FE}$ ) statistics are shown in Fig. 5, along with those of top-gate devices characterized on  $SiO_2$  substrates. There was ~10× increase in mobility for devices on  $Al_2O_3$  substrates compared to devices on  $HfO_2$  substrates. The  $HfO_2$  substrates appear to have yielded devices with mobility values worse than those of devices on  $SiO_2$  substrates.

**Fig. 5.** Mobility statistics of multiple top-gate FETs shows a  $\sim 10 \times$  improvement in field effect mobility ( $\mu_{FE}$ ) on Al<sub>2</sub>O<sub>3</sub> substrates over HfO<sub>2</sub> substrates.

Comparing the I<sub>D</sub>-V<sub>G</sub> of two best top-gate devices in Fig. 6, the device on a HfO<sub>2</sub> substrate (inset) demonstrates a poor  $I_{ON}/I_{OFF}$  of ~10 and a high  $SS_{MIN}$  of ~1400 mV/dec, while the device on an Al<sub>2</sub>O<sub>3</sub> substrate demonstrates a good  $I_{\text{ON}}/I_{\text{OFF}}$  of  ${\sim}10^6$  and a near-ideal SS<sub>MIN</sub> of 69 mV/dec. Even though the devices on both high-k substrates had good performance as FG annealed back-gate devices and went through the same top-gate conversion, those on Al<sub>2</sub>O<sub>3</sub> substrates showed an improvement while those on HfO<sub>2</sub> substrates became worse as a top-gate device than as a back-gate device. This suggests that for MoS<sub>2</sub>, a high-quality Al<sub>2</sub>O<sub>3</sub> substrate may provide a beneficial effect to top-gate devices under the conditions stated earlier as opposed to HfO2 substrates, with further study required for combinations of top-gate dielectrics and TMDs.

**Fig. 6.**  $I_D$ - $V_G$  for top-gate FETs show a subthreshold swing (SS) from ~1400 mV/dec for a HfO<sub>2</sub> substrate (inset) to a near-deal ~69 mV/dec for  $Al_2O_3$  substrate.

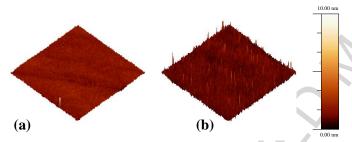

To determine a possible origin of the better device performance on  $Al_2O_3$  substrates than on  $HfO_2$  substrates, atomic force microscopy (AFM) was used to ascertain surface roughness. AFM images shown in Fig. 7 demonstrate the average RMS roughness of the  $Al_2O_3$  substrate to be 0.19 nm, compared to 0.25 nm for the  $HfO_2$  substrate. There are also indications of contaminants on the  $HfO_2$  surface, most likely attributed to carbon residue[23]. The surface roughness of the backside dielectric appears to influence the exfoliated  $MoS_2$  flake size and top-gate device performance.

**Fig. 7.** AFM images of (a)  $Al_2O_3$  substrate and (b)  $HfO_2$  substrate with an RMS roughness value of 0.19 nm and 0.25 nm, respectively.

#### 4. Conclusions

High quality  $HfO_2$  and  $Al_2O_3$  substrates were fabricated for top-gate  $MoS_2$  field-effect-transistors and their impact on device performance was compared. A forming gas anneal was used to reduce the interface trap density and passivate these high-k substrates. The devices on  $Al_2O_3$  substrates demonstrated much better performance compared to those on  $HfO_2$  substrates, possibly due to substrate surface roughness. This suggests a better interface is formed between the  $Al_2O_3$  substrate and the  $MoS_2$  material, leading to a near-ideal substhreshold swing of 69 mV/dec for a top-gate device. This work provides insight into utilizing high-k substrates for top-gate devices in future applications of TMD materials.

#### Acknowledgement

This work was supported in part by the US/Ireland R&D Partnership (UNITE) under the NSF award ECCS-

1407765, and the center for Low Energy Systems Technology (LEAST), one of six SRC STARnet Centers, sponsored by MARCO and DARPA.

#### References

- [1] H.Y. Chang, S. Yang, J. Lee, L. Tao, W.S. Hwang, D. Jena, N. Lu, D. Akinwande, High-performance, highly bendable MoS2 transistors with high-K dielectrics for flexible low-power systems, ACS Nano. 7 (2013) 5446–5452. doi:10.1021/nn401429w.

- [2] S. Das, J. Appenzeller, WSe2 field effect transistors with enhanced ambipolar characteristics, Appl. Phys. Lett. 103 (2013) 103501. doi:10.1063/1.4820408.

- [3] L. Yu, D. El-Damak, S. Ha, X. Ling, Y. Lin, A. Zubair, Y. Zhang, Y.-H. Lee, J. Kong, A. Chandrakasan, T. Palacios, Enhancement-mode single-layer CVD MoS2 FET technology for digital electronics, in: 2015 IEEE Int. Electron Devices Meet., IEEE, 2015: p. 32.3.1-32.3.4. doi:10.1109/IEDM.2015.7409814.

- [4] H. Wang, L. Yu, Y.-H. Lee, W. Fang, A. Hsu, P. Herring, M. Chin, M. Dubey, L.-J. Li, J. Kong, T. Palacios, Large-scale 2D Electronics based on Single-layer MoS 2 Grown by Chemical Vapor Deposition, (n.d.).

- [5] X. Zou, J. Wang, C.-H. Chiu, Y. Wu, X. Xiao, C. Jiang, W.-W. Wu, L. Mai, T. Chen, J. Li, J.C. Ho, L. Liao, Interface Engineering for High-Performance Top-Gated MoS <sub>2</sub> Field-Effect Transistors, Adv. Mater. 26 (2014) 6255–6261. doi:10.1002/adma.201402008.

- B. Radisavljevic, M.B. Whitwick, A. Kis, Integrated Circuits and Logic Operations Based on Single-Layer MoS 2, ACS Nano. 5 (2011) 9934–9938. doi:10.1021/nn203715c.

- B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, A. Kis, Single-layer MoS2 transistors, Nat. Nanotechnol. 6 (2011) 147–150. doi:10.1038/nnano.2010.279.

- [8] J. Kang, W. Liu, K. Banerjee, High-performance MoS 2 transistors with low-resistance molybdenum contacts, Appl. Phys. Lett. 104 (2014) 93106. doi:10.1063/1.4866340.

- [9] T. Li, B. Wan, G. Du, B. Zhang, Z. Zeng, Electrical performance of multilayer MoS 2 transistors on high- κ Al 2 O 3 coated Si substrates, AIP Adv. 5 (2015) 57102. doi:10.1063/1.4919800.

- [10] K.L. Ganapathi, S. Bhattacharjee, S. Mohan, N. Bhat, High-Performance HfO2 Back Gated Multilayer MoS2 Transistors, IEEE Electron Device Lett. 37 (2016) 797–800. doi:10.1109/LED.2016.2553059.

- [11] A. Konar, T. Fang, D. Jena, Effect of high- κ gate dielectrics on charge transport in graphene-based field effect transistors, Phys. Rev. B. 82 (2010) 115452. doi:10.1103/PhysRevB.82.115452.

- [12] A. Azcatl, S. McDonnell, K.C. Santosh, X. Peng, H. Dong, X. Qin, R. Addou, G.I. Mordi, N. Lu, J. Kim, M.J. Kim, K. Cho, R.M. Wallace, MoS2 functionalization for ultra-thin atomic layer deposited dielectrics, Appl. Phys. Lett. 104 (2014) 111601. doi:10.1063/1.4869149.

- [13] P. Zhao, A. Azcatl, P. Bolshakov-Barrett, R.M. Wallace, C.D. Young, P.K. Hurley, Top-gated MoS2 capacitors and transistors with high-k dielectrics for interface study, in: 2016 Int. Conf. Microelectron. Test Struct., IEEE, 2016: pp. 172–175. doi:10.1109/ICMTS.2016.7476201.

- [14] P. Zhao, A. Azcatl, P. Bolshakov, J. Moon, C.L. Hinkle, P.K. Hurley, R.M. Wallace, C.D. Young, Effects of annealing on top-gated MoS 2 transistors with HfO 2 dielectric, J. Vac. Sci. Technol. B, Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 35 (2017) 01A118. doi:10.1116/1.4974220.

- [15] A. Azcatl, S. KC, X. Peng, N. Lu, S. McDonnell, X. Qin, F. de Dios, R. Addou, J. Kim, M.J. Kim, K. Cho, R.M. Wallace, HfO 2 on UV–O 3 exposed transition metal dichalcogenides: interfacial reactions study, 2D Mater. 2 (2015) 14004. doi:10.1088/2053-1583/2/1/014004.

- [16] S. McDonnell, B. Brennan, A. Azcatl, N. Lu, H. Dong, C. Buie, J. Kim, C.L. Hinkle, M.J. Kim, R.M. Wallace, HfO 2 on MoS 2 by Atomic Layer Deposition: Adsorption Mechanisms and Thickness Scalability, ACS Nano. 7 (2013) 10354–10361. doi:10.1021/nn404775u.

- [17] D.K. Schroder, Semiconductor material and device characterization, IEEE Press, 2006.

- [18] R. Addou, L. Colombo, R.M. Wallace, Surface Defects on Natural MoS 2, ACS Appl. Mater. Interfaces. 7 (2015) 11921–11929. doi:10.1021/acsami.5b01778.

- [19] R. Addou, S. McDonnell, D. Barrera, Z. Guo, A. Azcatl, J. Wang, H. Zhu, C.L. Hinkle, M. Quevedo-Lopez, H.N. Alshareef, L. Colombo, J.W.P. Hsu, R.M. Wallace, Impurities and Electronic Property Variations of Natural MoS 2 Crystal Surfaces, ACS Nano. 9 (2015) 9124–9133. doi:10.1021/acsnano.5b03309.

- [20] S. Bhattacharjee, K.L. Ganapathi, D.N. Nath, N. Bhat, Surface States Engineering of Metal/MoS2 Contacts Using Sulfur Treatment for Reduced Contact Resistance and Variability, (2015). doi:10.1109/TED.2016.2554149.

- [21] K. Cho, M. Min, T.-Y. Kim, H. Jeong, J. Pak, J.-K. Kim, J. Jang, S.J. Yun, Y.H. Lee, W.-K. Hong, T. Lee, Electrical and Optical Characterization of MoS 2 with Sulfur Vacancy Passivation by Treatment with Alkanethiol Molecules, ACS Nano. 9 (2015) 8044–8053. doi:10.1021/acsnano.5b04400.

- [22] M. Amani, D.-H. Lien, D. Kiriya, J. Xiao, A. Azcatl, J. Noh, S.R. Madhvapathy, R. Addou, S. KC, M. Dubey, K. Cho, R.M. Wallace, S.-C. Lee, J.-H. He, J.W. Ager, X. Zhang, E. Yablonovitch, A. Javey, Near-unity photoluminescence quantum yield in MoS2, Science (80-.). 350 (2015).

- [23] X. Liu, S. Ramanathan, A. Longdergan, A. Srivastava, E. Lee, T.E. Seidel, J.T. Barton, D. Pang, R.G. Gordon, ALD of Hafnium Oxide Thin Films from Tetrakis " ethylmethylamino...hafnium and Ozone, (2005). doi:10.1149/1.1859631.

**Graphical abstract**

#### Highlights

- Top-gate MoS<sub>2</sub> FETs were fabricated on high-k dielectric substrates

- A forming gas anneal enhances device performance with a reduction in D<sub>it</sub>

- Top-gate devices on Al<sub>2</sub>O<sub>3</sub>/Si showed better performance than on HfO<sub>2</sub>/Si

- AFM images suggest that substrate surface roughness affects device performance