|                      | ,                                                                                                                                                 |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Title                | Novel processes, test structures and characterisation for future germanium technologies                                                           |  |  |  |

| Authors              | Shayesteh, Maryam                                                                                                                                 |  |  |  |

| Publication date     | 2014                                                                                                                                              |  |  |  |

| Original Citation    | Shayesteh, M. 2014. Novel processes, test structures and characterisation for future germanium technologies. PhD Thesis, University College Cork. |  |  |  |

| Type of publication  | Doctoral thesis                                                                                                                                   |  |  |  |

| Rights               | © 2014, Maryam Shayesteh - http://creativecommons.org/<br>licenses/by-nc-nd/3.0/                                                                  |  |  |  |

| Download date        | 2025-06-08 10:49:17                                                                                                                               |  |  |  |

| Item downloaded from | https://hdl.handle.net/10468/1786                                                                                                                 |  |  |  |

# Novel Processes, Test Structures and Characterisation for Future Germanium Technologies

Maryam Shayesteh 108112541

National University of Ireland, Cork

Department of Electrical and Electronic Engineering

Tyndall National Institute

# Thesis submitted for the degree of Doctor of philosophy

September 2014

Supervisor: Dr. Ray Duffy

Head of Department: Prof. Nabeel A. Riza

Research supported by Science Foundation Ireland

# **Table of Contents**

| Abstract                                                                                                                | X   |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| List of Publications                                                                                                    | xii |

| Chapter 1                                                                                                               | 1   |

| Introduction                                                                                                            | 1   |

| 1.1 Motivation and background                                                                                           | 1   |

| 1.1.1 Transistor shrinking challenges                                                                                   | 4   |

| 1.2 Potential replacements for Si                                                                                       | 8   |

| 1.3 New device architectures                                                                                            | 9   |

| 1.4 Challenges for introducing Ge to CMOS technology                                                                    | 11  |

| 1.5 Thesis structure                                                                                                    | 13  |

| Chapter 2                                                                                                               | 15  |

| Contacts on Germanium Devices                                                                                           | 15  |

| 2.1 Introduction                                                                                                        | 15  |

| 2.2 Metal semiconductor contacts                                                                                        |     |

| 2.3 Fermi level pinning                                                                                                 |     |

| 2.3.1 Surface states                                                                                                    |     |

| 2.3.2 Metal induced gap states (MIGS)                                                                                   |     |

| 2.4 State-of-the-art work for contacts to n-type Ge                                                                     |     |

| 2.4.1 Thin insulating layers                                                                                            |     |

| 2.4.2 NiGe optimization                                                                                                 |     |

| 2.4.3 High dopant activation                                                                                            |     |

| 2.4.4 Other interface engineering techniques                                                                            |     |

| 2.5 Contacts on p-type Ge                                                                                               |     |

| 2.6 NiGe contacts made by Rapid Thermal Anneal                                                                          |     |

| 2.6.1 Experimental procedure                                                                                            |     |

| 2.6.2 Results of the electrical characterization                                                                        |     |

| <ul> <li>2.6.2.1 ρ<sub>c</sub> versus P implant dose</li> <li>2.6.2.2 ρ<sub>c</sub> versus choice of implant</li> </ul> |     |

| <ul> <li>2.6.2.2 ρ<sub>c</sub> versus choice of implant</li></ul>                                                       |     |

| 2.7 NiGe contacts made by Laser Thermal Anneal                                                                          |     |

| 2.7.1 Experimental procedure                                                                                            |     |

| 2.7.2 Results of the material characterisation                                                                          |     |

| 2.7.3 Results of the electrical characterization                                                                        |     |

| 2.8 Conclusion                                                                                                          |     |

| Chapter 3                                                                                                               | 53  |

| N-type Dopant Studies                                                                                                   | 53  |

| 3.1 Introduction                                                                                                        |     |

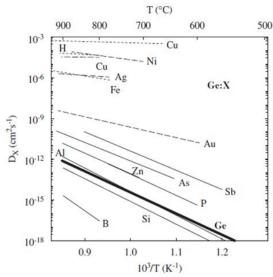

| 3.2 Doping and annealing methodologies                                                                                  | 53  |

| 3.2.1 Laser anneal activation                                                                                           |     |

| 3.2.2 Experimental procedure                                                                                            |     |

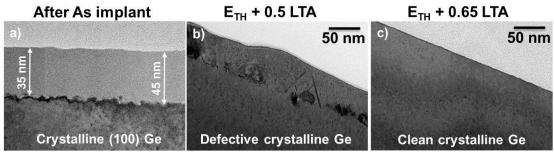

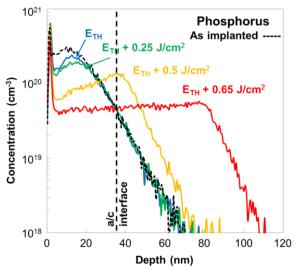

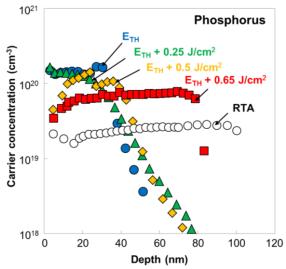

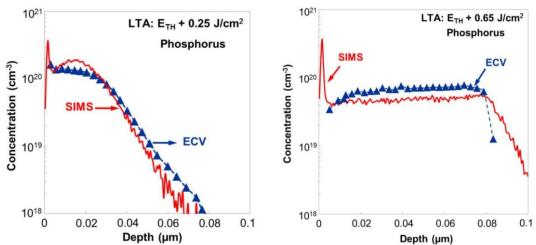

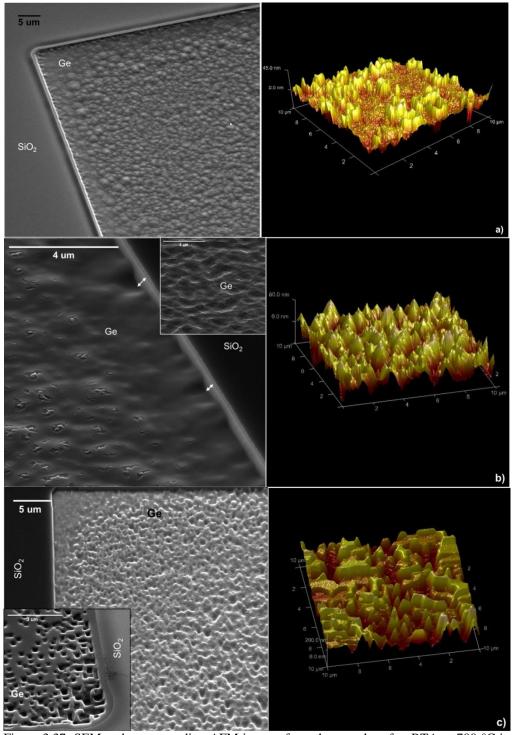

| 3.2.3 Results of the material characterization                                                                          | 59  |

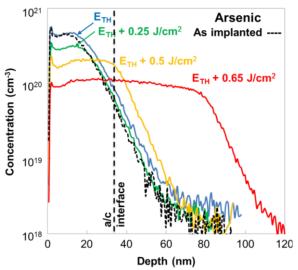

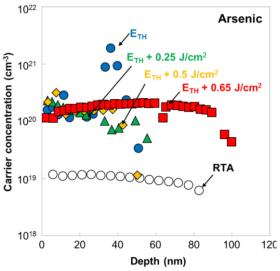

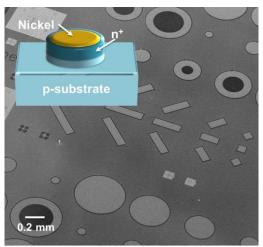

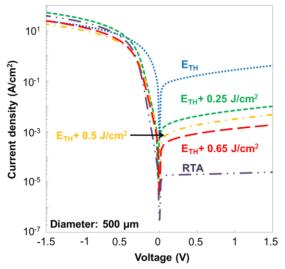

| 3.2.4 Results of the electrical characterization on diodes                                                              | 66  |

| 3.3 Co-implantation                                                               | 74  |

|-----------------------------------------------------------------------------------|-----|

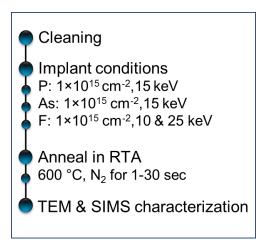

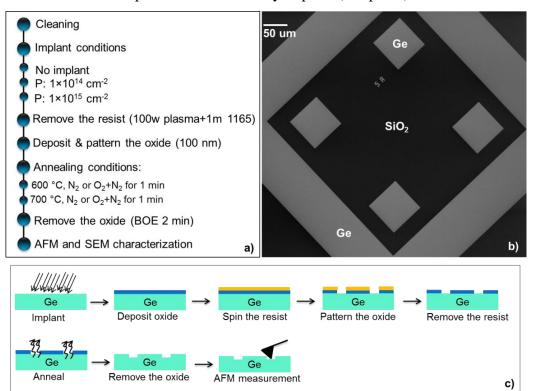

| 3.3.1 Experimental procedure                                                      | 76  |

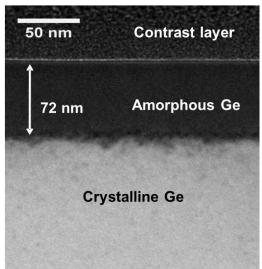

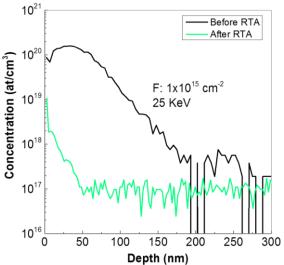

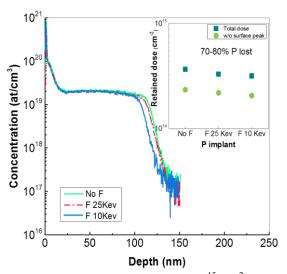

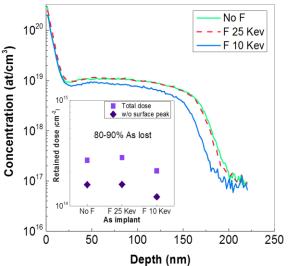

| 3.3.2 Results of the material characterization                                    | 77  |

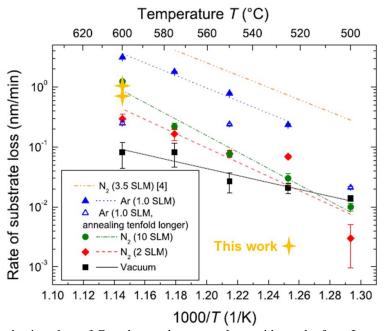

| 3.4 Substrate desorption and dopant outgassing                                    | 81  |

| 3.4.1 Experimental procedure                                                      | 82  |

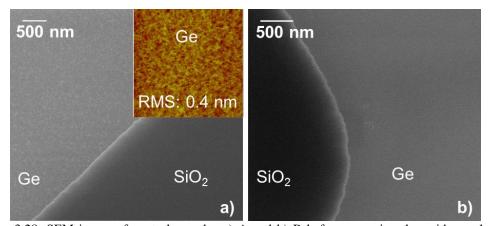

| 3.4.2 Results of the material characterisation                                    | 83  |

| 3.4.2.1 Annealing in N <sub>2</sub> ambient                                       | 84  |

| 3.4.2.2 Annealing in $N_2$ and $O_2$ mix ambient                                  | 86  |

| 3.5 Conclusion                                                                    | 94  |

| Chapter 4                                                                         | 05  |

| Chapter 4                                                                         | 93  |

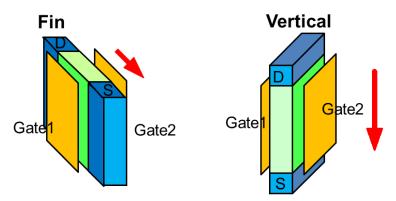

| Fins, Resistors, and Thin Body Devices                                            | 95  |

| 4.1 Introduction                                                                  | 05  |

|                                                                                   |     |

| 4.2 SRIM (The Stopping and Range of Ions in Matter)                               |     |

| 4.2.1 Definitions                                                                 |     |

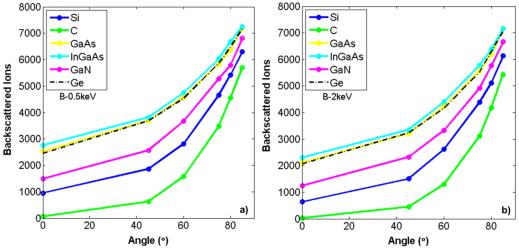

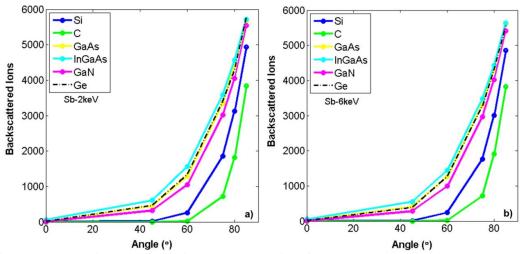

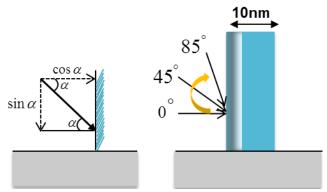

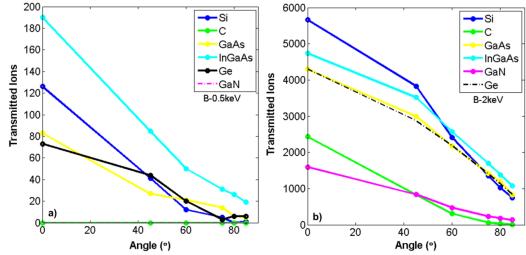

| 4.2.2 Modelling of ion implantation in C, Si, Ge and III-V i 4.2.3 Backscattering |     |

| _                                                                                 |     |

|                                                                                   |     |

|                                                                                   |     |

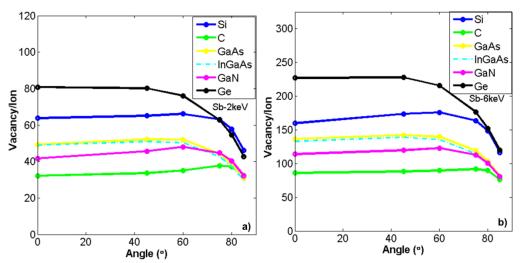

| 4.2.6 Vacancy                                                                     |     |

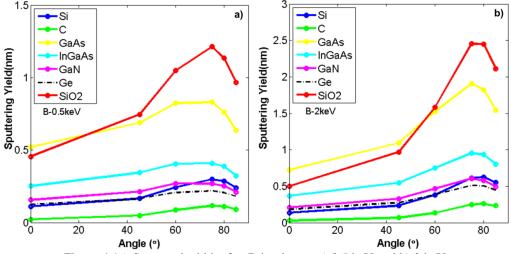

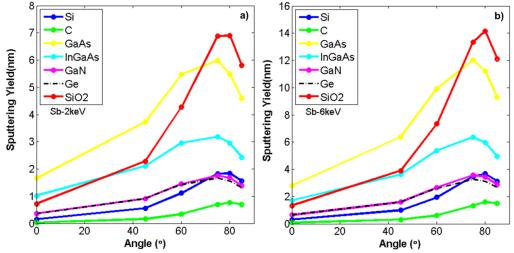

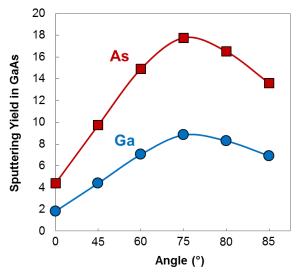

| 4.2.7 Sputtering yield                                                            |     |

| 4.2.8 Limitations of SRIM                                                         |     |

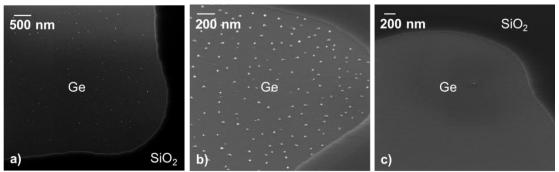

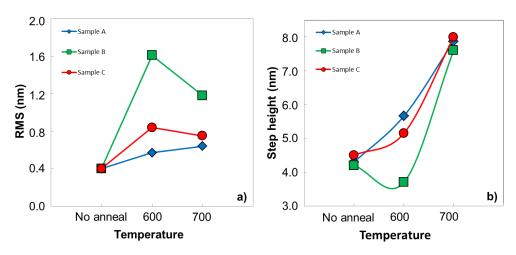

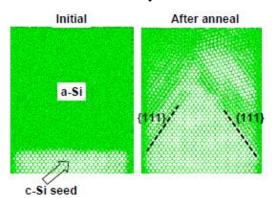

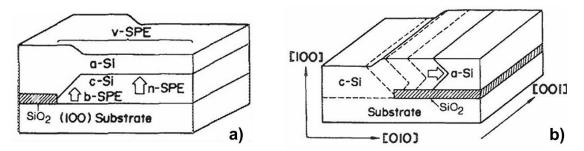

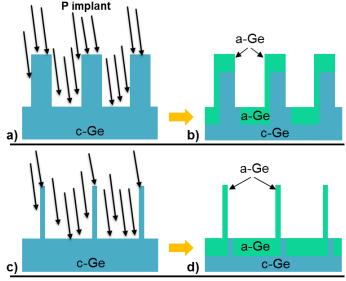

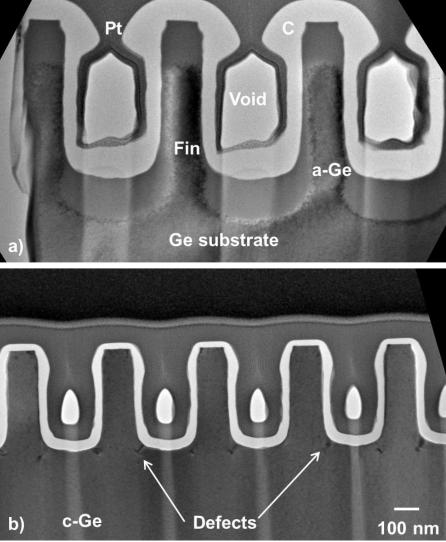

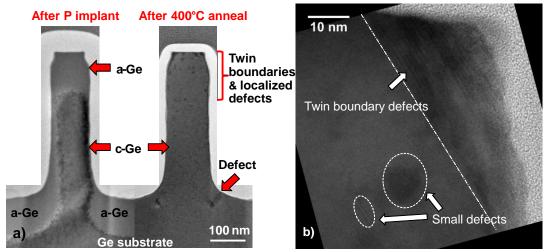

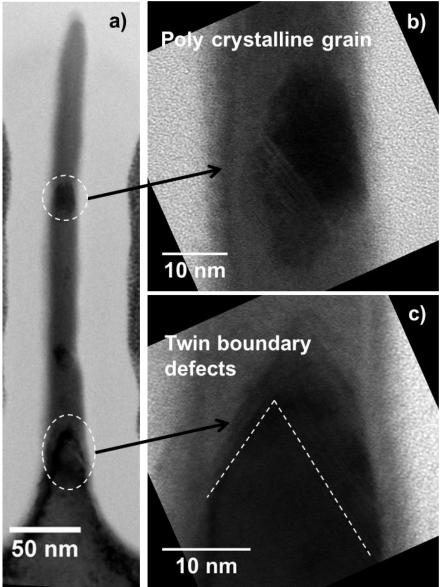

| 4.3 Recrystallization of thin-body Ge structures                                  |     |

| 4.3.1 State-of-the-art work                                                       |     |

| 4.3.2 Experimental procedure                                                      |     |

| 4.4 Non-destructive doping of Ge                                                  |     |

| 4.4.1 State-of-the- art work                                                      |     |

| 4.4.1 State-of-the- art work                                                      |     |

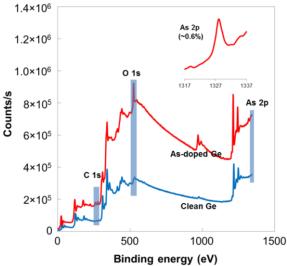

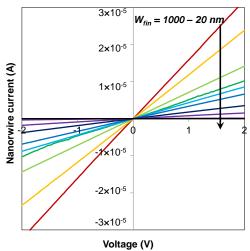

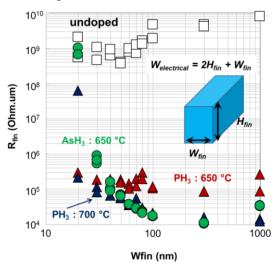

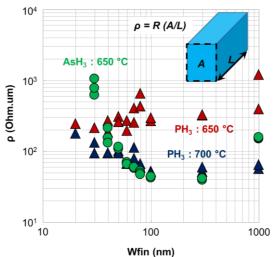

| 4.4.3 Results of the material characterization                                    |     |

| 4.4.4 Results of the electrical characterization                                  |     |

| 4.5 Conclusion                                                                    |     |

|                                                                                   |     |

| Chapter 5                                                                         |     |

| Summary and future work                                                           | 137 |

| 5.1 Summary                                                                       |     |

| 5.2 Future work                                                                   |     |

| 5.3 Contributions and impact of the work                                          | 140 |

| I, Maryam Shayesteh, certify | that this thesis is m | ny own work and I have not                        |

|------------------------------|-----------------------|---------------------------------------------------|

|                              |                       | the basis of the work submitted  Maryam Shayesteh |

|                              |                       |                                                   |

|                              |                       |                                                   |

|                              |                       |                                                   |

|                              |                       |                                                   |

To Masoud, Ryan & my parents

# Acknowledgements

Looking back at the time this PhD started I genuinely believe that I could not have a better chance to follow my dreams, which finally came true through invaluable contribution and help of many people who are engraved on my memory forever.

First and foremost my supervisor Dr. Ray Duffy to whom I am greatly indebted to for his patience, support, and motivation. Not only his immense knowledge and professional guidance but also his unique and caring personality is what I have always appreciated. Every PhD student is well aware of the value of a supervisor who is always reachable and ready to help.

I sincerely thank Dr. Paul Hurley, head of Nanoelectronic Materials and Device group for his guidance, support and encouragement.

I am also very grateful to Dr. Mark van Dal and Dr. Karim Cherkaoui for serving on my dissertation committee and for the knowledge they have imparted to improve my work.

I extend my heartfelt gratitude to Brenda Long for all her support, encouragement, and sincere friendship. Thank you for your scientific contribution in my PhD and also all the happy moments you created over the past years.

I convey my gratefulness to many former and current colleagues, and friends; Anne-Marie Kelleher, Dan O'Connell, Mary white, Alan Blake, Brendan McCarthy, Jim Scully, Ran Yu, Vladimir Djara, Michael Schmidt, Nikolay Petkov, Chris Daunt, Niall Kelly, Patrick Carolan, Marina Manganaro, Agnieszka Gocalinska, Kevin Thomas, Emanuele Pelucchi, Yordan Georgiev, Anushka Gangnaik, Justin Holmes, Brendan O'Neil, and Giuseppe Alessio Vernì.

Hua Yang, Noreen Nudds, and Marc Rensing you made the last couple of years an amazing and unforgettable experience for me. Thank you for being such lovely true friends.

I was privileged enough to collaborate with very knowledgeable and professional scientists to whom I am deeply grateful for their guidance and generous help. Thanks to Karim Huet, and Ines Toque Tresonne at Screen-Lasse, Fuccio Cristiano at university of Toulouse, and Simona Boninelli at University of Catania, Dirch

Hjorth Petersen and Henrik Hartmann Henrichsen at Technical University of Denmark and Peter Folmer Nielsen at CAPRES.

I wish to thank Donagh O'Mahony for patiently supporting and helping me over the past couple of months.

Also thanks to my heroes who happened to be my lovely family; Mahvash, Saeed, Iman and Alireza. Thank you for your endless love, and support encouragement.

And the last but not the least, thank you to my lifelong friend, and beloved Masoud who supported and helped me at every stage of this journey, and Ryan my bundle of joy without whom life would not be as exciting and joyful.

## **Abstract**

Since Si is struggling with fundamental limitations in aggressively scaled devices, new higher mobility materials like Ge and III-V have become of interest as potential replacements in advanced CMOS technology. However with respect to the underlying knowledge and research, these materials seem quite young, compared to Si which has more than 40 years of research behind it. Undoubtedly to be widely used in advanced CMOS devices, the process and integration of these materials has to be well established so that their high mobility benefit is not swamped by imperfect manufacturing procedures.

In this dissertation number of key bottlenecks in realization of Ge devices are investigated;

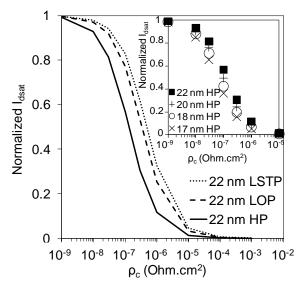

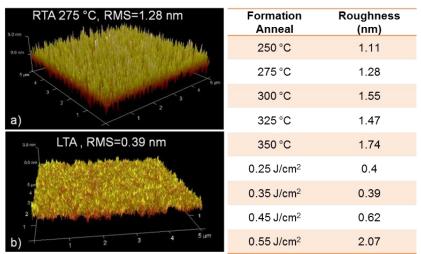

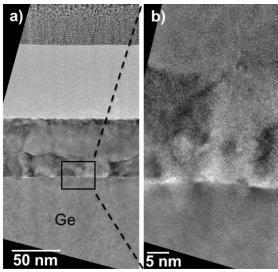

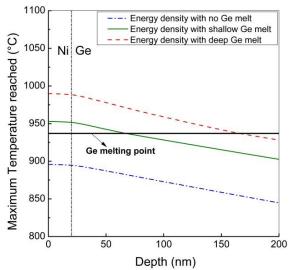

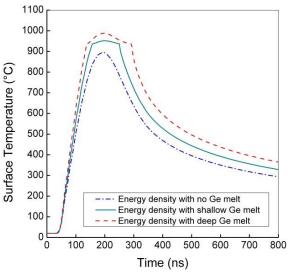

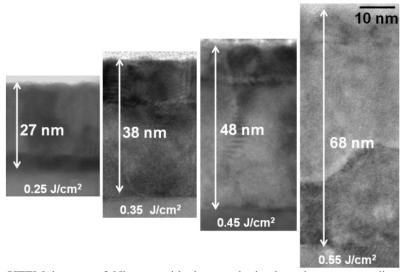

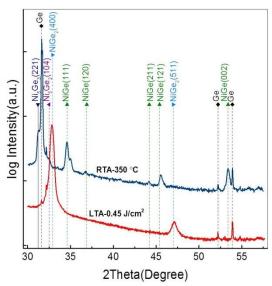

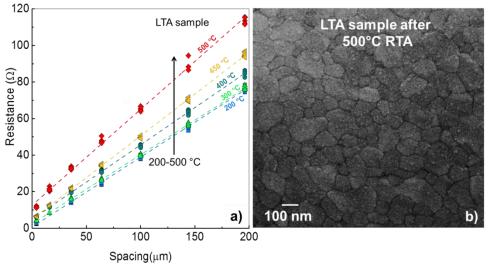

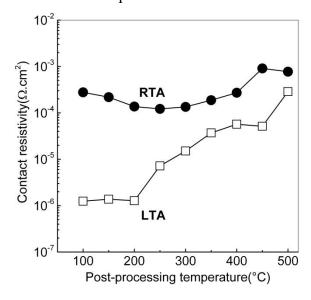

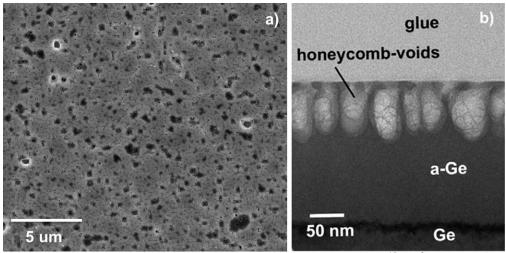

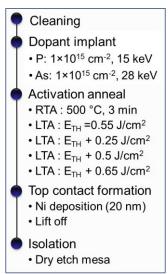

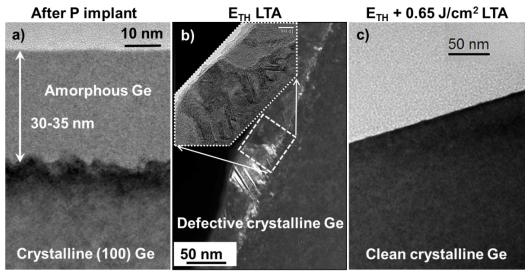

First we address the challenge of the formation of low resistivity contacts on n-type Ge, comparing conventional and advanced rapid thermal annealing (RTA) and laser thermal annealing (LTA) techniques respectively. LTA appears to be a feasible approach for realization of low resistivity contacts with an incredibly sharp germanide-substrate interface and contact resistivity in the order of  $10^{-7} \,\Omega.\text{cm}^2$ . The thermal stability of these contacts has to be carefully addressed.

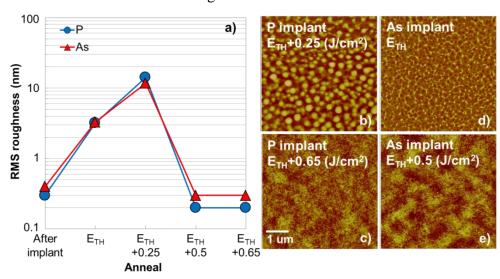

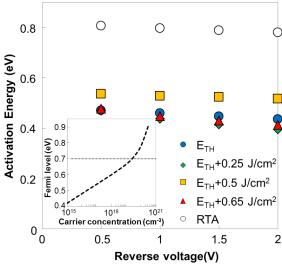

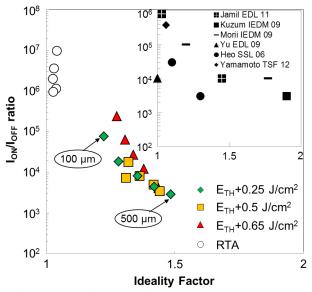

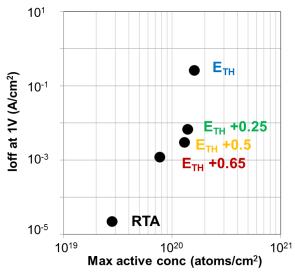

Further obstacles were also studied from a dopant activation level and leakage current point of view, where the influence of RTA and LTA on dopant activation and leakage current suppression in n+/p Ge junction were compared. Providing very high active carrier concentration >  $10^{20}$  cm<sup>-3</sup>, LTA resulted in higher leakage current compared to RTA which provided lower carrier concentration ~  $10^{19}$  cm<sup>-3</sup>. This is an indication of a trade-off between high activation level and junction leakage current. Obtaining high  $I_{ON}/I_{OFF}$  ratio ~  $10^7$  was the main achievement of this study, which to the best of our knowledge is the best reported value for n-type Ge so far.

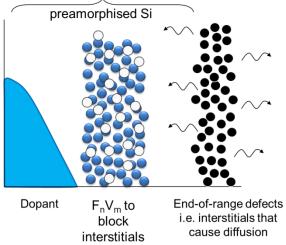

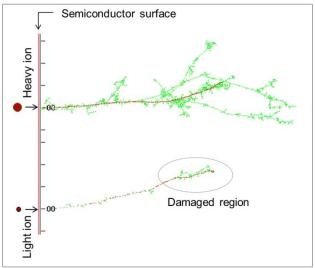

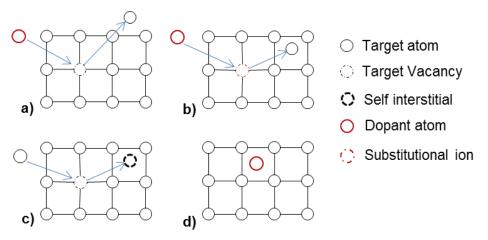

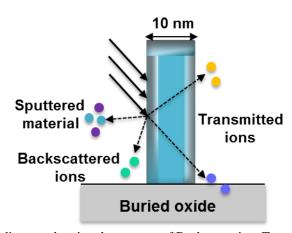

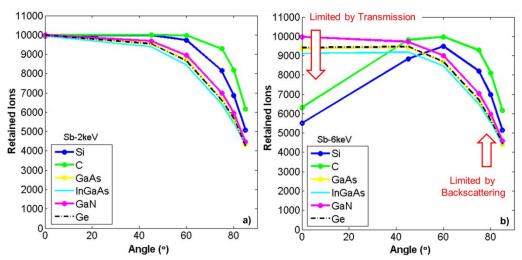

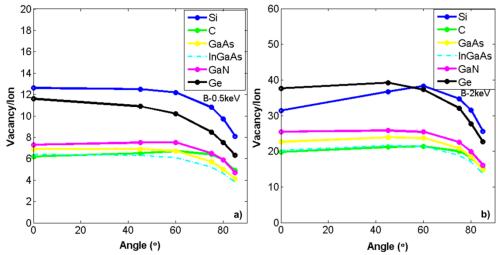

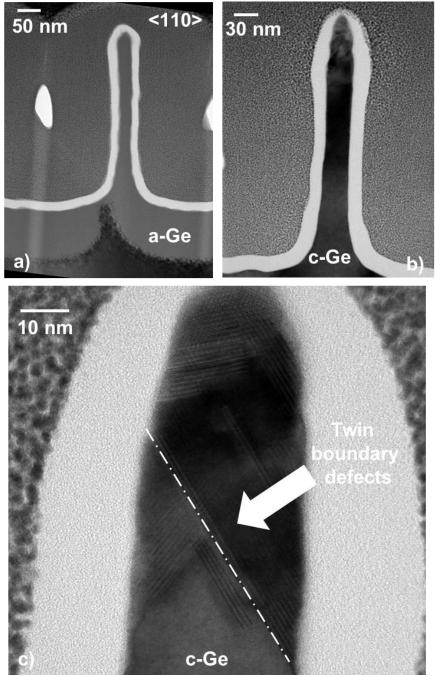

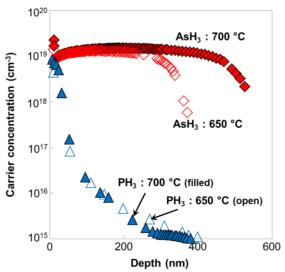

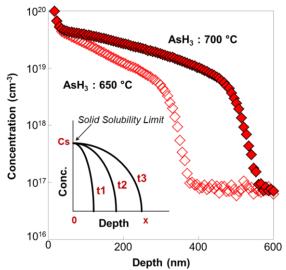

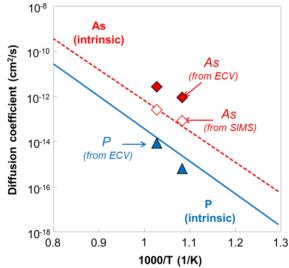

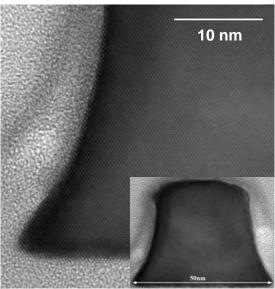

The final part of this PhD was devoted to studies on Ge thin body structures. Simulations were carried out to investigate how target sputtering, dose retention, and damage formation is generated in thin-body semiconductors by means of energetic ion impacts and how they are dependent on the target physical material properties. Solid phase epitaxy studies in wide and thin Ge fins confirmed the

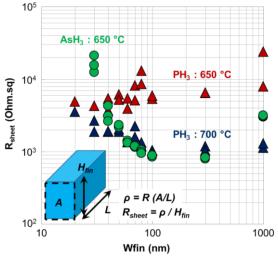

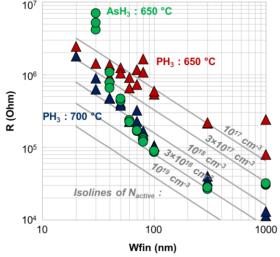

formation of twin boundary defects and random nucleation growth, like in Si, but here 600 °C annealing temperature was found to be effective to reduce these defects. Finally, a non-destructive doping technique was successfully implemented to dope Ge nanowires, where nanowire resistivity was reduced by 5 orders of magnitude using PH<sub>3</sub> based in-diffusion process.

#### **List of Publications**

#### Based on results presented in this thesis:

- [1] M. Shayesteh, C. L. L. M. Daunt, D. O'Connell, V. Djara, M. White, B. Long, and R. Duffy, "NiGe contacts and junction architectures for P and As doped germanium devices," *IEEE Transactions on Electron Devices*, vol. 58, pp. 3801-3807, 2011.

- [2] <u>M. Shayesteh</u>, C. L. M. Daunt, D. O'Connell, V. Djara, M. White, B. Long, and R. Duffy, "N-type doped germanium contact resistance extraction and evaluation for advanced devices," in *European Solid-State Device Research Conference*, 2011, pp. 235-238.

- [3] <u>M. Shayesteh</u>, V. Djara, M. Schmidt, M. White, A. M. Kelleher, and R. Duffy, "Fluorine implantation in germanium for dopant diffusion control," in *AIP Conference Proceedings*, 2012, pp. 115-118.

- [4] <u>M. Shayesteh</u>, R. Duffy, B. McCarthy, A. Blake, M. White, J. Scully, R. Yu, V. Djara, M. Schmidt, N. Petkov, and A. M. Kelleher, "Germanium fin structure optimization for future MugFET and FinFET applications," in *ECS Transactions*, 2011, pp. 27-34.

- [5] M. Shayesteh, K. Huet, I. Toque-Tresonne, R. Negru, C. L. M. Daunt, N. Kelly, D. O'Connell, R. Yu, V. Djara, P. B. Carolan, N. Petkov, and R. Duffy, "Atomically flat low-resistive germanide contacts formed by laser thermal anneal," *IEEE Transactions on Electron Devices*, vol. 60, pp. 2178-2185, 2013.

- [6] M. Shayesteh, D. O' Connell, F. Gity, P. Murphy, R. Yu, K. Huet, I. Toqué-Tresonne, F. Cristiano, S. Boninelli, H. H. Henrichsen, P. F. Nielsen, D. H. Petersen, and R. Duffy "Optimised Laser Thermal Annealing on Germanium for Reduced Access Resistance and Low Leakage Current ", *IEEE Transactions on Electron Devices, under publication.*

- [7] M. Shayesteh, D. O'Connell, F. Gity, F. Murphy-Armando, R. Yu, K. Huet, I. Toque-Tresonne, F. Cristiano, S. Boninelli, H. H. Henrichsen, D. H. Petersen, P. F. Nielsen, and R. Duffy, "Laser thermal annealing of Ge, optimized for highly activated dopants and diode ION/IOFF ratios," 20th International Conference on Ion Implantation Technology (IIT), 2014, 2014.

- [8] R. Duffy and <u>M. Shayesteh</u>, "FinFET doping; material science, metrology, and process modeling studies for optimized device performance," in *AIP Conference Proceedings*, 2010, pp. 17-22.

- [9] R. Duffy and M. Shayesteh, "Germanium doping, contacts, and thin-body structures," in *ECS Transactions*, 2012, pp. 189-201.

- [10] R. Duffy and M. Shayesteh, "Novel processing for access resistance reduction in Germanium devices," in 2014 International Workshop on Junction Technology, IWJT 2014, 2014, pp. 155-160.

- [11] R. Duffy, M. Shayesteh, I. Kazadojev, and R. Yu, "Germanium doping challenges," in *Extended Abstracts of the 13th International Workshop on Junction Technology 2013, IWJT 2013*, 2013, pp. 16-21.

- [12] R. Duffy, M. Shayesteh, B. McCarthy, A. Blake, M. White, J. Scully, R. Yu, A. M. Kelleher, M. Schmidt, N. Petkov, L. Pelaz, and L. A. Marqués, "The curious case of thin-body Ge crystallization," *Applied Physics Letters*, vol. 99, 2011.

- [13] R. Duffy, <u>M. Shayesteh</u>, M. White, J. Kearney, and A. M. Kelleher, "The formation, stability, and suitability of n-type junctions in germanium formed by solid phase epitaxial recrystallization," *Applied Physics Letters*, vol. 96, 2010.

- [14] K. Huet, M. Shayesteh, I. Toqué-Tresonne, R. Negru, C. L. M. Daunt, N. Kelly, D. O'Connell, R. Yu, V. Djara, P. Carolan, N. Petkov, and R. Duffy, "Laser thermal anneal formation of atomically-flat low-resistive germanide contacts," *Physica Status Solidi (C) Current Topics in Solid State Physics*, vol. 11, pp. 169-173, 2014.

- [15] R. Duffy, M. Shayesteh, K. Thomas, E. Pelucchi, R. Yu, A. Gangnaik, Y. M. Georgiev, P. Carolan, N. Petkov, B. Long, J. D. Holmes, "Access resistance reduction in Ge nanowires and substrates based on non-destructive gassource dopant in-diffusion," *Journal of Materials Chemistry C*, vol. 2, pp. 9248-9257, 2014.

#### Other contributions that are not discussed in the thesis:

- [1] B. Long, G. Alessio Verni, J. O'Connell, J. Holmes, <u>M. Shayesteh</u>, D. O'Connell, and R. Duffy, "Molecular Layer Doping: Non-destructive doping of silicon and germanium," in *20th International Conference on Ion Implantation Technology (IIT)*, *2014*, 2014, pp. 1-4.

- [2] B. Long, R. Duffy, G. Alessio-Verni, J. O'Connell, <u>M. Shayesteh</u>, A. Gangnaik, Y. M. Georgiev, P. Carolan, D. O'Connell, K. J. Kuhn, S. B. Clendenning and J. D. Holmes, "Conformal and non-destructive doping of germanium nanowires," Journal of Materials Chemistry C, Ready for submission

- [3] R. Yu, S. Das, I. Ferain, P. Razavi, <u>M. Shayesteh</u>, A. Kranti, R. Duffy, and J. P. Colinge, "Device design and estimated performance for p-type junctionless transistors on bulk germanium substrates," *IEEE Transactions on Electron Devices*, vol. 59, pp. 2308-2313, 2012.

- [4] R. Yu, Y. M. Georgiev, S. Das, R. G. Hobbs, I. M. Povey, N. Petkov, <u>M. Shayesteh</u>, D. O'Connell, J. D. Holmes, and R. Duffy, "Junctionless nanowire transistor fabricated with high mobility Ge channel," *Physica Status Solidi Rapid Research Letters*, vol. 8, pp. 65-68, 2014.

- [5] R. Yu, A. N. Nazarov, V. S. Lysenko, S. Das, I. Ferain, P. Razavi, <u>M. Shayesteh</u>, A. Kranti, R. Duffy, and J. P. Colinge, "Impact ionization induced dynamic floating body effect in junctionless transistors," *Solid-State Electronics*, vol. 90, pp. 28-33, 2013.

# Chapter 1

# Introduction

## 1.1 Motivation and background

The idea of making a transistor goes back to 1925 when Julius Edgar Lilienfeld invented a field effect transistor (FET) [1]. He only filed a patent on his work but later on it was proved that his device was operational [2].

In 1947 a new working transistor was made from Ge semiconductor. A couple of years later another transistor made from Si was introduced, which was more interesting than Ge transistor due to the inexpensive, abundant, Si substrate and its superb stable native oxide. The amorphous SiO<sub>2</sub> has a large energy gap of approximately 9 eV, and a dielectric strength which is sufficient for supporting electric field strengths of several megavolts/cm, (10<sup>6</sup> V/cm) which is especially critical for metal-oxide-semiconductor field effect transistor (MOSFET) operation [3]. Since then Si has been the main material used in semiconductor industry.

In 1965 Gordon Moore, considering the fabrication cost and technological capabilities in that time, speculated that the number of transistors on a single integrated circuit could be doubled per year [4]. The idea which was called "Moore's Law" was later on amended to double transistors on a chip every 2 years [5].

For more than four decades this guideline has been the driving force for endless innovations in design and fabrication of transistors and integrated circuits which appeared to be smaller in size and more densely packed at each technology node, providing incredible sophisticated functionalities.

Apparently the path has never been easy since each new generation of electronic devices would impose challenges from processing and fabrication to circuit integration, test and reliability issues [6].

According to Dennard *et al.* continuous device scaling while maintaining the same electric field in the device needs a transformation of the transistor dimensions

as well as the voltage and doping by a factor of  $\alpha$  [7]. This reduction includes the vertical as well as horizontal dimensions of the device. The applied voltage to the device should also be reduced by  $\alpha$ . On the other hand the substrate doping concentration should be increased using the same scaling factor i.e.  $(\alpha.N_a)$  [7, 8]. As a result the switching speed is boosted by a factor of  $\alpha$  when the power consumption is reduced by a factor of  $\alpha^2$ . In Table 1.1 a summary of the scaled features as well as the effects on the device performance is shown.

Table 1.1: Scaling results for circuit performance which follow from circuit dimension. The rules apply to constant electric field scaling [7].

| Device or circuit parameter         | Scaling factor |  |  |

|-------------------------------------|----------------|--|--|

| Device dimension, tox, L, W         | $1/\alpha$     |  |  |

| Doping concentration N <sub>a</sub> | α              |  |  |

| Voltage V                           | 1/α            |  |  |

| Current I                           | 1/α            |  |  |

| Capacitance                         | 1/α            |  |  |

| Delay time/circuit VC/I             | 1/α            |  |  |

| Power dissipation/circuit VI        | $1/\alpha^2$   |  |  |

| Power density VI/A                  | 1              |  |  |

|                                     |                |  |  |

For more than 4 decades lots of efforts have been made in order to meet Moore's law with respect to the scaling factor proposed by Dennard.

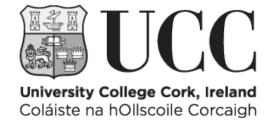

Figure 1.1: Transistor density per square millimetre versus the year of the device introduction (left axis) along with transistor gate length shrinkage versus the year of the device introduction (right axis) Copyright 2011 Nature publishing group [9].

Figure 1.1 shows the evolution of gate length and the density of transistors in microprocessors over the last decades. The gate length shrank from  $10~\mu m$  to 28~nm

and the number of transistors per square millimetre increased from 200 to over 1 million [9].

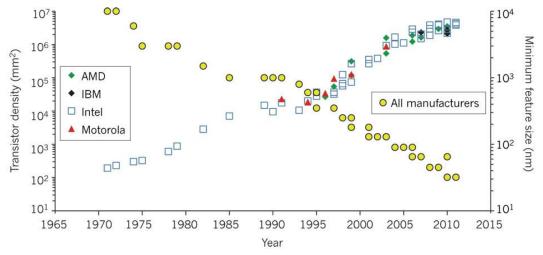

With respect to microprocessors and integrated circuits CMOS technology is facing two major problems; power dissipation and variability [10]. From power density perspective, the complexity of the integrated circuits has been accompanied by an increase in power dissipation. As the transistors become smaller in size and faster in performance the overall active power increases due dissipative switching of charge between transistor terminals during logic operations. Although it was relatively negligible a few generations back the standby power has become significantly high and comparable to the active power density. This is caused by the overall increase in the off-state leakage current as a result of gate length scaling and oxide thickness reduction [11]. Figure 1.2 depicts the passive power trend based on the Subthreshold current and show a cross-over point below 20 nm gate length [12].

Figure 1.2: Active and subthreshold power density trends plotted from the industry data versus the gate length for junction temperature of 25 °C. The empirical extrapolated dashed-lines show that the active and standby power equal at 20 nm gate length [12].

Regarding the variability issue, doping processes require a very precise control in nanoscale devices. At this scale a random displacement of the dopants can influence the electrical characteristics of the device. In addition fluctuations of channel dopants can cause variations in the threshold voltage which is problematic for circuit design in terms of yield and reliability [10]. In fact other processes (e.g. lithography, etch) can also introduce variability or defects in the substrate. All of these things become more critical as the transistor scales.

## 1.1.1 Transistor shrinking challenges

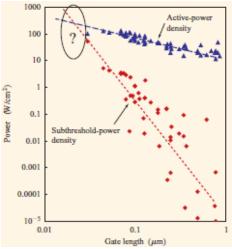

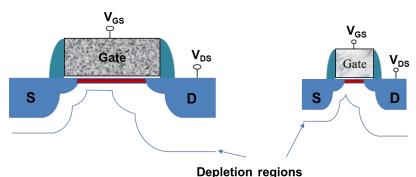

In a typical n-type bulk transistor like Figure 1.3 the channel is controlled by the gate. When the gate voltage reaches a certain value called threshold voltage the holes are pushed away and electrons are attracted to the channel forming an inversion layer underneath the gate. At this stage, increasing drain voltage results in electron current flowing from source to the drain. The current keeps increasing by the drain voltage until the pinch off stage happens where some part of the channel is disappeared due to the spreading depletion region that is heavily affected by the drain. Meanwhile the strong electric field around the drain region pulls the electrons to the channel. From now on the current is a function of the gate voltage and is almost independent of the drain voltage. This is where the transistor enters the on state (saturation region).

In this case the on current is calculated from

$$I_{on} = \mu W \frac{\varepsilon_{ox}}{2L_g t_{ox}} (V_{GS} - V_T)^2$$

(1.1)

where  $\mu$  is the carrier mobility in the channel, W is the width of the gate,  $L_g$  is the gate length and  $\epsilon_{ox}$  and  $t_{ox}$  are the oxide permittivity and thickness respectively.

Figure 1.3: Schematic representation of a typical bulk transistor and the corresponding current voltage characteristic.

From the equation above it is clear that a thinner gate oxide, shorter gate length as well as a wider gate can boost the on current as it has been achieved over the last decades of conventional transistor downscaling. Nevertheless the continuous

shrinking trend came with consequences as the Si technology reached fundamental physical limits.

For instance, the gate oxide thinning can no longer improve the device performance. Poor silicon dioxide (less than about 3 nm thickness) results in high tunnelling leakage current ( $\sim 3\times$  for every 0.1 nm thickness reduction [11]) through the film which increases the device power consumption. High- $\kappa$  dielectrics such as zirconia (ZrO<sub>2</sub>) and hafnia (HfO<sub>2</sub>) have already been introduced to allow further scaling without sacrificing the device throughput.

Moreover the reduced spacing between the source and drain at shorter gate lengths causes short channel effects (SCE) which manifests itself in number of undesired behaviours. The issue looks more critical considering the fact that the practical source drain distance is approximately 50% shorter than the gate length, for example for a 30 nm gate length the actual effective channel length is 15 nm [9]. Figure 1.4 shows a schematic of a transistor and SCE.

Figure 1.4: Schematic of bulk transistor and short channel effect due to transistor shrinkage. High leakage current and mobility reduction degrade the transistor performance.

In classical transistors there is a potential barrier for electrons to flow from source to the drain. When the gate length is long enough (~ 1 µm) the source and drain are far apart therefore the channel is controlled by the gate whereas at shorter gate lengths, the drain depletion region is extended under the gate, taking over the control of the channel by reducing the potential barrier for electrons to flow from source to the drain. So, as the drain voltage is increased, the current starts increasing even before the voltage on the gate reaches the threshold value. This effect known as drain induced barrier lowering (DIBL) results in reduction of the threshold voltage as the drain voltage increases [9]. This is equivalent to Vt roll-off effect that the gate threshold voltage decreases as the channel length is reduced. The resulting

current flow is called Subthreshold current. The rate of the current increase below the threshold voltage is referred to as subthreshold swing (SS) which is another figure of merit for the device performance and is formulated as [13]

$$SS = \frac{kT}{q} \cdot \ln(10) \cdot n \tag{1.2}$$

corresponding to the inverse of the slope of the linear region in Id-Vg curve (see Figure 1.3). The unit is mV/decade. Here,  $k_B$  is the Boltzmann constant, q is the charge of an electron, T is the temperature in Kelvin, ln (10) is coming from the logarithmic scale of the plot and n is the body factor which is an indication of the level of efficiency of the gate control over the channel. The body factor can be calculated from

$$n = \left(1 + \frac{C_b}{C_g}\right)$$

$$C_b = \frac{\varepsilon_{Si}}{W_d}$$

$$C_g = \frac{\varepsilon_{ox}}{t_{ox}}$$

(1.3)

where  $C_b$  and  $C_g$  are the bulk and gate capacitance respectively.  $\epsilon_{si}$  and  $\epsilon_{ox}$  denote the Si and oxide dielectrics respectively.  $W_d$  is the depletion region under the channel and  $t_{ox}$  is the gate oxide thickness.

As is seen in the equation SS cannot be below a certain value due to the theoretical limits. In fact in the best possible case where gate has the full control over the channel the SS is approximately 60 mV/decade at room temperature. However, in practice the body factor is larger than 1, so the SS is always above 60 mV/decade. To minimize SS the gate should establish a relatively fixed bulk charge in the depletion region as the gate voltage is changing so that the bulk capacitance is kept as small as possible.

Again the importance of maintaining the gate control over the channel is highlighted. In short channel devices the extended electric field from the drain can result in increased SS value. One possible solution for this issue is lightly doped substrate.

Another side effect of transistor shrinkage is velocity saturation. Due to strong electric field in the channel the velocity of carriers reaches the maximum, and does

not follow the linear relation with the electric field. This is attributed to increased levels of scattering that the accelerated electrons are going through so that they lose their energy. Saturation velocity was observed for 250 nm gate length in SOI transistors [14].

Generally speaking the main outcome of the SCE is high leakage current which results in more power dissipation.

In order to minimize SCE and access resistance in conventional planar devices it is necessary to highly dope source and drain regions while maintaining shallow and abrupt junctions. In this case the scattering rate of the ionized dopant atoms is higher resulting in mobility degradation.

Higher doping concentration in the channel in order to reduce the depletion width is also required along with mobility enhancement techniques such as strain engineering by using SiGe, or SiC to introduce strain in Si lattice.

One of the important features that affect the transistor performance is parasitic source drain resistance ( $R_{SD}$ ). It is suggested that four components contribute to the  $R_{SD}$ , which can be listed as: overlap resistance ( $R_{ov}$ ), extension resistance ( $R_{ex}$ ), deep resistance ( $R_{dp}$ ), and contact resistance ( $R_{c}$ ). In nanometre size transistors  $R_{SD}$  is more pronounced and needs special attention. Among the resistance components overlap resistance is strongly dependent on the doping concentration in the overlap region as well as the lateral abruptness of the region which can affect the current spreading and the accumulation carrier density. So care must be taken when doping this region [15].

In an extensive study by Seong-Dong *et al.* it was predicted that at 50 nm gate length the contact resistance and the overlap resistance contribute up to 70% of the total source drain resistance and as the transistor gets smaller the contact resistance contribution in the total resistance becomes more significant [16]. Therefore it is essential to implement novel processing techniques for doping and annealing in order to minimize contact resistance in new generations of the scaled transistors.

A feasible solution for advanced CMOS technology to pursue the downscaling trend seems to be the emergence of new generations of transistors with innovative geometrical structures such a multi-gate MOSFETs and FinFETs [9] as well as introduction of new alternatives for silicon e.g. III-V materials and Ge.

#### 1.2 Potential replacements for Si

In the first place Si became the prevailing material in semiconductor technology due to its excellent native oxide, but because of the failure of the gate oxide in aggressively scaled transistors new hi- $\kappa$  materials had to be introduced to do the task. When SiO<sub>2</sub> was replaced, one of the main reasons for using Si was lost and researchers began investigating new high mobility semiconductor materials such as III-V compounds, Ge, graphene, and transition metal dichalcogenides (TMD) [17]which seem to have the potential to replace Si. Table 1.2 shows the properties of several high mobility materials that could be used in nanoscale devices.

Table 1.2: Comparison of high mobility materials with Si [11].

| Property                                | Si   | Ge   | GaAs | InP  | InAs  | InSb  |

|-----------------------------------------|------|------|------|------|-------|-------|

| Electron mobility (cm <sup>2</sup> /Vs) | 1500 | 3900 | 8500 | 5400 | 40000 | 77000 |

| Hole mobility (cm <sup>2</sup> /Vs)     | 475  | 1900 | 400  | 200  | 500   | 850   |

| Bandgap (eV)                            | 1.12 | 0.66 | 1.42 | 1.34 | 0.35  | 0.17  |

| Dielectric constant                     | 11.7 | 16.2 | 12.9 | 12.5 | 15.2  | 16.8  |

| (mterial)                               | 11./ | 10.2 | 12.9 | 12.3 | 13.2  |       |

These materials benefit from high electron mobility that is essential in making high speed devices. GaAs and InAs, and InSb have significantly higher electron mobility than Si which makes them promising materials for high performance n-type transistors. On the contrary, they have less or comparable hole mobility as compared to Si which is not quite favourable for making p-type transistors. Processing and fabrication of these expensive materials is costly as well and may need a separate fabrication line as these materials cannot be processed in conventional Si labs due to contamination issues. On the other hand, Ge appears to have several distinctive characteristics over the other candidates. Compared to Si, it benefits from higher carrier mobility for both electrons (2×) and holes (4×). More importantly, Ge is a non-contaminant element, which makes it compatible with Si fabrication tools and infrastructure. Note that Ge has already been used in the form

of SiGe in 90 nm and smaller technology node transistors to obtain higher mobility and faster devices.

Although these advantages suggest Ge as a good choice, Ge technology is not fully mature [18] in order to extensively incorporate this material in the advanced CMOS technology. Perhaps the biggest challenge is process and integration of Ge in an efficient way so that high-mobility benefit is not swamped by imperfect manufacturing procedures.

#### 1.3 New device architectures

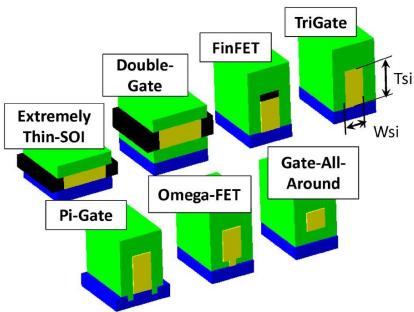

The transistor miniaturization has led to the emergence of various revolutionary device architectures. Figure 1.5 shows the evolution of transistors from 1980s till now. The main point of these architectures is to improve the gate control over the channel. It is well established that silicon-on-insulator (SOI) devices have the potential to improve SCE in traditional bulk transistors.

Figure 1.5: Illustration of the alternative transistor designs reducing the short channel effect [19].

In these devices that are known as extremely thin SOI device (ETSOI) the Si film thickness is thinner than the channel depletion depth [19]. These devices benefit from smaller source/drain to substrate capacitance, switch faster and run at lower voltages and offer body bias [19]. However the necessity for very small thickness of the Si film create challenges such as thickness targeting and variations

in the ETSOI wafer, high parasitic source drain resistance, quantum confinement and scattering. Also, the drive current in these devices is less than comparable bulk transistors.

Another alternative approach is surrounding the gate with two or more opposing gates where each additional gate improves the SCE. These devices can be oriented horizontally (double-gate device) or vertically (FinFETs) and also can be fabricated on SOI substrates. They have the advantage of enhanced gate control therefore the leakage current is suppressed and the switching speed is increased. An additional benefit of these devices compared to ETSOI devices is that the total electrical area can be dramatically larger than the device footprint [19].

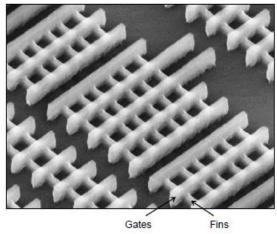

Figure 1.6: 22 nm Tri-gate transistors on bulk Si made by Intel [20].

Switching to new non-planar structures has enabled the industry to proceed to the 22 nm technology node. The vertical architecture of these devices allows integration of more devices on a chip and making faster circuits and probably a wider range of functionalities. Manufacturing of these devices is quite challenging. The higher device current achieved in these devices can very well pay off the difficulties for fabricating these devices. In fact patterning and fabrication of high aspect ratio fin structures at aggressively reduced fin pitches impose new challenges and demand new doping and annealing techniques. In 2011 Intel introduced a new generation of the CPUs fabricated from Tri-gates on SOI. Figure 1.6 is a representative image of the transistors demonstrated on bulk Si substrate.

It is generally accepted that the FET devices will continue the transistor scaling toward ultrathin body channels [17].

The ultimate CMOS device is likely to be a nanowire with a gate-all-around geometry, a hi-k gate dielectric and conductive gate electrode. In these devices scaling the gate pitch can be done by scaling the source and drain regions, spacer and overlap regions or the channel length, however there are trade-offs associated with that. For example, a wider spacer can decrease the parasitic capacitance but at the cost of increased parasitic source drain resistance as these regions will have to be smaller. If there are good electrostatics then the channel length can be shorter enabling larger S/D regions and smaller parasitic resistance but it is accompanied by increased gate parasitic resistance [19]. The interference of parasitic resistance in each region of these devices can impede the device performance by reducing the drive current and making the device slower. As an example the gate region contains a gate contact with underlying gate metal layers and there is a resistance associated with each of these layers. The resistance of the S/D regions includes the resistances of the contact, the silicide, and an epi layer, and the most critical task is probably minimizing the Schottky barrier height. Parasitic capacitance will be more challenging in new devices due to the reduced distance between the gate and the other parts [19]. Therefore it appears that advanced technologies and materials are needed to address the traditional as well as the new challenges in device scaling.

#### 1.4 Challenges for introducing Ge to CMOS technology

Even though Ge is very similar to Si, there are some differences in terms of material characteristics that make it a challenging task for industry to fabricate fully operational Ge transistors.

The most well-known challenges facing the Ge technology can be summarized as:

- The substrate / integrate Ge on Si wafer

- Gate dielectric

- Doping

- Contacts

- Thin body devices

- Leakage current

The issues in bold will be discussed in this thesis. Regarding the material strength Ge wafers (in 300 or 450 nm diameter) are not strong enough to survive the auto-feed handling involved in mass production of integrated circuits. The lattice constant of Ge is ~4% greater than that of Si, therefore Ge growth on Si will start to relax almost immediately via the formation of misfit dislocations. To solve this problem, a thick Si<sub>x</sub>Ge<sub>1-x</sub> buffer layer is grown on the Si substrate and the active Ge layer is grown on top of that, where the defect density is reduced considerably. This buffered-growth technique provides a way of integrating Ge devices on a Si handle wafer [17]. Another approach is growth in trenches using the aspect ratio trapping technique [21].

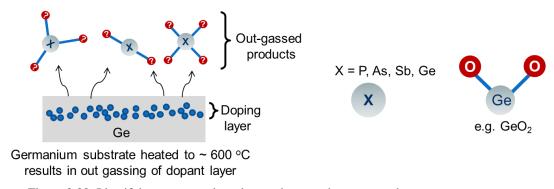

One of the most well-known obstacles rises from the unstable water soluble germanium oxide (GeO<sub>2</sub>) that cannot be used as gate dielectric in Ge MOSFETs in a straightforward approach. In fact GeO<sub>2</sub> when in contact with Ge transforms into GeO which tends to desorb at temperatures above 400 °C. The consequence is the loss of the underlying Ge layer as well as desorption of the oxide layer, and roughness of the surface.

Various approaches have been proposed to form a proper dielectric on Ge such as, such as Si, GeO<sub>2</sub>, and oxynitride interfacial layers, high pressure thermal oxidation, sulphur passivation, plasma oxidation, etc. Other high-κ materials are also introduced for Ge CMOS devices, like HfO<sub>2</sub>, LaLuO<sub>3</sub>, ZrO<sub>2</sub>, and GeO<sub>2</sub>/AlO<sub>3</sub> gate stacks for n-type Ge devices [17].

The other major problem is realization of n-type ultra-shallow junctions with highly activated dopants. It is well established that n-type dopants in Ge tend to diffuse quickly and are relatively difficult to activate. In contrast, p-type dopants i.e. B exhibit low diffusivity as well as high activation levels (>  $10^{20} \text{cm}^{-3}$ ) in Ge, favourable for fabricating high performance PMOS Ge devices [18]. The shallowest p-type profile in Ge has been generated by B 2 keV implant [22] whereas As 5 keV implant have been carried out to produce the shallowest n-type doping profile [23].

Point defect engineering techniques such as co-implants as well as non-implant doping approaches like plasma doping, spin-on-dopant along with novel annealing techniques like laser, flash lamp or microwave annealing might be helpful to offer solutions for these problems.

Realizing a low resistive contact on n-type Ge is another key bottleneck. The problem arises from the material properties which lead to formation of high Schottky barriers between Ge and the contact metal. In contrast formation of ohmic contacts on p-type Ge is more straightforward. Several solutions have been proposed to minimize the barrier height and form an ohmic contact mainly with two approaches; terminating the dangling bonds on the surface and optimization of the germanide alloy with high doping concentrations underneath.

Ge band gap (0.67 eV) is about half of that of Si leading to higher leakage current in pn junctions [24]. Utilizing advanced processing techniques, and point defect engineering would allow formation of junctions with minimum defects which are one of the main reasons for leakage current.

Modelling capabilities are not developed as compared to extensive experimental works that are being done on Ge and need to be improved in order to give substantial input for time and cost effective development of Ge devices [17].

As stated earlier there are many unknowns about Ge that need to be answered and this entails application of novel approaches for doping, annealing, fabrication so that Ge can be extensively used in device fabrication. The main focus of this thesis is on the problems related to doping, contacts, leakage current and thin body devices.

#### 1.5 Thesis structure

This dissertation addresses different issues in the fabrication and characterization of Ge based devices.

Chapter 2 provides a short introduction on metal semiconductor contacts, Fermi level pinning and the mechanism involved in this phenomenon. A short literature review on contacts on n-type Ge is presented as well. Formation and characterization of low resistance NiGe contacts on Ge with respect to dopant type, dopant concentration, and annealing techniques is discussed.

In Chapter 3 we discuss different doping and annealing methodologies with main focus on laser and rapid thermal annealing techniques where we systematically compare the impact of the two on dopant activation, and leakage current in n+/p

junctions. The effect of F for controlling dopant diffusion is studied. The Ge desorption phenomenon and its contribution to dopant loss is investigated as well.

In Chapter 4 we briefly analyse the effect of ion implantation into thin body structures using SRIM simulation tool. Next we study solid phase epitaxy in thin body Ge structures. In the final section we implement a MOVPE-based non-destructive doping technique for doping nanometre thick fin resistors and show the results of material characterizations and extract electrical parameter associated with resistance.

Finally Chapter 5 summarizes the key points of this study and discusses possible future works that can help to expand the understanding of Ge challenges and their potential solutions.

# Chapter 2

#### **Contacts on Germanium Devices**

#### 2.1 Introduction

Metal semiconductor (MS) contacts are known as a key part in every semiconductor based device. They can be classified as: (i) Ohmic, which is essential in connecting the integrated circuits to the outside world with no/negligible resistance so that it does not affect the performance and efficiency of the device, and (ii) Schottky, which is used in high speed rectifying diodes, solar panels, and power devices.

A brief introduction of MS contacts and Fermi level pinning (FLP) phenomena are in the opening of this chapter followed by the state-of-the-art work that has been reported so far to address the issue. The main focus of this chapter is on formation of low resistance contacts on n-type Ge and their characteristics with regard to dopants concentration, dopant type and annealing techniques.

#### 2.2 Metal semiconductor contacts

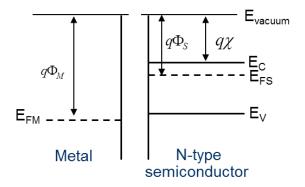

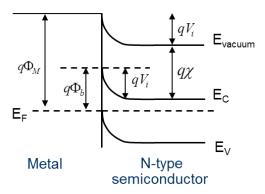

Metal work function is defined as the energy (in electron volts) required for freeing an electron from the metal Fermi level to the vacuum level while the electron is still close to the surface in macroscopic scale. This value is a property of the material and cannot be changed. In semiconductors the work function can be tuned by changing the concentration of the dopants. Figure 2.1 illustrates the band diagram of the metal-semiconductor system before making contact.  $q\Phi_M$  and  $q\Phi_S$  are the metal and semiconductor work functions respectively.  $q\chi$  is the semiconductor electron affinity referring to the energy required to extract an electron from the conduction band to the vacuum level. If the materials do not interact then for  $\Phi_M > \Phi_S$  it can be said that the average total energy of an electron in semiconductor is higher than that of metal.

The opposite is true if  $\Phi M < \Phi S$ . When these materials come to an intimate contact, electrical current flows across the interface in a non-linear fashion against the biased voltage [25].

The underlying story is that after the contact is made in order to establish equilibrium the conduction band (CB) electrons flow from the semiconductor to the metal. For p-type semiconductors this role belongs to the holes in the valence band (VB). As a result Fermi levels are aligned, with a new arrangement made in the band diagrams as is shown in Figure 2.2.

Figure 2.1: Schematic of the energy band diagram of metal and n-type semiconductor before making contact.

Migration of electrons from the semiconductor CB to the metal leaves fixed positive charges behind leading to formation of a depletion region at the interface.

Figure 2.2: Energy band diagram of the MS Schottky contact under equilibrium [26].

At this point a potential barrier is formed preventing further movement of electrons and is given by

$$qV_i = q\Phi_M - q\chi \tag{2.1}$$

In the meantime on the metal side a built-in potential barrier is formed known as electron Schottky barrier height (eSBH):

$$q\Phi_b = qV_i + (E_c - E_V) \tag{2.2}$$

This barrier leads to a rectifying behaviour allowing the current flow only from one side to the other. The current flow from the semiconductor to the metal changes depending on the applied bias voltage. If a positive voltage bias is applied to the MS contact the potential barrier is reduced for the electrons in semiconductor but not for the electrons in metal. Therefore the electron current flow from the semiconductor to the metal increases. In a reversed bias situation the potential barrier increases and the current flow from semiconductor to the metal decreases drastically. In both situations the SBH is not changed and therefore the electron current flow from the metal to the semiconductor remains unchanged leading to a rectifying non-linear current—voltage behaviour [26]. The MS contact is a majority carrier device with little minority carrier conduction, and therefore it is a fast switching device. Similar discussion is applied for p-type semiconductor with holes being the majority carriers [27].

Ohmic contacts in MS system are possible via: (i) formation of tunnelling barriers where the metal is a degenerately doped n-type semiconductor (ii) MS systems where the metal work function is smaller than that of the semiconductor [27]. In a degenerately doped n-type semiconductor Fermi level is near the conduction band. In this case the dopant concentration is very large so that the depletion region is very small where tunnelling through the potential barrier can happen (see Figure 2.6 c)). In this case in reversed bias condition the electrons easily tunnel through the barrier from metal to the semiconductor and in forward bias they tunnel through the barrier from the semiconductor to the metal. Much of the same can be said for metal Schottky tunnel barriers on degenerate p-type semiconductors in which the holes flow from the metal to the semiconductor and vice versa.

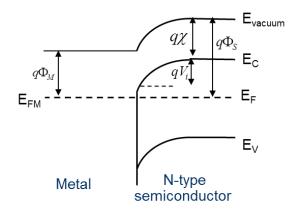

Regarding the second approach, the metal with smaller work function has the electrons with higher energy levels so the intimate contact between the two materials would lead to the electron flow from metal to the semiconductor. Here the

surface of the semiconductor consists of free mobile electrons, which is not the case for the Schottky contacts. Also the electrons from the conduction band of the semiconductor see no barrier towards the metal as is shown in Figure 2.3[27].

Figure 2.3: Energy band diagram of an ideal the MS ohmic contact under equilibrium [27].

Nevertheless, this approach does not seem to be applicable for n-type Ge in contrast to Si according to the extensive experimental studies carried out in this area [28]. The mechanism involved in this is discussed in the following section.

In general a large SBH and Schottky MS system on n-type Ge is expected to behave ohmic for the equivalent MS system on p-type Ge. For example in a study by Nishimura *et al.* an identical process fabrication on n and p-type Ge resulted in Schottky and ohmic contacts on the n and p-type Ge substrates respectively [29].

#### 2.3 Fermi level pinning

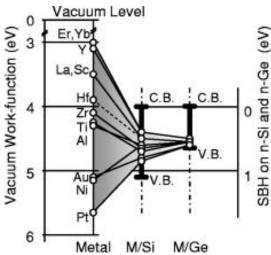

Experimental works on SBH measurements in Ge revealed that in many of the materials SBH is independent of the metal work function [25]. This phenomenon, which is called Fermi level pinning (FLP), was later attributed to two mechanisms.

#### 2.3.1 Surface states

During the fabrication procedure of a semiconductor device the surface integrity and crystal lattice of the semiconductor is perturbed leading to formation of dangling bonds at the semiconductor surface. This would subsequently give rise to the number of surface states in the semiconductor band gap near the interface. Being called interface traps these states lie within the band gap and are occupied with electrons if they are below the Fermi level.

When contact is formed between metal and the semiconductor, again Fermi levels should align on both sides and as a result band bending should happen. If the interface state density is large then a negligible movement of Fermi level at the semiconductor surface will transfer sufficient amount of charge from the semiconductor to the metal (see Figure 2.4).

Figure 2.4: Energy band diagram of a non-ideal MS contact.

Therefore the alignment of the Fermi level is accomplished by movement of the electrons in the interface traps to the metal indicating that the contribution of band bending in alignment of Fermi level is negligible [26]. For Ge, the Fermi level is pinned close to the Charge Neutrality Level (CNL) located only 0.09 eV above the valence band [30], resulting in a large electron SBH and high contact resistance for n-type devices. As is shown in Figure 2.5 the SBH formed on Ge is almost independent of the metal work function.

The barrier height is calculated from

$$q\Phi_b = E_g - q\Phi_0 \tag{2.3}$$

According to Nishimura *et al.* the barrier height in Ge is hardly modulated by annealing in forming gas, metal-germanide/Ge interface or changing the substrate orientation [28]. Figure 2.5 shows the SBH extracted for various metals on n-type Si and Ge. Nevertheless it appears that processing and surface preparation techniques can significantly affect the SBH in MS contacts [25].

Figure 2.5: The experimentally obtained SBH on n-type Si and Ge using metals with a wide range of work functions. In contrast to Si SBH in Ge is nearly independent on the work function of the metal [28].

### 2.3.2 Metal induced gap states (MIGS)

Another possible reason proposed for FLP is metal induced gap states (MIGS) that are the energy states in the semiconductor originated from the tailing of the metal electron wave functions. As a result there is a scattering of negative charge from the metal into the semiconductor. In this case inserting an ultrathin insulating layer could depin the FL as the tailing of the metal electron wave function is blocked.

Engineering the barrier height in order to form ohmic contacts seems to be impractical at this stage since the formation mechanism of the SBH is still unclear itself. However it is possible to tune the depletion width at the interface by manipulating the semiconductor doping. This is also the case study for formation of low ohmic contacts on n-type Ge which is one of the stumbling blocks associated with the successful integration of advanced Ge devices.

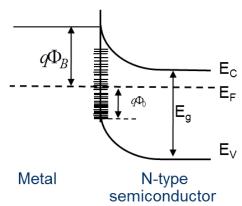

As mentioned earlier, as a result of making a contact between a metal and n-type semiconductor, electrons transfer from the semiconductor to the metal, and a depletion region is formed. The width of this region changes depending on the doping concentration of the semiconductor  $(N_D)$  affecting the conduction mechanism in MS contacts [31] which is shown in Figure 2.6.

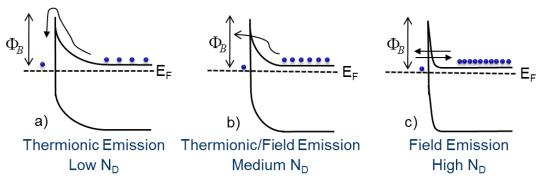

Figure 2.6: Electron flow mechanism for metal-n-type semiconductor contacts for different semiconductor doping concentrations. a) is for lowly doped Ge and c) is for highly doped Ge [31].

In lowly doped semiconductors the electrons leap over the barrier when they are thermally excited. This mechanism is shown in Figure 2.6 a) and is called thermionic emission (TE). For a moderately doped semiconductor the dominant mechanism is thermionic-field emission (TFE). In this case conduction happens in two steps in which electrons are thermally excited to a higher energy level where the barrier width is narrow so that they can tunnel through to the other side (Figure 2.6 b). For a highly doped semiconductor current flows under field emission (FE) mechanism where the electrons can tunnel through the barrier which has become sufficiently narrow as is shown in Figure 2.6 c) [31].

# 2.4 State-of-the-art work for contacts to n-type Ge

# 2.4.1 Thin insulating layers

Several methods and techniques are suggested to modulate eSBH. Ultra-thin amorphous insulating layers, such as  $Ge_3N_4$  [32] or  $GeO_x$  (1.6-2.2 nm) [29] can terminate the free dangling bonds, and eliminate FLP. A  $GeO_x$  layer between a metal and n-type Ge has been used to improve contact performance [33]. MgO ultrathin layers can also depin the surface and exhibit a weak thickness dependence [34]. It was shown that an amorphous interlayer at TiN/Ge contacts which contains nitrogen can alleviate FLP [35]. An extensive theoretical study by Roy *et al.* predicted contact resistivity ( $\rho_c$ ) of tunnel barrier contacts where the variable was the thickness of a thin insulating layer [36].

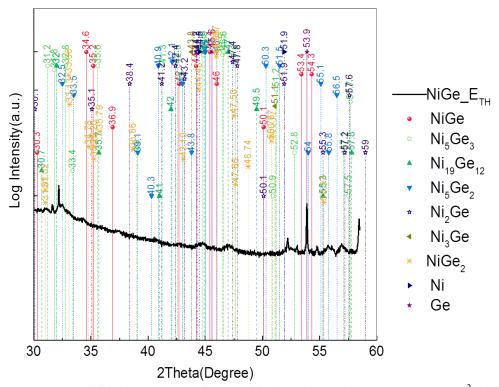

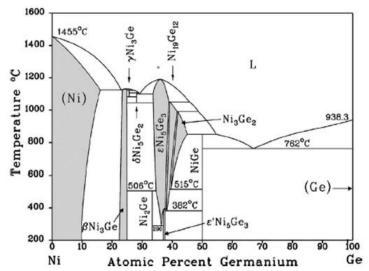

## 2.4.2 NiGe optimization

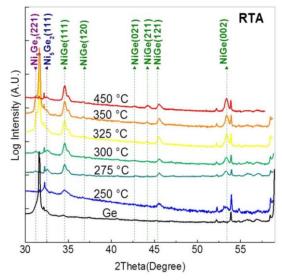

Another approach to creating stable low resistive contacts is to form a metal-semiconductor compound at the surface in combination with high doping concentrations underneath. Gaudet *et al.* examined twenty transition metals as candidates for metal-germanium reaction [37]. Based on the low formation temperature, stability, resistivity, and sensitivity to oxidation, NiGe and PdGe were suggested as the most promising candidates. NiGe is often favoured due to less problematic removal of unreacted Ni [38] during the full MOSFET process flow. Lee and Zhang also performed NiGe material studies where the germanides were formed at different reaction temperatures [39, 40]. Sheet resistance rose sharply above 500 °C, attributed to NiGe agglomeration. P and As segregation during NiGe formation reduces the eSBH due to the snowplow effect of the dopant atoms in front of the growing germanide front [41]. In that work the dopants were ion implanted, and As had a stronger influence than P, presumably due to a more effective snowplow of the larger atom.

Selenium segregation was also used to reduce eSBH for NiGe/n-Ge contacts [42]. NiGe contacts formed by a 300-400 °C germanidation anneal showed ohmic behaviour (derived from I-V characteristics) in combination with high phosphorus doping [43, 44]. Furthermore, Ikeda *et al.* modulated eSBH by Sulphur snowplow during germanidation [45]. Gallacher *et al.* extracted specific contact resistivity ( $\rho_c$ ) of  $2.3\times10^{-7}~\Omega.cm^2$  on n-type Ge that was doped during epitaxial growth [46]. The optimum NiGe formation temperature was a 340°C RTA. However the NiGe interface with the underlying substrate was not smooth. Recently ohmic Ni contacts on n-type GeSn were reported [47].

### 2.4.3 High dopant activation

Hutin *et al.* presented further evidence of eSBH reduction with increased dopant concentration at the surface [48]. Koike *et al.* performed two step P implantation prior to formation of NiGe contact on Ge [49]. After the first P ion implantation high-temperature annealing (at 600 °C for 1 min) was carried out to form n+/p junctions. This was followed by the second P implantation into the n+-Ge after contact holes were formed on the surface. In order to suppress P diffusion no

activation annealing was carried out. After Ni deposition and RTA treatment at 350  $^{\circ}$ C  $\rho_{c}$   $_{\circ}$   $3\times10^{-8}$   $\Omega.cm^{2}$  was obtained.

Low  $\rho_c$  was reported by Miyoshi *et al.* using carrier-activation enhancement (CAE) technique. In that work P/Sb co-implantation was used to reduce SBH in NiGe/n+ Ge contacts [50].

## 2.4.4 Other interface engineering techniques

The other promising segregation technique known as Implantation Through Silicide (ITS) was used by Dubois et al., where dopants were implanted after the alloy formation [51]. In that method dopants segregate at the interface during low temperature post RTA, while the silicide front is not growing. P segregation has also been employed during PtGe formation to reduce eSBH, where P was originally in-diffused from a spin-on-resist, and the process variable was the in-diffusion anneal step [52]. Dumas *et al.* used an evaporation of a mixed alloy of Ag/Sb (99%/1%) onto to a moderately doped (N<sub>D</sub>=1×10<sup>18</sup> cm<sup>-3</sup>) n-type Ge and showed formation of AgSb ohmic contacts. In that work Ge was epitaxially grown on Si wafers with P in-situ doping [53]. CF<sub>4</sub> plasma treatment of the Ge surface was demonstrated experimentally to alleviate FLP [54]. Zheng *et al.* reported ohmic contacts to n-type Ge using Yb-germanide where 60 nm of Yb was deposited followed by SiO<sub>2</sub> deposition to prevent Yb oxidation and finally RTA treatment at 500 °C [55].

One of the state-of-the-art techniques which has been proven to be effective in formation of low resistance contacts is laser thermal annealing (LTA). Firrincieli *et al.* studied  $\rho_c$  of NiGe contact using two different approaches; sub-melt laser anneal (LA) prior to germanidation and Snowplow effect. Using LTA for dopant activation, in combination with RTA for NiGe formation resulted in  $\rho_c$  of  $8\times10^{-7}$   $\Omega.\text{cm}^2$  on n-type Ge. In snowplow effect the implantation of n-type dopant species is followed by NiGe formation at low temperatures (maximum 400 °C) leading to segregation of dopants during germanidation to the NiGe/Ge interface. The group reported  $\rho_c$  of  $2\times10^{-5}$   $\Omega.\text{cm}^2$  using this technique. In that work the NiGe layers were thermally stable up to 350 °C, but the interface with the Ge substrate was not flat. This is common for NiGe layers formed by RTA [56].

Lim *et al.* have demonstrated Fermi-level depinning using multi-pulsed LTA by the formation of epitaxial NiGe<sub>2</sub> [57]. While the steps accompanying the growth of germanides, and closely related silicides, by RTA have been studied to some extent, the formation pathway for the LTA processed materials has not been thoroughly investigated.

## 2.5 Contacts on p-type Ge

On the contrary to n-type, FLP is favourable in making ohmic contacts to p-type Ge [29, 30]. It is a common practice to form contacts on Ge after a pre-amorphisation implant (PAI) followed by ion implantation (II) and RTA. Bhatt *et al.* achieved a record low  $\rho_c$  of  $1.7\times10^{-8}~\Omega.cm^2$  and  $7.7\times10^{-8}~\Omega.cm^2$  using cryogenic and room temperature (RT) B implantation respectively. A summary of  $\rho_c$  obtained for p-type Ge is presented in Table 2.1. A table on the n-type doped Ge is shown later in this chapter.

Table 2.1: Representative o<sub>c</sub> values reported to for p-type doped germanium (from Ref. [58])

| Table 2.1. Representative $p_c$ values reported to for p-type doped germanium (from Ref. [36]) |                           |                     |                                     |  |  |

|------------------------------------------------------------------------------------------------|---------------------------|---------------------|-------------------------------------|--|--|

| Method                                                                                         | N peak(cm <sup>-3</sup> ) | $R_{sh}(\Omega/sq)$ | $\rho_{\rm c}  (\Omega.{\rm cm}^2)$ |  |  |

| PAI+II+RTA                                                                                     | $1 \times 10^{19}$        | NA                  | 8×10 <sup>-8</sup>                  |  |  |

| p-Ge                                                                                           | 1×10 <sup>19</sup>        | NA                  | 2×10 <sup>-6</sup>                  |  |  |

| p-Ge                                                                                           | $1 \times 10^{18}$        | NA                  | 3.5×10 <sup>-7</sup>                |  |  |

| RT II+RTA                                                                                      | $>1.2\times10^{19}$       | 155                 | 7.7×10 <sup>-8</sup>                |  |  |

| Cryo II+RTA                                                                                    | >4×10 <sup>20</sup>       | 28                  | 1.7×10 <sup>-8</sup>                |  |  |

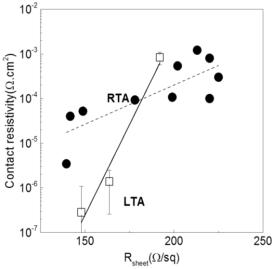

In the following section  $\rho_c$  dependence on implant dose will be determined, as well as a comparison of P-doped and As-doped Ge layers. P is the slowest n-type dopant in terms of diffusion in Ge [59] thus this parameter extraction is of vital importance. Also we aim to extract a set of  $\rho_c$  in the low activation anneal temperature regime (500 °C), consistent with solid-phase-epitaxial-recrystallization [60]. 500 °C appears to be an optimum annealing temperature for n-type dopants, as lower temperatures (e.g. 400 °C) result in poor sheet resistance and activation while at higher temperatures (e.g. 600 °C) diffusion is a concern [61]. A few studies have shown high activation levels (especially for P) without visible diffusion at 500 °C [61, 62].

## 2.6 NiGe contacts made by Rapid Thermal Anneal

## 2.6.1 Experimental procedure

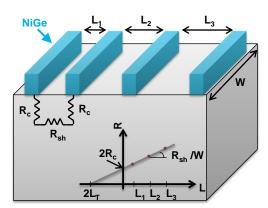

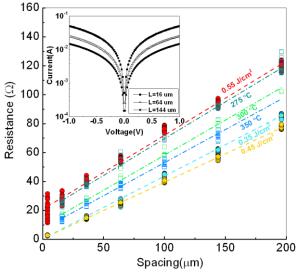

In order to extract  $\rho_c$  we use the Transfer Length Method (TLM) [31]. Figure 2.7 depicts the schematic of a typical TLM structure. Resistance between two adjacent metal strips is measured, and as shown in the inset of Figure 2.7 resistance is plotted versus contact spacing. A linear fit to the data yields the transfer length ( $L_T$ ), and contact resistance ( $R_c$ ) from which sheet resistance  $R_{sh}$ , and  $\rho_c$  are extracted by

$$R_{sh} = \frac{R_c W}{L_T} \tag{2.4}$$

$$\rho_c = R_{sh} L_T^2 \tag{2.5}$$

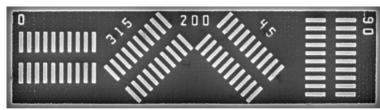

where W is the width of the structure. In our TLM test structure each NiGe bar was  $380 \times 100~\mu m^2$  and the spacings in-between were 4, 16, 36, 64, 100, 144, and 196  $\mu m$ .

Figure 2.7: A schematic of the Transfer Length Method structure.

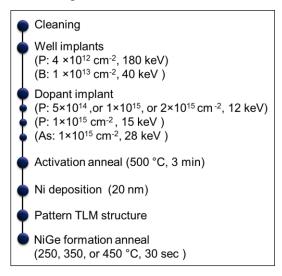

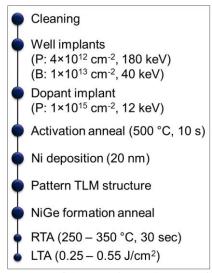

The layout consisted of a repeated array of this TLM design. More than 20 TLM structures within each array were electrically measured in order to extract values for  $\rho_c$  and  $R_{sh}$ . Figure 2.8 shows a summary of the process flow in the experiments undertaken here.

After cleaning, high-resistivity (>40  $\Omega$ .cm) n-type (100) Ge wafers received well implants, namely P with a dose of  $4 \times 10^{12}$  cm<sup>-2</sup> and energy of 180 keV, and B with a dose of  $1 \times 10^{13}$  cm<sup>-2</sup> and energy of 40 keV, to create a semi-insulating layer.

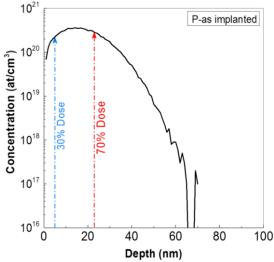

Next the shallow dopant implant was performed. In one sample set the P implant dose was varied from  $5 \times 10^{14}$  to  $2 \times 10^{15}$  cm<sup>-2</sup>. The implant energy was 12 keV. In another sample set P and As implants were compared by implanting with the same dose  $(1 \times 10^{15} \text{ cm}^{-2})$  and with two different energies (15, 28 keV respectively). The dopant profiles had the same projected range (approx. 15 nm) and junction depth (approx. 60 nm) calculated by SRIM modelling [63]. A furnace anneal at 500 °C 3 min in N<sub>2</sub> was performed for dopant activation in all the samples [60].

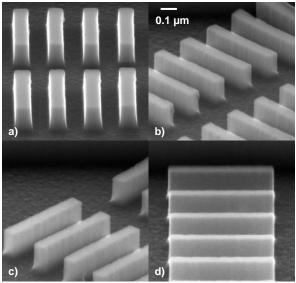

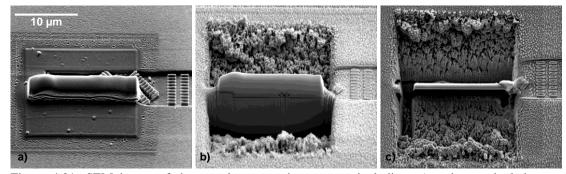

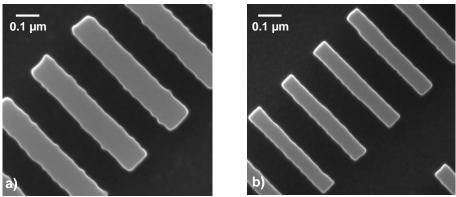

Sheet resistance measurement of selected samples was performed using Prometrix OmniMap RS35e. The tip spacing was 1.016 mm. Thereafter, 20 nm Ni was deposited on the samples by thermal evaporation. Lift-off process was performed afterwards. A trench was dry etched down to 400 nm deep to avoid leakage current. The samples were subjected to 250, 350, or 450  $^{\circ}$ C RTA for 30 sec in N<sub>2</sub> for the NiGe reaction. According to data in [37], [39], and [40] this is the process window for low-resistive NiGe formation. Scanning Electron Microscopy (SEM) was done for inspection, using a QUANTA FEG 650. Electrical characterization was done using a KEITHLEY 37100 and a KEITHLEY 2602.

Figure 2.8: A summary of the experimental process flow.

#### 2.6.2 Results of the electrical characterization

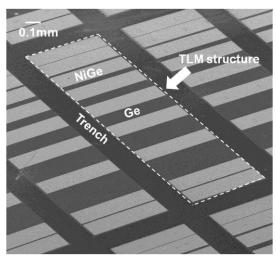

Figure 2.9 shows a representative SEM image of the finished TLM patterns. A dashed box highlights an individual TLM, with bright NiGe strips created on the Ge

substrate, surrounded by a 400 nm deep trench which is also labelled. The gaps were measured by SEM to confirm the outcome of the lithography process.

Figure 2.9: A representative SEM image of the TLM structures. Bright strips are NiGe formed on bulk Ge. The TLMs are surrounded by a 400 nm deep trench.

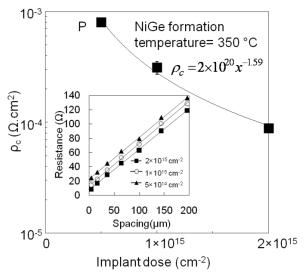

#### 2.6.2.1 $\rho_c$ versus P implant dose

First we consider the sample set where the P implant dose was varied from  $5\times10^{14}$  to  $2\times10^{15}$  cm<sup>-2</sup>. Here a 350 °C NiGe formation anneal was applied.

Figure 2.10:  $\rho_c$  versus the P implant dose. Increasing the implant dose resulted in decreasing the  $\rho_c$ . The inset shows the resistance between two consecutive metal contacts versus the spacing for all the P implant doses. Straight lines are well fitted to the data.

Figure 2.10 represents the result. The inset shows the total resistance as a function of the contact spacing, extracted from a typical TLM electrical measurement, for the three P implant doses.

As is seen straight lines are fitted to the data. Intercepts of the line with vertical and horizontal axes yield  $R_c$  and  $L_T$  respectively.  $\rho_c$  and  $R_{sh}$  were then calculated.  $\rho_c$  versus P implant dose is shown in the main part of Figure 2.10.

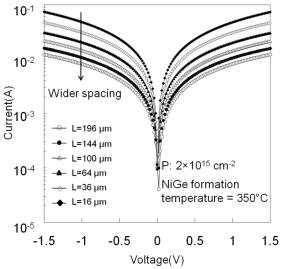

Note that the standard deviation was plotted in the form of error bars, but are so small here that they are barely visible (standard deviation in this case is between 2 to 5 percent). Increasing the implant dose resulted in decreasing the  $\rho_c$ , from  $7.97\times10^{-4}~\Omega.cm^2$  at the dose of  $5\times10^{14}~cm^{-2}$  to  $8.81\times10^{-5}~\Omega.cm^2$  at the dose of  $2\times10^{15}~cm^{-2}$ . The trend line empirically fitted to the data shows that the resistivity is proportional to  $x^{-1.59}$ , where x is the implant dose. When NiGe TLMs were used to extract  $\rho_c$  on p-type Ge [64],  $\rho_c$  was found to be proportional to  $N_A^{-0.62}$ , where  $N_A$  was the acceptor concentration and was in the  $10^{17}$ - $10^{20}~cm^{-3}$  range, i.e. increasing B concentration reduces  $\rho_c$ . For the P implant dose =  $2\times10^{15}~cm^{-2}$ , the I-V characteristics are shown in Figure 2.11. It can also be seen in the figure that the resistance between contacts increases as the spacing increases.

Figure 2.11: I-V characteristics for TLM structures where P implant dose is  $2\times10^{15}$  cm<sup>-2</sup> and NiGe formation temperature is 350 °C.

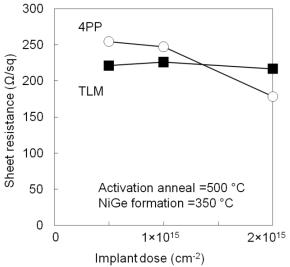

Figure 2.12 presents the  $R_{sh}$  of the P implanted samples versus the implant dose, extracted by standard 4PP and by the TLM structure. The error on the 4PP measurement was  $\pm$  10 %. The purpose here is to sanity-check the data extracted from the TLM electrical characterization. Essentially,  $R_{sh}$  of the samples is compared before and after TLM patterning, and show reasonable agreement.

Figure 2.12:  $R_{sh}$  calculated from TLM patterns versus the implant dose, comparing the  $R_{sh}$  of the samples before and after TLM patterning.

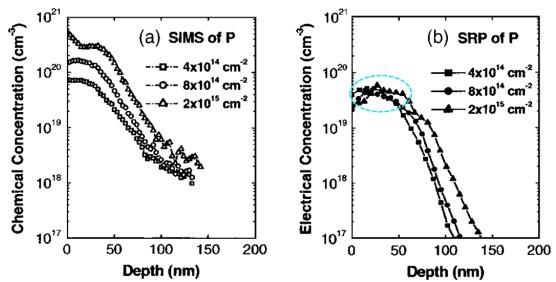

Secondary ions mass spectroscopy (SIMS) and spreading resistance probe (SRP) profiles for similar implant doses and RTA conditions to our work was done by Chui *et al.* [61] and is shown in Figure 2.13.

Figure 2.13: SIMS and SRP profiles of P after 10 s RTA at 500 with varying implanted doses from  $4\times10^{14}$  to  $2\times10^{15}$  cm<sup>-2</sup>. The electrical concentration in all the samples is limited to ~  $5\times10^{19}$  cm<sup>-3</sup> due to solubility limit of P in Ge. Copyright 2005 American Institute of Physics [61].

The results show very similar levels of active dopant concentrations for implant doses from  $4\times10^{14}$  to  $2\times10^{15}$  cm<sup>-2</sup> which indicates a solid solubility limit, and consequently  $R_{sh}$  does not show significant change for the implant range.  $R_{sh}$  values and SRIM modelling of the implanted profiles reveals that increasing the implant dose has increased the inactive P dose without significant change in the active P

dose. Regarding this, the decreasing  $\rho_c$  in Figure 2.10 could be attributed to the increase in inactive P dose piling up at the NiGe/Ge interface. There are many reports of impurities at the germanide or silicide interface modulating the eSBH [51], [45],[65].

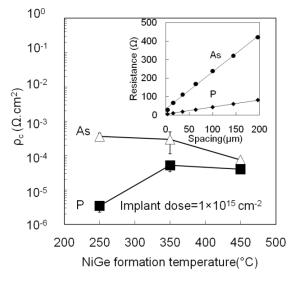

#### $2.6.2.2 \rho_c$ versus choice of implant

Next we consider the sample set where P and As implants were compared by implanting with the same dose and with energies so that the dopant profile had the same projected range. The inset in Figure 2.14 shows the total resistance of contacts versus spacing for the P and As implanted samples after 350 °C NiGe formation anneal.  $\rho_c$  of the TLM structures patterned on these samples were also extracted (Figure 2.14). The variable in this section was the NiGe formation temperature. It can be seen that at each temperature  $\rho_c$  of the P implanted sample is lower than that of the As case.

Figure 2.14: pc versus NiGe formation temperature. TLMs patterned on P implanted samples have lower resistance compared with As implanted samples. The inset shows the resistance as a function of spacing for both cases.

Chui *et al.* reported higher active doses for P over As after a 500 °C RTA [61]. Activation of As at 500 °C is poor presumably due to unfavourable solubility and tendency to form clusters at this temperature. Following the same methodology as in [60] the active levels for the P implanted samples here are in the order of  $3-6\times10^{19}$  cm<sup>-3</sup>, depending on the implant dose and energy. Higher active levels were achieved in [60] using a Ge pre amorphisation implant (PAI).

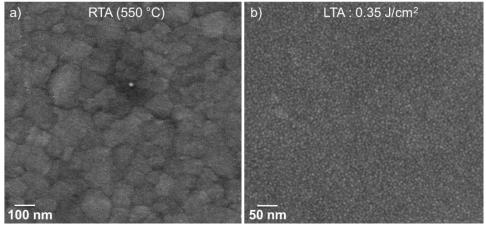

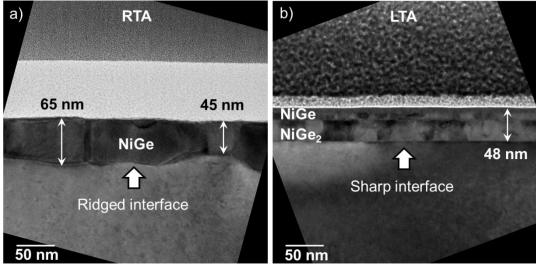

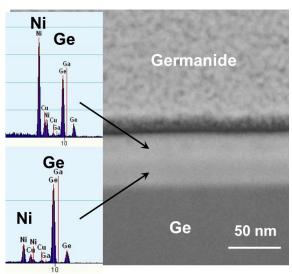

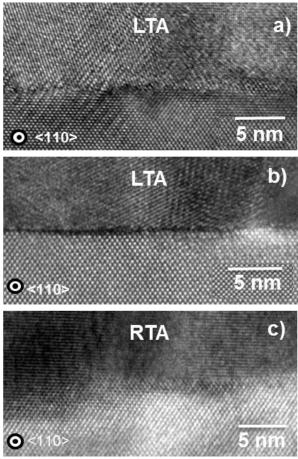

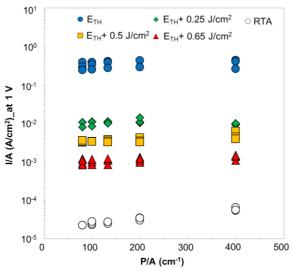

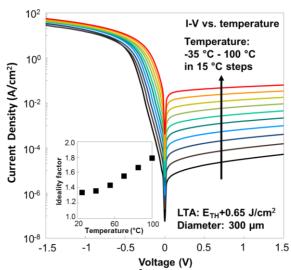

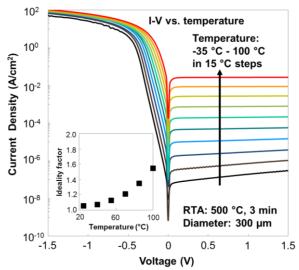

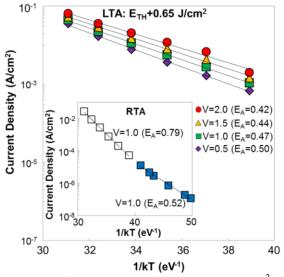

Table 2.2 represents  $\rho_c$  data, which to the best of our knowledge are currently in the public domain, relating to metal contacts on n-type doped Ge. Information regarding the contact material, dopant, and process conditions are listed therein.