| Title                       | Effect of low temperature RF plasma treatment on electrical properties of junctionless InGaAs MOSFETs                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Gomeniuk, Y. V.;Gomeniuk, Y. Y.;Rudenko, T. E.;Okholin, P.<br>N.;Glotov, V. I.;Nazarova, T. M.;Djara, Vladimir;Cherkaoui,<br>Karim;Hurley, Paul K.;Nazarov, A. N.                                                                                                                                                                                                                                                                                                   |

| Publication date            | 2019-03-02                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Original Citation           | Gomeniuk, Y. V., Gomeniuk, Y. Y., Rudenko, T. E., Okholin, P. N., Glotov, V. I., Nazarova, T. M., Djara, V., Cherkaoui, K., Hurley, P. K. and Nazarov, A. N. (2019) 'Effect of low temperature RF plasma treatment on electrical properties of junctionless InGaAs MOSFETs', ECS Journal of Solid State Science and Technology, 8(2), pp. Q24-Q31. doi: 10.1149/2.0181902jss                                                                                        |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Link to publisher's version | 10.1149/2.0181902jss                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Rights                      | © 2019, The Electrochemical Society. Published by IOP Publishing. This is an author-created, un-copyedited version of an article accepted for publication in ECS Journal of Solid State Science and Technology. The publisher is not responsible for any errors or omissions in this version of the manuscript or any version derived from it. The Version of Record is available online at 10.1149/2.0181902jss https://creativecommons.org/licenses/by-nc-nd/3.0/ |

| Download date               | 2025-05-09 16:58:11                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Item downloaded from        | https://hdl.handle.net/10468/10204                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Effect of Low Temperature RF Plasma Treatment on Electrical Properties of Junctionless InGaAs MOSFETs

Y. V. Gomeniuk, Y. Y. Gomeniuk, T. E. Rudenko, P. N. Okholin, V. I. Glotov, T. M. Nazarova, V. Djara, K. Cherkaoui, P. K. Hurley, and A. N. Nazarov<sup>1,3,\*,z</sup>

#### **Abstract**

In this paper, we study the effect of low-temperature RF plasma treatment in forming gas (10% H<sub>2</sub>+90% N<sub>2</sub>) on the electrical characteristics of junctionless MOSFETs with *n*-In<sub>0.53</sub>Ga<sub>0.47</sub>As channel and an Al<sub>2</sub>O<sub>3</sub> gate dielectric. The impact of plasma power density on the device parameters is investigated. It is found that RF plasma annealing with a low power density (0.5 W/cm<sup>2</sup>) at 150°C for 10 min provides substantial improvement of source/drain contacts resistance and the carrier mobility resulting in a considerable increase of the on-state current and transconductance. It also improves the subthreshold slope and reduces the fixed positive charge in Al<sub>2</sub>O<sub>3</sub> under the gate, shifting the threshold voltage towards positive values. It is demonstrated that non-thermal factors play a principle role in modification of electrical properties of the JL MOSFETs under RF plasma treatment. Such treatment may be an efficient tool for the improvement of the performance of the advanced MOSFETs with III-V channel materials.

This was Paper 1464 presented at the Seattle, Washington Meeting of the Society, May 13-17, 2018.

#### Introduction

The junctionless (JL) device concept for silicon-on-insulator MOSFETs was introduced by Colinge et al. in 2010, demonstrating considerable gains in terms of process simplicity when compared to conventional inversion-mode MOSFETs. The JL device architecture is particularly well suited to III-V channel materials. Firstly, a high body doping concentration ( $N_d$ ), being the key requirement for JL MOSFETs, is less problematic for  $In_{0.53}Ga_{0.47}As$  than it is for Si. Indeed, the bulk electron mobility in Si is  $\leq 100 \text{ cm}^2/\text{V} \cdot \text{s}$  at  $N_d = 1 \times 10^{19} \text{ cm}^{-3}$ , while in  $In_{0.53}Ga_{0.47}As$  the bulk mobility is  $\sim 2500 \text{ cm}^2/\text{V} \cdot \text{s}$  at a similar  $N_d$  level. Moreover, the JL architecture allows to obviate the difficulties associated with implantation or regrowth techniques generally used to form the source/drain (S/D) regions of III-V inversion-mode MOSFETs and to improve the thermal budget. Recently, tri-gate JL MOSFETs with the InGaAs channel have been demonstrated. A major concern for these devices is found to be a high S/D resistance ( $R_{SD}$ ). The formation of good Ohmic S/D contacts requires device annealing at temperatures  $\geq 300^{\circ}\text{C}$  that could lead to unintentional diffusion of In atoms into the gate dielectric. In this work, low-temperature RF plasma

<sup>&</sup>lt;sup>1</sup>Lashkaryov Institute of Semiconductor Physics NASU, Kyiv, Ukraine

<sup>&</sup>lt;sup>2</sup>Research Institute of Microdevices NASU, Kyiv, Ukraine

<sup>&</sup>lt;sup>3</sup>National Technical University of Ukraine "Igor Sikorsky KPI", Kyiv, Ukraine

<sup>&</sup>lt;sup>4</sup>Tyndall National Institute, University College Cork, Cork, Ireland

<sup>\*</sup>Electrochemical Society Member.

<sup>&</sup>lt;sup>z</sup>E-mail: nazarov@lab15.kiev.ua

treatment (RFPT)<sup>9</sup> is proposed to form S/D contacts and improve the performance of JL In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs. In our previous publications it has been shown that RF plasma treatment is efficient in reducing the density of fixed positive charges in SiO<sub>2</sub> layers and interface traps at the Si-SiO<sub>2</sub> interface, <sup>9-11</sup> annealing radiation-induced and ion implantation defects in metal-insulator-semiconductor (MIS) structures, <sup>12,13</sup> structural ordering and recrystallization of thin amorphous semiconductor layers, <sup>14,15</sup> low-temperature activation of implanted doping impurities in Si and Ge. <sup>15-17</sup> In this paper, we report that low-temperature RF plasma treatment in forming gas (10%H<sub>2</sub>+90%N<sub>2</sub>) can significantly improve the electrical characteristics of *n*-In<sub>0.53</sub>Ga<sub>0.47</sub>As JL MOSFETs with an Al<sub>2</sub>O<sub>3</sub> gate dielectric. In particular, it provides substantial reduction of S/D resistances, an increase of the electron mobility, resulting in the strong increase of the on-state current and transconductance, reduction of the effective positive charge in the Al<sub>2</sub>O<sub>3</sub> gate dielectric, and improvement of the subthreshold slope.

### **Experimental**

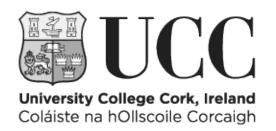

A structure consisting of a highly Si-doped ( $N_d = 2 \times 10^{18}$  cm<sup>-3</sup>) 32-nm-thick n-In<sub>0.53</sub>Ga<sub>0.47</sub>As layer on a 500-nm-thick Zn-doped p-In<sub>0.52</sub>Al<sub>0.48</sub>As ( $N_a = 8 \times 10^{15}$  cm<sup>-3</sup>) barrier was grown by metal organic vapour-phase epitaxy (MOVPE) on a  $p^+$ -InP wafer. Schematic representation and transmission electron microscopy image of the resulting heterostructure is illustrated in Figure 1 (a). In order to form a channel for the JL devices, the In<sub>0.53</sub>Ga<sub>0.47</sub>As layer was thinned using a 10% H<sub>2</sub>O<sub>2</sub>/10% HCl digital wet etching process to achieve channel thickness of 20 nm. A gate enclosed device layout was employed to simplify the fabrication process flow. The main steps of the In<sub>0.53</sub>Ga<sub>0.47</sub>As junctionless n-MOSFET fabrication process are illustrated in Figures 1(b-e)). A surface passivation in 10% (NH<sub>4</sub>)<sub>2</sub>S for 30 min<sup>18</sup> was performed before atomic layer deposition (ALD) of an 8.5-nm-thick Al<sub>2</sub>O<sub>3</sub> gate oxide. A Pd gate was formed by e-beam evaporation and lift-off. No S/D implantation and no selective epitaxial growth were used to reduce the S/D resistance. The Al<sub>2</sub>O<sub>3</sub> on the S/D contact areas was etched in dilute HF. The S/D contact formation was carried out by e-beam evaporation of a Au/Ge/Au/Ni/Au stack and lift-off.

The samples used in this study were not subjected to any post-fabrication thermal anneal; instead the fabricated samples were exposed to the RF (13.6 MHz) plasma treatment in forming gas (10%  $H_2 + 90\%$   $N_2$ ) during 10 min with additional heating of the sample holder to 150°C. Plasma power density was varied from 0.5 to 1.75 W/cm². Temperature of the samples during RF plasma treatment did not exceed 250°C. In order to distinguish between thermal and non-thermal effects of the RFPT in some cases the treatment was performed in the same process for two chips - one from the side of metal electrodes (top side) and another from the side of  $p^+$ -InP substrate (back side).

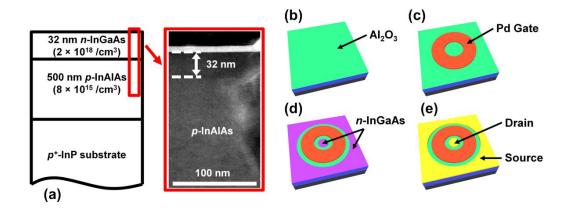

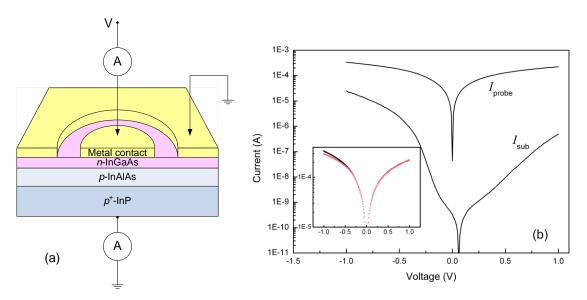

Figure 2 (a) shows a schematic view of the gate-enclosed junctionless MOSFET architecture, where  $r_g$ ,  $r_s$ ,  $r_g^{in}$  and  $r_g^{out}$  are the drain, source, gate inner and gate outer radii, respectively. The MOSFETs being investigated had the gate length  $L_g = r_g^{out} - r_g^{in}$  of 40, 60 and 80  $\mu$ m with a 10- $\mu$ m separation between the gate and source and drain contact pads. The devices with large  $L_g$  values were used for avoiding short-channel effects when investigating the impact of RF plasma treatment on the electrical properties of InGaAs JL MOSFETs.

Layout of the circular transmission line  $(CTL)^{19}$  which was used for measurements of sheet resistance of n-In<sub>0.53</sub>Ga<sub>0.47</sub>As layer and of specific contact resistance of S/D contacts is shown in Figure 2 (b). Current-voltage (I-V) characteristics of JL MOSFETs and CTL were measured by Agilent 4156C precision semiconductor parameter analyzer. Most measurements were performed with grounded outer electrode and electrically isolated (floating) substrate to avoid a parasitic effect of a leakage current through the buried p-n junction. This regime corresponds to zero current through the substrate. In some cases, to determine properties of the buried p-n junction and the effect of plasma treatment, the substrate was grounded.

#### **Results and Discussion**

Effect of RF plasma treatment on sheet resistance and specific contact resistance. The specific contact resistance,  $\rho_c$ , is the parameter used to characterize metal/semiconductor interface, which is independent on the geometry of the contact. Measurements of the specific contact resistance and sheet resistance of the semiconductor film were carried out using simplified two-contact CTL technique. Test structures consisted of inner circular contact pads with radius r of 100  $\mu$ m separated from the surrounding outer contact of larger area with different gap spacings d of 16, 24, 32, 40, 48, 64, 80 and 96  $\mu$ m (see Figure 2 (b)). The outer radius of semiconductor film ring not covered by metallization is then R = r + d. The total resistance between two contacts separated by a circular gap is given by:

$$R_{t} = \frac{R_{sh}}{2\pi} \times \left[ \ln \left( \frac{R}{r} \right) + L_{t} \left( \frac{1}{R} + \frac{1}{r} \right) \right], \tag{1}$$

where  $R_{\rm sh}$  is the sheet resistance of the semiconductor film, r and R represent the radius of the inner and outer contacts, respectively, and  $L_{\rm t}$  is the transfer length. The total resistance measured for different spacing is plotted as function of  $\ln(R/r)$  and approximated by a straight line. The slope of this line is equal to  $R_{\rm sh}/2\pi$ , and the intercept with the Y axis at  $\ln(R/r)=0$  is  $R_{\rm sh}\cdot L_{\rm t}/\pi r$ , giving  $L_{\rm t}$ . Then the specific contact resistance,  $\rho_c$ , can be found from the equation:

$$L_{t} = \sqrt{\frac{\rho_{c}}{R_{sh}}} \tag{2}$$

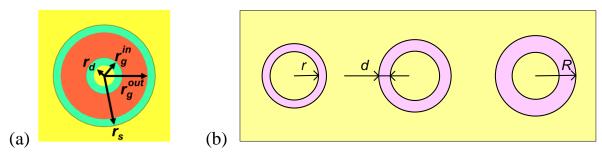

First we checked an absence of the possible effect of the buried p-n junction degradation, which may occur after the plasma treatment, on the measurement results.  $I_{sub}$ -V characteristic of the buried p-n junction (where  $I_{sub}$  is the current through the p-n junction into the substrate) was measured together with I-V characteristic of the element of CTL. The circuit diagram of the measurements is presented in Figure 3 (a). When the substrate and the outer electrode of CTL (see Figures 2 (b) and 3 (a)) are grounded a good rectifying  $I_{sub}$ -V characteristic is observed (Figure 3 (b)).  $I_{sub}$  current through the buried p-n junction is several orders of magnitude smaller than the measured current between contacts of CTL almost in the whole voltage range, and the I-V characteristics of CTL with grounded substrate and electrically isolated substrate match exactly in the range of the inner contact voltage from -0.5V to +1 V (Figure 3 (b), inset). The total resistance of the structure was determined in the range with minimum leakage current where I-V characteristics for grounded and isolated substrate

electrode coincide. In this case the error in determination of the film and contact resistance has to be rather small.

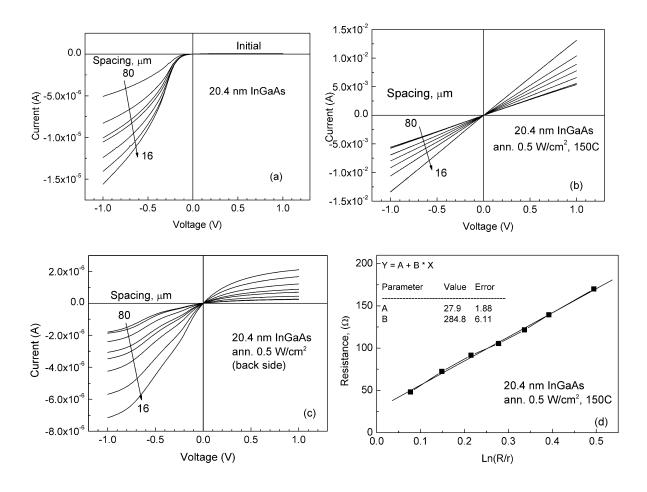

Figures 4 (a)-(c) show the current-voltage characteristics measured on CTL structures with different spacing and electrically isolated substrate before and after RFPT for the 20 nm InGaAs film. It can be seen in Figure 4 (a) that I-V characteristics of the initial sample are strongly non-linear due to presence of a rectifying barrier between metal and semiconductor after metallization. The strong asymmetry of the I-V curves is due to different areas of the two contacts. At positive voltage the current is limited by the higher resistance of the reverse connected diode of the small inner contact, and is substantially lower than at negative voltage of the same magnitude, when the limiting contact has much larger area and, respectively, lower resistance. In the case of non-linear current-voltage characteristics we determined for further evaluations the resistance of the test structure as a reciprocal of the maximum differential conductance (dI/dV). After RF plasma annealing from top side with power density of 0.5 W/cm<sup>2</sup> at 150°C the current-voltage characteristics (Figure 4(b)) become absolutely linear reflecting the conversion of the rectifying contacts into Ohmic ones. After RF plasma annealing from back side at the same treatment regime the level of currents is approximately the same as in the initial sample and the contacts remain evidently non-Ohmic (Figure 4 (c)). Figure 4 (d) illustrates the procedure of extracting of sheet resistance and contact resistivity from the CTL measurements. The slope of the approximating straight line leads to  $R_{\rm sh}$ , and from the intercept the value of the specific contact resistivity  $\rho_c$  can be determined. One can see that after RFPT from top side with plasma power density of 0.5 W/cm<sup>2</sup> both sheet resistance and contact resistance are reduced dramatically. Sheet resistance of the 20-nm-thick film reduces from  $\approx 330 \text{ k}\Omega/\text{sq}$  to about 2 k $\Omega/\text{sq}$  after RFPT at 0.5 W/cm<sup>2</sup>. Specific contact resistivity also falls by more than two orders of magnitude after such treatment. After the RFPT from back side the contact resistivity and sheet resistance are changed insignificantly.

Comparison of the results obtained after RFPT of the structures treated from top side and back side indicates that strong non-thermal effects occur during the plasma treatment from top side. Indeed at top-side RFPT the following factors affect subsurface layers of the structure<sup>9</sup>: thermal heating; low-energy ion and electron bombardment; x-ray and UV irradiation combining with alternating RF electric field; protons as catalyst of defect transformation. Under RF plasma treatment from the back side, the main factors that influence the studied layers are temperature, soft x-ray irradiation, and alternating electric field. Thus, a decrease of specific contact resistivity after RFPT from top side is probably attributable to low-energy ion and electron bombardment of the multilayer contact structure during plasma exposure, resulting in the formation of Ohmic contacts due to reduction of the potential barrier at the metal/semiconductor interface. It should be noted that Schottky barrier height reduction on n-GaAs at low-energy ion bombardment was previously observed by a number of authors. <sup>23-25</sup>

Reduction of the sheet resistance of uncoated *n*-InGaAs film under N<sub>2</sub>/H<sub>2</sub> plasma exposure from top side can be attributed to surface nitridation, resulting in suppression of Ga oxides and As oxides and formation of Ga-N bonds at the surface, which strongly reduces the interface trap density, and hydrogen passivation of bulk and surface defects. However, hydrogen in III-V semiconductors also is known to passivate (or deactivate) shallow dopants, specifically Si, which reduces the free carrier concentration in the semiconductor layer. The latter effect is temperature-dependent and reversible, since a temperature increase brings

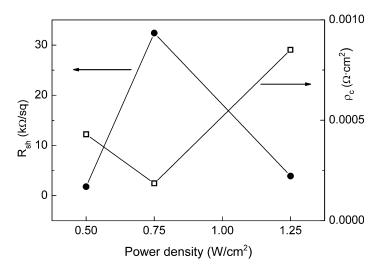

about the dopant reactivation. <sup>25,28-30</sup> This allows explaining the hump on the dependence of the sheet resistance on the plasma power density (see Figure 5). Figure 5 illustrates also the variation of specific contact resistivity with the RF plasma power density. Specific contact resistivity reaches the lowest values at plasma power density 0.75 W/cm<sup>2</sup> and increases with further increasing power density, which can be attributed to the ion bombardment damage.

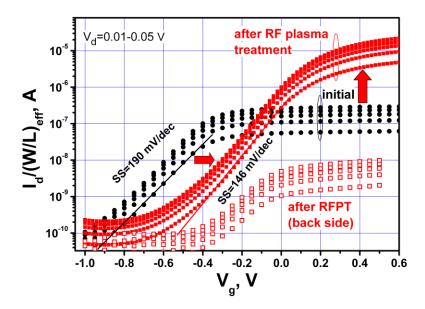

Effect of RF plasma treatment on transfer characteristics of JL MOSFETs n-InGaAs channel and ALD  $Al_2O_3$  gate dielectric. - Figure 6 shows drain current  $(I_d)$  versus gate voltage  $(V_g)$  transfer characteristics measured as the drain voltage  $(V_d)$  varied from 10 mV to 50 mV on the 40-µm-gate-length n-InGaAs JL MOSFET before and after RF plasma treatment at a low plasma power density P=0.5 W/cm². The drain current values in Figure 6 are normalized to the effective gate width-to-length ratio,  $(W/L)_{eff}$ , which for a gate-enclosed transistor with annular gate is expressed as: $^{32}$

$$\left(\frac{W}{L}\right)_{eff} = \frac{2\pi}{\ln\left(r_g^{out}/r_g^{in}\right)},\tag{3}$$

where  $r_g^{out}$  and  $r_g^{in}$  are gate outer and gate inner radii, respectively.

As is seen from Figure 6, RF plasma treatment from top side results in the shift of the  $I_d(V_g)$ - characteristics towards positive values, which is indicative of the reduction of the fixed positive charge in the gate dielectric. The threshold voltage  $(V_{th})$  evaluated by the second derivative method<sup>33</sup> before and after plasma treatment at the plasma power density of 0.5 W/cm<sup>2</sup> is, respectively, -0.49 V and 0.05 V. This  $V_{th}$  shift is attributable to the reduction of an equivalent density of fixed positive oxide charge at the Al<sub>2</sub>O<sub>3</sub>/ n-In<sub>0.53</sub>Ga<sub>0.47</sub>As interface in the gated area by ~2.8×10<sup>12</sup> /cm<sup>2</sup>. The reduction of positive charge is consistent with what is observed with a standard forming gas anneal in a 5%  $H_2/95\%$   $N_2$  ambient at 350 °C for 30 minutes.<sup>34</sup> Another consequence of RF plasma treatment is a decrease of the inverse subthreshold slope (SS) from 190 mV/dec to 150 mV/dec, which can be attributed to the reduction of the interface trap density  $(D_{it})$  from ~1.1×10<sup>13</sup> /cm<sup>2</sup>·eV to 7.5×10<sup>12</sup>/cm<sup>2</sup>·eV. However, the most remarkable result of RF plasma treatment is significant increase (approximately by two orders of magnitude) of the on-state current,  $I_{ON}$ , which is evidently related to reduction of the S/D contact series resistance, since initial samples were not subjected to any post-metallization processing and RF plasma was used for contact annealing. The on-to-off current ratio  $(I_{ON}/I_{OFF})$  after plasma annealing at the plasma power density P=0.5W/cm<sup>2</sup> is  $\approx 1.7 \times 10^{5}$ .

It is worth to note that RFPT from back side does not increase the  $I_{ON}/I_{OFF}$  ratio in comparison with the initial device and even slightly deteriorates the subthreshold slope (see Figure 6). The first effect is due to the absence of reduction of the S/D contact series resistance; and the second one reflects the increase of the interface trap density and/or of surface potential fluctuations. At the same time the shift of the  $I_d(V_g)$  - characteristic (about 0.45V) towards positive values is observed as a result of reduction of fixed positive oxide charge in the  $Al_2O_3$  gate dielectric. The value of the shift is similar (a bit smaller) to that after RFPT from top side, and it is possible to conclude that in this case the same mechanisms of charge annealing can

take place. As it was mentioned before the main factors affecting the gate dielectric and InGaAs film at RF plasma treatment from back side are temperature, RF electric field and soft x-ray irradiation. Combination of the last two factors results in strong electron and hole injection from the semiconductor and from the metal gate into the gate dielectric leading to recombination-enhanced processes of fixed positive change neutralization and defects annealing in the dielectric.<sup>35</sup>

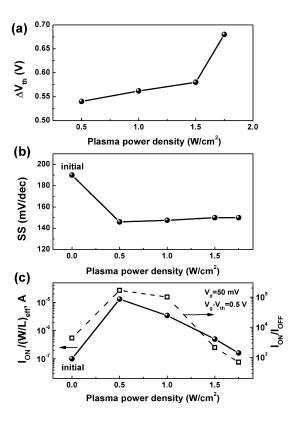

Figures 7(a)-(c) illustrate the impact of the plasma power density on the threshold voltage shift  $\Delta V_{th}$ , the inverse subthreshold slope SS, as well as the on-current and on-to-off current ratio. on the plasma power density. It can be seen that the threshold voltage shift tends to increase with power density (Figure 7(a)). Increasing the plasma power density from 0.5 W/cm<sup>2</sup> to 1.75 W/cm<sup>2</sup> has only a minor effect on SS (Figure 7(b)), however, it strongly decreases  $I_{ON}$  and  $I_{ON}/I_{OFF}$  ratio (Figure 7(c)), which can be explained by both degradation of the mobility and an increase of the parasitic S/D resistance.

Effect of RF plasma treatment on electron mobility and source-drain series resistance in InGaAs JL MOSFETs. - The carrier mobility was evaluated using the Y-function methodology and the split C-V method. According to the approach developed in  $^{36}$  for heavily doped Si layers, the drain current in JL MOSFET in volume conduction region with considering the parasitic S/D resistance,  $R_{SD}$ , can be written as:

$$I_d = \frac{W}{L} \cdot C_{ox} \cdot \frac{\mu_{vol}}{1 + \theta_1 (V_g - V_0)} \cdot (V_g - V_0) \cdot V_d, \tag{4}$$

where W and L are the gate width and length, respectively,  $C_{ox}$  is the gate dielectric capacitance,  $\mu_{vol}$  is the carrier mobility in the volume of the semiconductor layer assumed to be uniform across the film thickness,  $V_g$  is the gate voltage,  $V_0$  is a characteristic gate voltage, which provides full depletion of the film,  $V_d$  is the drain voltage, and  $\theta_l$  is the coefficient considering  $R_{SD}$ :

$$\theta_1 = R_{SD} \cdot \mu_{vol} \cdot C_{ox} \cdot \frac{W}{L} \quad . \tag{5}$$

From (4) one can obtain:

$$Y_{vol} = \frac{I_d}{\sqrt{g_m(V_g)}} = \sqrt{\frac{W}{L} \cdot C_{ox} \cdot \mu_{vol} \cdot V_d} \cdot (V_g - V_0), \tag{6}$$

where the effect of  $R_{SD}$  is eliminated. From (6) it follows that the slope of the  $Y_{vol}(V_g)$  dependence yields the value of  $\mu_{vol}$  being unaffected by the S/D series resistance. Thus the procedure for the extraction of  $\mu_{vol}$  in JL MOSFETs is similar to that in the conventional Y-function technique used for extracting low-field mobility,  $\mu_0$ , in inversion-mode MOSFETs.<sup>37</sup> The S/D series resistance  $R_{SD}$  is involved in the coefficient  $\theta_1$ , which is obtainable from the slope of  $1/\sqrt{g_m}$  versus  $V_g$  dependence:<sup>38</sup>

$$\frac{1}{\sqrt{g_m(V_g)}} = \frac{1 + \theta_1 \cdot (V_g - V_0)}{\sqrt{C_{ox} \cdot \frac{W}{L} \cdot \mu_{vol} \cdot V_d}}.$$

(7)

In the case of the transistor with annular gate, the ratio W/L in equations (4)-(7) should be replaced by the effective gate width-to-length ratio  $(W/L)_{eff}$  given by eq. (3).

Since the physical meaning of the threshold voltage in JL MOSFETs is the transition from the full depletion regime to partially depletion regime, we can consider  $V_0 \approx V_{th}$ . The range of  $V_g$  corresponding to volume conduction regime in JL MOSFETs (between the threshold voltage  $V_{th}$  and flat band voltage  $V_{FB}$ ) is usually identified from the positions of the two peaks of the second derivative of the drain current versus gate voltage characteristics,  $d^2I_{d'}dV_g^2$ . However, in the case of relatively high series resistance, the second peak in the  $d^2I_{d'}dV_g^2$  curves, associated with the transition to the surface accumulation regime, is not pronounced, <sup>40</sup> as in our case. The  $V_g$  range corresponding to volume conduction can be estimated as follows:

$$\Delta V_g = V_{FB} - V_{th} \approx \frac{q \cdot N_d \cdot t_{hGaAs}^2}{2 \cdot \varepsilon_{hGaAs}} + \frac{q \cdot N_d \cdot t_{hGaAs}}{C_{ox}}, \tag{8}$$

which for our device parameters is  $\approx 0.8 \text{ V}$ .

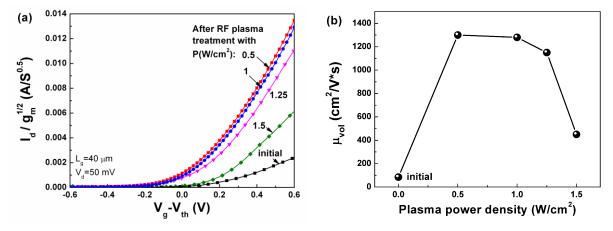

Figure 8(a) shows  $Y_{vol} = I_d / \sqrt{g_m}$  versus gate voltage overdrive  $(V_g - V_{th})$  obtained at

$V_d$ =50 mV on the 40-µm-gate-length JL MOSFETs before and after RF plasma treatment with various plasma power densities. It is clearly seen that plasma annealing, especially at a low power density, results in the strong increase of the slope of the linear region of the Y-function compared to that for the initial sample, suggesting that RF plasma treatment increases the carrier mobility in the  $In_{0.53}Ga_{0.47}As$  film. The extracted mobility values obtained for the initial sample and after RF plasma treatment with different plasma power densities are presented in Figure 8(b). The value of  $\mu_{vol}$  obtained for the initial sample is  $\approx$ 90 cm²/V·s, whereas after plasma annealing with a low plasma power density (P=0.5  $\div$  1 W/cm²) it is  $\approx$ 1300 cm²/V·s. This is attributable to RF plasma-assisted annealing of bulk and surface defects in the  $In_{0.53}Ga_{0.47}As$  film, due to a cooperative effect of the RF field, the X-ray radiation, and the induced wafer temperature, resulting in the recombination-enhanced defect reactions in metal-insulator-semiconductor structures. An increase of the plasma power density from 1.25 W/cm² to 1.5 W/cm² results in the significant mobility degradation, which is explainable by the creation of new defects (Figure 8 b), resulting from the increase of the intensity of X-ray and UV radiation accompanying RFPT.

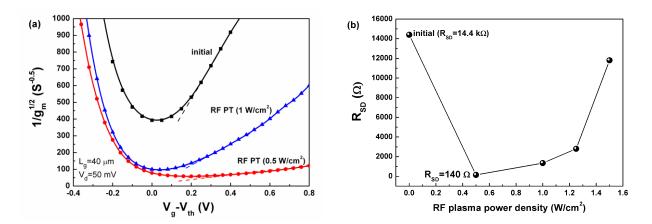

Plotted in Figure 9(a) are  $1/\sqrt{g_m}$  versus  $(V_g - V_{th})$  characteristics obtained on the InGaAs JL MOSFETs with  $L_g$ =40  $\mu$ m before and after RF plasma treatment at two different plasma power densities, 0.5 W/cm<sup>2</sup> and 1 W/cm<sup>2</sup>. Larger slope of the  $1/\sqrt{g_m}$  curve above  $V_{th}$  for the initial sample suggests larger S/D series resistance. The obtained results for  $R_{SD}$  in the initial

sample and after RF plasma treatment at different plasma power densities are presented in Figure 9(b). As follows from Figure 9(b), plasma treatment at P=0.5 W/cm² results in the considerable (by two orders of magnitude) reduction of  $R_{SD}$ , namely, from 14.4 k $\Omega$  in the initial sample to 140  $\Omega$  after RF plasma anneal, which agrees well with results for the contact resistance. It should be noted that in the devices with a given geometry the source/drain parasitic resistance  $R_{SD}$  is determined not only by the contact resistance, but also it includes the resistance of the n-In<sub>0.53</sub>Ga<sub>0.47</sub>As film outside of the Pd gate between the gate and source and drain regions (see Figure 2). Therefore, one would expect that the treatment, which reduces the fixed positive charge in Al<sub>2</sub>O<sub>3</sub>, can increase  $R_{SD}$  and thereby reduce  $I_{ON}$  due to a decrease or removal of accumulation in the non-gated regions of the n-In<sub>0.53</sub>Ga<sub>0.47</sub>As film, as it was observed in the case of H<sub>2</sub>/N<sub>2</sub> thermal anneal reported in Ref. 42. However, the effect of RF plasma is most likely not the same for the insulator/semiconductor systems with and without metal gate.

An increase of the plasma power density from  $0.5 \text{ W/cm}^2$  to  $1.25 \text{ W/cm}^2$  results in the gradual increase of  $R_{SD}$ ; further increase of plasma power sharply increases  $R_{SD}$ . This can be explained by the defect formation in the InGaAs film with an increase of the energy of incident bombarding ions.

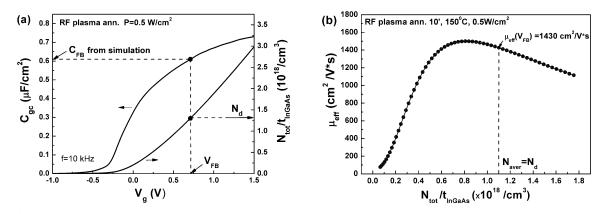

Using combined drain current and gate-to-channel capacitance ( $C_{gc}$ ) versus  $V_g$  measurements, we evaluated the effective electron mobility for plasma power density of 0.5 W/cm², which provides the best results in terms of  $I_{ON}$ ,  $\mu_{vol}$  and  $R_{SD}$ . The extraction of the effective electron mobility ( $\mu_{eff}$ ) was performed on the test MOSFETs with channel length of 100 and 150  $\mu$ m. The  $C_{gc}$ - $V_g$  characteristic used for the extraction of  $\mu_{eff}$  is shown in Figure 10(a). Resulting  $\mu_{eff}$  is presented in Figure 10(b) as a function of the average carrier concentration  $N_{aver}$  in the  $In_{0.53}Ga_{0.47}As$  film, where  $N_{aver}$  was obtained by dividing the total carrier density  $N_{tot}$  by the film thickness,  $N_{aver} = N_{tot} / t_{InGasAs}$ , and  $N_{tot}$  was obtained by integrating the measured  $C_{gc}(V_g)$  curve. Using a value of a flat-band capacitance ( $C_{FB}$ ) of 0.61  $\mu$ F/cm², obtained from Poisson-Schrödinger simulations, we extracted for a given plasma power density a flat-band voltage  $V_{FB}$  of 0.71 V and electrically active doping concentration in the  $In_{0.53}Ga_{0.47}As$  film ( $N_d$ ) of 1.3×10<sup>18</sup>/cm³ (Figure 10(a)). As is seen from Figure 10(b), the maximum value of  $\mu_{eff}$  for a given plasma power density is ≈1500 cm²/V·s, whereas at flat-band conditions it is ≈1430 cm²/V·s. The obtained results for  $\mu_{eff}$  agree well with the corresponding  $\mu_{vol}$  value extracted by the Y-function method.

#### **Conclusions**

In summary, we investigated the effects of the RF plasma treatment in the forming gas (10%H<sub>2</sub>+90%N<sub>2</sub>) on the characteristics of In<sub>0.53</sub>Ga<sub>0.47</sub>As channel MOS transistors with an Al<sub>2</sub>O<sub>3</sub> gate dielectric and having a junctionless layout. We have demonstrated that RF plasma treatment at 150-200°C for 10 min with a low power density (~0.5 W/cm<sup>2</sup>) allows one to anneal effectively the source/drain contacts to the InGaAs film decreasing the contact resistance by more than two orders of magnitude without degradation of buried p-n junction. Moreover, RF plasma treatment provides strong enhancement of the carrier mobility in the In<sub>0.53</sub>Ga<sub>0.47</sub>As film, which together with reduction of the source/drain resistance results in the dramatic increase of the on-current. It was found also that RFPT reduces the built-in positive charge in the dielectric layer shifting the threshold voltage to positive values. It was

demonstrated that non-thermal factors play a principle role in modification of electrical properties of the JL MOSFETs under RFPT. RF plasma treatment was proven to be an effective technique for formation of source/drain contacts and for improvement of the performance of the In<sub>0.53</sub>Ga<sub>0.47</sub>As JL MOSFETs, and more generally could be applicable to reduction of source/drain resistance in 3D sequential integration.

## Acknowledgments

The authors acknowledge the financial support of the EU Horizon 2020 programme, through the project ASCENT (grant agreement 654384), and of Science Foundation Ireland through the project INVEST (15/IA/3131).

#### References

- 1. J.-P. Colinge, C.-W. Lee, A. Afzalian, N.D. Akhavan R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and R. Murphy, *Nature Nanotechnology*, **5**, 225 (2010).

- 2. G. Mazetti, M. Severi, and S. Solmi, *IEEE Trans. on Electron Dev.*, 30, 764 (1983).

- 3. N. Daix, E. Uccelli, L. Uccelli, D. Caimi, C. Rossel, M. Sousa, H. Siegwart, C. Marchiori, J. M. Hartmann, K.-T. Shiu, C.-W. Cheng, M. Krishnan, M. Lofaro, M. Kobayashi, D. Sadana, and J. Fompeyrine, *APL Mater.*, **2**, 086104 (2014).

- 4. V. Djara, K. Cherkaoui, S. B. Newcomb, K. Thomas, E. Pelucchi, D. O'Connell, L. Floyd, V. Dimastrodonato, L. O. Mereni, and P. K. Hurley, *Semiconductor Science and Technology*, **27**, 082001 (2012).

- 5. M. A. Negara, V. Djara, T. P. O'Regan, K. Cherkaoui, M. Burke, Y. Y. Gomeniuk, M. Schmidt, E. O'Connor, I. M. Povey, A. J. Quinn, and P. K. Hurley, " *Solid-State Electronics*, **88**, 37 (2013).

- 6. U. Singisetti, M. A. Wistey, G. J. Burek, A. K. Baraskar, B. J. Thibeault, A. C. Gossard, M. J. W. Rodwell, S. Byungha, E. J. Kim, P. C. McIntyre, Y. Bo, Y. Yu, D. Wang, T. Yuan, P. Asbeck, and L. Yong-Ju, *Electron Device Letters*, *IEEE*, **30**, 1128 (2009).

- 7. V. Djara, L. Czornomaz, V. Deshpande, N. Daix, E. Uccelli, D. Caimi, M. Sousa, J. Fompeyrine, *Solid State Electronics*, **115**, 103 (2016).

- 8. C. B. Zota, M. Borg, L.-E. Wernersson, and E. Lind, *Jpn. Journ. Appl. Phys.*, **56**, 120306 (2017).

- 9. A. N. Nazarov, V. S. Lysenko and T. M. Nazarova, *Semiconductor Physics, Quantum Electronics & Optoelectronics*, **11**, 101 (2008).

- 10. V. S. Lysenko, A. N. Nazarov, I. N. Osiyuk, V. I. Turchanikov, *Appl. Surf. Sci.* **39** (1), 388 (1989).

- 11. A. N. Nazarov, V. I. Kilchitska, I. P. Barchuk, A. S. Tkachenko, S. Ashok, *J. Vac. Sci. Technol. B* **18** (3), 1254 (2000).

- 12. V. S. Lysenko, M. M. Lokshin, A. N. Nazarov, and T. E. Rudenko, *Phys. status solidi* (a) **88** (2), 705 (1985).

- 13. V. S. Lysenko, A. N. Nazarov, S. A. Valiev, I. M. Zaritskii, T. E. Rudenko, and A. S. Tkachenko, *Phys. status solidi* (a), **113** (2), 655 (1989).

- 14. V. V. Artamonov, V. S. Lysenko, A. N. Nazarov, B. D. Nichiporuk, V. V. Streltchuk, and M. Ya. Valakh, *Phys. status solidi* (a), **120** (2), 475 (1990).

- 15. P. N. Okholin, V. I. Glotov, A. N. Nazarov, V. O. Yuchymchuk, V. P. Kladko, S. B. Kryvyi, P. M. Lytvyn, S. I. Tiagulskyi, V. S. Lysenko, M. Shayesteh, and R. Duffy, *Materials Science in Semiconductor Processing*, **42.** 204 (2016).

- 16. M. Ya. Valakh, V. S. Lysenko, A. N. Nazarov, G. Yu. Rudko, A. S. Tkachenko, and N. I. Shakhraychuk, *Nucl. Instr. and Meth. Phys. Res. B*, **44**, 146 (1989).

- 17. A. N. Nazarov, V. O. Yukhymchuk, Y. V. Gomeniuk, S. B. Kryvyi, P. N. Okholin, P. M. Lytvyn, V. P. Kladko, and V.S. Lysenko, *J. Vac. Sci. Technol.* **B 35**, 051203 (2017).

- 18. É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, *Journal of Applied Physics*, **109**, 024101 (2011).

- 19. G. K. Reeves, *Solid-State Electronics*, **23**, 487(1980).

- 20. G. S. Marlow and M. B. Das, Solid State Electronics, 25, 91 (1982).

- 21. Y. Pan, G. K. Reeves, P. W. Leech, and A. S. Holland, *IEEE Transactions on Electron Devices*, **60**, 1202 (2013).

- 22. J.-K. Ho, C.-S. Jong, C. C. Chiu, C.-N. Huang, K.-K. Shih, L.-C. Chen, F.-R. Chen, and J.-J. Kai, *Journal of Applied Physics*, **86**, 4491(1999).

- 23. Y. G.. Wang and S. Ashok, *Physica B*, **17**, 513 (1991).

- 24. T. Neffati, G.N. Lu and C. Barret, Solid State Electronics, 31. 1335 (1988).

- 25. Y. G.. Wang and S. Ashok, *Journal of Applied Physics*, **75**, 2447 (1994).

- 26. T. Hoshii, M. Yokoyama, H. Yamada, M. Hata, T. Yasuda, M. Takenaka, and S. Takagi, *Applied Physics Letters*, **97**, 132102 (2010).

- 27. T. Hoshii, S. Lee, R. Suzuki, N. Taoka, M. Yokoyama, H. Yamada, M. Hata, T. Yasuda, M. Takenaka, and S. Takagi, *Journal of Applied Physics*, **112**, 073702 (2012).

- 28. J. Chevallier, W.C. Dautremont-Smith, C.W. Tu, S.J. Pearton, *Applied Physics Letters*, **47**, 108 (1985).

- 29. J. C. Nabity, Michael Stavola, J. Lopata, W. C. Dautremont-Smith, C. W. Tu, and S. J. Pearton, *Applied Physics Letters*, **50**, 921 (1987).

- 30. A. Jalil, A. Heurtel, Y. Marfaing, and J. Chevallier, *Journal of Applied Physics*, **66**, 5854 (1989).

- 31. S. M. Lord, G. Roos, J.S. Harris Jr., and N.M. Johnson, *Journal of Applied Physics*, **73**, 740 (1993).

- 32. J. A. De Lima, S. P. Gimenez, and K. H. Cirne, *IEEE Transactions on Power Electronics*, **27**, 1622 (2012).

- 33. H. S. Wong, M.H. White, T. J. Krutsick, and R.V. Booth, *Solid State Electronics*, **30**, 953 (1987).

- 34. P. K. Hurley, É. O'Connor, V. Djara, S. Monaghan, I. M. Povey, R. D. Long, B. Sheehan, J. Lin, P. C. McIntyre, B. Brennan, R. M. Wallace, M. E. Pemble, and K. Cherkaoui, *IEEE Transactions on Device and Materials Reliability*, **13**, 429 (2013).

- 35. T. P. Ma and M. R. Chin, *Journal of Applied Physics*, **51**, 5458 (1980).

- 36. F. Y. Liu, A. Diab, I. Ionica, K. Akarvardar, C. Hobbs, T. Ouisse, X. Mescot, and S. Cristoloveanu, *Solid State Electronics*, **90**, 65 (2013).

- 37. G. Ghibaudo, *Electronics Letters*, **24**, 543 (1988).

- 38. H. J. Park, L. Pirro, L. Czornomaz, I. Ionica, M. Bawedin, V. Djara, V. Deshpande, and S. Cristoloveanu, *Solid State Electronics*, **128**, 80 (2017).

- 39. D.-Y. Jeon, S. Park, M. Mouis, M. Berthom, S. Barraud, G.-T. Kim, and G. Ghibaudo, *Solid-State Electron.* **90**, 86 (2013).

- 40. D.-Y. Jeon, S.J. Park, M. Mouis, S. Barraud, G.-T. Kim, and G. Ghibaudo, *Solid State Electronics*, **129**, 103 (2017).

- 41. T. P. Ma, W. H.-L. Ma, Solid State Electronics, 22 (4), 663 (1979).

- 42. V. Djara, K. Cherkaoui, M. Schmidt, S. Monaghan, É. O'Connor, I. M. Povey, D. O'Connell, M. E. Pemble, and P. K. Hurley, *IEEE Transactions on Electron Devices*, **59**, 1084 (2012).

**Figure 1.** (a) Cross-section schematic and transmission electron microscopy image of the MOVPE grown  $n\text{-In}_{0.53}\text{Ga}_{0.47}\text{As}$  (32 nm)/ $p\text{-In}_{0.52}\text{Al}_{0.48}\text{As}$  (500 nm)/ $p^+$ -InP wafer structure. The In<sub>0.53</sub>Ga<sub>0.47</sub>As Junctionless n-MOSFET fabrication process flow including (b) (NH<sub>4</sub>)<sub>2</sub>S passivation and atomic-layer deposition of Al<sub>2</sub>O<sub>3</sub>, (c) Pd gate lift-off, (d) S/D contact opening and (e) NH<sub>4</sub>OH treatment and S/D contact formation and lift-off.

**Figure 2.** (a) Schematic representation of a gate-enclosed junctionless MOSFET architecture, where  $r_{\rm d}$ ,  $r_{\rm s}$ ,  $r_{\rm g}^{\rm in}$ , and  $r_{\rm g}^{\rm out}$  are the drain, source, gate inner and gate outer radii, respectively. (b) Layout of circular transmission line,  $r=100~\mu{\rm m}$ , d varies from 16 to 96  $\mu{\rm m}$ .

Figure 3. (a) Circuit diagram of CTL measurements. (b) I-V characteristics between metal contacts ( $I_{\text{probe}}$ ) and between the central contact and the substrate ( $I_{\text{sub}}$ ). Inset shows in larger scale  $I_{\text{probe}}$  measured with grounded (black dots) and isolated (red dots) substrate.

**Figure 4.** *I-V* characteristics of circular contacts in CTL before treatment (a), after RF plasma treatment (0.5 W/cm<sup>2</sup>; 150°C; 10 min) from top side (b) and after RFPT from back side (c). (d) Plot of total resistance vs. ln(R/r) after RFPT.

**Figure 5**. Dependence of the sheet resistance of the InGaAs film (dots) and specific contact resistance (open squares) on plasma power density.

**Figure 6.** Transfer  $(I_d - V_g)$  characteristics measured at different values of  $V_d$  varied from 10 mV to 50 mV on the 40- $\mu$ m-gate-length n-InGaAs JL MOSFET before and after RF plasma treatment with plasma power density P=0.5 W/cm<sup>2</sup>.

**Figure 7.** The threshold voltage shift  $\Delta V_{th}$  (a), the inverse subthreshold slope SS (b), and the on-current  $I_{ON}$  and on-to-off current ratio  $I_{ON}/I_{OFF}$  (c) as a function of the RF plasma power density in In<sub>0.53</sub>Ga<sub>0.47</sub>As JL MOSFETs ( $L_g$ =40  $\mu$ m,  $V_d$ =50 mV). The data in Figure 6(c) are obtained at  $V_g$ - $V_{th}$ =0.5 V, where  $V_{th}$  values are evaluated by the second derivative drain current method.

**Figure 8.** (a) Y-function plotted versus gate voltage overdrive in the range of volume conduction obtained at  $V_d$ =50 mV on In<sub>0.53</sub>Ga<sub>0.47</sub>As JL MOSFETs ( $L_g$ =40  $\mu$ m) before and after RF plasma treatment with various plasma power densities and (b) the extracted carrier mobility  $\mu_{vol}$  as a function of RF plasma power density

**Figure 9.** (a)  $1/\sqrt{g_m}$  versus gate voltage overdrive obtained on  $In_{0.53}Ga_{0.47}As$  JL MOSFETs before and after RF plasma treatment with plasma power densities of 0.5 W/cm<sup>2</sup> and 1 W/cm<sup>2</sup> ( $L_g$ =40 µm,  $V_d$ =50 mV); (b) the extracted source/drain series resistance  $R_{SD}$  as a function of RF plasma power density.

**Figure 10.** (a) The  $C_{gc}$ - $V_g$  characteristic measured at f=10 kHz in the JL In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET after RF plasma treatment with P=0.5 W/cm<sup>2</sup> (left axis), and the average electron concentration in the In<sub>0.53</sub>Ga<sub>0.47</sub>As film obtained by integrating the  $C_{gc}$ - $V_g$  curve and dividing by the film thickness (right axis). (b) The effective electron mobility  $\mu_{eff}$  versus the average electron concentration in the In<sub>0.53</sub>Ga<sub>0.47</sub>As film.