| Title                          | Flip chip packaging of digital silicon photonics MEMS Switch for cloud computing and data centre                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                        | Hwang, How Yuan;Lee, Jun Su;Seok, Tae Joon;Forencich,<br>Alex;Grant, Hannah R.;Knutson, Dylan;Quack, Niels;Han,<br>Sangyoon;Muller, Richard S.;Papen, George C.;Wu, Ming<br>C.;O'Brien, Peter A.                                                                                                                                                                                                                                                                          |

| Publication date               | 2017-06                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Original Citation              | Hwang, H. Y., Lee, J. S., Seok, T. J., Forencich, A., Grant, H. R.,<br>Knutson, D., Quack, N., Han, S., Muller, R. S., Papen, G. C., Wu,<br>M. C., O'Brien, P. (2017) 'Flip chip packaging of digital silicon<br>photonics MEMS Switch for cloud computing and data centre',<br>IEEE Photonics Journal, 9(3), 2900210 (10pp). doi: 10.1109/<br>JPHOT.2017.2704097                                                                                                         |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Link to publisher's<br>version | 10.1109/JPHOT.2017.2704097                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Rights                         | © 2017, IEEE. Personal use of this material is permitted.<br>Permission from IEEE must be obtained for all other users,<br>including reprinting/ republishing this material for advertising or<br>promotional purposes, creating new collective works for resale<br>or redistribution to servers or lists, or reuse of any copyrighted<br>components of this work in other works https://www.ieee.org/<br>publications_standards/publications/rights/copyrightpolicy.html |

| Download date                  | 2024-12-27 01:46:49                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Item downloaded<br>from        | https://hdl.handle.net/10468/4040                                                                                                                                                                                                                                                                                                                                                                                                                                         |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

Open Access

# Flip Chip Packaging of Digital Silicon Photonics MEMS Switch for Cloud Computing and Data Centre

(Invited Paper)

### Volume 9, Number 3, June 2017

How Yuan Hwang Jun Su Lee Tae Joon Seok Alex Forencich Hannah R. Grant Dylan Knutson Niels Quack Sangyoon Han Richard S. Muller George C. Papen Ming C. Wu Peter O'Brien

DOI: 10.1109/JPHOT.2017.2704097 1943-0655 © 2017 IEEE

## Flip Chip Packaging of Digital Silicon Photonics MEMS Switch for Cloud Computing and Data Centre

(Invited Paper)

How Yuan Hwang,<sup>1</sup> Jun Su Lee,<sup>1</sup> Tae Joon Seok,<sup>2,3</sup> Alex Forencich,<sup>4</sup> Hannah R. Grant,<sup>4</sup> Dylan Knutson,<sup>4</sup> Niels Quack,<sup>2,5</sup> Sangyoon Han,<sup>2,6</sup> Richard S. Muller,<sup>2</sup> George C. Papen,<sup>4</sup> Ming C. Wu,<sup>2</sup> and Peter O'Brien<sup>1</sup>

<sup>1</sup>Tyndall National Institute, University College Cork, Cork T12 R5CP, Ireland

<sup>2</sup>Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720 USA

<sup>3</sup>School of Electrical Engineering and Computer Science, Gwangju Institute of Science and Technology, Gwangju, South Korea

<sup>4</sup>Department of Electrical and Computer Engineering, University of California, San Diego, CA 92093 USA

<sup>5</sup>École Polytechnique Fédérale de Lausanne, Lausanne CH-1015, Switzerland

<sup>6</sup>College of Natural Sciences, Korea Advanced Institute of Science and Technology, Daejeon 305-338, South Korea

DOI:10.1109/JPHOT.2017.2704097

1943-0655 © 2017 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received March 29, 2017; revised May 1, 2017; accepted May 9, 2017. Date of publication May 15, 2017; date of current version May 26, 2017. This work was supported in part by the Science Foundation Ireland under Grant 12/RC/2276, in part by the National Science Foundation Center for Integrated Access Network under grant #EEC-0812072, and in part by the Defense Advanced Research Project Agency POEM Program under HR0011-17-1-0001. Corresponding author: How Yuan Hwang (e-mail: howyuan.hwang@tyndall.ie).

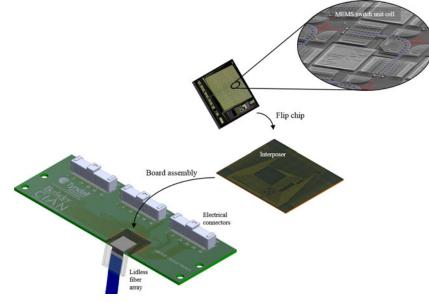

**Abstract:** We report on the flip chip packaging of Micro-Electro-Mechanical System (MEMS)-based digital silicon photonic switching device and the characterization results of 12 × 12 switching ports. The challenges in packaging N<sup>2</sup> electrical and 2N optical interconnections are addressed with single-layer electrical redistribution lines of 25  $\mu$ m line width and space on aluminum nitride interposer and 13° polished 64-channel lidless fiber array (FA) with a pitch of 127  $\mu$ m. 50  $\mu$ m diameter solder spheres are laser-jetted onto the electrical bond pads surrounded by suspended MEMS actuators on the device before fluxless flip-chip bonding. A lidless FA is finally coupled near-vertically onto the device gratings using a 6-degree-of-freedom (6-DOF) alignment system. Fiber-to-grating coupler loss of 4.25 dB/facet, 10<sup>-11</sup> bit error rate (BER) through the longest optical path, and 0.4  $\mu$ s switch reconfiguration time have been demonstrated using 10 Gb/s Ethernet data stream.

**Index Terms:** Flip chip, interposer, micro-electro-mechanical system (MEMS) packaging, optical switches, silicon photonics.

#### 1. Introduction

Demand for cloud computing and content-rich applications has led to massive growth in data traffic managed by data centre. With an expected three-fold data traffic growth from 135 zettabytes in 2014

to 500 zettabytes by 2019 [1], data centre operation is undergoing a paradigm shift in the network architecture. Up to recent years, CMOS electronics, which are data rate and protocol dependent, have been responsible for traditional data traffic routing. Commonly known as OEO switching, there are three components involved in the switching operation. Incoming optical signals are first converted into the electrical signal (OE conversion) before switching operation in the electrical domain and finally reconverted back into optical signals (EO conversion). Scaling up of data centre to adapt to the growth in data traffic becomes increasingly challenging as any expansion requires the addition or replacement of OE and EO converter modules. As a result, the management of system size, power consumption and hardware cost becomes challenging.

Fortunately, progress in silicon photonics since the first demonstration of silicon-on-insulator (SOI) waveguides in 1985 [2]-[4] has now made data switching in the optical domain (OOO switching) possible. Large scale integrated photonic switches can be realized on silicon at low cost and with high yield leveraging the advanced manufacturing processes adopted in complementary metaloxide-semiconductor (CMOS) industry. Higher degrees of freedom available in the optical domain allow a tremendous increase in bandwidth per fiber and the data processed in the switch fabric [5]–[8]. In fact, close to 75 % of the data traffic is transferred between servers in the data centre [1], making OOO switching systems more attractive. Over the years, there have been a variety of optical switching fabric proposed and demonstrated based on electro-optic [9], [10], thermo-optic [11]–[15] and three-dimensional (3-D) MEMS [16], [17] switching mechanisms. 3–D MEMS switch has merits for low optical loss, scalability and polarization insensitivity, but it is slow with millisecond response time. Previous integrated switches are based on cascaded multi-stage switching architecture, therefore the optical loss is guickly increased as the switch size scales up. While photonics device design and fabrication based on SOI have made tremendous progress, packaging of these devices continues to meet various technical challenges [18]-[21] and more so when MEMS structures are involved [22]-[25].

Recently, the team at UC Berkeley has developed 50  $\times$  50 and 64  $\times$  64 digital silicon photonic MEMS switches with sub-microsecond switching times, low on-chip losses and broad optical bandwidths [26]–[28]. In general, for an N  $\times$  N digital switching device, there are N<sup>2</sup> electrical interconnects (excluding grounds) and 2N optical interconnects. We have previously demonstrated that a N  $\times$  N silicon photonic MEMS switch matrix with N<sup>2</sup> individual switch unit cells can be electrically interfaced using a row-column addressing method, exploiting the inherent hysteresis of the electrostatic MEMS actuator [29]. This reduces the required electrical interface to 2N contacts, which is compatible with standard wire bonding. However, this approach relies on a tradeoff between ease of integration and achievable switching speed, as the individual switch unit cells can only be addressed sequentially. In order to fully harness the sub-microsecond switching time, individual addressing of N<sup>2</sup> electrical contacts is required. This poses major electrical routing challenges for packaging due to the density of these interconnects. Similarly, 2N optical interconnects will lead to a large fiber array for external coupling, considering the typical pitches of 127  $\mu$ m and 250  $\mu$ m. Depending on the manufacturing tolerances, there can be channel-to-channel pitch variations and these can accumulate and lead to high insertion losses. Large fiber array alignment onto optical interconnects also poses additional challenges, as a precise 6-degree-of-freedom (6-DOF) control is needed to minimize the insertion loss variations from one end of the array to another. Finally, suspended MEMS near electrical interconnects do not allow the use of material that can leave residues such as solder flux [30], [31] and polymer resin such as glob top or underfill near them due to interference.

In this article, we report in detail the electrical and optical packaging of the 50  $\times$  50 switch device and its associated challenges. We selected a sub-array of 12  $\times$  12 switches in this first packaging demonstration, using single layer electrical redistribution lines (RDL) ceramic interposers to fan-out the 146 electrical interconnects (including grounds) through flip-chip configuration. An angle polished lidless fiber array (FA), consisting of 64 SMF-28 and spaced at 127  $\mu$ m was used for optical coupling. The optical transmission characteristics such as bit error rate (BER) and

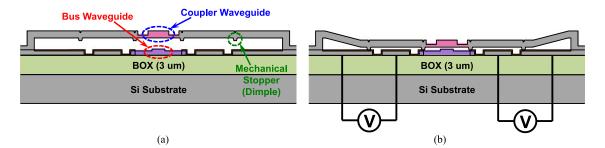

Fig. 1. Schematics of MEMS switch unit cell depicting coupler and bus waveguides, the mechanical stoppers and their operating principle during (a) OFF state and (b) ON state.

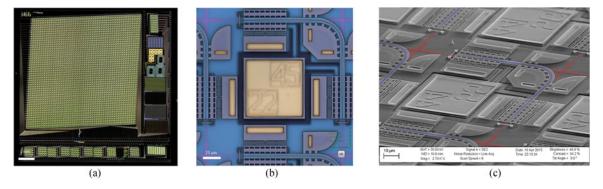

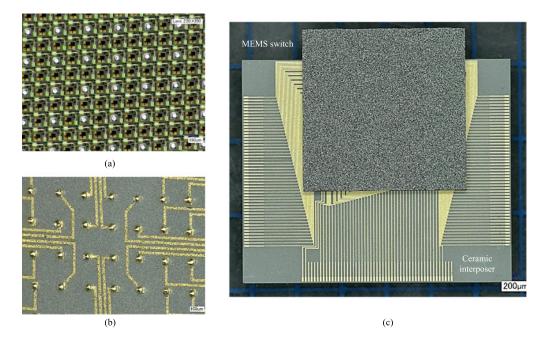

Fig. 2. (a) Overview of the  $50 \times 50$  switching device used in packaging demonstration and a switch unit cell under (b) optical and (c) scanning electron microscope (SEM).

reconfiguration time of the packaged switch were finally measured using 10 Gb/s Ethernet data streams.

#### 2. Overview of Digital Silicon Photonic MEMS Switch

The operating principle of the silicon photonic MEMS switch is illustrated in Fig. 1. The switching element consists of a pair of adiabatic couplers suspended above the bus waveguides. When the device is under OFF state, the adiabatic couplers are suspended at 1  $\mu$ m above the bus waveguides and do not interfere with the light propagation within the bus waveguides. When a voltage is supplied (ON state), the initially suspended adiabatic couplers are pulled down by the integrated MEMS actuators electrostatically, allowing light coupling from the bus waveguides to the first adiabatic couplers. After a 90° turn, light is coupled to orthogonal bus waveguides through the second adiabatic couplers. Mechanical stoppers patterned by photolithography define the coupling distance between adiabatic couplers and bus waveguides precisely. The optical insertion loss and crosstalk are independent of the bias voltage applied to the MEMS actuators. The intrinsic digital operation of MEMS actuators enables large scale digital switching operations and we have observed a good reliability that the switch can operate over ten billion cycles without failures [27].

Fig. 2 shows the 50  $\times$  50 switching device selected for the first optical and electrical packaging demonstration. 2500 silicon photonic switches are monolithically integrated on SOI, within an area of 7.6 mm  $\times$  7.6 mm. Each pair of suspended MEMS actuators (top and right of Fig. 2(b)) are controlled by the bond pad in the centre. This switching architecture is highly scalable as light passes through only one switching element regardless of the switch size. The grating couplers implemented on the switch device have a uniform pitch of 640 nm and a duty cycle of 50 % for optimum coupling of TE-polarized light. Although this device was designed for TE-polarized light, it has been reported that polarization insensitive switches can be demonstrated using the same silicon photonic MEMS switching architecture [32]. Device level characterisation has shown a

sub-microsecond switching time (approximately 3 orders of magnitude faster than commercial 3-D MEMS switches), broad spectral bandwidth (1400 – 1700 nm), high extinction ratio (>50 dB) and digital switching characteristic.

#### 3. Electrical Packaging

#### 3.1. Electrical Design

In order to realize the full potential of the switching device, there is a need to address the large number of electrical ports. For instance, an N  $\times$  N switching device will require N<sup>2</sup> electrical interconnects at the test board interfacing the device and end user. Density of electrical bond pads to be connected and their locations in the centre of the device do not allow straightforward wire bonding onto the test board as long wires can lead to sagging and shorting. Exposed and suspended MEMS structures located at the four corners of electrical bond pads also limit the application of glob top (typically used in electronic packaging) to keep the wires rigid and in place. On the other hand, there is a mismatch between the device and printed circuit board (PCB) design rules, making direct flip-chip bonding onto the board challenging. At the same time, difference in coefficient of thermal expansion (CTE) between silicon (2.9 ppm/K) and PCB (FR4, 14 ppm/K) could lead to reliability issues especially when underfills are not used.

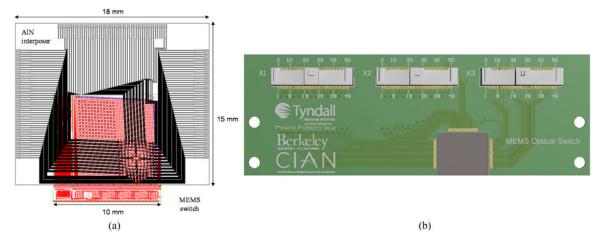

In this first packaging demonstration, we selected a sub-array of  $12 \times 12$  (out of  $50 \times 50$ ) switching cells for faster assembly, which results in 146 electrical interconnects (including ground pads). Instead of a direct flip-chip-bonding onto the PCB, a 250  $\mu$ m thick aluminum nitride (AIN, 4.5 ppm/K) interposer was used as an intermediate substrate between the device and board to minimize CTE mismatches. Unlike wire bonding, flip-chip requires a mirrored bond pad orientation on the substrate, thus the design convention (device face up or face down) should be decided at the beginning and consistently followed. This is particularly important for non-symmetrical pad-array configuration. Based on the device layout, only 3 edges of the interposer can be used to populate the electrical bond pads connecting to the PCB, as optical interconnections are needed at one of the edges. Single metal layer electrical redistribution lines (RDL) were designed using 25  $\mu$ m line width and space specification to fan-out the 146 electrical interconnects from the device. This design resulted from the decision to connect every alternate bond pad from the device, effectively doubling the pad pitch from 145  $\mu$ m to 290  $\mu$ m thus relaxing the routing density. Titanium/platinum/gold (Ti/Pt/Au) was selected as the preferred RDL metallization on the interposer to reduce transmission line resistance. The number of switching cells can be readily expanded / scaled up with the use of multi-layer RDL or finer line width and space RDL design rule available with advanced silicon and glass interposers. Simplistically speaking, assuming similar line widths of 25  $\mu$ m, two metallization layers will be required should the number of electrical interconnect be doubled from 146 to 292 (assuming that the pad pitch remains the same), and this will add to the manufacturing cost as well.

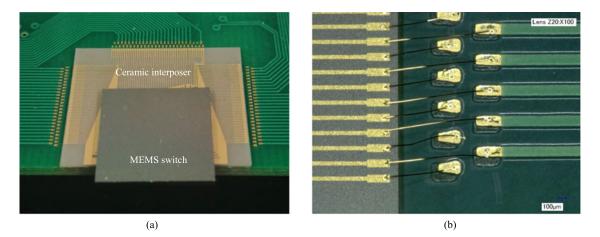

At the same time, a two-layer PCB was also designed to connect the 146 electrical lines from the device, with the bond pads arranged in staggered fashion to match the pad pitch of the interposer. This minimizes the wire bonding length and prevents overlapping and sagging of bond wires, thus preventing shorts. The bond pads were finished with electroless nickel immersion gold (ENIG) for wire joint reliability. Three pluggable electrical sockets, each capable of taking 50 discrete electrical wires, were placed at one side of the PCB and served as the interface for testing and characterisation. The final design of the ceramic interposer and PCB are shown in Fig. 3. The electrical designs were then matched and confirmed with optical designs before components manufacturing were committed.

#### 3.2. Electrical Assembly

Prior to flip chip assembly, 50  $\mu$ m diameter solder spheres made of tin-silver-copper (SAC 305, Duksan Hi-Metal Co. Ltd.) were laser jetted onto the device bond pads using PacTech SB<sup>2</sup>-SM (Fig. 4(a)). The jetting process was automated by generating a rhombus shape bond map, defining

Fig. 3. Design of (a) ceramic interposer to fan-out  $12 \times 12$  electrical interconnects located at the bottom right quadrant of the device and (b) printed circuit board (PCB) assembly with staggered wire bond pads.

Fig. 4. (a) Solder (SAC 305) bumps on switch device and (b) gold (Au) stud bumps on ceramic interposer and (c) flip chip assembly of the device on interposer.

the coordinates where a solder bump was required on the device. Gold stud bumps were also made on an AlN interposer using 0.8 mil wires and coined (flattened) for co-planarity and flip-chip height control (Fig. 4(b)). The device was then flipped and aligned onto AlN interposer using a Finetech flip chip bonder and reflowed at a peak temperature of 260 °C within a N<sub>2</sub> enclosure. Fluxless reflow was used to prevent residue on MEMS actuators and optical gratings. Similarly no capillary underfill was used to improve solder joint strength in order to prevent gap filling within MEMS actuators and obstruct their motions. The reflowed assembly is shown in Fig. 4(c).

Assembled component (device and interposer) was then attached onto PCB using thermal epoxy, making sure that the pads on the interposer were aligned properly with those on the PCB (Fig. 5(a)). Electrical connections to test sockets were finally formed between the interposer and PCB through gold wires and protected with glob top (Fig. 5(b)). The board was finally attached onto a carrier

Fig. 5. (a) Flip-chip assembly bonded onto PCB and (b) gold wires connecting AIN interposer to PCB.

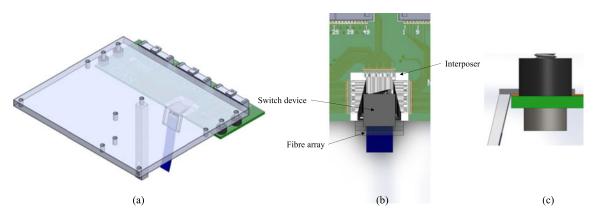

Fig. 6. 3-D Solidworks models showing (a) the expected package assembly with its mechanical housing and fiber support post, (b) top view of the model showing FA alignment onto device, interposer and PCB and (c) side view of the model showing that only a lidless fiber will be able to couple to the device gratings due to proximity to interposer edge.

made for optical packaging. Optical coupling is typically processed as the final packaging step due to sensitivity in index-matching resin to temperature. Glass-transition-temperatures ( $T_g$ ) of these materials are generally lower than those used for electronic encapsulation and molding. Process temperatures above  $T_g$  soften the resin, leading to optical alignment issues [33].

#### 4. Optical Packaging

#### 4.1. Optical Design

Similar to electrical packaging, there is also a need to address the large number of 2N optical interconnects needed for an N  $\times$  N switching device. In this packaging demonstration, there are 36 optical ports serving as input, through and drop ports which can only be accessed using a 64-channel FA, owing to the device configuration. The PCB, FA and mechanical housing were put together using SolidWorks in 3-dimensions (3-D) during the design stage to confirm the optical assembly (Fig. 6). The model made clear that the close proximity between the grating couplers and the interposer edge would not allow a typical FA to reach the couplers. Although a planar coupling approach would have solved this issue, a high polished angle (51.5°) FA cannot be fabricated due to the large array size. High angle polishing, in which individual fiber are resin-fixed on the V-groove,

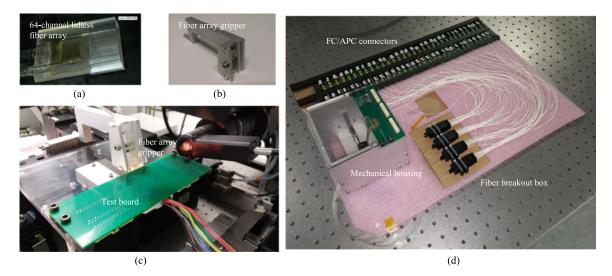

Fig. 7. (a) Lidless FA and (b) the FA gripper used during (c) active alignment. (d) The fully assembled optical switch package completed with mechanical housing.

proved to be challenging as some fiber peel off was observed. Thus, a 13° polished lidless FA was used instead.

#### 4.2. Optical Assembly

After electrical assembly, the lidless 64-channel FA (Fig. 7(a)) was coupled near-vertically to the device gratings through active alignment using a 6-DOF alignment system from Newport Corp (Fig. 7(c)). A gripper capable of handling a large FA was used (Fig. 7(b)). Due to the large width of FA, the alignment process becomes more challenging even with the assistance of shunts on the device. The FA had to be slowly adjusted to make sure that it was parallel to the gratings plane, because a larger gap between FA and grating couplers will lead to higher insertion loss. Passive optical coupling solutions such as optical proximity coupling [34], [35] or evanescent coupling [36] therefore become attractive especially when large numbers of coupling channel are required. Indexmatching resin (NOA 61, Norland) was then applied to fill the air gap between the FA and grating couplers before finishing with OP-4-20632 (Dymax) at the edges for mechanical strength. Extra care and precise dispensing of optical resin were needed to prevent the resin from flowing into the flip-chip gap. Finally, a fiber post was attached onto the carrier, fixed with room-temperaturecuring resin and transferred to a mechanical housing to maintain the integrity of the FA. The fully assembled silicon photonic switch package is shown in Fig. 7(d). The packaging assembly had been designed for ease of characterisation using long fiber terminated with FC/APC connectors. For commercial application, MTP or MPO connectors can be used as optical fiber termination to keep the package lean.

#### 5. Results And Analysis

#### 5.1. Electrical and Optical Assembly

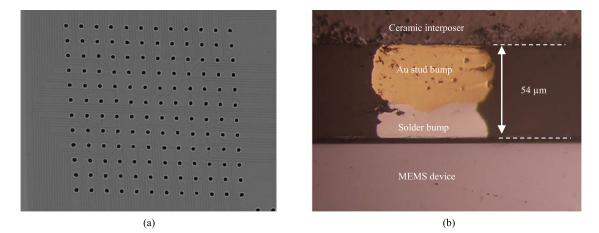

In order to confirm the flip-chip alignment after reflow, samples were analyzed through nondestructive and destructive methods. Nondestructive methods such X-ray imaging allows a quick confirmation of the alignment after reflow process. On the other hand, destructive methods such as mechanical polishing can provide more information, including solder joint quality, assembly height and bump height variations across the flip chip assembly. Further analysis after mechanical polishing can also be done using scanning electron microscopy (SEM) and energy dispersive x-ray microscopy (EDX) to study the solder joint microstructures and reveal fine cracks and delamination

Fig. 9. (a) Measured transmission as a function of bias voltage of a switch cell, (b) switching voltage distribution of 70 MEMS switch cells and (c) fiber-to-fiber transmissions of various switch path.

not immediately clear through optical microscopy. Fig. 8(a) shows an x-ray image of the flip-chip assembly, in which solder bumps on the device were properly aligned with the stud bumps on the interposer. Mechanical polishing of the assembly confirmed the bump alignment, the solder-stud joint quality and the assembly height (Fig. 8(b)).

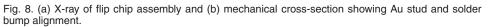

Subsequently, the fully assembled package was tested and analyzed. The MEMS actuations were driven using a Keithley 2400 power supply by varying the voltage only. Input light source was supplied by a 1550 nm peak superluminescent diode (SLD) and the fiber-to-fiber transmissions were measured using an Anritsu MS9710C spectrum analyser. Fig. 9(a) showed the transmission characteristics of a switch cell as a function of bias voltage. The OFF- and ON- state switching voltages were measured to be 34.6 V and 24.8 V with standard deviations of 1.1 V and 1.6 V respectively (Fig. 9(b)). The 10 V difference between OFF- and ON- state voltages is due to intrinsic bias hysteresis of the gap-closing actuators. Meanwhile fiber-to-coupler loss was measured to be 4.25 dB / facet and fiber-to-fiber transmissions between 12.9 dB to 14.5 dB near 1550 nm were recorded (Fig. 9(c)). The variation in fiber-to-fiber transmission was due to the optical path length difference of the  $12 \times 12$  ports being analyzed.

#### 5.2. System Characterisation

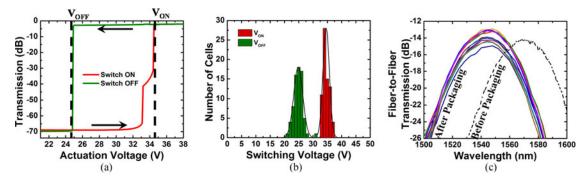

Finally, system level characterisation was performed on the package to analyse the switching performance. For bit error rate (BER) experiment, a 10 Gb/s Ethernet data stream was generated by a Virtex-6 FPGA and drove an enhanced small form-factor pluggable (SFP+) transceiver module. The optical data stream from the SFP+ module was inserted to the switch package. The output

Fig. 10. (a) Block diagram of system level characterization and (b) switching performance with 10 Gb/s data stream.

signal from the package was sent to the SFP+ module on the FPGA to measure BER. For the longest optical path switching configuration (worst case), BER was measured to be  $10^{-11}$ . For switch reconfiguration experiment, we used the system experiment setup shown in Fig. 10(a). The optical data stream was split and sent to two input ports of the switch package. In the stream paths, EDFA and attenuators were used to compensate the split loss and recover the output power of the SPF+ module for each stream. Two switch cells were controlled to select one of two input streams and send it to an output port. The output stream from the package was split and monitored by a linear detector [yellow trace in Fig 10(b)] and a SPF+ module on the FPGA board [green trace in Fig. 10(b)]. Physical switch reconfiguration time of the package was recorded to be 0.4  $\mu$ s.

#### 6. Conclusion

The first MEMS-based silicon photonic switch package has been demonstrated using a flip-chip configuration. The packaging challenges (N<sup>2</sup> electrical and 2N optical interconnects) are addressed with the use of 25  $\mu$ m line width / space RDL on ceramic interposer and lidless fiber array (FA) consisting of 64 SMF-28 fibers spaced at 127  $\mu$ m. A fluxless reflow with laser jetted solder bumps has demonstrated good alignment between the device and interposer. A fiber-to-grating coupler loss of 4.25 dB / facet and an average switching ON voltage of 34.6 V with a standard deviation of 1.1 V had been recorded. The worst case bit-error-rate (BER) of the package was 10<sup>-11</sup> while the switch reconfiguration time was 0.4  $\mu$ s using a 10 Gb/s Ethernet data stream.

Future work includes expanding the number of packaged port counts using multi-layer RDL glass interposer and pitch reducing fiber-to-device planar coupling array. Passive optical coupling solution based on evanescent transmission is also in the work and will be demonstrated in the future. This approach will allow high density and large scale optical / electrical interconnects to be incorporated on silicon photonics devices. It will also allow heterogenous integration of electronic and photonic components into a system-in-package (SiP) for the age of "Internet of Everything".

#### Acknowledgment

H. Y. Hwang would like to thank Dr. L. Carroll in manuscript preparation and N. Nudds in preparing the Au stud bumps on AIN interposer.

#### References

- [1] Cisco, "Global cloud index: Forecast and methodology, 2014–2019," White Paper, 2015. [Online]. Available: www.cisco.com

- [2] R. A. Soref and J. P. Lorenzo, "Single-crystal silicon: A new material for 1.3 and 1.6 μm integrated-optical components, "*Electron. Lett.*, vol. 21, no. 21, pp. 953–954, 1985.

- [3] G. T. Reed, W. R. Headley, and C. E. J. Png, "Silicon photonics: The early years," Proc. SPIE, Optoelectronic Integration on Silicon II, vol. 5730, pp. 1–18, Mar. 14, 2005.

- [4] D. Thomson et al., "Roadmap on silicon photonics," J. Opt., vol. 18, no. 7, 2016, Art. no. 073003.

- [5] G. I. Papadimitriou, C. Papazoglou, and A. S. Pomportsis, "Optical switching: Switch fabrics, techniques, and architecture," J. Lighw. Technol., vol. 21, no. 2, pp. 384–405, Feb. 2003.

- [6] M. Yano, F. Yamagishi, and T. Tsuda, "Optical MEMS for photonic switching-compact and stable optical crossconnect switches for simple, fast, and flexible wavelength applications in recent photonic networks," *IEEE J. Sel. Topics Quantum Electron.*, vol. 11, no. 2, pp. 383–394, Mar./Apr. 2005.

- [7] K. Vlachos, L. Raptis, A. Teixeira, G. M. T. Beleffi, and K. Yiannopoulos, "Optical switch fabrics (OSFs) and their application," in *Enabling Optical Internet With Advanced Network Technologies*, J. Aracil and F. Callegati, Eds. London, U.K.: Springer-Verlag, 2009, Ch. 6, pp. 150–190.

- [8] R. Stabile, A. Albores-Meija, A. Rohit, and K. A. Williams, "Integrated optical switch matrices for packet data networks," *Microsyst. Nanoeng.*, vol. 2, 2016, Art. no. 15042.

- [9] J. Van Campenhout, W. M. Green, S. Assefa, and Y. A. Vlasov, "Low-power, 2 × 2 silicon electrooptic switch with 110-nm bandwidth for broadband reconfigurable optical networks," *Opt. Exp.*, vol. 17, no. 26, pp. 24020–24029, Dec. 2009.

- [10] M. Yang *et al.*, "Non-blocking 4 × 4 electro-optic silicon switch for on-chip photonic networks," *Opt. Exp.*, vol. 19, no. 1, pp. 47–54, Jan. 2011.

- [11] Y. Shoji, K. Kintaka, S. Suda, H. Kawashima, T. Hasama, and H. Ishikawa, "Low-crosstalk 2 × 2 thermo-optic switch with silicon wire waveguides," Opt. Exp., vol. 18, no. 9, pp. 9071–9075, Apr. 2010.

- [12] L. Chen and Y. Chen, "Compact, low-loss and low-power 8×8 broadband silicon optical switch," Opt. Exp., vol. 20, no. 17, pp. 18977–18985, Aug. 2012.

- [13] G. W. Cong et al., "Large current MOSFET on photonic silicon-on-insulator wafers and its monolithic integration with a thermo-optic 2 × 2 Mach–Zehnder switch," Opt. Exp., vol. 21, no. 6, pp. 6889–6894, Mar. 2013.

- [14] K. Suzuki et al., "Ultra-compact 8 × 8 strictly non- blocking Si-wire PILOSS switch," Opt. Exp., vol. 22, no. 4, pp. 3887– 3894, Feb. 2014.

- [15] S. Nakamura, S. Yanagimachi, H. Takeshita, A. Tajima, T. Hino, and K. Fukuchi, "Optical switches based on silicon photonics for ROADM application," *IEEE J. Sel. Topics Quantum Electron.*, vol. 22, no. 6, pp. 185–193, Nov./Dec. 2016.

- [16] V. Kaman, R. J. Helkey, and J. E. Bowers, "Compact and scalable three-dimensional microelectromechanical system optical switches," *J. Opt. Netw.*, vol. 6, no. 1, pp. 19–24, 2007.

[17] Y. Kawajiri *et al.*, "512 × 512 Port 3D MEMS optical switch module with toroidal concave mirror," *NTT Tech. Rev.*,

- [17] Y. Kawajiri et al., "512 × 512 Port 3D MEMS optical switch module with toroidal concave mirror," NTT Tech. Rev., vol. 10, no. 11, pp. 1–7, Nov. 2012.

- [18] J. S. Lee et al., "Meeting the electrical, optical and thermal design challenges of photonic-packaging," IEEE J. Sel. Topics Quantum Electron., vol. 22, no. 6, pp. 409–417, Nov./Dec. 2016.

- [19] L. Carroll *et al.*, "Photonic packaging: Transforming silicon photonic integrated circuits into photonic devices," *Appl. Sci.*, vol. 6, no. 12, p. 426, Dec. 2016.

- [20] H. Lu et al., "Flip-chip integration of tilted VCSELs onto a silicon photonic integrated circuit," Opt. Exp., vol. 24, pp. 16258–16266, 2016.

- [21] K. Gradkowski et al., "Thermal challenges for packaging integrated photonic devices," in Proc. 2016 6th Electron. Syst. Integr. Technol. Conf., Grenoble, France, 2016, pp. 1–5.

- [22] R. Ramesham and R. Ghaffarian, "Challenges in interconnection and packaging of microelectromechanical systems (MEMS)," in Proc. Electron. Compon. Technol. Conf., 2000, pp. 666–675.

- [23] Y. C. Lee, B. A. Parviz, J. A. Chiou, and S. Chen, "Packaging for microelectromechanical and nanoelectromechanical systems," *IEEE Trans. Adv. Packag.*, vol. 26, no. 3, pp. 217–226, Aug. 2003.

- [24] R. Darveaux and L. Munukutla, "Critical challenges in packaging MEMS devices," in Proc. IEEE/SEMI Adv. Semicond. Manuf. Conf., 2005, pp. 210–216.

- [25] Z. Wang, "3-D integration and through-silicon vias in MEMS and microsensors," J. Microelectromech. Syst., vol. 24, no. 5, pp. 1211–1244, 2015.

- [26] S. Han, T. J. Seok, N. Quack, B. -W. Yoo, and M. C. Wu, "Large-scale silicon photonic switches with movable direction couplers," *Optica*, vol. 2, no. 4, pp. 370–375, 2015.

- [27] T. J. Seok, N. Quack, S. Han, R. S. Muller, and M. C. Wu, "Large-scale broadband digital silicon photonic switches with vertical adiabatic couplers," *Optica*, vol. 3, no. 1, pp. 64–70, 2016.

- [28] T. J. Seok, N. Quack, S. Han, R. S. Muller, and M. C. Wu, "Highly Scalable digital silicon photonic MEMS Switches," J. Lightw. Technol., vol. 34, no. 2, pp. 365–371, Jan. 2016.

- [29] N. Quack, T. J. Seok, S. Han, R. S. Muller, and M. C. Wu, "Scalable row/column addressing of silicon photonic MEMS Switches," IEEE Photon. Technol. Lett., vol. 28, no. 5, pp. 561–564, Mar. 2016.

- [30] S. Lim, J. Chou, M. Durham, and A. Mackie, "Flux challenges in flip-chip die-attach," in Proc. IEEE 17th Electron. Packag. Technol. Conf., 2016, pp. 1–5.

- [31] M. Durham, H. Jo, S. Lim, J. Chou, and A. C. Mackie, "Ultra-low residue semiconductor-grade fluxes for cu-pillar flip chip assembly," *Chip Scale Rev.*, vol. 19, no. 4, pp. 21–25, 2015.

- [32] S. Han, T. J. Seok, K. Yu, N. Quack, R. S. Muller, and M. C. Wu, "50 × 50 polarization-insensitive silicon photonic MEMS switches: Design and experiment," in *Proc. 42nd Eur. Conf. Opt. Commun.*, 2016, pp. 1–3.

- [33] A. Bachmann, J. Arnold, and N. Langer, "Movement between bonded optics," *Dymax Corp. Tech. Rep.*, Sep. 2001. [Online]. Available: www.dymax.com

- [34] J. Yao et al., "Grating-coupler-based optical proximity coupling for scalable computing systems," Proc. SPIE, Optoelectron. Interconnects Compon. Integr. XI, vol. 7944, Jan. 17, 2011, Art. no. 794405.

- [35] S. Bernabé, C. Kopp, M. Volpert, J. Harduin, J-M. Fédéli, and H. Ribot, "Chip-to-chip optical interconnections between stacked self-aligned SOI photonic chips," *Opt. Exp.*, vol. 20, pp. 7886–7894, 2012.

- [36] T. Barwicz et al., "A novel approach to photonic packaging leveraging existing high-throughput microelectronic facilities," IEEE J. Sel. Topics Quantum Electron., vol. 22, no. 6, Nov./Dec. 2016, Art. no. 8200712.