| Title                | Investigation of electrically active defects at the interface of high-k dielectrics and compound semiconductors                                                          |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors              | O'Connor, Éamon                                                                                                                                                          |

| Publication date     | 2014                                                                                                                                                                     |

| Original Citation    | O'Connor, E. 2014. Investigation of electrically active defects at the interface of high-k dielectrics and compound semiconductors. PhD Thesis, University College Cork. |

| Type of publication  | Doctoral thesis                                                                                                                                                          |

| Rights               | © 2014, Éamon O'Connor http://creativecommons.org/licenses/<br>by-nc-nd/3.0/                                                                                             |

| Download date        | 2024-04-25 13:25:22                                                                                                                                                      |

| Item downloaded from | https://hdl.handle.net/10468/3019                                                                                                                                        |

# Ollscoil na hÉireann, Corcaigh NATIONAL UNIVERSITY OF IRELAND, CORK

# Investigation of electrically active defects at the interface of high-k dielectrics and compound semiconductors

A thesis presented to

The National University of Ireland

for the degree of Doctor of Philosophy

by

# Éamon O'Connor, B.E, MEngSc

Tyndall National Institute University College Cork

October 2014

Supervised by Dr. Paul Hurley Co-Supervisor: Dr. Karim Cherkaoui

| CONT    | ENTS                                                                                                                 | II  |

|---------|----------------------------------------------------------------------------------------------------------------------|-----|

| Declar  | ation                                                                                                                | vi  |

| List of | Acroynms                                                                                                             | vii |

| List of | Symbols                                                                                                              | ix  |

| Abstra  | ct                                                                                                                   | xii |

| Ackno   | wledgements                                                                                                          | xvi |

| СНАР    | TER 1                                                                                                                | 1   |

| 1. Ba   | ckground and Motivation                                                                                              | 1   |

| 1.1.    | Introduction                                                                                                         | 1   |

| 1.2.    | Moore's Law                                                                                                          | 1   |

| 1.3.    | Incorporation of high-k dielectrics                                                                                  | 3   |

| 1.4.    | High mobility semiconductors                                                                                         | 8   |

| 1.5.    | Challenges for incorporation of high-k on III-V                                                                      | 9   |

| 1.6.    | Co-integration of Ge and III-V materials on a Si based platform                                                      | 12  |

| 1.7.    | Use of novel device architectures                                                                                    | 14  |

| 1.8.    | Thesis Outline                                                                                                       | 15  |

| CHAP    | TER 2                                                                                                                | 23  |

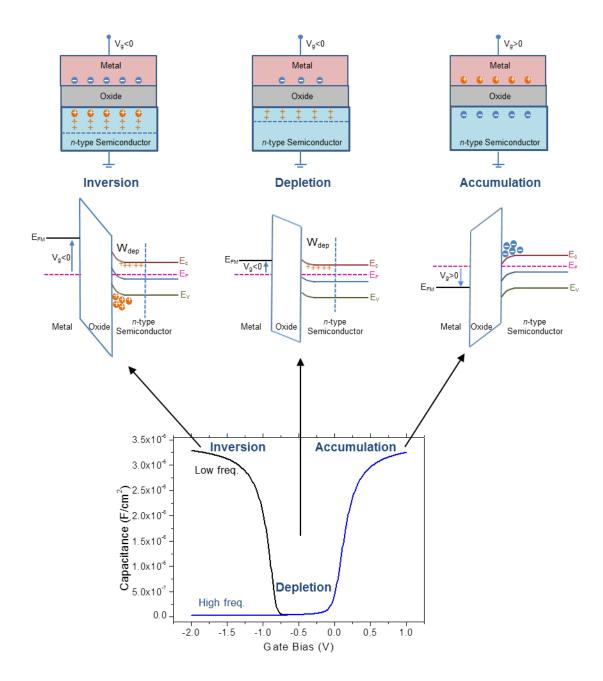

|         | arged defect components in the MOS system: Influence on th tance-voltage and conductance-voltage response, and metho |     |

| _       | density quantification                                                                                               |     |

| 2.1.    | Introduction                                                                                                         |     |

| 2.2.    | Capacitance-Voltage Response of MOS capacitors                                                                       |     |

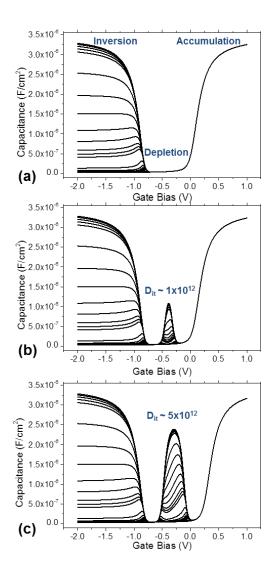

| 2.3.    | Simulated CV response: Effect of interface defect states, oxide char                                                 |     |

| bord    | er traps                                                                                                             |     |

| 2.4.    | The effect of very high D <sub>it</sub> level on the MOS CV response                                                 |     |

| 2.5.    | Evaluation of D <sub>it</sub> : Conductance Method and High-Low CV Method                                            |     |

| 2.6.    | Conclusions                                                                                                          |     |

| CHAP   | TER 3                                                                                                                | 39                                |

|--------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 3. Te  | emperature and frequency dependent electrical characterizat                                                          | ion of                            |

|        | In <sub>x</sub> Ga <sub>1-x</sub> As interfaces                                                                      |                                   |

| 3.1.   | Introduction                                                                                                         |                                   |

| 3.2.   | Experimental Details                                                                                                 | 40                                |

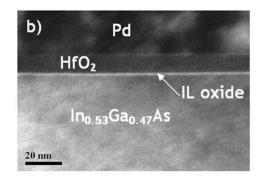

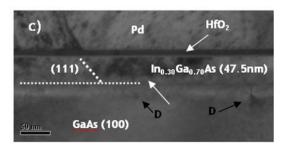

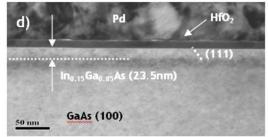

| 3.3.   | Structural Analysis                                                                                                  |                                   |

| 3.4.   | Room Temperature Electrical Analysis                                                                                 | 43                                |

| 3.5.   | - · · · · · · · · · · · · · · · · · · ·                                                                              |                                   |

| 3.5    | 5.1. Variable Temperature CV: -50°C to 75°C                                                                          | 45                                |

| 3.5    | 5.2. Variable Temperature CV: 77 K to 295 K                                                                          | 47                                |

| 3.6.   | D <sub>it</sub> Analysis of Pd/HfO <sub>2</sub> /In <sub>0.53</sub> Ga <sub>0.47</sub> As/InP devices                |                                   |

| 3.7.   | Conclusions                                                                                                          | 54                                |

| СНАР   | TER 4                                                                                                                | 57                                |

| 4. A:  | systematic study of $In_{0.53}Ga_{0.47}As$ surface passivation using (N                                              | H <sub>4</sub> ) <sub>2</sub> S57 |

| 4.1.   | Introduction                                                                                                         | 57                                |

| 4.2.   | Experimental Details                                                                                                 | 58                                |

| 4.3.   | Structural Analysis                                                                                                  | 60                                |

| 4.4.   | Electrical Analysis: CV and GV characteristics                                                                       | 62                                |

| 4.5.   | XPS analysis                                                                                                         | 69                                |

| 4.6.   | Dit extraction using High-Low CV and Conductance Techniques                                                          | 71                                |

| 4.7.   | Conclusions                                                                                                          | 78                                |

| СНАР   | TER 5                                                                                                                | 83                                |

| 5. Tł  | ne Al <sub>2</sub> O <sub>3</sub> /In <sub>0.53</sub> Ga <sub>0.47</sub> As system: Interface state reduction, surfa | ice                               |

| invers | tion, and analysis of the minority carrier response                                                                  | 83                                |

| 5.1.   | Introduction                                                                                                         | 83                                |

| 5.2.   | Experimental Details                                                                                                 | 84                                |

| 5.2    | 2.1. Samples for analysis of Minority Carrier Response                                                               | 84                                |

| 5.2    | 2.2. Samples for variable doping experiment                                                                          | 86                                |

| 5.3.   | Simulated CV and GV responses                                                                                        | 86                                |

| 5.4.   | Measured CV and GV response                                                                                          | 88                                |

| 5.5.   | Sources of Minority Carrier Response                                                                                 | 93                                |

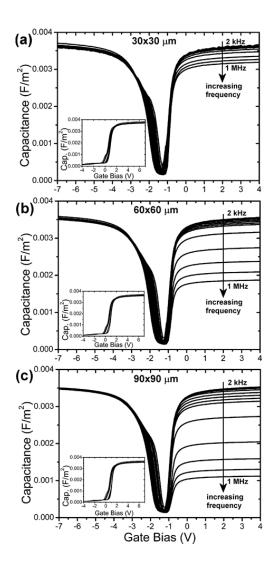

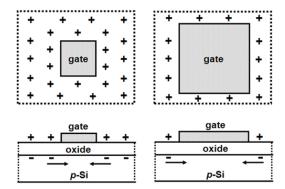

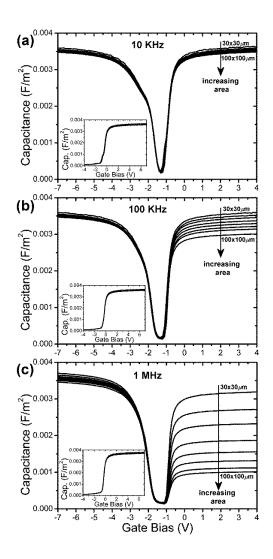

| 5.5    | 5.1. Peripheral Inversion                                                                                            | 93                                |

| 5.6.   | Temperature Response                                                                                                 | 96                                |

| 5.7.   | Arrhenius Extraction of Activation Energies                                                                          | 98                                |

| 5.8.   | Variable Doping Experiment: Motivation                                                                               | 101                               |

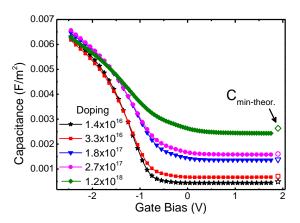

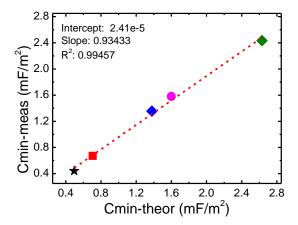

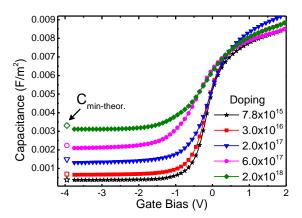

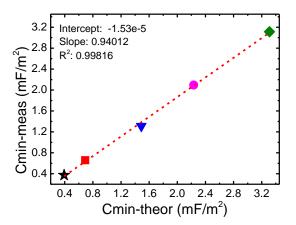

| 5.9.        | C <sub>min</sub> as a function of In <sub>0.53</sub> Ga <sub>0.47</sub> As doping concentration      | 103   |

|-------------|------------------------------------------------------------------------------------------------------|-------|

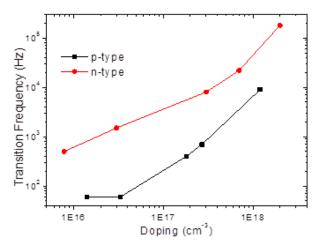

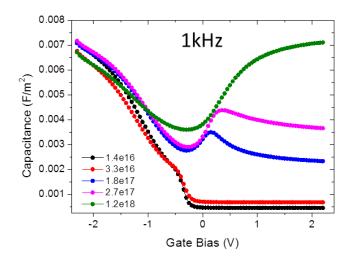

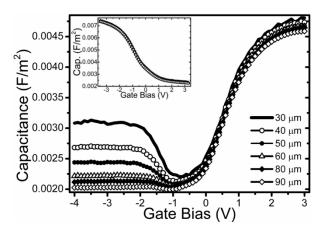

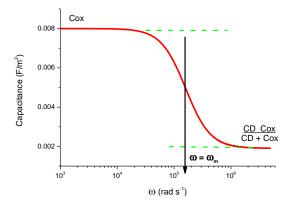

| 5.10.       | Variation in ω <sub>m</sub> with In <sub>0.53</sub> Ga <sub>0.47</sub> As doping concentration       | 106   |

| 5.11.       |                                                                                                      |       |

|             |                                                                                                      |       |

| CHAP        | TER 6                                                                                                | .112  |

|             |                                                                                                      |       |

| 6. Ex       | perimental method for extraction of C <sub>ox</sub> for In <sub>0.53</sub> Ga <sub>0.47</sub> As MOS |       |

| capaci      | tors, and the effect of FGA on minority carrier response                                             |       |

| 6.1.        | Introduction                                                                                         |       |

| 6.2.        | Experimental Details                                                                                 | 113   |

| 6.2         | .1. Samples for determination of C <sub>ox</sub>                                                     | 113   |

| 6.2         | 2.2. Samples with variable Al <sub>2</sub> O <sub>3</sub> thickness                                  | 114   |

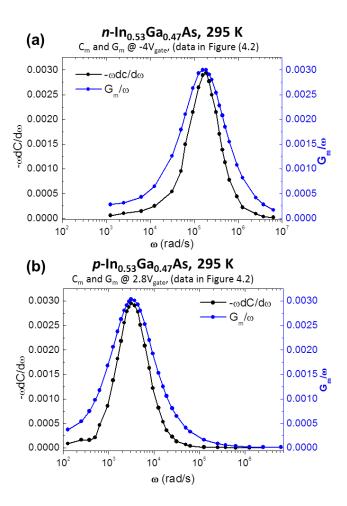

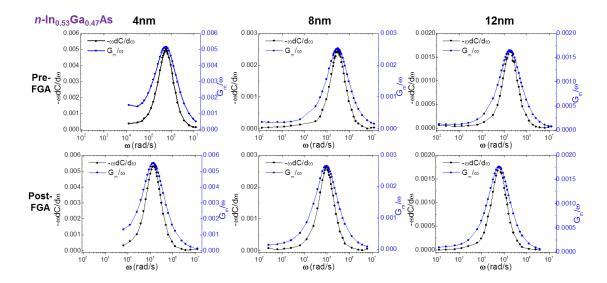

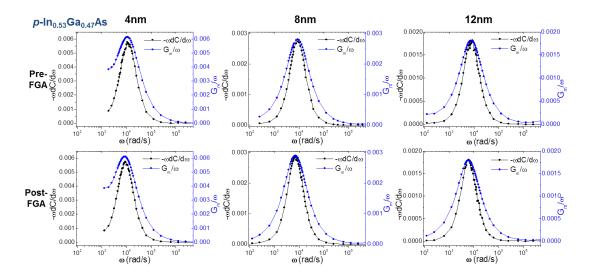

| 6.3.        | Experimental Observation: $G/\omega$ and $-\omega dC/d\omega$ relationship in inversion              | 114   |

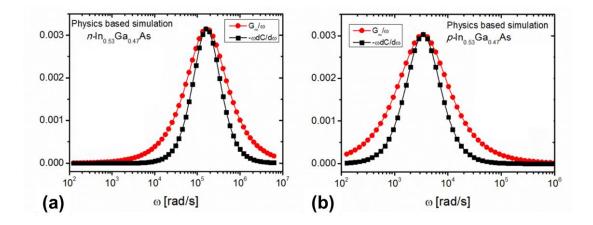

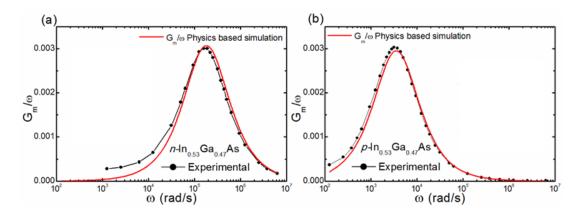

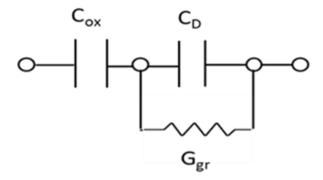

| 6.4.        | Simulations: $G/\omega$ and $-\omega dC/d\omega$ relationship in inversion                           | 116   |

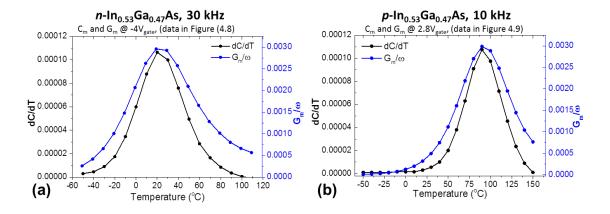

| 6.5.        | Experimental Observation: $G/\omega$ and $dC/dT$ relationship in inversion                           | 118   |

| 6.6.        | Mathematical Derivation of $G/\omega$ and $-\omega dC/d\omega$                                       |       |

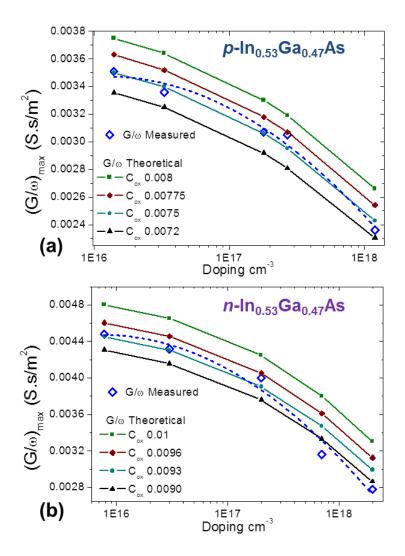

| 6.7.        | $G/\omega$ and $C_{ox}$ relationship as a function of semiconductor doping                           |       |

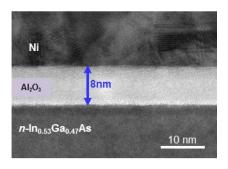

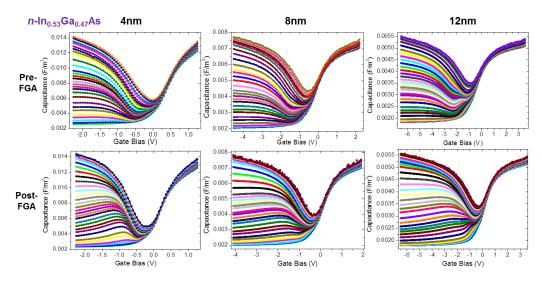

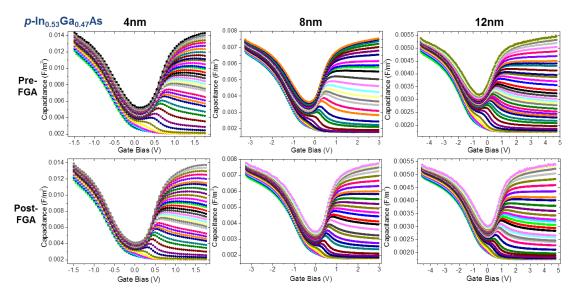

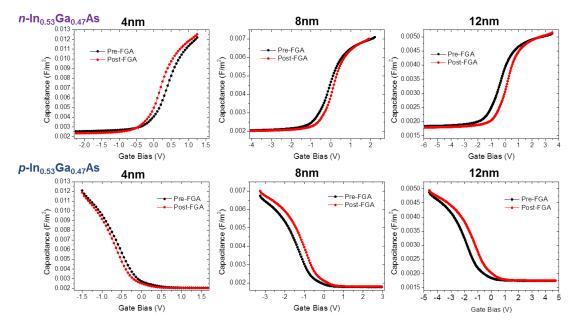

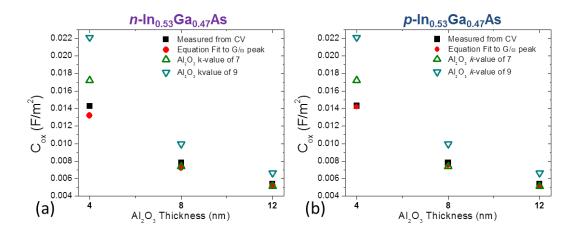

| 6.8.        | Inversion Response with varying Al <sub>2</sub> O <sub>3</sub> thickness                             |       |

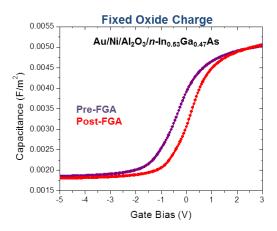

| 6.9.        | Fixed Oxide Charge: Effect of FGA and varying Al <sub>2</sub> O <sub>3</sub> thickness               |       |

| 6.10.       | $G/\omega$ and $-\omega dC/d\omega$ relationship with varying $t_{ox}$                               |       |

| 6.11.       | Influence of t <sub>ox</sub> and FGA on minority carrier generation lifetime                         |       |

| 6.12.       | •                                                                                                    |       |

| 0.12.       | Conclusions                                                                                          | 133   |

| CUAD        | TER 7                                                                                                | 126   |

| СПАР        | 1ER /                                                                                                | 130   |

| 7. Su       | mmary and Suggestions for Future Work                                                                | . 136 |

| 7.1.        | Summary of work presented in thesis                                                                  |       |

|             | Suggestions for future work                                                                          |       |

|             |                                                                                                      |       |

| <b>VDDE</b> | NDIX 1                                                                                               | 143   |

|             |                                                                                                      | 1173  |

| 8. Pu       | blications, Conference Presentations, Awards                                                         | . 143 |

| 8.1.        | Publications directly linked to work presented in Thesis                                             |       |

| 8.2.        | •                                                                                                    |       |

| 8.2         |                                                                                                      |       |

| 8.2         |                                                                                                      |       |

| 8.3.        |                                                                                                      |       |

|             | Full List of Publications                                                                            |       |

| <ul> <li>10.1. CV and G/ω plots for variable doping experiment sam</li> <li>10.2. G/ω plots for variable Al<sub>2</sub>O<sub>3</sub> thickness samples</li> </ul> | 9. App         | endix 2: Peripheral Inversion in MOS devices              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------|

|                                                                                                                                                                   | APPEN          | DIX 3                                                     |

| 10.2. $G/\omega$ plots for variable $Al_2O_3$ thickness samples                                                                                                   | 10. A <u>r</u> | ppendix 3 - Supplementary Results                         |

|                                                                                                                                                                   | 10.1.          | CV and G/ω plots for variable doping experiment same      |

| PPENDIX 4                                                                                                                                                         | 10.2.          | $G/\omega$ plots for variable $Al_2O_3$ thickness samples |

|                                                                                                                                                                   | PPEN           | DIX 4                                                     |

|                                                                                                                                                                   |                | ppendix 4 - Supplementary Information                     |

| -  | 1   |    |    |    |    |

|----|-----|----|----|----|----|

| I) | ecl | เล | ra | tı | on |

The work in this thesis has been carried out by me at the Tyndall National Institute, University College Cork, Ireland. Any work carried out by my colleagues or collaborators is clearly indicated. This work not been submitted for another degree, either at University College Cork or elsewhere.

\_\_\_\_\_

Éamon O'Connor Date

# **List of Acroynms**

3-D 3-dimensional

a.c alternating current

AFM Atomic Force Microscopy

ALD Atomic Layer Deposition

a-Si amorphous Silicon

CV Capacitance-Voltage

CMOS Complementary Metal-Oxide-Semiconductor

CVD Chemical Vapor Deposition

DC Direct Current

e-beam electron-beam

EOT Equivalent Oxide Thickness

FET Field Effect Transistor

FGA Forming Gas (H<sub>2</sub>/N<sub>2</sub>) Anneal

GV Conductance-Voltage

IV Current-Voltage

ITRS International Technology Roadmap for Semiconductors

MBE Molecular beam Epitaxy

MOS Metal-Oxide-Semiconductor

MOSCAP Metal-Oxide-Semiconductor Capacitor

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

MOVPE Metal-Organic Vapor Phase Epitaxy

PECVD Plasma Enhanced Chemical Vapour Deposition

PVD Physical Vapour Deposition

RMS Root Mean Square

RTA Rapid Thermal Anneal

SEM Scanning Electron Microscopy

SOI Silicon on Insulator

SS Subthreshold Swing

TEM Transmission Electron Microscopy

TMA Trimethyl-Aluminum [Al(CH<sub>3</sub>)<sub>3</sub>]

UHV Ultra High Vacuum

XPS X-Ray Photoelectron Spectroscopy

## **List of Symbols**

A Device Area [m<sup>2</sup>]

C Capacitance [F/m<sup>2</sup>]

C<sub>D</sub> Depletion Layer Capacitance [F/m<sup>2</sup>]

C<sub>et</sub> Capacitance Equivalent Thickness [F/m<sup>2</sup>]

C<sub>fb</sub> Flat-band Capacitance [F/m<sup>2</sup>]

C<sub>HF</sub> High-Frequency Capacitance [F/m<sup>2</sup>]

C<sub>it</sub> Interface State Capacitance [F/m<sup>2</sup>]

C<sub>LF</sub> Low-Frequency Capacitance [F/m<sup>2</sup>]

C<sub>m</sub> Measured Capacitance [F/m<sup>2</sup>]

C<sub>min-meas</sub> Measured Minimum Capacitance [F/m<sup>2</sup>]

C<sub>min-theor</sub> Theoretical Minimum Capacitance [F/m<sup>2</sup>]

C<sub>ox</sub> Oxide Capacitance [F/m<sup>2</sup>]

D<sub>it</sub> Interface State Density [cm<sup>-2</sup>eV<sup>-1</sup>]

E<sub>A</sub> Activation Energy [eV]

E<sub>C</sub> Conduction Band Edge [eV]

E<sub>f</sub> Fermi level [eV]

$E_{f-M}$  Metal Fermi Level [eV]

$E_g$  Energy Bandgap [eV]

$\epsilon_0$  Permittivity of Free Space [F/m]

ε<sub>s</sub> Semiconductor Dielectric Constant

E<sub>V</sub> Valence Band Edge [eV]

f<sub>p</sub> Parallel Conductance Peak Frequency [Hz]

G Conductance [S]

G<sub>m</sub> Measured Conductance [S/m<sup>2</sup>]

G<sub>p</sub> Parallel Conductance [F/m<sup>2</sup>]

I<sub>OFF</sub> Off-state current [A/m<sup>2</sup>]

k Dielectric Constant (or relative permittivity)

k<sub>B</sub> Boltzmann Constant [J/K]

L MOSFET Gate Length [m]

N<sub>D</sub> Semiconductor Dopant Density [m<sup>-3</sup>]

n<sub>i</sub> Intrinsic Carrier Density [m<sup>-3</sup>]

q Electron Charge [C]

Q<sub>fixed</sub> Fixed Oxide Charge [C/m<sup>2</sup>]

Q<sub>it</sub> Interface State Charge [C/m<sup>2</sup>]

t<sub>ox</sub> Oxide Thickness [m]

$\tau_g \qquad \qquad \text{Minority Carrier Generation Lifetime [s]}$

V Voltage [V]

V<sub>DD</sub> Supply Voltage [V]

V<sub>fb</sub> Flat-band Voltage [V]

V<sub>gate</sub> Gate Bias [V]

$V_T$  Threshold Voltage [V]

ω Angular Frequency [rad/s]

W MOSFET Gate Width [m]

W<sub>f</sub> Metal Work Function [eV]

$x_{d-max}$  Maximum Depletion Width [m]

#### Abstract

As silicon based devices in integrated circuits reach the fundamental limits of dimensional scaling there is a growing research interest in the use of high electron mobility channel materials, such as indium gallium arsenide (InGaAs), in conjunction with high dielectric constant (high-k) gate oxides for Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) based devices. The motivation for the use of high mobility channel materials is to reduce the overall power dissipation in integrated circuits while also providing improved performance. For the successful implementation of high mobility channel materials in large volume manufacturing, it will be essential to gain a more complete understanding of electrically active defect states in the high-k/InGaAs MOS system which forms the gate stack of the MOSFET. The work presented in this PhD thesis details the characterization of MOS devices incorporating high-k dielectrics on III-V semiconductor substrates. The analysis examines the role of the semiconductor substrate, optimization of device passivation procedures, and analysis of electrically active interface defect states at the highk/InGaAs interface primarily through the capacitance-voltage (CV) and conductancevoltage (GV) response of the InGaAs MOS system as a function of frequency and temperature.

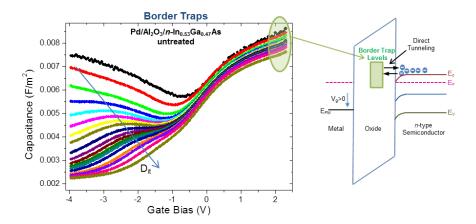

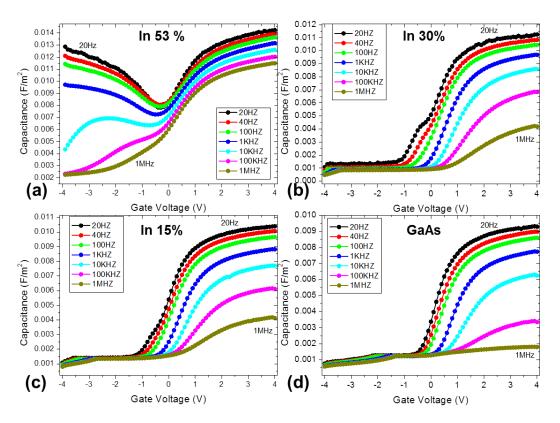

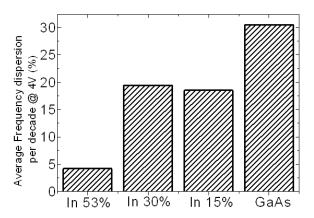

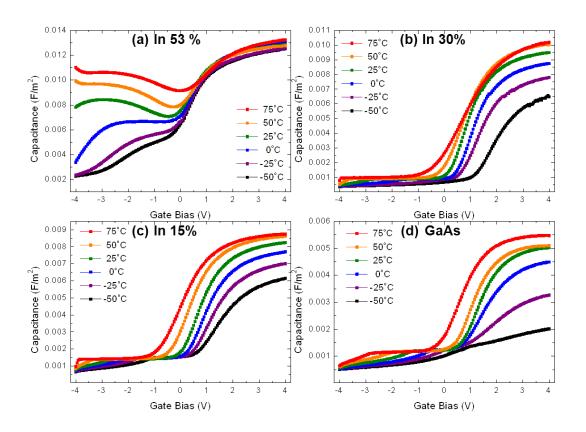

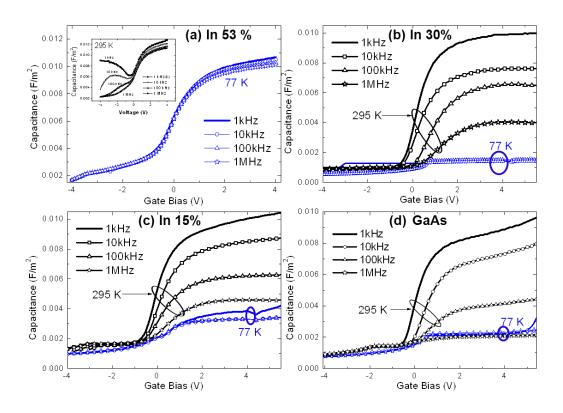

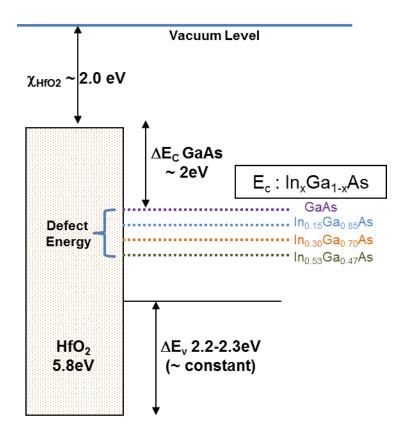

Given one of the primary motivations for introducing these III-V materials is to take advantage of their mobility, one factor of interest is to examine  $In_xGa_{1-x}As$  channels with varying indium concentrations, as a higher indium concentration increases the electron mobility. Of additional significance is how the modification of the  $In_xGa_{1-x}As$  bandgap with varying In concentration affects device performance in terms of interface defect concentration ( $D_{it}$ ) at the high- $k/In_xGa_{1-x}As$  interface. To this end, the structural and electrical properties of  $HfO_2$  films on GaAs and  $In_xGa_{1-x}As$  substrates for x: 0, 0.15, 0.30, and 0.53, were examined. A large dispersion of accumulation capacitance was observed for n-type GaAs and low In content (x = 0.30, 0.15)  $In_xGa_{1-x}As$  epitaxial layers, the electrical behaviour being dominated by an interface state defect response. By contrast, comparison of the capacitance voltage characteristics at 295K and cooled to 77K indicates that it is possible to achieve true

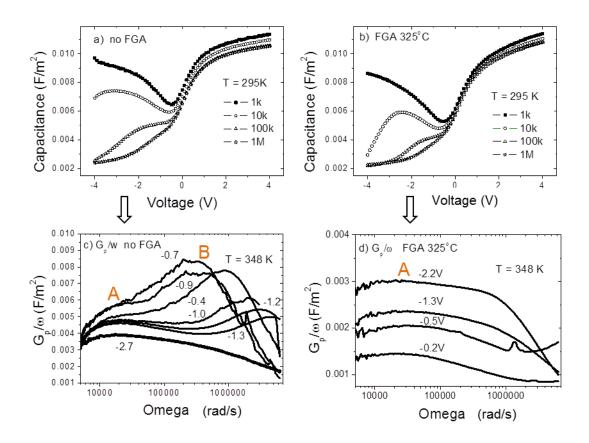

accumulation for an  $In_{0.53}Ga_{0.47}As$  MOS structure. The defect responsible for the accumulation dispersion has a minimum density of  $2.5x10^{13}$  cm<sup>-2</sup>, with an energy level  $\geq 0.75$  eV above the valence band in the  $HfO_2/In_xGa_{1-x}As$  system, where the defect energy with respect to the valence band does not change with the composition of the  $In_xGa_{1-x}As$ . A post-gate metallization  $325^{\circ}C$  forming gas anneal was found to reduce the interface state concentration ( $D_{it}$ ) at the  $HfO_2/In_{0.53}Ga_{0.47}As$  interface, as determined from both CV curves, and analysis of the conductance response versus frequency. As true surface accumulation was only achieved for MOS structures formed on  $In_xGa_{1-x}As$  with a 53% In concentration (x=0.53), the remaining chapters of the thesis focused on  $In_{0.53}Ga_{0.47}As$  lattice matched to InP substrates.

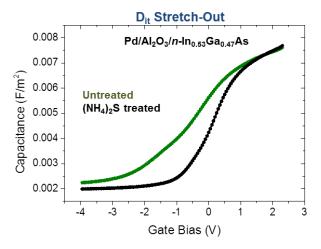

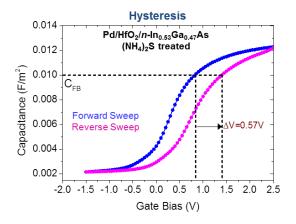

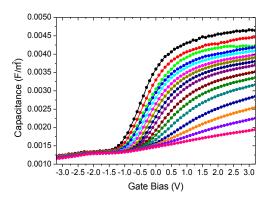

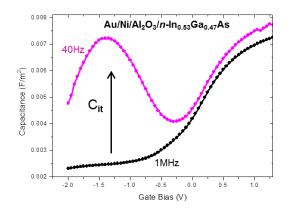

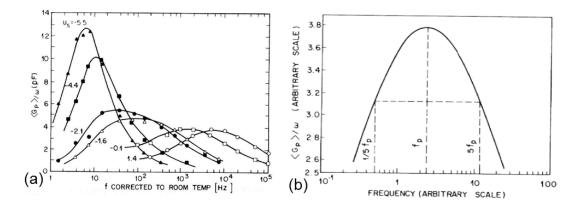

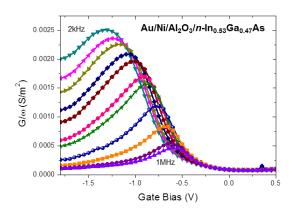

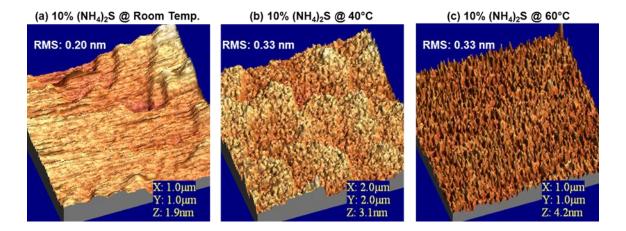

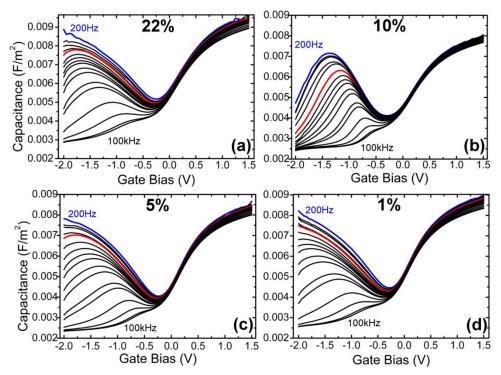

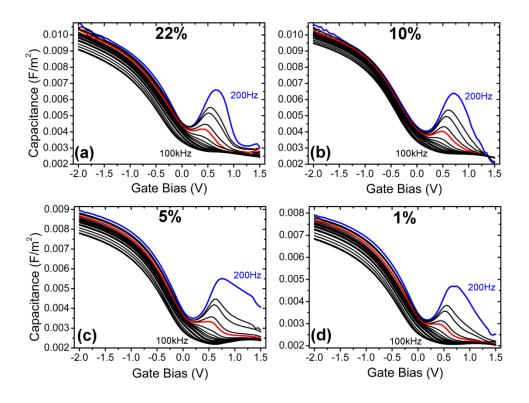

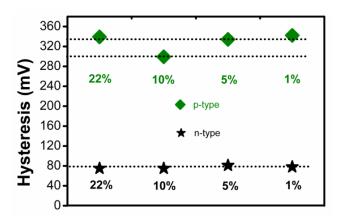

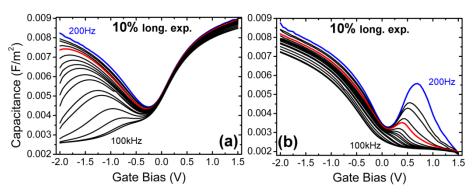

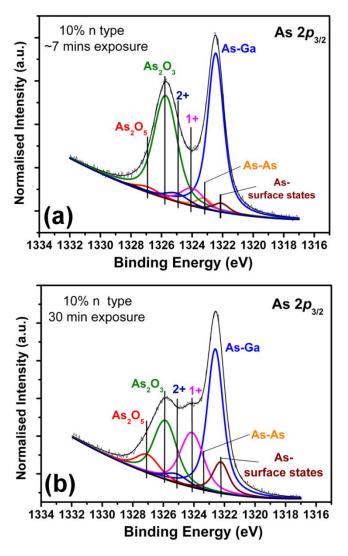

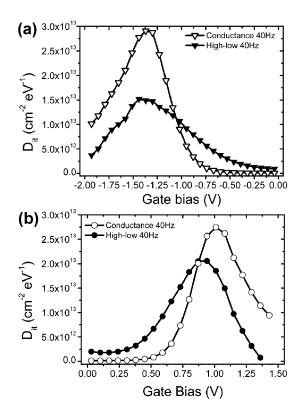

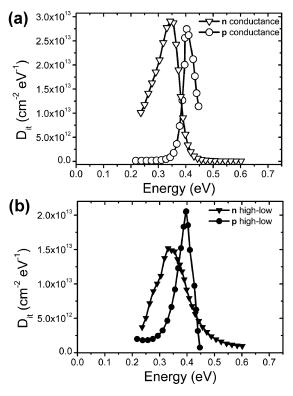

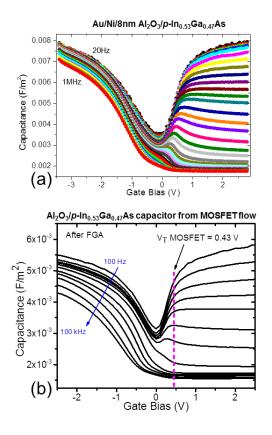

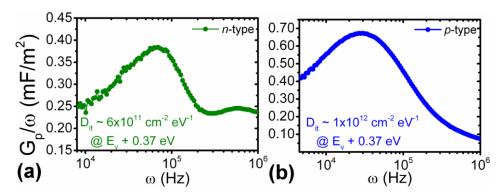

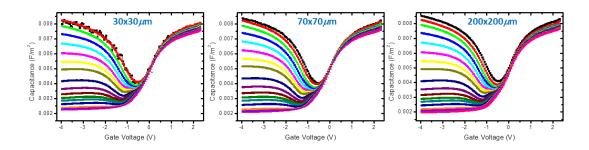

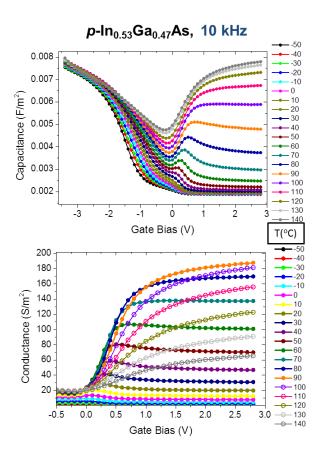

A wide range of passivation approaches have been investigated in order to improve the characteristics of the high-k/III-V interface. Among these are solution based approaches, one of the more popular methods being immersion of the III-V surface in an ammonium sulfide, (NH<sub>4</sub>)<sub>2</sub>S, solution prior to oxide deposition. However, there has not been a clear discussion in terms of optimization of the (NH<sub>4</sub>)<sub>2</sub>S passivation procedure with different research groups using a variety of pretreatments, (NH<sub>4</sub>)<sub>2</sub>S concentrations, and immersion times. Therefore, a systematic study was performed to optimize an ammonium sulphide (NH<sub>4</sub>)<sub>2</sub>S surface passivation technique for In<sub>0.53</sub>Ga<sub>0.47</sub>As. (NH<sub>4</sub>)<sub>2</sub>S concentrations (ranging from 1% to 22%) were investigated, with multi-frequency CV results indicating that the lowest frequency dispersion over the bias range examined occurred for n and p-type Au/Ni/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As devices treated in the 10% (NH<sub>4</sub>)<sub>2</sub>S solution. A deleterious effect on device electrical behaviour of prolonged ambient exposure post In<sub>0.53</sub>Ga<sub>0.47</sub>As surface passivation was identified. Physical analysis of identical films performed using XPS supported this observation through changes in the composition of the re-grown oxide. Estimations of interface state density, Dit, extracted using the Conductance Method, and the High-Low Capacitance-Voltage Method, show very good agreement both in terms of magnitude and characteristic peak profile for the optimum 10% (NH<sub>4</sub>)<sub>2</sub>S passivated In<sub>0.53</sub>Ga<sub>0.47</sub>As devices. The results suggest that these *n*-type and *p*-type devices have an integrated  $D_{it}$  of ~  $2.5 \times 10^{12}$  cm<sup>-2</sup> ( $\pm 1 \times 10^{12}$

cm<sup>-2</sup>) across the  $In_{0.53}Ga_{0.47}As$  energy gap, with the peak density approximately  $0.37eV~(\pm 0.03~eV)$  from the valence band edge.

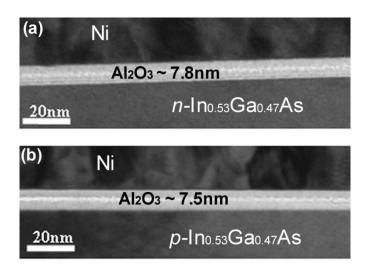

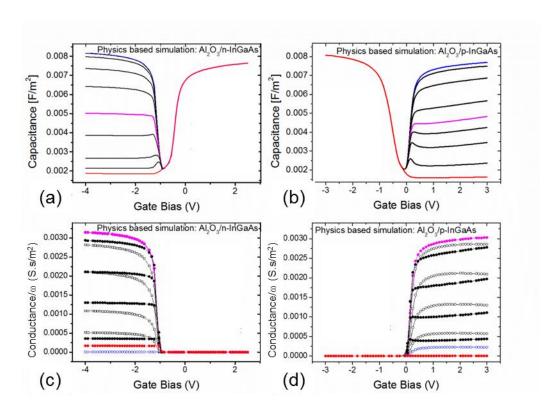

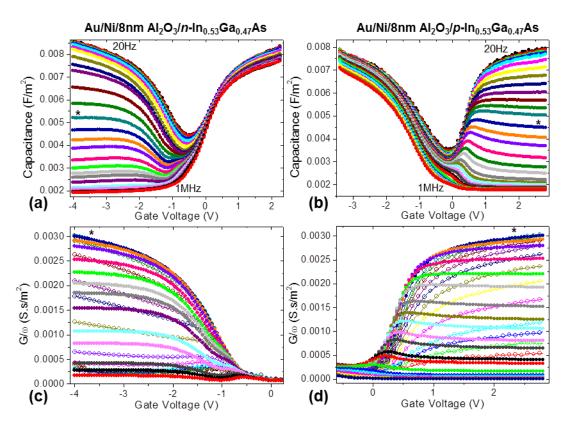

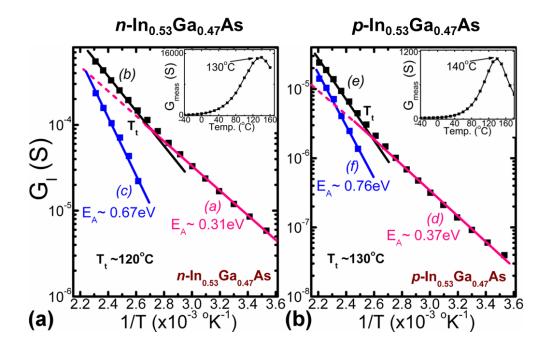

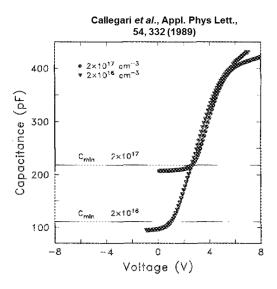

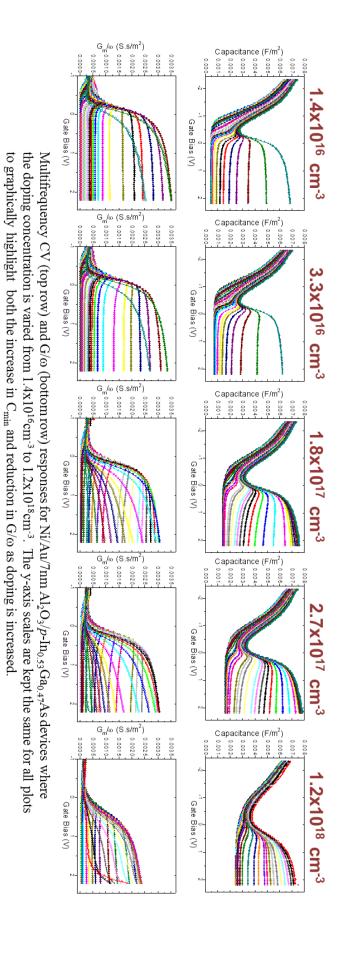

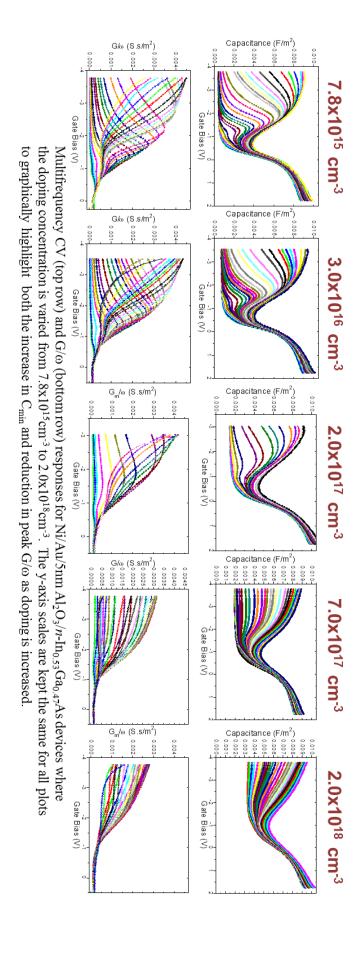

Despite a large research effort worldwide over a number of years, very few studies to date have demonstrated results indicating genuine surface inversion at the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface, owing primarily to the high D<sub>it</sub> typically observed in these devices. Achieving free Fermi level modulation across the bandgap in devices incorporating high-k on In<sub>0.53</sub>Ga<sub>0.47</sub>As, has presented one of the major obstacles to the introduction of this materials system in commercial applications. Following an optimized 10% (NH<sub>4</sub>)<sub>2</sub>S treatment with minimal ambient exposure pre-ALD, a clear minority carrier response was observed for both *n*-type and *p*-type Au/Ni/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS devices in this work. Multi-frequency CV and GV characteristics of the devices exhibited a number of signature features consistent with inversion of the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface. Analogous behavior was observed at fixed frequency with varying measurement temperature. An Arrhenius extraction of activation energies for the minority carrier response indicated a transition from a generation-recombination regime at lower temperature to a diffusion controlled response at elevated temperatures, for both n-type and p-type devices. Also, MOS capacitors were fabricated on n and p-In<sub>0.53</sub>Ga<sub>0.47</sub>As with semiconductor doping concentrations ranging over two orders of magnitude from ~1x10<sup>16</sup>cm<sup>-3</sup> to ~ $2x10^{18}$ cm<sup>-3</sup>. It was clearly observed for both n and p-In<sub>0.53</sub>Ga<sub>0.47</sub>As devices that the measured C<sub>min</sub> increases as doping concentration increases, and that the measured C<sub>min</sub> is in very good agreement with the theoretical value calculated by assuming an inverted surface. Taken as a whole, these observations are consistent with a Dit which is sufficiently reduced for the n-type and p-type devices examined in this work to permit the Fermi level to be swept across the band gap at the In<sub>0.53</sub>Ga<sub>0.47</sub>As/Al<sub>2</sub>O<sub>3</sub> interface.

The oxide capacitance,  $C_{ox}$ , is an important parameter in general for device analysis, for example in many common  $D_{it}$  extraction methods. Therefore an experimental method to determine  $C_{ox}$  accurately would be of great benefit for device analysis purposes, particularly for narrow bandgap systems such as  $In_{0.53}Ga_{0.47}As$ . Experimental observations for  $In_{0.53}Ga_{0.47}As$  devices in this work indicated that in

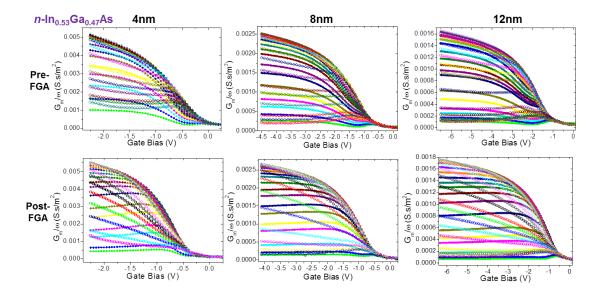

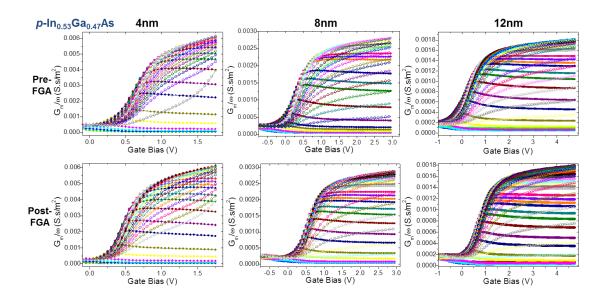

strong inversion the peak magnitudes of  $G/\omega$  and  $-\omega dC/d\omega$  are equal, with the peaks being coincident at the transition frequency,  $\omega_{\rm m}$ . Physics based simulations exhibited near-identical behavior. The observation of this unique relationship offers an experimental route to estimate the value of oxide capacitance, Cox. Mathematical derivations performed using an equivalent circuit model yielded expressions of  $C_{ox}^{2}/2(C_{ox}+C_{D})$  for  $(G/\omega)_{max}$  and  $(-\omega dC/d\omega)_{max}$ , where  $C_{D}$  is the semiconductor depletion capacitance. This provides a straightforward method for more accurate determination of Cox not only for III-V based devices, but for MOS systems in general. The usefulness of this relationship was demonstrated by varying the experimental C<sub>ox</sub> of samples through the use of a range of Al<sub>2</sub>O<sub>3</sub> thicknesses (4nm, 8nm, and 12nm) on n and p-type  $In_{0.53}Ga_{0.47}As$ . The expression derived for  $(G/\omega)_{max}$ was found to provide an accurate fit to the Cox measured from CV at low frequency over the thickness range, providing a practical example of the application of this relationship and it's benefits particularly with regard to lower E<sub>ot</sub> devices. In addition it was found that a post gate metallization forming gas anneal leads to a reduction in the measured transition frequency. This is inversely proportional to the minority carrier generation lifetime, which was extracted through simulations from the measured  $\omega_m$  values. This provides another metric to assess improvements in device quality as an increase in the minority carrier generation lifetime indicates a reduction in the density of bulk defects responsible for the minority carrier response in the generation-recombination regime.

#### Acknowledgements

Firstly, I want to thank my supervisor Dr. Paul Hurley. I consider myself very fortunate to have had the privilege to work as his PhD student for the past number of years. Thanks to Paul, I was involved in exciting research, had the opportunity to travel and to experience other research environments, and was allowed great freedom in the research I wanted to pursue. I also enjoyed the benefits of learning from Paul's expert knowledge, and being motivated by his positivity, and I could not have wished for a better PhD experience. In addition I am indebted to Dr. Karim Cherkaoui, not only for his very generous help and support over the years, but also for his friendship.

I wish to thank Dr. Scott Monaghan for his contributions to the work over the years. I would like to acknowledge other members of our group, both past and present, with whom it has been a pleasure to work, namely Vladimir Djara, Brendan Sheehan, Jun Lin, Adi Negara, Barry Hutchinson, and Adrian Walsh.

I sincerely thank Prof. Bruce Hamilton of the University of Manchester and Prof. Jim Greer of Tyndall National Institute for acting as my PhD examiners.

I wish to express my gratitude to some of my Tyndall colleagues for their support of this work over a number of years, in particular Dr. Ian Povey for the many ALD growths, and Dan O'Connell for the metallization runs. I am grateful also to Dr. Kevin Thomas for the MOVPE growths, to Dr. Pat Carolan for TEM imaging, and to Liam Floyd for his contribution to the mathematical analysis. I wish to acknowledge also Prof. Martyn Pemble and my other collaborators on the FORME project.

I would like to express particular thanks to Dr. Bob Wallace for his generosity in hosting me for seven months in his research group at the University of Texas at Dallas in 2009. It was an enormously valuable learning experience and some of the work we performed there provided a platform for the progress that subsequently followed back home.

I also express my appreciation to Dr. Martin Frank, Dr. John Rozen, Dr. Vijay Narayanan, and Dr. Richard Haight, who hosted me for a summer internship at IBM Yorktown in 2013. I am grateful to my colleagues at DCU, in particular, Dr. Greg

Hughes and Dr. Barry Brennan. I thank Dr. Simon Newcomb of Glebe Scientific for his TEM analysis. Additionally, I had the good fortune of working with Dr. Guy Brammertz of IMEC, and Prof. Enrique Miranda of UAT Barcelona, and enjoyed my research visits to their respective laboratories.

I wish to acknowledge our many valuable discussions and fruitful collaboration with Intel Components Research, in particular, Dr. Kelin Kuhn, Dr. Rafael Rios, and Dr. Fahmida Ferdousi. I would also like to thank Roger Nagle, Intel researcher in residence at Tyndall.

I would like to thank my friends who have been there in good times, and just as importantly in difficult times. Thanks to John, not least for playing his role in one of history's most intense sporting rivalries, and more; thanks to Number One, an accomplice amongst other things in forays into fiction and adventures across continental Europe; and lastly I thank Kevin for his "absolutely average" friendship. Finally, and most importantly, I thank my family, my brother Brian, my mother Bridgid, and my late father, Eddie. I owe them everything for the opportunities I enjoy today. This work is dedicated to them.

# Chapter 1

# 1. Background and Motivation

#### 1.1. Introduction

The purpose of this chapter is to place in context the motivation for exploring the devices and materials systems studied in this thesis. A brief overview of the history of complementary metal-oxide-semiconductor (CMOS) transistor development is presented. In addition current trends in terms of the materials and device concepts being considered for future CMOS generations are outlined. An overview of the content of the thesis is also described.

#### 1.2. Moore's Law

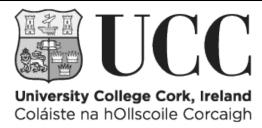

The last forty years have seen dramatic developments in computing power, information storage and digital communication technologies. This progress has been fuelled primarily by on-going miniaturisation of the metal oxide semiconductor field effect transistors (MOSFETs), which are the fundamental switching elements of integrated circuits. A schematic of a traditional *n*-MOSFET structure is shown in Figure 1.1, where W is the width of the device and L is the gate length. The thickness of the gate oxide employed as a dielectric in the structure is usually referred to as t<sub>ox</sub>. The scaling of MOSFET gate length dimensions from values of around 10  $\mu$ m in the early 1970's to values of around 65nm in 2007 was achieved without changing the basic device concept or the silicon and silicon dioxide (SiO<sub>2</sub>) materials which constitute the device.

Figure 1.1 Schematic of traditional *n*-MOSFET. L and W are the device length and width respectively.

In 1965 Gordon Moore predicted that the density of transistors on a single chip would double every 18 months. While a reduction in transistor size has obvious benefits in terms of footprint, allowing greater functionality per chip, the work of Dennard et al. also demonstrated attendant advantages in that as devices are scaled their logic characteristics also improve.<sup>2</sup> Decades of scaling have therefore resulted in vast improvements in switching speed, switching power, and supply voltage reduction. In recent years however it became clear that further scaling would not be possible using conventional device architectures and materials. A plateau was reached in this respect owing to the fact that device dimensions were now reduced to values where issues such as short channel effects become significant.<sup>3, 4</sup> Additionally, and of fundamental importance as consumer demand for low-power electronics increases is the fact that the density of devices per chip has reached levels where the power dissipation per chip is a major issue. The use of techniques such as strained Si was introduced at the 90nm and 65nm technology nodes to offset some of the problems associated with these shrinking device dimensions. One of the disadvantages in this respect was posed by ultra-thin SiO<sub>2</sub> layers, the thickness of which was now approaching 1.2 nm, equating to just a few atomic layers. Direct electron tunneling

through the gate oxide becomes a major problem at this thickness, resulting in high leakage currents and inevitably higher power consumption. In fact the off-state power dissipation becomes comparable to the active power dissipation, which is an unsustainable situation and requires impractical solutions in terms of cooling and packaging. Additionally, the impact of such tunneling currents raised serious concerns about reliability and lifetime issues in utilization of such thin oxide layers. In order to continue to meet targets set by Moore's Law a more revolutionary approach was required.

### 1.3. Incorporation of high-k dielectrics

The 45nm node marked the greatest shift in the history of MOSFET development in terms of its material composition. Intel introduced an oxide layer with a dielectric constant (k) higher than that of SiO<sub>2</sub> (3.9). For ease of nomenclature all materials with k>3.9 are usually referred to as high-k dielectrics. The source-drain current of a MOSFET is largely dependent on the capacitance of the MOS gate stack at the heart of an FET device. The rationale for incorporating a high-k material can be easily understood using the relationship in Equation 1.1, where C is capacitance,  $\epsilon_0$  is the permittivity of free space, k is the dielectric constant (or relative permittivity) of the dielectric, A is the area of the capacitor, and  $t_{ox}$  is the oxide thickness.

$$C = \frac{\varepsilon_0 kA}{t_{ox}}$$

[EQ. 1.1]

It is obvious that an equivalent capacitance density can be achieved using a thicker oxide with a higher dielectric constant. Therefore, given that tunneling current decreases exponentially with distance, this offers the potential to incorporate a thicker oxide layer in the MOSFET structure to eliminate some of the issues associated with excessive ultra-thin gate oxide leakage. A useful term is the Equivalent Oxide Thickness (EOT) which refers to the theoretical thickness of SiO<sub>2</sub> which would be required to achieve an equivalent capacitance density to that using a high-*k* dielectric.

$$EOT = \frac{3.9}{k_{high-k}} t_{high-k}$$

[EQ. 1.2]

Incorporation of high-k materials in CMOS posed a number of formidable challenges, not only as the existing SiO<sub>2</sub>/Si technology was decades into its development, but also in that the industry had benefited enormously from a number of fortuitous and remarkable properties of SiO<sub>2</sub> on Si. Research into high-k oxides exploded in the late 1990's and early 2000's and a review paper by Wilk et al,<sup>5</sup> identified a number of key attributes required for any SiO<sub>2</sub> replacement. Among these were: permittivity; band offsets and insulating properties; thermodynamic stability; morphology; interface quality; process compatibility; reliability. SiO<sub>2</sub> is stable up to 1000°C, critical for example in terms of thermal budget for source/drain implants. In terms of processing, SiO<sub>2</sub> was ideal as it was possible to thermally oxidize the Si to form SiO<sub>2</sub>, giving the added benefits of near ideal stoichiometry, excellent film morphology with a smooth interface with Si, and a very low density of interface defects (Dit). SiO<sub>2</sub> also remained amorphous to high temperature, which avoided the issue of grain boundaries forming in the oxide to promote leakage pathways. One other important asset of the SiO<sub>2</sub>/Si system was its etch selectivity, which was critical as device dimensions reduced exponentially, and it was possible to pattern to the nanometer scale.

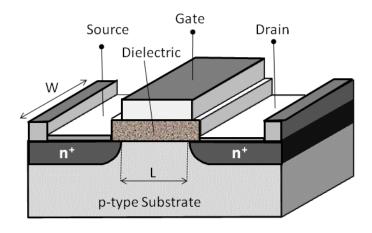

Figure 1.2 A plot of bandgap versus dielectric constant for a selection of the high-k candidate materials.<sup>6</sup>

Some of the prominent high-k options, and a plot of their band-gap versus permittivity, are seen in Figure 1.2. <sup>6</sup> As research into high-k materials progressed, the primary difficulties associated with their use became apparent. In terms of processing, the existing polysilicon gate was unsuitable for use with high-k, necessitating the use of metal gates in order to prevent reactions at the high-k polysilicon interface affecting device performance. Some complications in this regard stem from the fact that if a single gate metal is chosen then it would have to have a work function suitable for n-MOS and p-MOS, and if different gate metals were tailored for each this would induce extra processing complexity.

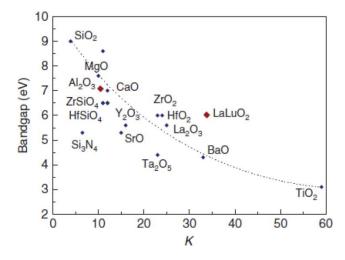

As the advantage of thermal oxide growth of the native oxide was lost, another issue became the deposition method on Si to be used for the high-k oxides. Thermally grown oxides are of higher quality than deposited oxides. Physical Vapour Deposition (PVD), Chemical Vapour Deposition (CVD), and Atomic Layer Deposition (ALD) were considered as possible techniques for high-k. ALD became one of the more popular methods adopted for research purposes. ALD operates in a sequence of alternating half-cycles where gaseous precursors are introduced to a vacuum deposition chamber in isolation. One pulse carries the metal associated with the high-k oxide (e.g., Al or Hf) and the second pulse carries the oxidant species. As the first gaseous precursor is injected it is chemisorbed on to the heated substrate. A

Figure 1.3 A schematic showing a typical pulse-purge sequence in the deposition of  $Al_2O_3$ , using  $Al(CH_3)_3$  and  $H_2O$  as precursors, from the review of Wallace *et al.*<sup>11</sup>

purge pulse is then used to remove physisorbed unreacted precursor and gas phase by-products. The whole process is repeated using the second precursor to complete an ALD cycle. This results in highly controllable self-limiting monolayer growth. Another important advantage is that it results in highly conformal films, making it suitable for complex structures and small feature sizes, ideal for CMOS. A typical pulse-purge sequence for deposition of Al<sub>2</sub>O<sub>3</sub>, using Al(CH<sub>3</sub>)<sub>3</sub> and H<sub>2</sub>O as precursors, is shown in the schematic from the review of Wallace *et al* in Figure 1.3. However, one drawback is that the use of precursors in the ALD of high-*k* oxides can introduce impurities in the oxide film originating from the precursor ligands. Defects in the oxide can lead to trapping of charges within the oxide layer, inducing threshold voltage shifts in MOSFET devices, and affecting reliability. Further it has been reported that remote phonon scattering effects from charges in the high-*k* can lead to a mobility reduction for devices incorporating high-*k* on Si.

One of the most significant problems associated with the incorporation of high-*k* materials was that interface defect densities at the interface of high-*k* with Si tended to be higher than those obtained for SiO<sub>2</sub>/Si. In that system so called dangling bond defects (P<sub>b</sub> type defects) were known to exist originating from the Si surface, adversely affecting device performance. However these could be reduced significantly by annealing in forming gas (H<sub>2</sub>/N<sub>2</sub>), resulting in very low defect densities of the order of mid 10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup>. It is very difficult to achieve comparable densities at the interface of high-*k* directly on Si. A higher D<sub>it</sub> at the interface degrades the subthreshold slope (SS) of a MOSFET device, which impinges on its switching performance. In addition interface defects compromise MOSFET mobility values due to Coulomb scattering effects. Annealing of the defects is not as straightforward as for the SiO<sub>2</sub>/Si case, as there are greater thermal budget constraints on high-*k* oxides. For example HfO<sub>2</sub> tends to crystallize at temperatures as low as 350°C to 500°C. Any roughening at the interface due to thermal degradation will also deleteriously affect mobility.

It was indeed a remarkable feat that Intel overcame many of the engineering obstacles with the introduction of their 45 nm node device, incorporating HfO<sub>2</sub> in the MOSFET gate stack which became the first high-k material used in mainstream CMOS manufacture. One point to make in this regard is that it was found that a very thin SiO<sub>2</sub> layer was required at the interface between the Si and the HfO<sub>2</sub>, see Figure 1.4. The incorporation of this layer was deemed necessary to offset some of the aforementioned issues. This means the interface is still effectively SiO<sub>2</sub> on Si, which negates some of the mobility reduction introduced by high-k due to surface roughening, Coulomb scattering due to interface defects, and remote phonon scattering due to defects in the high-k film. However this now raises one of the main concerns originally mooted for high-k, ie. whether the scaling benefits would last for more than one technology generation. Continued EOT scaling requires thinning of the HfO<sub>2</sub> and this SiO<sub>2</sub> interlayer, yet the screening benefits of the interlayer are inhibited with reducing thickness. Therefore some opinion formed in the field that while the introduction of high-k was a stepping stone, an even more drastic step in terms of material composition was needed.

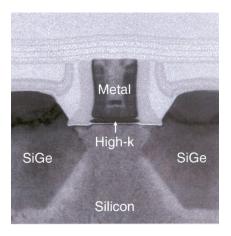

Figure 1.4 SEM image showing the device structure for the 45nm node device introduced by Intel in 2007, the first device in mainstream CMOS manufacture incorporating a high-k dielectric. The device also utilized a metal gate, and a thin SiO<sub>2</sub> layer is visible between the HfO<sub>2</sub> high-k layer and the Si channel.<sup>8</sup>

#### 1.4. High mobility semiconductors

Some of the critical requirements for future generations according to the International Technology Roadmap for Semiconductors (ITRS) were summarized in a recent review article by Thayne et al.. 9, 10 Given the stringent criteria for device performance beyond the 15 nm technology generation it is foreseen that replacing silicon with high mobility channels will be the next major materials revolution. Using high mobility channel materials allows for a reduction in operating voltage, leading to reduced power dissipation, and their incorporation potentially combats some of the mobility reductions mentioned previously for high-k/Si systems. Therefore in recent years, materials with a higher mobility than Si have been researched as the channel layer for future MOSFET design. Table 1.1 summarizes the electron and hole mobilities for a range of semiconductor materials. For the case of n-channel devices, high electron mobility is desirable, with GaAs among the materials fulfilling this requirement and in the case of In<sub>0.53</sub>Ga<sub>0.47</sub>As the increase is around one order of magnitude when compared to Si. It is notable that the hole mobility of In<sub>0.53</sub>Ga<sub>0.47</sub>As is not exceptional, which is one of the reasons why Ge is also under consideration for use as a p-channel, with its hole mobility being over four times higher than that of Si. Therefore one potential approach to maintain the scaling roadmap is the heterogeneous integration onto a silicon platform of these high mobility semiconductors, using Ge for p channel devices and III-V compound semiconductors for the complementary n channel devices. As the work presented in this thesis is conducted primarily for devices incorporating oxides on GaAs and In<sub>0.53</sub>Ga<sub>0.47</sub>As surfaces, the discussion here will focus on these materials.

| Material                   | Si   | Ge   | GaAs | In <sub>0.53</sub> Ga <sub>0.47</sub> As | InAs  | InSb  |

|----------------------------|------|------|------|------------------------------------------|-------|-------|

| Electron Mobility (cm²/Vs) | 1400 | 3900 | 8500 | 14000                                    | 40000 | 78000 |

| Hole mobility<br>(cm²/Vs)  | 450  | 1900 | 400  | 300                                      | 500   | 850   |

Table 1.1 Electron and hole mobilities for a number of semiconductor materials

#### 1.5. Challenges for incorporation of high-k on III-V

One of the primary challenges with regard to incorporation of high-k materials on III-V semiconductors is that there tends to be a high density of defects at the interface of the dielectric and the semiconductor, with the majority of studies reporting values in excess of  $10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>, compared to ~ mid- $10^{10}$  cm<sup>-2</sup> eV<sup>-1</sup> for SiO<sub>2</sub>/Si. Unfortunately, there are no beneficial native oxides on III-V. As already discussed, the incorporation of high-k on Si was fraught with difficulties at the interface, which were not entirely resolved as Intel incorporated a SiO<sub>2</sub> layer in their 45nm technology. The problem is now even more complicated in that you have a high-k layer in contact with a compound semiconductor. If you compare for example the ideal case of a SiO<sub>2</sub> on Si interface with that of one comprised of HfO<sub>2</sub> on In<sub>0.53</sub>Ga<sub>0.47</sub>As, you venture from a materials system where two elements are present to one where you have five distinct elements, and therefore a far greater propensity for defect formation. 11 Competition between these elements leads to a greater range of potential interfacial oxides at the high-k/III-V interface. Formation of multiple oxide states, some of which are unstable are thought to be one of the main contributors to the poor interfacial properties observed for this materials system.

The level of D<sub>it</sub> observed historically for devices incorporating dielectrics on GaAs, being over two orders of magnitude higher than that for SiO<sub>2</sub>/Si systems, has typically meant that it is not possible to modulate the Fermi level to achieve free movement of charge carriers within the GaAs channel layer. Note that more specific discussion of electrical characteristics of devices relevant to this thesis work is presented in Chapter 2. Despite over three decades of research, even at the time of writing relatively few studies have demonstrated acceptable results for dielectrics on GaAs. Callegari *et al* observed an improvement for MOS devices by using a plasma clean treatment on the GaAs surface and then depositing a gallium oxide film by e-beam evaporation. Passlack *et al* deposited a Ga<sub>2</sub>O layer on GaAs by molecular beam epitaxy (MBE). However, deposition approaches such as e-beam and MBE are not particularly suited for expansion to a full manufacturing process.

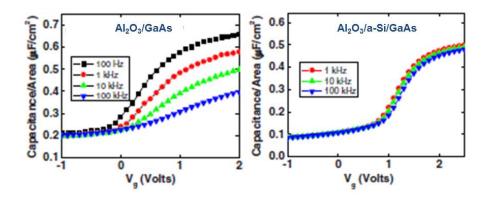

More recently the incorporation of amorphous silicon (*a*-Si) capping layers has shown promising results. <sup>14, 15</sup> DeSouza *et al* performed a study using different techniques to deposit the *a*-Si layer, e-beam evaporation, MBE, and plasma enhanced chemical vapor deposition (PECVD). Significantly this was only successful using the PECVD method, which is notable for being a hydrogen rich environment. Therefore it was surmised that hydrogenation of the surface was key to the improved electrical characteristics. As mentioned before H based anneals such as forming gas annealing are routinely used for Si based devices. Hinkle *et al*, using a similar PECVD *a*-Si layer on GaAs, attempted to correlate an improvement in the electrical characteristics with physical characterization of oxide species at the interface via X-Ray Photoelectron Spectroscopy (XPS). Such correlation of electrical and physical properties is far from trivial, but can help provide valuable understanding of high-*k*/III-V interfaces, and remains an area somewhat under-explored in the literature. It is worth stating that achieving comparable results with high-*k* layers deposited on GaAs in the absence of the interlayers mentioned above remains elusive.

With regard to  $In_xGa_{1-x}As$ , lower indium content films (x<0.53) are usually formed by epitaxial growth on GaAs, while higher indium content layers (x $\geq$ 0.53), such as  $In_{0.53}Ga_{0.47}As$ , are typically grown on InP by employing metal organic vapour phase epitaxy (MOVPE). The latter has garnered much favour in research over the last number of years as  $In_{0.53}Ga_{0.47}As$  can be grown lattice matched to the underlying InP, and this results in high-quality epitaxial layers with a low density of structural defects. Additionally MOVPE is viewed as being more suitable than MBE for large scale wafer production.

Various techniques have been used in an attempt to passivate the high- $k/In_xGa_{1-x}As$  interface. A common approach due to its relative simplicity is to use wet chemical treatments to remove native oxide species prior to deposition of the dielectric. A wide range of wet chemical solutions have been employed: dilutions of ammonium hydroxide (NH<sub>4</sub>OH) in either HCl or water<sup>17, 18</sup>; acid cleans such as sulphuric (H<sub>2</sub>SO<sub>4</sub>), hydrofluoric (HF), and hydrochloric (HCl) <sup>19</sup>; and aqueous solutions of ammonium sulfide, (NH<sub>4</sub>)<sub>2</sub>S, which was frequently used in the past for

InP and GaAs has become one of the most popular solution based passivation methods. <sup>20, 21, 22</sup> Another technique has been to flow hydrogen sulfide (H<sub>2</sub>S) gas over the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface at the end of MOVPE growth in an effort to passivate the surface using atomic H and S. <sup>23</sup> Obviously, given that subsequent oxide deposition is performed ex-situ following the aforementioned treatments, the efficiency of the passivation can be compromised somewhat by the exposure to ambient conditions during the transfer to the oxide deposition system.

A rather different approach has been to deposit interface passivation layers on In<sub>0.53</sub>Ga<sub>0.47</sub>As prior to ALD of the high-k, in an attempt to suppress formation of oxides on In<sub>0.53</sub>Ga<sub>0.47</sub>As and to yield an improved interface compared to that of high-k directly on In<sub>0.53</sub>Ga<sub>0.47</sub>As. In that vein, groups have also adopted the a-Si passivation layers mentioned earlier for GaAs for use in their In<sub>0.53</sub>Ga<sub>0.47</sub>As devices. <sup>24,25, 26</sup> Other groups have utilized "capping" layers, which are deposited in-situ after the In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial growth and thus are designed to prevent any oxidation and preserve the integrity of the surface. InP is one such capping layer that has been deposited in-situ after In<sub>0.53</sub>Ga<sub>0.47</sub>As growth.<sup>27</sup> These thin InP layers have a suitable bandgap, prevent uncontrolled oxidation of the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface, and also have the benefit of moving the critical interface so that carriers in the In<sub>0.53</sub>Ga<sub>0.47</sub>As channel are less susceptible to the influence of defects. Zhao et al. reported an improvement in In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET characteristics on inclusion of a 4nm thick InP capping layer. Intel have also reported the use of a 2nm InP capping layer on a In<sub>0.7</sub>Ga<sub>0.3</sub>As channel. <sup>28</sup> A slight variant on this idea has also been used whereby a sacrificial arsenic capping layer is formed at the end of the InGaAs epitaxial growth. This is subsequently desorbed in-situ at high temperature in the same chamber used for dielectric deposition. 29, 30,31

While a wide variety of high-*k* dielectrics have been examined, such as HfO<sub>2</sub><sup>22, 23</sup>, LaAlO<sub>3</sub><sup>29</sup>, Si<sub>3</sub>N<sub>4</sub><sup>32,33</sup>, Ga<sub>2</sub>O<sub>3</sub>/Gd<sub>0.25</sub>Ga<sub>0.15</sub>O<sub>6</sub><sup>34</sup>, and Sr<sub>2</sub>TaO<sub>6</sub><sup>35</sup>, Al<sub>2</sub>O<sub>3</sub> has emerged as one of the most heavily investigated oxide layers for both GaAs and In<sub>0.53</sub>Ga<sub>0.47</sub>As. One of the main reasons for the focus on Al<sub>2</sub>O<sub>3</sub> is due to the reported "self-cleaning" effect during ALD deposition of Al<sub>2</sub>O<sub>3</sub> from the Al(CH<sub>3</sub>), (trimethylaluminium,

TMA) precursor. Numerous reports in the literature indicate that growth of  $Al_2O_3$  using TMA evidently results in either the removal of interfacial oxide species, or their conversion to  $Al_2O_3$  during the ALD process.  $^{36, 37, 38}$  One of the contributory factors to this is thought to be the reactivity of the TMA precursor itself.  $^{39}$  By contrast this is not observed using the most common precursors used for ALD deposition of  $HfO_2$  on III-V, and therefore some interfacial oxide layers typically remain. As a consequence electrical characteristics indicate a higher  $D_{it}$  for similar devices utilizing  $HfO_2$  compared to  $Al_2O_3$ . Although the dielectric constant of  $Al_2O_3$  is relatively modest (in the range 7 to 9), its potential to from a good interface with III-V semiconductors has sustained interest in its use. Indeed recently, one route to compensate for the k-value of  $Al_2O_3$  in order to achieve the EOT scaling necessary has been to use a bi-layer gate stack, whereby a thin  $Al_2O_3$  layer is used to improve the interface and a higher dielectric constant material such as  $HfO_2$  is then deposited for EOT scaling purposes.  $^{40, 41}$

# 1.6. Co-integration of Ge and III-V materials on a Si based platform

As mentioned earlier a possible evolution for CMOS is utilizing III-V materials for n-channel devices and Ge for p-channel devices. For economic and practical reasons it will be necessary to combine the benefits of these new materials with well-established Si manufacturing processes, requiring co-integration of Ge and III-V FETS on the same Si substrate. The use of large diameter Si wafers is cost effective, and realistically the new technologies must fit in with the existing Si based manufacturing platform to make use of the extensive tool set developed by industry in this regard. Co-integration of III-V and Ge on Si poses difficulties perhaps as significant as any other for their viability as a future materials system. III-V materials in particular differ significantly from Si with regard to crystal structure, lattice properties, and coefficient of thermal expansion. It is envisaged that Ge and  $In_xGa_{1-x}As$  (x > 0.53) active areas will be co-integrated at a nanometer lateral scale on the same large size Si wafer (300 or 400 mm). Different methods are being considered to obtain such

hybrid substrates, be it with selective epitaxy, also called aspect ratio trapping, <sup>42</sup> or with direct wafer bonding. <sup>43, 44</sup> The differing thermal stabilities of Ge, In<sub>x</sub>Ga<sub>1-x</sub>As, and Si, come into play regardless of which method is used. The melting point of Ge is for example about 940°C, 500°C lower than silicon, and In<sub>x</sub>Ga<sub>1-x</sub>As tends to decompose above 600°C. This potentially introduces tremendous processing complexity in that anneals intended for either Ge *p*-FET or In<sub>x</sub>Ga<sub>1-x</sub>As *n*-FET must be compatible in order to not exceed the thermal tolerance of the other material. It is possible that techniques such as milli-second annealing will therefore also be a key technology to enable the co-integration of Ge and In<sub>x</sub>Ga<sub>1-x</sub>As. Some progress is being made in this area, as evident in a recent report by Czornomaz *et al.* of IBM, <sup>44</sup> see Figure 1.5 below. The nanoscale co-integration of such materials with differing lattice constants and thermal budget constraints, while maintaining a sufficiently low density of structural defects remains one of the most significant challenges in this field.

Figure 1.5 Top-view SEM image from the work of Czornomaz *et al.*<sup>44</sup> at IBM showing dense co-integration of co-planar nano-scaled SiGe based p-FETs and InGaAs based n-FETs on a Si substrate.

#### 1.7. Use of novel device architectures

It is worth briefly mentioning that in addition to the increasing movement towards incorporation of new materials, there is also large effort being invested in the design of new transistor architectures in the drive for continued scaling. In a recent review article, Thayne  $et\ al^{16}$  described some of the alternative architectures being investigated for planar III-V devices and described some of the considerations justifying these approaches.

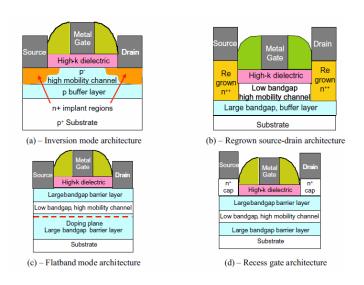

Figure 1.6 A sample of some of the device architectures reported in the literature for III-V based devices, as discussed by Thayne  $et\ al.^{16}$

Even for Si-based devices, Intel has already moved away from the traditional two-dimensional, planar MOSFET design to the use of a three-dimensional (3-D) multiple gate architecture they introduced at the 22nm node in 2011. These so-called Tri-gate devices offer improved electrostatic control compared to their planar counterparts, while the tradeoff to be overcome in this case was that the introduction of such a device architecture obviously entailed very significant design complexity as well as manufacturing challenges. Figure 1.7 shows a schematic of a Tri-Gate architecture, alongside which an SEM of a processed device shows the gate and fin structures. A number of groups have also recently explored using such 3-D architectures for III-V channel materials. The same architecture away from the traditional two-dimensional control compared to their planar counterparts, while the tradeoff to be overcome in this case was that the introduction of such a device architecture obviously entailed very significant design complexity as well as manufacturing challenges. The same architecture of a Tri-Gate architecture, alongside which an SEM of a processed device shows the gate and fin structures. A number of groups have also recently explored using such 3-D architectures for III-V channel materials.

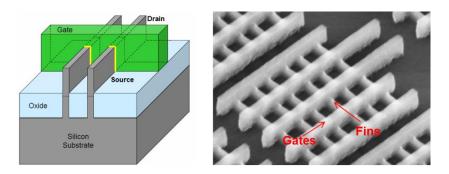

Figure 1.7 Schematic of device structure and SEM showing gates and fins in an Intel Tri-gate 22nm node device. 49

#### 1.8. Thesis Outline

As mentioned in the previous section there are a range of challenges associated with the incorporation of III-V based channel materials into a CMOS process. The research work described in this thesis is focused on the high- $k/In_xGa_{1-x}As$  gate stack, and covers issues associated primarily with the characterization, understanding, and control, of electrically active interface defects.

The electrically active interface defects are investigated through the fabrication and characterization of MOS devices incorporating high-k dielectrics on III-V semiconductors. As alluded to earlier, MOS capacitors serve as ideal test structures to evaluate a number of passivation methods designed to reduce  $D_{it}$  at the high-k/III-V interface. This includes techniques to passivate the III-V epitaxial surface prior to ALD deposition of the high-k, and annealing performed after gate metal deposition. Obviously MOS devices can be fabricated more quickly and easily than MOSFETs, which typically require multiple process flows, and this enables MOS devices to be used to efficiently screen numerous passivation approaches. In addition, analysis of MOS structures allows some understanding of the fundamental behavior of the high-k/III-V system in the absence of any complicating effects on device performance that are introduced during the multiple processing steps inherent in a MOSFET fabrication

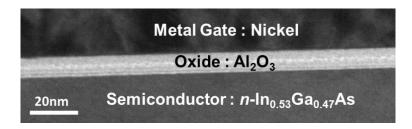

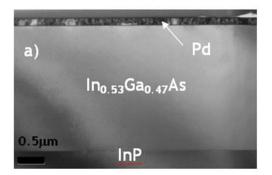

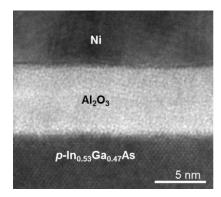

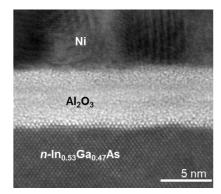

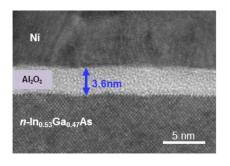

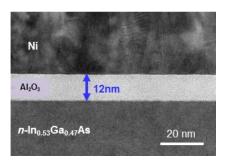

Figure 1.7 Transmission Electron Spectroscopy (TEM) image of a Ni/Al<sub>2</sub>O<sub>3</sub>/*n*-In<sub>0.53</sub>Ga<sub>0.47</sub>As, Metal-Oxide-Semiconductor (MOS) structure, typical of that explored in this thesis.

flow. Obviously it is important that the results obtained on MOS devices be relevant in a wider context. An MOS stack is at the heart of a traditional MOSFET device so therefore improvements observed for MOS devices should ideally be transferable to related MOSFET devices. A cross sectional transmission electron microscopy (TEM) image of a typical gate stack structure examined in this thesis is shown in Figure 1.7.

In Chapter 2 some basic theory is presented to provide an overview of the electrical characteristics expected for a MOS system. This encompasses the responses for an ideal system, and also a description of the effect of various defects and oxide charges on device electrical characteristics. An emphasis is placed on the non-idealities and electrical characterization methods most relevant to the discussion of the experimental MOS devices in the subsequent chapters of the thesis.

In the first experimental chapter of the thesis [Chapter 3], the effect of varying the % indium composition in the In<sub>x</sub>Ga<sub>1-x</sub>As (x: 0, 0.15, 0.30, 0.53) semiconductor epitaxial layer was investigated. From a technological perspective there is an interest to examine In<sub>x</sub>Ga<sub>1-x</sub>As channels with varying indium concentrations, as a higher indium concentration increases the electron mobility, however, it also reduces the band gap, which can increase off-state currents. From a scientific perspective, how D<sub>it</sub> values change with the indium percentage is also of interest, as it is possible that certain interface defects will move out of the In<sub>x</sub>Ga<sub>1-x</sub>As energy gap with increasing indium content. For the samples in this study, HfO<sub>2</sub> films served as the high-*k* gate oxide. Devices were characterized over a wide temperature range, 77K to 295K, to examine the influence of interface defects on the electrical response of the MOS

devices as the bandgap varies with % indium content. Additionally, the effect of forming gas annealing on defect densities at the  $HfO_2/In_{0.53}Ga_{0.47}As$  interface was examined.

The experimental results and analysis in Chapter 3, indicated that with ALD based high-k oxide deposition it was only possible to achieve a genuine surface accumulation in n-In $_x$ Ga $_{1-x}$ As MOS with 53% indium, and as a consequence the remainder of the thesis work focused primarily on utilizing In $_{0.53}$ Ga $_{0.47}$ As as a semiconductor layer. A common passivation technique used for III-V surfaces is immersion in an ammonium sulfide solution, and a study was performed to investigate the effect of varying the passivation parameters [Chapter 4]. Various concentrations of (NH $_4$ ) $_2$ S were used and the optimum condition was assessed based on the electrical and physical characteristics of the devices. In addition a comparison was performed of the Conductance Method and the High-Low Capacitance Voltage Method to compare the D $_{it}$  extracted using the two approaches.

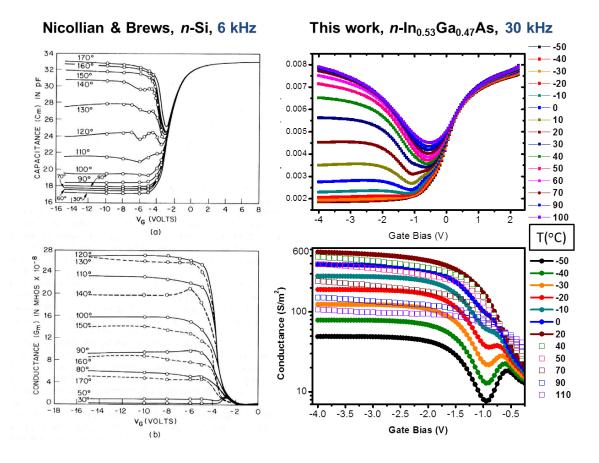

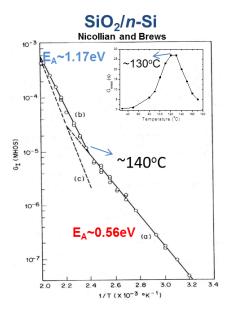

Further optimization of the passivation technique was used to fabricate MOS devices, again incorporating  $Al_2O_3$  on  $In_{0.53}Ga_{0.47}As$ , where  $D_{it}$  values were reduced to levels allowing genuine surface inversion to be achieved in both n and p type  $In_{0.53}Ga_{0.47}As/Al_2O_3$  MOS. Techniques developed by Nicollian and Brews  $^{50}$  were used to analyze the signatures of, and mechanisms for, the minority carrier response observed over n-type and p-type substrates in inversion [Chapter 5]. In addition the effect of the  $In_{0.53}Ga_{0.47}As$  epitaxial doping concentration on the inversion responses was studied through use of n- and p-type  $In_{0.53}Ga_{0.47}As$  with doping concentrations varying over two orders of magnitude.

In Chapter 6 the analysis of the  $In_{0.53}Ga_{0.47}As/Al_2O_3$  MOS inversion response was extended on the basis of an experimental observation indicating a unique relationship between the capacitance and conductance in strong inversion [Chapter 6]. This chapter also indicates how these new observations can have a practical application to the extraction of the oxide capacitance ( $C_{ox}$ ), which can be particularly challenging in the case of  $In_{0.53}Ga_{0.47}As$  based MOS structures. The effect of  $t_{ox}$  and FGA on the

minority carrier responses was also studied. Finally, the main findings of the thesis are summarized with some suggestions on possible future work [Chapter 7].

<sup>1</sup> G. E. Moore, *Electronics*, **38**, (8), p 114, (1965).

<sup>&</sup>lt;sup>2</sup> R. H. Dennard, F. H. Gaensslen, V. L. Rideout, E. Bassous, and A. R. LeBlanc, *IEEE JSSC*, **9**, (5), p. 256, (1974).

<sup>&</sup>lt;sup>3</sup> J. A. del Alamo, *Nature*, **479**, p317, (2011).

<sup>&</sup>lt;sup>4</sup> K. Kuhn, *Proceedings of 13<sup>th</sup> International Workshop on Computational Electronics*, *IEEE*, (2009).

<sup>&</sup>lt;sup>5</sup> G. D. Wilk, R. M. Wallace, and J. Anthony, J. App. Phys, **89**, (10), 5243, (2001).

<sup>&</sup>lt;sup>6</sup> J. Robertson, *Comprehensive Semiconductor Science and Technology*, 4, p 132-176, (2011).

<sup>&</sup>lt;sup>7</sup> M. M. Frank, *Proceedings of ESSDERC 2011*, p25-33, (2011).

<sup>&</sup>lt;sup>8</sup> http://www.intel.com/pressroom/kits/45nm/photos.htm

<sup>&</sup>lt;sup>9</sup> I. Thayne, S. Bentley, M. Holland, W. Jansen, X. Li, D. Macintyre, S. Thoms, B. Shin, J. Ahn, and P. McIntyre, *Microelec. Eng.*, **88**, 1070–1075, (2011).

<sup>&</sup>lt;sup>10</sup> http://www.itrs.net , International Technology Roadmap for Semiconductors.

<sup>&</sup>lt;sup>11</sup> R. M. Wallace, P. C. McIntyre, J. Kim, and Y. Nishi, *MRS Bulletin*, **34**, p 493 (2009).

<sup>&</sup>lt;sup>12</sup> A. Callegari, P. D. Hoh, D.A. Buchanan, and D. Lacey, *Appl. Phys Lett.*, **54**, 332 (1989).

<sup>&</sup>lt;sup>13</sup> M. Passlack, M.Hong and J.P. Mannaertz, *Appl. Phys. Lett.*, **68**, 1099 (1996).

<sup>&</sup>lt;sup>14</sup> J. P. de Souza, E. Kiewra, Y. Sun, A. Callegari, D. K. Sadana, G. Shahidi, D. J. Webb, J. Fompeyrine, R. Germann, C. Rossel, and C. Marchiori, *Appl. Phys. Lett.*, **92**, 153508 (2008).

<sup>&</sup>lt;sup>15</sup> C. L. Hinkle, M. Milojevic, B. Brennan, A. M. Sonnet, F. S. Aguirre-Tostado, G. J. Hughes, E. M. Vogel, and R. M. Wallace, *Appl. Phys. Lett.*, **94**, 162101 (2009).

<sup>&</sup>lt;sup>16</sup> I.G. Thayne, R.J.W. Hill, M.C. Holland, X. Li, H.Zhou, D.S. Macintyre, S. Thoms, K. Kalna, C.R. Stanley, A. Asenov, R.Droopad, and M. Passlack, *ECS Trans.*, **19** (5) p275-286 (2009).

<sup>17</sup> B. Shin, D. Choi, J. S. Harris, and P. C. McIntyre, *Appl. Phys. Lett.*, **93**, 052911 (2008).

- <sup>18</sup> B. Shin, J. Cagnon, R. D. Long, P. K. Hurley, S. Stemmer, and Paul C. McIntyre, *Electrochem. Sol.-State Lett.*, **12**, 8, G40-G43 (2009).

- <sup>19</sup> Y. Sun, P. Pianetta, P.-T. Chen, M. Kobayashi, Y. Nishi, N. Goel, M. Garner, and W. Tsai, *Appl. Phys. Lett.*, **93**, 194103 (2008).

- <sup>20</sup> H.-C. Lin, W.-E. Wang, G. Brammertz, M. Meuris, M. Heyns, *Microelec. Eng.*, **86**, 1554–1557, (2009).

- <sup>21</sup> G. Brammertz, H. C. Lin, K. Martens, A. Alian, C. Merckling, J. Penaud, D. Kohen, W.-E Wang, S. Sioncke, A. Delabie, M. Meuris, M. Caymax, M. Heyns. *ECS Trans.*, **19**, (5) 375-386 (2009).

- <sup>22</sup> N. Goel, P. Majhi, C. O. Chui, W. Tsai, D. Choi, and J. S. Harris, *Appl. Phys. Lett.*, **89**, 163517, (2006).

- <sup>23</sup> E. O'Connor, R.D. Long, K. Cherkaoui, K.K. Thomas, F. Chalvet, I.M. Povey, M.E. Pemble, P.K. Hurley, B. Brennan, G. Hughes, S.B. Newcomb, *Appl. Phys. Lett.* **92**, 022902, (2008).

- <sup>24</sup> S. Oktyabrsky, V. Tokranov, M. Yakimov, R. Moore, S. Koveshnikov, W. Tsai, F. Zhuc, J.C. Lee, *Mat. Sci Eng. B*, **135**, p 272-276, (2006).

- <sup>25</sup> M. El Kazzi, L. Czornomaz, C. Rossel, C. Gerl, D. Caimi, H. Siegwart, J. Fompeyrine, and C. Marchiori, *Appl. Phys. Lett.*, **100**, 063505 (2012).

- <sup>26</sup> C. Marchiori, M. El Kazzi, L. Czornomaz, D. Pierucci, M. Silly, F. Sirotti, S. Abel, E. Uccelli, M. Sousa, and J. Fompeyrine, *J. Phys D: Appl. Phys.*, **47**, 055101, (2014).

- <sup>27</sup> H. Zhao, Y-T Chen, J. H. Yum, Y. Wang, N. Goel, and J. C. Lee, *App. Phys. Lett.*, **94**, 193502, (2009).

- <sup>28</sup> M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, *IEDM Tech. Dig.*, p. 319–322,(2009).

- <sup>29</sup> N. Goel, P. Majhi, W. Tsai, M. Warusawithana, D. G. Schlom, M. B. Santos, J. S. Harris, and Y. Nishi, *Appl. Phys. Lett.*, **91**, 093509 (2007).

<sup>30</sup> E. J. Kim, E. Chagarov, J. Cagnon, Y. Yuan, A. C. Kummel, P. M. Asbeck, S. Stemmer, K. C. Saraswat, and P. C. McIntyre, *J. Appl. Phys.*, **106**, 124508 (2009)

- <sup>31</sup> Y. Hwang, R. E.-Herbert, N. G. Rudawski, and S. Stemmer, *J. Appl. Phys.*, **108**, 034111 (2010).

- <sup>32</sup> I. Krylov, A. Gavrilov, D. Ritter, and M. Eizenberg, *Appl. Phys. Lett.*, **99**, 203504 (2011).

- <sup>33</sup> E. O'Connor, V. Djara, S. Monaghan, P. K. Hurley, and K. Cherkaoui, *ECS Trans.*, **35** (3), 415-430 (2011).

- <sup>34</sup> G. W. Paterson, M. C. Holland, S. J. Bentley, I. G. Thayne, and A. R. Long, *J. Appl. Phys.*, **109**, 124112 (2011).

- <sup>35</sup> P. F. Zhang, R. E. Nagle, N. Deepak, I. M. Povey, Y. Y. Gomeniuk, E. O'Connor, N. Petkov, M. Schmidt, T. P. O'Regan, K. Cherkaoui, M. E. Pemble, P.K. Hurley, R. Whatmore, *Microelec. Eng.*, **88**, (7), 1054-1057 (2011).

- <sup>36</sup> P. D. Ye, G. D. Wilk, B. Yang. J. Kwo, S. N. G. Chu, S. Nakahara, H.-J. L. Gossmann, J. P. Mannaerts, M. Hong, K. K. Ng, and J. Bude, *Appl. Phys. Lett.* **83**, 180 (2003).

- <sup>37</sup> M. M. Frank, G. D. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y. J. Chabal, J. Grazul and D. A. Miller, *Appl. Phys. Lett.* **86**, 152904, (2005).

- <sup>38</sup> C. L. Hinkle, A. M. Sonnet, E. M. Vogel, S. McDonnell, G. J. Hughes, M. Milojevic, B. Lee, F. S. Aguirre-Tostado, K. J. Choi, H. C. Kim, J. Kim and R. M. Wallace, *Appl. Phys. Lett.* **92**, 071901 (2008).

- <sup>39</sup> M. M. Frank, Y. Zhu, S. W. Bedell, T. Ando, and V. Narayanan, *ECS Transactions*, **61**, p 213-223 (2014).

- <sup>40</sup> A. O'Mahony, S. Monaghan, G. Provenzano, I. M. Povey, M. G. Nolan, E. O'Connor, K. Cherkaoui, S. B. Newcomb, F. Crupi, P. K. Hurley, M. E. Pemble, *App. Phys. Lett.*, **97**, 052904 (2010).

- <sup>41</sup> R. Suzuki, N. Taoka, M. Yokoyama, S. Lee, S. H. Kim, T. Hoshii, T. Yasuda, W. Jevasuwan, T. Maeda, O.Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, *Appl. Phys. Lett.*, **100**, 132906 (2012).

<sup>42</sup> M. Heyns *et al*, *IEDM Tech. Digest*, p 13.1.1, (2011).

- <sup>44</sup> L. Czornomaz, N. Daix, K. Cheng, D. Caimi, C. Rossel, K. Lister, M Sousa, and J. Fompeyrine, *Proc. of IEDM*, p 2.8.1 2.8.4, (2012).

- <sup>45</sup> K. Kuhn, U. Avci, A. Cappellani, M. Giles, M. Haverty, S. Kim, R. Kotlyar, S. Manipatruni, D. Nikonov, C. Pawashe, M. Radosavljevic, R. Rios, S. Shankar, R. Vedula, R. Chau, and I. Young, *IEDM 2012*, p. 8.1.1 (2012).

- <sup>46</sup> K. Kuhn, *IEEE Trans. Elec. Dev.*, **59**, 7, (2012).

- <sup>47</sup> X. Zhang, H. X. Guo, Z. Zhu, X. Gong, Y.-C. Yeo, *Sol.-State Electronics*, **84**, p 83–89, (2013).

- <sup>48</sup> N. Waldron *et al*, *IEEE 2014 Symposium on VLSI Technology Digest of Technical Papers*, (2014).

- <sup>49</sup> http://www.intel.com/content/www/us/en/silicon-innovations/intel-22nm-technology.html

- <sup>50</sup> E. H. Nicollian and J. R. Brews, Page **331**, *MOS Physics and Technology*, New York, Wiley, (1982).

<sup>&</sup>lt;sup>43</sup> M. Yokohama, H. Takagi, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, and S. Takagi, *Appl. Phys. Express* **4**, 054202 (2011).

# Chapter 2

2. Charged defect components in the MOS system: Influence on the capacitance-voltage and conductance-voltage response, and methods for defect density quantification

#### 2.1. Introduction