| Title                       | An investigation of capacitance-voltage hysteresis in metal/high-k/In0.53Ga0.47As metal-oxide-semiconductor capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Authors                     | Lin, Jun;Gomeniuk, Yuri Y.;Monaghan, Scott;Povey, Ian<br>M.;Cherkaoui, Karim;O'Connor, Éamon;Power, Maire;Hurley, Paul<br>K.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Publication date            | 2013                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Original Citation           | Lin, J., Gomeniuk, Y. Y., Monaghan, S., Povey, I. M., Cherkaoui, K., O'Connor, É., Power, M. and Hurley, P. K. (2013) 'An investigation of capacitance-voltage hysteresis in metal/high-k/In0.53Ga0.47As metal-oxide-semiconductor capacitors', Journal of Applied Physics, 114(14), 144105 (7pp). doi: 10.1063/1.4824066                                                                                                                                                                                                                                                                  |  |  |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Link to publisher's version | http://aip.scitation.org/doi/10.1063/1.4824066 - 10.1063/1.4824066                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Rights                      | © 2013, AIP Publishing LLC. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in Lin, J., Gomeniuk, Y. Y., Monaghan, S., Povey, I. M., Cherkaoui, K., O'Connor, É., Power, M. and Hurley, P. K. (2013) 'An investigation of capacitance-voltage hysteresis in metal/high-k/In0.53Ga0.47As metal-oxide-semiconductor capacitors', Journal of Applied Physics, 114(14), 144105 (7pp). doi: 10.1063/1.4824066 and may be found at http://aip.scitation.org/doi/10.1063/1.4824066 |  |  |

| Download date               | 2025-09-06 00:49:11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Item downloaded from        | https://hdl.handle.net/10468/4723                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

# An investigation of capacitance-voltage hysteresis in metal/high-k/ln $_{0.53}$ Ga $_{0.47}$ As metal-oxide-semiconductor capacitors

Jun Lin, Yuri Y. Gomeniuk, Scott Monaghan, Ian M. Povey, Karim Cherkaoui, Éamon O'Connor, Máire Power, and Paul K. Hurley

Citation: Journal of Applied Physics 114, 144105 (2013); doi: 10.1063/1.4824066

View online: http://dx.doi.org/10.1063/1.4824066

View Table of Contents: http://aip.scitation.org/toc/jap/114/14

Published by the American Institute of Physics

## Articles you may be interested in

Inversion in the  $In_{0.53}Ga_{0.47}As$  metal-oxide-semiconductor system: Impact of the  $In_{0.53}Ga_{0.47}As$  doping concentration

Applied Physics Letters 110, 032902 (2017); 10.1063/1.4973971

$1-nm\text{-}capacitance\text{-}equivalent\text{-}thickness HfO}_2/\text{Al}_2\text{O}_3/\text{InGaAs metal-oxide-semiconductor structure with low interface trap density and low gate leakage current density}$

Applied Physics Letters 100, 132906 (2012); 10.1063/1.3698095

Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces Journal of Applied Physics **108**, 124101 (2010); 10.1063/1.3520431

Effects of oxide traps, interface traps, and "border traps" on metal-oxide-semiconductor devices Journal of Applied Physics **73**, 5058 (1998); 10.1063/1.353777

Border traps in  $Al_2O_3/In_{0.53}Ga_{0.47}As$  (100) gate stacks and their passivation by hydrogen anneals Applied Physics Letters **96**, 012906 (2010); 10.1063/1.3281027

Temperature and frequency dependent electrical characterization of  $HfO_2/In_xGa_{1-x}As$  interfaces using capacitance-voltage and conductance methods

Applied Physics Letters 94, 102902 (2009); 10.1063/1.3089688

## An investigation of capacitance-voltage hysteresis in metal/high-k/ln<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor capacitors

Jun Lin, <sup>1</sup> Yuri Y. Gomeniuk, <sup>1,2</sup> Scott Monaghan, <sup>1</sup> Ian M. Povey, <sup>1</sup> Karim Cherkaoui, <sup>1</sup> Éamon O'Connor, <sup>1</sup> Máire Power, <sup>1</sup> and Paul K. Hurley <sup>1</sup>

<sup>1</sup>Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland <sup>2</sup>Lashkaryov Institute of Semiconductor Physics, 41 Prospect Nauki, 03028 Kiev, Ukraine

(Received 24 May 2013; accepted 16 September 2013; published online 11 October 2013)

In this work, we present the results of an investigation into charge trapping in metal/high-k/In<sub>0.53</sub> Ga<sub>0.47</sub>As metal-oxide-semiconductor capacitors (MOS capacitors), which is analysed using the hysteresis exhibited in the capacitance-voltage (C-V) response. The availability of both n and pdoped In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial layers allows the investigation of both hole and electron trapping in the bulk of HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> films formed using atomic layer deposition (ALD). The HfO<sub>2</sub>/In<sub>0.53</sub> Ga<sub>0.47</sub>As and Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors exhibit an almost reversible trapping behaviour, where the density of trapped charge is of a similar level to high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface state density, for both electrons and holes in the HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> films. The experimental results demonstrate that the magnitude of the C-V hysteresis increases significantly for samples which have a native oxide layer present between the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface and the high-k oxide, suggesting that the charge trapping responsible for the C-V hysteresis is taking place primarily in the interfacial oxide transition layer between the In<sub>0.53</sub>Ga<sub>0.47</sub>As and the ALD deposited oxide. Analysis of samples with a range of oxide thickness values also demonstrates that the magnitude of the C-V hysteresis window increases linearly with the increasing oxide thickness, and the corresponding trapped charge density is not a function of the oxide thickness, providing further evidence that the charge trapping is predominantly localised as a line charge and taking place primarily in the interfacial oxide transition layer located between the In<sub>0.53</sub>Ga<sub>0.47</sub>As and the high-k oxide. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4824066]

#### I. INTRODUCTION

As the minimum feature size of silicon based Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) reaches the limits of dimensional scaling, there is a concerted research effort directed towards the use of alternative high mobility channel materials (e.g., Ge and III-V materials) and high dielectric constant (high-k) gate oxides in future MOSFETs. 1-6 The motivation for using high mobility channel materials and high-k gate oxides is for lower leakage, lower power consumption, and higher speed of operation for minimum channel lengths below 22 nm. However, there are a range of challenges associated with the integration of high mobility compound semiconductor channels into a MOSFET process, which include the integration of the high mobility materials onto a large area silicon platform, forming high-k gate oxide layers on the III-V substrate, and finding a suitable p channel device when using III-V materials for both the p and n channel MOSFET. Due to the combination of a high electron mobility ( $\sim$ 14 000 cm<sup>2</sup>/V s at low doping levels), suitable energy gap ( $\sim 0.75 \, \text{eV}$ ) and the fact that it can be grown lattice matched in InP, there has been a considerable focus of research attention on InGaAs with a 53% In concentration (i.e., In<sub>0.53</sub>Ga<sub>0.47</sub>As). The electrically active interface defects between the high-k gate oxide and the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface,  $^{7-16}$  and fixed charges within the high-k oxide,  $^{15-17}$ have been studied in some detail in the literature. Charge trapping states can also be located in the transition region between the high-k oxide and In<sub>0.53</sub>Ga<sub>0.47</sub>As surface and are often referred to a "slow states" or "border traps". These trapping sites have been examined based on the dispersion they cause in the capacitance with ac signal frequency for In<sub>0.53</sub>Ga<sub>0.47</sub> As MOS structures biased in accumulation. <sup>18–21</sup> However, this dispersion can also include fast interface states aligned with energy levels in the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band. 9,10,22 In addition to causing frequency dispersion in the measured capacitance, charge trapping sites located in the oxide can be manifest as hysteresis in the C-V response. The issue of C-V hysteresis in the In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system has received only a limited amount of research attention to date. 23,24 The issue of C-V hysteresis is important from a technological perspective as it represents a physical process that results in device instability, and in addition, the level of charge trapping can be comparable to, or greater than, the effect of interface states for the In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system.<sup>23</sup> From a scientific perspective, the study of C-V hysteresis is of interest as it presents a method to analyse and quantify the density of charge trapping states in high-k oxides on III-V surfaces.

The principal aim of this work is to investigate C-V hysteresis in the high- $k/In_{0.53}Ga_{0.47}As$  MOS system for different metal gate electrodes and varying experimental bias conditions in order to quantify the level of electron and hole trapping, and to gain a more complete understanding of the primary location of the charge trapping sites. The experimental results also provide insight into the approach that is required to reduce the density of charge trapping sites

responsible for the C-V hysteresis in the In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system.

#### II. EXPERIMENTAL DETAILS

The samples used in this work were heavily *n*-doped (S at  $\sim 2 \times 10^{18}$  cm<sup>-3</sup>) and heavily *p*-doped (Zn at  $\sim 2 \times 10^{18}$ cm<sup>-3</sup>) InP(100) substrates with  $2 \mu m n$ -type (S at  $\sim 4 \times 10^{17}$ cm<sup>-3</sup>) and p-type (Zn at  $\sim 4 \times 10^{17}$  cm<sup>-3</sup>) In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial layers, respectively, grown by metal organic vapour phase epitaxy (MOVPE). The In<sub>0.53</sub>Ga<sub>0.47</sub>As surfaces were initially degreased by sequentially rinsing for 1 min each in acetone, methanol, and isopropanol. Before the high-k oxide deposition, the samples were immersed in (NH<sub>4</sub>)<sub>2</sub>S solutions (10% in deionized H<sub>2</sub>O) for 20 min at room temperature ( $\sim$ 295 K). The 10% (NH<sub>4</sub>)<sub>2</sub>S passivation approach for 20 min and room temperature was found to be the optimum to suppress the formation of In<sub>0.53</sub>Ga<sub>0.47</sub>As native oxides and to reduce the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface state density as reported in Ref. 25. Samples were then introduced to the atomic layer deposition (ALD) chamber load lock (base pressure of less than  $2 \times 10^{-5}$  mbar) after the removal from the 10% (NH<sub>4</sub>)<sub>2</sub>S surface passivation solution. The transfer time from the aqueous (NH<sub>4</sub>)<sub>2</sub>S solution to the ALD chamber was kept to a minimum in order to minimise the formation of In<sub>0.53</sub>Ga<sub>0.47</sub>As native oxides due to air exposure.

Either HfO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> were deposited on the In<sub>0.53</sub>Ga<sub>0.47</sub> As by ALD. The HfO<sub>2</sub> dielectric has a nominal thickness of 5 nm by ALD using Hf[N(CH<sub>3</sub>)C<sub>2</sub>H<sub>5</sub>]<sub>4</sub> (TEMAH) and H<sub>2</sub>O as precursors at 250 °C. The Al<sub>2</sub>O<sub>3</sub> dielectric has a nominal thickness of 8 nm and was deposited by ALD at 300 °C using trimethylaluminum (TMA)  $Al(CH_3)_3$  and  $H_2O$ . For the Al<sub>2</sub>O<sub>3</sub> thickness series results presented in this work, the Al<sub>2</sub>O<sub>3</sub> dielectric with nominal thicknesses of 5, 10, 15, 20 nm were deposited by ALD at 250 °C using the same aluminium precursor and H<sub>2</sub>O. In this work, we examined samples with several metal gates representing low and high work functions, which included Al, Pt, Pd, and Ni/Au. Gate contacts were formed by electron beam evaporation and a lift-off process. Pt (115 nm) and Al (115 nm) were used as the two metal gates for HfO<sub>2</sub> (5 nm) samples, Al (160 nm) and Ni(70 nm)/Au(90 nm) were the two gates for Al<sub>2</sub>O<sub>3</sub> (8 nm) samples, and Pd (160 nm) was the metal gate for the Al<sub>2</sub>O<sub>3</sub> thickness series(5–20 nm). The full sample details are provided in Table I.

The C-V hysteresis measurements were recorded using a Cascade Microtech probe station (model Submmit 12971B) and an Agilent CV-enabled B1500A semiconductor device analyser. All the C-V hysteresis measurements were

carried out at a high frequency of 1MHz and at room temperature (295 K) in order to minimise the contribution of highk/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface states to the overall capacitance. Under these conditions, the primary effect of the interface states is to stretch out the measured high frequency C-V along the gate voltage axis. 26,27 All the reported C-V hysteresis responses were measured starting from inversion and sweeping towards the accumulation region, and subsequently sweeping back towards inversion. There was no hold time in accumulation. The terms "inversion" and "accumulation" used here are for simplicity of expression to represent the nominal regions of the C-V characteristic. To confirm surface inversion would require more analysis, but this is beyond the scope and intention of this work. The MOS capacitors under investigation were all driven beyond the flatband condition and towards accumulation region which allows charge to be accumulated at the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface. The C-V hysteresis (i.e., the gate voltage difference between the double-directional sweeps) is estimated at either the flat-band capacitance (Cfb) or half the maximum capacitance in accumulation (C<sub>max</sub>/2). The level of charge trapping is quantified using the following equation:

$$Q_{trapped} = \frac{C_{ox} \times \Delta V}{q} (\text{cm}^{-2}), \tag{1}$$

where Q<sub>trapped</sub> is the population of trapped charge in cm<sup>-2</sup>,  $\Delta V$  is the C-V hysteresis in V,  $C_{ox}$  is the oxide capacitance in F/cm<sup>2</sup> (proportional to the oxide k-value and inversely proportional to the oxide thickness), and q is the elementary charge in C. The value of Q<sub>trapped</sub> in Eq. (1) represents the equivalent charge density at the oxide/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. Multiple sites with different capacitor areas were examined to ensure the C-V hysteresis results are representative of the sample behaviour. The effect of different oxide electric fields due to small variations in oxide thickness has been neglected. The C<sub>ox</sub> values are based on oxide thickness values obtained from high-resolution cross-sectional transmission electron microscopy (HR-TEM), taking into account any interfacial oxide layers formed in the MOS structure. The following dielectric constant values were adopted, HfO<sub>2</sub> (21),<sup>28</sup> Al<sub>2</sub>O<sub>3</sub> (8.6),<sup>23</sup> and the native oxide of  $In_{0.53}Ga_{0.47}As$  (9).<sup>29,30</sup>

#### III. RESULTS AND DISCUSSIONS

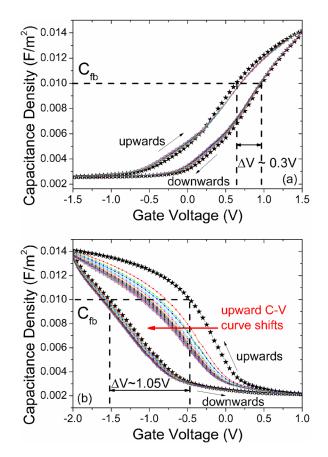

Twenty C-V hysteresis sweeps for n-type and p-type Pt/HfO<sub>2</sub>(5 nm)/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors are shown in Figures 1(a) and 1(b), respectively. The flat-band voltage (V<sub>fb</sub>) difference estimated from the first C-V hysteresis

TABLE I. Sample details.

| Sample                                                                                          | Gate (thickness)                 | Oxide (thickness)                                  | ALD precursors           | ALD temperatures |

|-------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------|--------------------------|------------------|

| HfO <sub>2</sub> /(n and p)In <sub>0.53</sub> Ga <sub>0.47</sub> As sample series               | Pt (115 nm)<br>Al (115 nm)       | HfO <sub>2</sub> (5 nm)<br>HfO <sub>2</sub> (5 nm) | TEMAH and $H_2O$         | 250 °C<br>250 °C |

| Al <sub>2</sub> O <sub>3</sub> /(n and p)In <sub>0.53</sub> Ga <sub>0.47</sub> As sample series | Ni/Au(70 nm/90nm)<br>Al (160 nm) | $Al_2O_3(8 \text{ nm})$ $Al_2O_3(8 \text{ nm})$    | TMA and ${\rm H_2O}$     | 300 °C<br>300 °C |

| $Al_2O_3$ /(n and p) $In_{0.53}Ga_{0.47}As$ oxide thickness series                              | Pd (160 nm)                      | Al <sub>2</sub> O <sub>3</sub> (5, 10, 15, 20 nm)  | TMA and H <sub>2</sub> O | 250°C            |

FIG. 1. Twenty C-V hysteresis responses at 1 MHz and 295 K for (a) Pt/HfO<sub>2</sub>(5 nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As/n-InP and (b) Pt/HfO<sub>2</sub>(5 nm)/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As/p-InP MOS capacitors. A progressive gate voltage shift occurring with subsequent C-V sweeps is evident in the upward sweep direction in (b). Note: the curve with black star symbols is the 1st C-V hysteresis sweep.

sweep, which is shown in black stars in Figure 1, corresponds to an electron trapping level of  $4.7 \times 10^{12} \text{ cm}^{-2}$  for the *n*-type sample, and a hole trapping level of  $1.6 \times 10^{13}$  cm<sup>-2</sup> for the p-type sample, assuming all the charge trapping is taking place at the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. The validity of this assumption will be explored later in the paper. The density calculations are based on an oxide capacitance value  $C_{ox} = 2.5 \times 10^{-6} \text{ F/cm}^2$  taking into consideration the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface oxide thickness observed in the TEM micrographs which will be presented and discussed later. Both the electron and hole trapping levels are comparable to the estimated interface state density (Dit) using the approach described in Ref. 15, highlighting the importance of electron and hole trapping in the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system. Considering first the *n*-type  $In_{0.53}Ga_{0.47}As$  sample in Figure 1(a), the repeated C-V hysteresis sweeps are almost overlapping the 1st C-V hysteresis in the upward sweep direction, where the MOS capacitor is measured from inversion to accumulation, indicating that the majority of charge trapping is a reversible process (or a temporary trapping behaviour). In the p-type  $In_{0.53}Ga_{0.47}As$  sample (Figure 1(b)), there is a significant shift in V<sub>fb</sub> between the 1st and 2nd C-V hysteresis sweeps, but subsequent sweeps show the same behaviour as the *n*-type sample, where the majority of the charge trapping is a reversible process. There is only a small non-reversible component referred to here as permanent charge trapping, which is manifested as a progressive shift in  $V_{fb}$  in the inversion to accumulation sweeps of the C-V responses, which is a positive  $V_{fb}$  shift for the n-type sample and a negative  $V_{fb}$  shift for the p-type sample. From Figure 1, it is clear that the progressive  $V_{fb}$  shift is more significant in the p-type sample, implying a larger portion of permanently trapped charges in the p-type sample compared to that in the n-type sample.

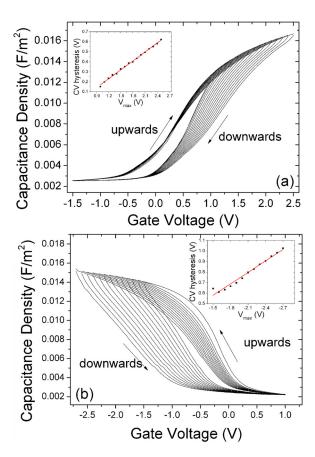

Figure 2 illustrates the effect of the maximum bias in accumulation on the level of C-V hysteresis. For these measurements, the same starting DC bias point in inversion is used, with an increasing maximum DC bias point in accumulation ( $V_{max}$ ) for the Pt/HfO<sub>2</sub>(5 nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As (Figure 2(a)) and Pt/HfO<sub>2</sub>(5 nm)/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As (Figure 2(b)) MOS capacitors. As shown in the insets of the figures, the C-V hysteresis window increases linearly with V<sub>max</sub>. The C-V hysteresis is also found to increase with V<sub>max</sub> for the Al<sub>2</sub>O<sub>3</sub>(8 nm)/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures, but the level of increase is less than observed for the HfO2 structures (results not shown). It has recently been demonstrated that SiO<sub>2</sub> doped HfO<sub>2</sub> (Ref. 31) and ZrHfO<sub>2</sub> thin films on silicon<sup>32</sup> exhibit a ferroelectric behaviour. The C-V results in Figures 2(a) and 2(b) obtained for the undoped HfO<sub>2</sub> are not consistent with a ferroelectric response, suggesting electron and hole trapping as the source of the C-V hysteresis. The origin of the linear increase of the C-V hysteresis window with the V<sub>max</sub> is the subject of further studies.

FIG. 2. C-V hysteresis at 1 MHz and 295 K for (a) Pt/HfO<sub>2</sub>(5 nm)/n-In<sub>0.53</sub> Ga<sub>0.47</sub>As and (b) Pt/HfO<sub>2</sub>(5 nm)/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors using the same start DC bias in inversion and increasing DC bias (V<sub>max</sub>) in accumulation. Inset is the C-V hysteresis as a function of V<sub>max</sub>.

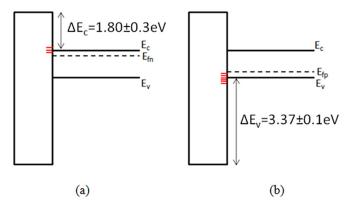

From Figure 2, which has a range of maximum bias values in accumulation, it is possible to compare the level of charge trapping in the *n*- and *p*-type  $In_{0.53}Ga_{0.47}As$  samples at the same maximum electric field across the oxide (i.e., the same  $|V_{max}-V_{fb}|$ ). It is important to have the same  $|V_{max}-V_{fb}|$ for the two samples so that same amount of majority carriers are accumulated at the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface which makes the comparison valid. For example, if  $|V_{max}-V_{fb}|$  is taken as 1.4 V, the trapped charge density is  $7.3 \times 10^{12}$  cm<sup>-2</sup> for the  $n\text{-In}_{0.53}\text{Ga}_{0.47}\text{As}$  sample and  $1.3 \times 10^{13} \, \text{cm}^{-2}$  for the p-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS sample. This indicates that there is a significantly lower level of charge trapping in the case of the n-type In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitor than in the case of p-In<sub>0.53</sub>Ga<sub>0.47</sub>As. There are a range of possible factors which can contribute to the higher level of temporary charge trapping (i.e., C-V hysteresis) and permanent charge trapping in the p-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures, which are illustrated schematically by the energy band diagrams shown in Figures 3(a) and 3(b) for the *n*-type and *p*-type samples, respectively. The possible reasons for a higher level of charge trapping in the p-type sample compared to the n-type sample are: (i) a higher density of border traps with energy levels aligned with the In<sub>0.53</sub>Ga<sub>0.47</sub>As valance band edge than that aligned with the conduction band edge, (ii) the barrier height  $\Delta E_v$  for the trapped holes to be removed from the border traps is larger than the barrier height  $\Delta E_c$  for the trapped electrons.<sup>33</sup>

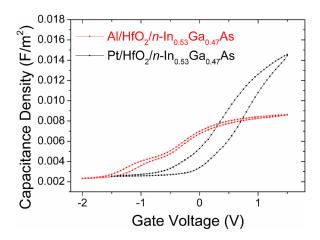

The study of the C-V hysteresis also included an examination of the impact of the metal gate based on low (i.e., aluminium) and high (i.e., platinum) work function metals, as detailed in Table I. Figure 4 shows the C-V hysteresis for the Pt/HfO<sub>2</sub>(5 nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As and Al/HfO<sub>2</sub>(5 nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors. The Al gate sample is driven into strong accumulation as the measured capacitance is plateauing at 1.5 V, and the value of  $|V_{max}$ -V<sub>fb</sub>| is higher for the Al gate samples than the Pt gate sample. Under this condition, the C-V responses exhibit three features of importance. First, the maximum capacitance in accumulation for the Al gate sample is almost half of that obtained for the Pt gate sample. Second, the level of charge trapping determined from the C-V hysteresis at the flat-band capacitance for the Al gate sample, of  $\sim$ 6.8  $\times$  10<sup>11</sup> cm<sup>-2</sup>, is significantly lower when

FIG. 3. Band diagrams for (a)  $HfO_2/n$ - $In_{0.53}Ga_{0.47}As$  and (b)  $HfO_2/p$ - $In_{0.53}Ga_{0.47}As$  structures.<sup>33</sup> The energy levels shown in red are the border trap energy levels which are aligned with the conduction band edge ( $E_c$ ) for the n-type sample and aligned with the valance band edge ( $E_v$ ) for the p-type sample.

FIG. 4. C-V hysteresis at 1 MHz and 295 K for Pt/HfO<sub>2</sub>(5 nm)/n-In<sub>0.53</sub> Ga<sub>0.47</sub>As and Al/HfO<sub>2</sub>(5 nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors. There is a significant reduction in the maximum capacitance for the Al gate sample in accumulation and a considerable reduction in  $Q_{trapped}$  (C-V hysteresis) in comparison to the Pt gate sample.

compared to  ${\sim}4.7\times10^{12}~cm^{-2}$  for the Pt gate sample. In addition, the reduced charge trapping for the Al gate sample occurs even with a higher value of  $|V_{max}\text{-}V_{fb}|$ . Finally, the samples exhibit a low level of frequency dispersion (<3.5%/decade) in the region corresponding to nominal accumulation (V $_g$  > 1.0 V) (not shown). In addition, the capacitance in this bias region does not significantly change when reducing the temperature to  $-50\,^{\circ}\text{C}$  (not shown). These results suggest the samples exhibit genuine surface accumulation.  $^{11}$

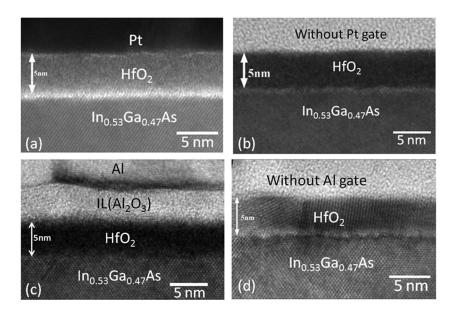

Further insight into the differences between the Al and Pt gate HfO<sub>2</sub>(5 nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS C-V responses can be obtained from the microstructure of the samples as indicated by TEM images for both samples, as shown in Figures 5(a)-5(d). The Pt gate sample exhibits an interface oxide of  $\sim 1 \text{ nm}$  between HfO<sub>2</sub> and the In<sub>0.53</sub>Ga<sub>0.47</sub>As. Previous analysis has indicated that this layer is the native oxide of In<sub>0.53</sub>Ga<sub>0.47</sub>As and predominantly comprised of a Ga oxide. 12 In Figure 4, the maximum capacitance of the Pt gate sample at  $+1.5 \,\mathrm{V}$  is  $\sim 0.0146 \,\mathrm{F/m^2}$ . The oxide capacitance associated with 5 nm of HfO<sub>2</sub> (k=21) is C<sub>ox</sub>  $= 0.037 \,\mathrm{F/m^2}$ . Even if the Pt gate  $\mathrm{HfO_2/n\text{-}In_{0.53}Ga_{0.47}As}$ MOS sample is driven further into accumulation, it is clear that the experimental capacitance will not acquire the C<sub>ox</sub> value associated with a 5 nm HfO<sub>2</sub> layer alone. This observation also points to a formation of interface oxide with a much lower k-value that is responsible for the reduction in  $C_{ox}$ . As observed from Figures 5(a) and 5(b), this interface oxide layer is present both in the areas under the Pt gate and in the areas outside the Pt gate. The same interfacial oxide is present for the Al gate sample in the area outside the Al gate (see Figure 5(d)). However, the TEM for the Al gate sample taken in the region where the Al gate is present shows that the electron-beam evaporated Al gate results in marked changes in the micro-structure of the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stack. First, a layer of Al<sub>2</sub>O<sub>3</sub> of ~5 nm in thickness is formed between the Al gate and HfO<sub>2</sub>, adding an extra capacitance in series with the total capacitance of the MOS capacitor and thus reducing the maximum capacitance for the

FIG. 5. TEM micrographs for Pt/HfO<sub>2</sub>  $(5 \text{ nm})/n\text{-In}_{0.53}\text{Ga}_{0.47}\text{As MOS}$  capacitor in the area (a) under the Pt gate and (b) outside the Pt gate, and for Al/HfO<sub>2</sub>  $(5 \text{ nm})/n\text{-In}_{0.53}\text{Ga}_{0.47}\text{As MOS}$  capacitor in the area (c) under the Al gate and (d) outside the Al gate. Note in (c) the thick interface layer (IL) formed between Al and HfO<sub>2</sub> and the removal of the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface oxide.

Al gate sample, as observed in Figure 4. It is noted that a similar Al/HfO2 interface layer was also observed in Al/HfO<sub>2</sub>/Ge MOS structures, as reported in Ref. 34. Second, the presence of the Al gate "scavenges" the In<sub>0.53</sub>Ga<sub>0.47</sub>As interfacial oxide layer and the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface oxide is almost gone in the region under the Al gate. This scavenging effect is similar to the effect reported for HfO2 on silicon MOS structures with a Ti gate,<sup>35</sup> but it is noted that for the samples presented in this work (Figure 5(c)) the scavenging on the interface oxide layer has occurred during a room temperature Al deposition without any subsequent thermal annealing. The removal of the native oxide interface layer also has a marked effect on the level of charge trapping, which is estimated from C-V hysteresis at the flat-band capacitance, and is approximately an order of magnitude lower for the Al gate sample than the Pt gate sample even though the Al gate sample is driven further into accumulation. This observation provides strong evidence that the charge trapping responsible for the observed C-V hysteresis is taking place predominantly at the interfacial transition layer between the high-k oxide and In<sub>0.53</sub>Ga<sub>0.47</sub>As, which can contain native oxides of Ga, In, and As substrate elements. 12

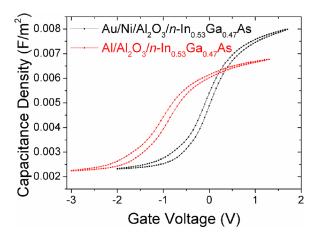

Figure 6 illustrates the C-V hysteresis for Al<sub>2</sub>O<sub>3</sub> (8 nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors using either Ni/Au or Al as metal gates. Due to the reported "self-cleaning" effect of the ALD process to form the Al<sub>2</sub>O<sub>3</sub>, removal of the interfacial oxide between the  $Al_2O_3$  and  $In_{0.53}Ga_{0.47}As$  is possible, with improved electrical performance as a result. 30,36-39 The charge trapping level estimated for Al<sub>2</sub>O<sub>3</sub> (8 nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors with no Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface layer, using either high (Ni/Au) or low (Al) work function gates is of a level which is around one order of magnitude lower than the typical interface state density in high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system. Table II summaries the charge trapping levels calculated from the C-V hysteresis at flat-band capacitance in Figures 4 and 6 for the case of samples with and without a native oxide interface transition layer between the high-k oxide and the In<sub>0.53</sub>Ga<sub>0.47</sub>As. This provides further evidence that the charge trapping phenomenon originates from the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As interfacial transition layer, indicating that engineering of the interface transition region is the key to reducing C-V hysteresis in metal/high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS systems. In addition, the maximum capacitance for Al/Al<sub>2</sub> O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors is slightly lower than the Au/Ni/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors. This is possibly due to the formation of a thin, self-limiting interface layer of Al<sub>2</sub>O<sub>3</sub> formed between the Al gate and Al<sub>2</sub>O<sub>3</sub>, which is similar to what is observed in Al/HfO<sub>2</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structure with a formation of Al<sub>2</sub>O<sub>3</sub> between Al and HfO<sub>2</sub>. The Al/Al<sub>2</sub>O<sub>3</sub> interface layer increases the nominal high-k oxide thickness and thus reduces the oxide capacitance, further reducing the total measured capacitance in accumulation (C<sub>max</sub>). As in the case of the C-V in Figure 4, the dependence of the capacitance on temperature and ac signal frequency at

FIG. 6. C-V hysteresis at 1 MHz and 295 K for Au/Ni/Al $_2$ O $_3$ (8 nm)/n-In $_{0.53}$ Ga $_{0.47}$ As and Al/Al $_2$ O $_3$ (8 nm)/n-In $_{0.53}$ Ga $_{0.47}$ As MOS capacitors measured under the same electric field across the Al $_2$ O $_3$ . The charge trapping level of these two samples is relatively low, and comparable to the Al/HfO $_2$ /n-In $_{0.53}$ Ga $_{0.47}$ As sample where the interlayer oxide is scavenged by the Al gate. The difference between the two C $_{max}$  values indicates an Al $_2$ O $_3$  oxide thickness difference of no more than  $\sim$ 1.7 nm, probably a result of a reactive Al/Al $_2$ O $_3$  interface compared to a non-reactive Ni/Al $_2$ O $_3$  interface.

TABLE II. Summary of charge trapping for the C-V hysteresis shown in Figures 4 and 6.

| Sample                                                                           | $Q_{trapped}$                          | High-k/In <sub>0.53</sub> Ga <sub>0.47</sub> As interfacial oxide layer | Comments                                                                                                                 |

|----------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Pt/HfO <sub>2</sub> /n-In <sub>0.53</sub> Ga <sub>0.47</sub> As                  | $4.7 \times 10^{12}  \text{cm}^{-2}$   | Yes                                                                     | $\sim$ 1 nm of HfO <sub>2</sub> /In <sub>0.53</sub> Ga <sub>0.47</sub> As IL                                             |

| Al/HfO <sub>2</sub> /n-In <sub>0.53</sub> Ga <sub>0.47</sub> As                  | $6.8 \times 10^{11}  \mathrm{cm}^{-2}$ | No                                                                      | Al scavenges the oxygen from the In <sub>0.53</sub> Ga <sub>0.47</sub> As surface                                        |

| Al/Al <sub>2</sub> O <sub>3</sub> /n-In <sub>0.53</sub> Ga <sub>0.47</sub> As    | $8.9 \times 10^{11}  \mathrm{cm}^{-2}$ | No                                                                      | "Self-cleaning process" of ALD of Al <sub>2</sub> O <sub>3</sub> removes the In <sub>0.53</sub> Ga <sub>0.47</sub> As IL |

| Au/Ni/Al <sub>2</sub> O <sub>3</sub> /n-In <sub>0.53</sub> Ga <sub>0.47</sub> As | $5.9 \times 10^{11}  \mathrm{cm}^{-2}$ | No                                                                      | "Self-cleaning process" of ALD of $Al_2O_3$ removes the $In_{0.53}Ga_{0.47}As\;IL$                                       |

$V_{\rm g}\!>\!0V$  (not shown) indicates that genuine surface accumulation has been achieved.

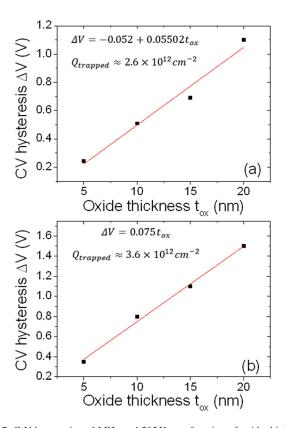

To further examine the physical location and distribution of the trapped charge, C-V hysteresis was measured as a function of oxide thickness series for (a) n-type and (b) p-type Pd/Al<sub>2</sub>O<sub>3</sub>(5–20 nm)/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors.<sup>23</sup> The use of a thickness series is useful in this respect, as for a trapped charge located in a plane within the oxide or at the oxide/semiconductor interface, the C-V hysteresis  $\Delta V$  increases linearly with increasing oxide thickness. This linear relation can be expressed by the following equation:

$$\Delta V = \frac{qQ_{trapped} \times t_{ox}}{\varepsilon_0 k},\tag{2}$$

where  $t_{ox}$  is the oxide thickness,  $\varepsilon_0$  is the vacuum permittivity, and  $\kappa$  is the relative permittivity of the oxide. If the charge is distributed throughout the oxide, then  $\Delta V$  is proportional to the square of the oxide thickness.<sup>40</sup>

FIG. 7. C-V hysteresis at 1 MHz and 295 K as a function of oxide thickness (5, 10, 15, 20 nm) for (a)  $Pd/Al_2O_3/n$ - $In_{0.53}Ga_{0.47}As$  and (b)  $Pd/Al_2O_3/p$ - $In_{0.53}Ga_{0.47}As$  MOS capacitors. The maximum electric field across the oxide, as determined by the maximum voltage in accumulation, is kept at the same value for all thicknesses for both n-type and p-type sample.

The C-V hysteresis  $\Delta V$  versus oxide thickness characteristics are shown in Figure 7 for (a) n-type, and (b) p-type, where  $\Delta V$  is the estimated at  $C_{max}/2$ , and both plots clearly demonstrate a linear dependence of  $\Delta V$  on the oxide thickness, supporting the earlier independent indications that the vast majority of the charge trapping occurs in a plane near the oxide/semiconductor interface and is not distributed through the oxide. The gradient of the plot of  $\Delta V$  versus the oxide thickness is proportional to the trapped charge and yields values of  $2.6 \times 10^{12} \ cm^{-2}$  for the n-In<sub>0.53</sub>Ga<sub>0.47</sub>As and 3.6  $\times 10^{12} \ cm^{-2}$  for the p-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures.

### **IV. CONCLUSIONS**

In this work, charge trapping behaviour in metal/highk/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS structures with either HfO<sub>2</sub> (5 nm) or Al<sub>2</sub>O<sub>3</sub> (5 nm to 20 nm) ALD deposited high-k oxides was studied using C-V hysteresis measurements in combination with TEM microscopy analysis. The samples studied employed both high work function metal gates (Pt, Pd, Ni/Au) and a low work function metal gate (Al). The high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system exhibits both electron and hole trapping, which is predominantly a reversible process. The temporary charge trapping levels, that can be as high as 10<sup>13</sup> cm<sup>-2</sup>, were recorded from the C-V hysteresis which is of the same magnitude as, or even greater than, the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface state density, indicating the importance of C-V hysteresis in the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system. C-V hysteresis is found to increase linearly with the increasing bias in accumulation, and the p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS samples exhibit a larger C-V hysteresis and permanent charge trapping than their n-type  $In_{0.53}Ga_{0.47}$ As counterparts.

Based on TEM analysis, it is observed that the use of an Al gate in HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As samples results in the formation of an Al<sub>2</sub>O<sub>3</sub> layer at the top Al/high-k oxide interface which reduces the maximum capacitance in accumulation. In addition, the top Al metal layer reduces the thickness of the native oxide transition layer present between the HfO<sub>2</sub> and the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface. The removal of the native oxide transition layer for the Al gate samples results in a marked reduction in the level of charge trapping and C-V hysteresis when compared to a Pt gate HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As sample with  $\sim 1$  nm of HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface oxide, indicating that the charge trapping takes place mainly at the interfacial transition layer between the high-k oxide and In<sub>0.53</sub>  $Ga_{0.47}As$ . In addition,  $Al/Al_2O_3/In_{0.53}Ga_{0.47}As$  and Au/Ni/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors, which have no detectable interface oxide due to the reported "self-cleaning" effect of Al<sub>2</sub>O<sub>3</sub> by ALD, have a relatively low level of charge trapping. The C-V hysteresis voltage window ( $\Delta V$ ) increases linearly with the increasing high-k oxide thickness, with the corresponding trapped charge being independent of the oxide thickness, providing further evidence that the trapped charge is predominantly localised as a line charge (in units in cm<sup>-2</sup>) at or near the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface. The results presented in this work identify the understanding and engineering of a native oxide interfacial transition layer between the high-k oxide and the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface, as central to reducing C-V hysteresis in the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS systems.

#### **ACKNOWLEDGMENTS**

The authors thank Michael Schmidt and Patrick Carolan, Tyndall National Institute for the TEM analysis. The authors acknowledge Science Foundation Ireland for financial support of the research work through the INVENT Project (09/IN.1/I2633).

- <sup>1</sup>C. H. Lee, T. Nishimura, K. Nagashio, K. Kita, and A. Toriumi, IEEE Trans. Electron Devices **58**, 1295 (2011).

- <sup>2</sup>F. Zhu, S. Koveshnikov, I. Ok, H. S. Kim, M. Zhang, T. Lee, G. Thareja, L. Yu, J. C. Lee, W. Tsai, V. Tokranov, M. Yakimov, and S. Oktyabrsky, Appl. Phys. Lett. 91, 043507 (2007).

- <sup>3</sup>M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, Tech. Dig. - Int. Electron Devices Meet. 2009, 319.

- <sup>4</sup>S. J. Bentley, M. Holland, X. Li, G. W. Paterson, H. Zhou, O. Ignatova, D. Macintyre, S. Thoms, A. Asenov, B. Shin, J. Ahn, P. C. McIntyre, and I. G. Thayne, IEEE Electron Device Lett. 32(4), 494–496 (2011).

- <sup>5</sup>A. W. Dey, C. Thelander, E. Lind, K. A. Dick, B. M. Borg, M. Borgstöm, P. Nilsson, and L.-E. Wernersson, IEEE Electron Device Lett. 33(6), 791-793 (2012).

- <sup>6</sup>R. Chau, J. Brask, S. Datta, G. Deway, M. Doczy, B. Doyle, J. Kavalieros, B. Jin, M. Metz, A. Majumdar, and M. Radosavljevic, Microelectron. Eng. **80**, 1 (2005).

- <sup>7</sup>N. Goel, P. Majhi, C. O. Chui, W. Tsai, D. Choi, and J. S. Harris, Appl. Phys. Lett. 89, 163517 (2006).

- <sup>8</sup>É. O'Connor, R. D. Long, K. Cherkaoui, K. K. Thomas, F. Chalvet, I. M. Povey, M. E. Pemble, P. K. Hurley, B. B. Brennan, G. Hughes, and S. Newcomb, Appl. Phys. Lett. 92, 022902 (2008).

- <sup>9</sup>É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev, and P. K. Hurley, Appl. Phys. Lett. 94, 102902 (2009).

- $^{10}\text{G.}$  Brammertz, H. C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, Appl. Phys. Lett. 95, 202109 (2009).

- <sup>11</sup>P. K. Hurley, É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, J. MacHale, A. J. Quinn, G. Brammertz et al., ECS Trans. 25(6), 113 (2009).

- <sup>12</sup>R. D. Long, É. O'Connor, S. B. Newcomb, S. Monaghan, K. Cherkaoui, P. Casey, G. Hughes, K. K. Thomas, F. Chalvet, I. M. Povey, M. E. Pemble, and P. K. Hurley, J. Appl. Phys. 106, 084508 (2009).

- <sup>13</sup>R. Engel-Herbert, Y. Hwang, and S. Stemmer, J. Appl. Phys. 108, 124101

- <sup>14</sup>Y. Hwang, R. Engel-Herbert, N. G. Rudawski, and S. Stemmer, Appl. Phys. Lett. 96, 102910 (2010).

- <sup>15</sup>R. D. Long, B. Shin, S. Monaghan, K. Cherkaoui, J. Cagnon, S. Stemmer, P. C. McIntyre, and P. K. Hurley, J. Electrochem. Soc. 158, G103 (2011).

- <sup>16</sup>V. Djara, K. Cherkaoui, M. Schmidt, S. Monaghan, É. O'Connor, I. M. Povey, D. O'Connell, M. E. Pemble, and P. K. Hurley, "Impact of forming gas annealing on the performance of surface-channel In0.53Ga0.47As MOSFETs with an ALD Al2O3 gate dielectric," IEEE Trans. Electron Devices 59(4), 1084-1090 (2012).

- <sup>17</sup>B. Shin, J. R. Weber, R. D. Long, P. K. Hurley, C. G. Van de Walle, and P. C. McIntyre, Appl. Phys. Lett. 96, 152908 (2010).

- <sup>18</sup>Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, "A distributed model for border traps in Al<sub>2</sub>O<sub>3</sub>-InGaAsMOS devices," IEEE Electron Device Lett. 32(4), 485-487 (2011).

- <sup>19</sup>G. Brammertz, A. Alian, D. H. C. Lin, M. Meuris, M. Caymax, and W. E. Wang, IEEE Trans. Electron Devices 58(11), 3890-3897 (2011).

- <sup>20</sup>E. J. Kim, L. Wang, P. M. Asbeck, K. C. Saraswat, and P. C. McIntyre,

- Appl. Phys. Lett. 96, 012906 (2010).

<sup>21</sup>A. Alian, G. Brammertz, R. Degraeve, M. Cho, C. Merckling, D. Lin, W. E. Wang, M. Caymax, M. Meuris, K. D. Meyer, and M. Heyns, IEEE Electron Device Lett. 33(11), 1544-1546 (2012).

- <sup>22</sup>N. Taoka, M. Yokoyama, S. H. Kim, R. Suzuki, R. Iida, S. Lee, T. Hoshii, W. Jevasuwan, T. Maeda, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, in Proceedings of the IEEE International Electron Devices Meeting—IEDM (IEEE, 2011), p. 610.

- <sup>23</sup>Y. Y. Gomeniuk, A. N. Nazarov, S. Monaghan, K. Cherkaoui, E. O'Connor, I. Povey, V. Djara, and P. K. Hurley, in Proceedings of the International Conference on nanomaterials: Applications and Properties (2012), Vol. 1, No. 3, p. 03TF16.

- <sup>24</sup>N. Goel, D. Heh, S. Koveshnikov, I. Ok, S. Oktyabrsky, V. Tokranov, R. Kambhampatic, M. Yakimov, Y. Sun, P. Pianetta, C. K. Gaspe, M. B. Santos, J. Lee, S. Datta, P. Majhi, and W. Tsai, Tech. Dig. - Int. Electron Devices Meet. 2008, 363-366.

- <sup>25</sup>É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble et al., J. Appl. Phys. 109, 024101 (2011).

- <sup>26</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices* (Wiley, NJ, 2007).

- <sup>27</sup>E. H. Nicollian and J. R. Brews, MOS Physics and Technology (Wiley, New York, 2003).

- <sup>28</sup>K. Cherkaoui, S. Monaghan, M. A. Negara, M. Modreanu, P. K. Hurley, D. O'Connell, S. McDonnell, G. Hughes, S. Wright, R. C. Barklie, P. Bailey, and T. C. Q. Noakes, J. Appl. Phys. 104, 064113 (2008).

- <sup>29</sup>D. P. Norton, Mater. Sci. Eng. R **43**, 139–247 (2004).

- $^{30}\mathrm{A.~O'Mahony,~S.~Monaghan,~G.~Provenzano,~I.~M.~Povey,~M.~G.~Nolan,~E.}$ O'Connor, K. Cherkaoui, S. B. Newcomb, F. Crupi, P. K. Hurley, and M. E. Pemble, Appl. Phys. Lett. 97, 052904 (2010).

- <sup>31</sup>T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, Appl. Phys. Lett. 99, 102903 (2011).

- <sup>32</sup>J. Müller, T. S. Böscke, D. Bräuhaus, U. Schröder, U. Böttger, J. Sundqvist, P. Kücher, T. Mikolajick, and L. Frey, Appl. Phys. Lett. 99, 112901 (2011).

- <sup>33</sup>M. Kobayashi, P. T. Chen, Y. Sun, N. Goel, P. Majhi, M. Garner, W. Tasai, P. Pianetta, and Y. Nishi, Appl. Phys. Lett. 93, 182103 (2008).

- <sup>34</sup>S. Rangan, E. Bersch, R. A. Bartynski, E. Garfunkel, and E. Vescovo, Appl. Phys. Lett. 92, 172906 (2008).

- <sup>35</sup>H. Kim, P. C. McIntyre, C. O. Chui, K. C. Saraswat, and S. Stemmer, J. Appl. Phys. 96, 3467 (2004).

- <sup>36</sup>S. Klejna and S. D. Elliot, J. Phys. Chem. C **116**(1), 643–654 (2012).

- <sup>37</sup>E. J. Kim, E. Chagarov, J. Cagnon, Y. Yuan, A. C. Kummel, P. M. Asbeck, S. Stemmer, K. C. Saraswat, and P. C. McIntyre, J. Appl. Phys. **106**, 124508 (2009).

- <sup>38</sup>M. Milojevic, F. S. Aguirre-Tostado, C. L. Hinkle, H. C. Kim, E. M. Vogel, J. Kim, and R. M. Wallace, Appl. Phys. Lett. 93, 202902 (2008).

- <sup>39</sup>S. Monaghan, A. O'Mahony, G. Provenzano, K. Cherkaoui, É. O'Connor, I. M. Povey, M. G. Nolan, D. O'Connell, S. B. Newcomb, F. Crupi, M. E. Pemble, and P. K. Hurley, J. Vac. Sci. Technol. B 29(1), 01A807 (2011).

- <sup>40</sup>R. S. Muller and T. I. Kamins, Device Electronics for Integrated Circuits (Wiley, New York, 1986).