|                                | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Title                          | Junctionless multigate field-effect transistor                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Authors                        | Lee, Chi-Woo;Afzalian, Aryan;Akhavan, Nima Dehdashti;Yan,<br>Ran;Ferain, Isabelle;Colinge, Jean-Pierre                                                                                                                                                                                                                                                                                                                                                                               |  |

| Publication date               | 2009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Original Citation              | Lee, CW., Afzalian, A., Akhavan, N. D., Yan, R., Ferain, I.<br>and Colinge, JP. (2009) 'Junctionless multigate field-effect<br>transistor', Applied Physics Letters, 94(5), pp. 053511. doi:<br>10.1063/1.3079411                                                                                                                                                                                                                                                                    |  |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Link to publisher's<br>version | http://aip.scitation.org/doi/abs/10.1063/1.3079411 -<br>10.1063/1.3079411                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Rights                         | © 2009 American Institute of Physics.This article may be<br>downloaded for personal use only. Any other use requires prior<br>permission of the author and AIP Publishing. The following<br>article appeared in Lee, CW., Afzalian, A., Akhavan, N. D.,<br>Yan, R., Ferain, I. and Colinge, JP. (2009) 'Junctionless<br>multigate field-effect transistor', Applied Physics Letters, 94(5),<br>pp. 053511 and may be found at http://aip.scitation.org/doi/<br>abs/10.1063/1.3079411 |  |

| Download date                  | 2025-04-18 05:59:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Item downloaded<br>from        | https://hdl.handle.net/10468/4364                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

## Junctionless multigate field-effect transistor

Chi-Woo Lee, Aryan Afzalian, Nima Dehdashti Akhavan, Ran Yan, Isabelle Ferain, and Jean-Pierre Colinge

Citation: Appl. Phys. Lett. **94**, 053511 (2009); doi: 10.1063/1.3079411 View online: http://dx.doi.org/10.1063/1.3079411 View Table of Contents: http://aip.scitation.org/toc/apl/94/5 Published by the American Institute of Physics

## Articles you may be interested in

Reduced electric field in junctionless transistors Applied Physics Letters **96**, 073510 (2010); 10.1063/1.3299014

Low subthreshold slope in junctionless multigate transistors Applied Physics Letters **96**, 102106 (2010); 10.1063/1.3358131

Simulation of junctionless Si nanowire transistors with 3 nm gate length Applied Physics Letters **97**, 062105 (2010); 10.1063/1.3478012

Planar junctionless transistor with non-uniform channel doping Applied Physics Letters **102**, 133505 (2013); 10.1063/1.4801443

A two-dimensional analytical model for short channel junctionless double-gate MOSFETs AIP Advances **5**, 057122 (2015); 10.1063/1.4921086

Gate-all-around junctionless silicon transistors with atomically thin nanosheet channel (0.65 nm) and record sub-threshold slope (43 mV/dec) Applied Physics Letters **110**, 032101 (2017); 10.1063/1.4974255

## Junctionless multigate field-effect transistor

Chi-Woo Lee, Aryan Afzalian, Nima Dehdashti Akhavan, Ran Yan, Isabelle Ferain, and Jean-Pierre Colinge<sup>a)</sup>

Tyndall National Institute, University College Cork Lee Maltings, Prospect Row, Cork, Ireland

(Received 27 November 2008; accepted 15 January 2009; published online 6 February 2009)

This paper describes a metal-oxide-semiconductor (MOS) transistor concept in which there are no junctions. The channel doping is equal in concentration and type to the source and drain extension doping. The proposed device is a thin and narrow multigate field-effect transistor, which can be fully depleted and turned off by the gate. Since this device has no junctions, it has simpler fabrication process, less variability, and better electrical properties than classical MOS devices with source and drain *PN* junctions. © 2009 American Institute of Physics. [DOI: 10.1063/1.3079411]

Research in multigate silicon-on-insulator metal-oxidesemiconductor field-effect transistors (MOSFETs) for deep submicron complementary MOS applications is currently being carried out by many semiconductor companies, as these devices hold the promise for pushing the limits of silicon integration beyond the limits of classical planar technologies.<sup>1</sup> In a multigate field-effect transistor (MuG-FET) the gate electrode is wrapped around a silicon wire, called "finger" or "fin," forming a gate structure that delivers optimal control of the channel potential. The excellent gateto-channel coupling combined with the use of a small wire section allows one to fully deplete the channel region even if it is heavily doped and, therefore, to turn the device off.

In very short-channel devices (L=10 nm or less) the formation of ultrasharp source and drain junctions imposes orders of magnitude of variation in doping concentration over a distance of a few nanometers. Such concentration gradients impose drastic conditions on doping techniques and thermal budget. The devices proposed here are fabricated without the need for forming junctions. Since the channel doping concentration and type are the same as in the source and drain extensions, there is no doping concentration gradient and therefore no impurity diffusion during thermal processing steps. This relaxes the thermal budget by a great deal.

Thin-film accumulation-mode double-gate devices have been shown to have better short-channel properties [draininduced barrier lowering (DIBL) and subthreshold slope degradation] than conventional inversion-mode (IM) devices.<sup>1</sup> It has been shown that the use of accumulation-mode devices (a family of device to which the proposed device belongs) improves contact resistance and reduces the sensitivity to gate overlap/underlap issues.<sup>2</sup> It has also been shown that accumulation-mode devices are less sensitive to doping fluctuation effects than classical IM devices.<sup>3</sup> Accumulationmode MuGFETs have been shown to be less sensitive to negative bias thermal instability than IM devices and to have less variation in drain current with doping concentration.<sup>4</sup>

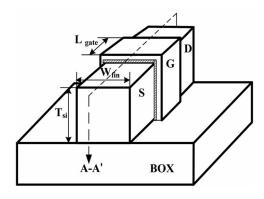

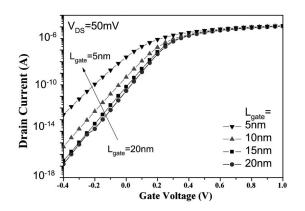

A junctionless transistor is basically an accumulationmode device in which the channel doping concentration is equal to that on the source and drain. Simulations show that these junctionless devices have better short-channel electrical characteristics than conventional IM devices. The electrical characteristics of both conventional  $(N^+ - P - N^+)$  and junctionless  $(N^+-N^+-N^+)$  devices were simulated using the Atlas 3-D device simulator.<sup>5</sup> Abrupt source and drain junctions are used for the conventional transistors. Table I shows the parameters used in device simulation, and Fig. 1 shows the general structure of a trigate MuGFET. The cross section of the device is  $5 \times 5$  nm<sup>2</sup>. The feasibility of accumulation-mode devices with such a small cross section was demonstrated in the past.<sup>6</sup> Because of the *N*-type doping of the channel, a N-channel junctionless device requires a gate material with a high work function such as  $P^+$  polycrystalline silicon or platinum in order to achieve a suitable  $V_{\rm th}$  value. It is, however, clear that the use of a metal as gate material is preferable for gate resistance reduction purposes. It is also to be noted that the junctionless device lends itself to the use of a gate-last process, which facilitates the use of a metal gate. A midgap gate material is used for the classical IM device. If the cross section of the channel is small enough, the gate can deplete the heavily doped channel entirely, which turns the transistor off. The subthreshold characteristics of junctionless MuGFETs with different gate lengths (5-20 nm) at low drain voltage are shown in Fig. 2. The subthreshold slope of shortest junctionless device (L=5 nm) is below 80 mV/decade. This shows the potential of junctionless transistor for extremely short-channel applications. It is important to note that the off current is determined solely by the electrostatic control of the gate and not by the leakage current of a reverse-biased diode. This renders the device less sensitive to contamination, which reduces carrier lifetime and to temperature, as shown in Ref. 1, for accumulation-mode doublegate transistors; it also enables one to minimize leakage current if a low-bandgap semiconductor such as germanium is used. It is important for the cross section of the junctionless device to be sufficiently small in order to be able to fully

|                      | Conventional                                       | Junctionless                                       |

|----------------------|----------------------------------------------------|----------------------------------------------------|

| Channel doping       | $2 \times 10^{15} \text{ cm}^{-3} (P\text{-type})$ | $8 \times 10^{19} \text{ cm}^{-3} (N-\text{type})$ |

| Gate oxide thickness | 2 nm                                               | 2 nm                                               |

| Gate work function   | 4.6 eV                                             | 5.5 eV                                             |

| T <sub>si</sub>      | 5 nm                                               | 5 nm                                               |

| $W_{\rm fin}$        | 5 nm                                               | 5 nm                                               |

| Lgate                | 5–30 nm                                            | 10–30 nm                                           |

<sup>&</sup>lt;sup>a)</sup>Electronic mail: jean-pierre.colinge@tyndall.ie.

FIG. 1. MuGFET device schematic view.

deplete the channel of carriers and turn the device off. The higher the channel doping concentration, the smaller the cross section needs to be. One may suggest further analysis of the device to parameter variations such as fin width and height and doping concentration.<sup>7</sup>

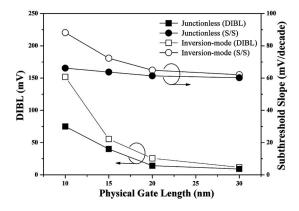

For the IM devices we used a lightly doped channel in order to avoid premature inversion at the corners.<sup>3</sup> The simulated IM devices have a source/drain and source/gate overlap of 1 nm, which means that effective channel length of the device is 8 nm when the physical gate length is 10 nm. The simulated results for DIBL and threshold voltage versus physical gate length for both junctionless MuGFETs and IM MuGFETs are plotted in Fig. 3. The DIBL is defined as the difference in threshold voltage when the drain voltage is increased from 0.05 to 1.0 V [DIBL= $V_{\rm th}(V_{\rm DS}=0.05 \text{ V})$  –  $V_{\rm th}(V_{\rm DS}=1 \text{ V})$ ]. The junctionless MuGFETs has better short-channel characteristics than the IM device. In the accumulation-mode device, the effective gate length, defined

FIG. 2. Subthreshold characteristics of junctionless devices with  $T_{si}=W_{si}$ =5 nm at  $V_{DS}$ =50 mV for different gate length values.

FIG. 3. DIBL and subthreshold slope at  $V_{\text{DS}}=50$  mV in junctionless and IM devices with  $T_{\text{si}}=W_{\text{si}}=5$  nm.

as the distance between the source and drain junctions, is 2 nm shorter than the printed gate length ( $L_{eff}=L_{gate}-2$  nm). In the junctionless device, we arbitrarily define the effective length as being equal to the printed gate length ( $L_{eff}=L_{gate}$ ). It is worth noting that the longer effective gate length of the junctionless device is not the reason for its better short-channel characteristics since, for instance, a junctionless transistor with  $L_{gate}=L_{eff}=10$  nm has a lower subthreshold slope than an IM device with  $L_{gate}=15$  nm and thus  $L_{eff}=13$  nm.

In conclusion, we propose a type of MOSFET in which there are no PN junctions and where the doping concentration in the channel is sensibly equal to that in the source and drain. The device exhibits excellent turn-off and shortchannel characteristics based on our simulations.

This material is based on works supported by the Science Foundation Ireland under Grant No. 05/IN/I888.

- <sup>1</sup>E. Rauly, B. Iñiguez, and D. Flandre, Electrochem. Solid-State Lett. 4, G28 (2001).

- <sup>2</sup>C.-W. Lee, D. Lederer, A. Afzalian, R. Yan, N. Dehdashti, W. Xiong, and J. P. Colinge, Solid-State Electron. **52**, 1815, (2008).

- <sup>3</sup>R. Yan, D. Lynch, T. Cayron, D. Lederer, A. Afzalian, C.-W. Lee, N.

- Dehdashti, and J. P. Colinge, Solid-State Electron. **52**, 1872 (2008).

- <sup>4</sup>W. Cheng, A. Teramoto, R. Kuroda, M. Hirayama, and T. Ohmi, Microelectron. Eng. **84**, 2105 (2007).

- <sup>5</sup>See http://www.silvaco.com.

- <sup>6</sup>F.-L. Yang, D.-H. Lee, H. -Y. Chen, C.-Y. Chang, S.-D. Liu, C.-C. Huang, T.-X. Chung, H.-W. Chen, C.-C. Huang, Y.-H. Liu, C.-C. Wu, C.-C. Chen, S.-C. Chen, Y.-T. Chen, Y.-H. Chen, C.-J. Chen, B.-W. Chan, P.-F. Hsu,

- J.-H. Shieh, H.-J. Tao, Y.-C. Yeo, Y. Li, J.-W. Lee, P. Chen, M.-S. Liang, and C. Hu, Dig. Tech. Pap. Symp. VLSI Technol. **2004**, 196.

- <sup>7</sup>K. Endo, Y. Ishikawa, Y. Liu, M. Masahara, T. Matsukawa, S.-I. O'uchi, K. Ishii, H. Yamauchi, J. Tsukada, and E. Suzuki, IEEE Electron Device Lett. **28**, 1123 (2007).