| Title                       | Reduced electric field in junctionless transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Colinge, Jean-Pierre;Lee, Chi-Woo;Ferain, Isabelle;Akhavan,<br>Nima Dehdashti;Yan, Ran;Razavi, Pedram;Yu, Ran;Nazarov, Alexei<br>N.;Doria, Rodrigo T.                                                                                                                                                                                                                                                                                                                                                   |

| Publication date            | 2010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Original Citation           | Colinge, JP., Lee, CW., Ferain, I., Akhavan, N. D., Yan, R., Razavi, P., Yu, R., Nazarov, A. N. and Doria, R. T. (2010) 'Reduced electric field in junctionless transistors', Applied Physics Letters, 96(7), pp. 073510. doi: 10.1063/1.3299014                                                                                                                                                                                                                                                        |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Link to publisher's version | http://aip.scitation.org/doi/abs/10.1063/1.3299014 - 10.1063/1.3299014                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Rights                      | © 2010 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in Colinge, JP., Lee, CW., Ferain, I., Akhavan, N. D., Yan, R., Razavi, P., Yu, R., Nazarov, A. N. and Doria, R. T. (2010) 'Reduced electric field in junctionless transistors', Applied Physics Letters, 96(7), pp. 073510 and may be found at http://aip.scitation.org/doi/abs/10.1063/1.3299014 |

| Download date               | 2025-01-15 04:25:46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Item downloaded from        | https://hdl.handle.net/10468/4346                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Reduced electric field in junctionless transistors

Jean-Pierre Colinge, Chi-Woo Lee, Isabelle Ferain, Nima Dehdashti Akhavan, Ran Yan, Pedram Razavi, Ran Yu, Alexei N. Nazarov, and Rodrigo T. Doria

Citation: Appl. Phys. Lett. 96, 073510 (2010); doi: 10.1063/1.3299014

View online: http://dx.doi.org/10.1063/1.3299014

View Table of Contents: http://aip.scitation.org/toc/apl/96/7

Published by the American Institute of Physics

## Articles you may be interested in

Junctionless multigate field-effect transistor

Applied Physics Letters 94, 053511 (2009); 10.1063/1.3079411

Low subthreshold slope in junctionless multigate transistors

Applied Physics Letters 96, 102106 (2010); 10.1063/1.3358131

Simulation of junctionless Si nanowire transistors with 3 nm gate length

Applied Physics Letters 97, 062105 (2010); 10.1063/1.3478012

Mobility improvement in nanowire junctionless transistors by uniaxial strain

Applied Physics Letters 97, 042114 (2010); 10.1063/1.3474608

Analysis of the leakage current in junctionless nanowire transistors

Applied Physics Letters 103, 202103 (2013); 10.1063/1.4829465

Gate-all-around junctionless silicon transistors with atomically thin nanosheet channel (0.65 nm) and record sub-threshold slope (43 mV/dec)

Applied Physics Letters 110, 032101 (2017); 10.1063/1.4974255

## Reduced electric field in junctionless transistors

Jean-Pierre Colinge, a) Chi-Woo Lee, Isabelle Ferain, Nima Dehdashti Akhavan, Ran Yan, Pedram Razavi, Ran Yu, Alexei N. Nazarov, and Rodrigo T. Doria<sup>c)</sup>

Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland

(Received 27 November 2009; accepted 4 January 2010; published online 19 February 2010)

The electric field perpendicular to the current flow is found to be significantly lower in junctionless transistors than in regular inversion-mode or accumulation-mode field-effect transistors. Since inversion channel mobility in metal-oxide-semionductor transistors is reduced by this electric field, the low field in junctionless transistor may give them an advantage in terms of current drive for nanometer-scale complementary metal-oxide semiconductor applications. This observation still applies when quantum confinement is present. © 2010 American Institute of Physics. [doi:10.1063/1.3299014]

The mobility of the carriers in a metal-oxide-silicon field-effect transistor (MOSFET) is strongly affected by the vertical electric field. The silicon universal mobility curves were published by Takagi et al. in 1994. The universal mobility curves show that the electron mobility in the channel of a MOSFET transistor,  $\mu$ , decreases as a function of the effective electric field,  $\mathcal{E}$ , following the law  $\mu \approx \mathcal{E}^{-0.3}$ . The study by Takagi et al. was limited to doping concentrations below 10<sup>18</sup> cm<sup>-3</sup> but a decrease in mobility with increasing electric field was observed for all cases of figure. As the dimensions of MOSFETs are scaled down, the effective oxide thickness (EOT) of the gate insulator is constantly decreased, which increases the vertical electrical field in the channel and increases carrier scattering, thereby decreasing mobility. It has been shown that electron channel mobility in MOSFETs has "historically" decreased from 400 to 300 and 130 cm<sup>2</sup>/V s when migrating from 0.8 to 0.6 and 0.13  $\mu$ m technology nodes, respectively, making it necessary to develop strain silicon technology to keep switching speeds increasing with device size reduction.<sup>3</sup> Without strain technology, the channel mobility in modern MOSFETs would be equal or lower than that in heavily doped silicon (100 cm<sup>2</sup>/V s for electrons in N<sup>+</sup> silicon).<sup>4</sup>

Recently, a nanowire transistor called the "junctionless transistor" or the "gated resistor" has been introduced. <sup>5,6</sup> It is made of an N<sup>+</sup> (or P<sup>+</sup> for a p-channel device) doped silicon nanowire with a gate electrode. The doping concentration typically ranges between 10<sup>19</sup> and 8×10<sup>19</sup> cm<sup>-3</sup>. Using a trigate device architecture it is possible to turn the device on and off and to obtain MOSFET-like electrical characteristics. <sup>5,6</sup> Even though the electrical characteristics of the junctionless transistor are similar to those of a regular MOSFET, there is a fundamental difference between the two devices. Classical MOSFETs, including multigate field-effect transistor, are normally-off devices, as the drain junction is reverse biased and blocks current flow if no channel is created between source and drain. To turn the device on, the gate voltage is increased in order to create an inversion channel. Since it is the electric field from the gate that attracts

inversion carriers, the presence of a high electric field in the channel is inherent to the operation of inversion-mode MOS-FETs. In accumulation-mode transistors, an accumulation channel is formed beneath the gate insulator because the carriers are attracted by the electric field from the gate. As a result; accumulation-mode transistors suffer from the same field-induced mobility degradation as inversion-mode devices. The junctionless transistor, on the other hand, is basically a normally-on device where the work function difference between the gate electrode and the silicon nanowire shifts flatband voltage and threshold voltage to positive values (we consider here an n-channel device). When the device is turned on it is in flatband condition and, as a result, there is a zero electric field in the directions x and y perpendicular to the current flow direction. In other words, the electric field from the gate is used to deplete the device and turn it off. When the device is on, carriers flow from source to drain in a "channel" of neutral silicon, in which there is no electric field perpendicular to current flow.

As the cross section of the device is reduced below approximately 7 nm, confinement effects in the directions perpendicular to the current flow alter the electron concentration profile. This raises the issue of calculating the electric field in nanowire devices. For instance, in a device that is in flatband conditions ( $\mathcal{E}$ =0) according to classical semiconductor device physics, the electric field is no longer equal to zero once quantum confinement effects are taken into consideration. To calculate the electric field we use a two-dimensional Poisson–Schrödinger solver.

Two n-channel devices are used for comparison as follows: an inversion-mode trigate MOSFET with a p-type channel doping concentration of  $10^{17}$  cm<sup>-3</sup> and a junction-less trigate MOSFET with an n-type channel doping concentration of  $10^{19}$  cm<sup>-3</sup>. Both devices have a silicon cross section of  $5\times 5$  nm<sup>2</sup> and an EOT of 1 nm. The buried oxide thickness is 10 nm and the back gate (substrate) is grounded. The gate voltage for the junctionless transistor  $(V_G)$  is chosen in such a way that the device is in "flatband" conditions (to be more accurate,  $V_G$  is chosen in such a way that the electron concentration, n, averaged over the device cross section, is equal to the doping concentration, or  $(1/T_{Si}W_{Si})\int_0^{W_{Si}}\int_0^{T_{Si}}n(x,y)dxdy=N_D$ , where  $T_{Si}$  is the silicon thickness,  $W_{Si}$  is the width of the nanowire, and  $N_D$  is the doping concentration). The gate voltage of the inversion-

a) Electronic mail: jean-pierre.colinge@tyndall.ie.

<sup>&</sup>lt;sup>b)</sup>Lashkaryov Institute of Semiconductor Physics, Kiev, Ukraine.

c)Departamento de Engenharia Elétrica, CentroUniversitário da FEI, São Bernardo do Campo, Brazil and LSI/PSI/USP/University of São Paulo, São Paulo, Brazil.

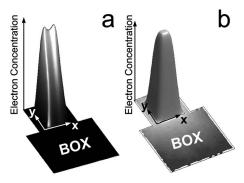

FIG. 1. Three-dimensional electron concentration profile in (a) an inversion-mode trigate MOSFET and (b) a heavily doped junctionless trigate MOSFET.  $W_{\rm Si}=T_{\rm Si}=5\,$  nm;  $T_{\rm OX}=1\,$  nm. BOX is the buried oxide with thickness  $T_{\rm BOX}=10\,$  nm. In the inversion-mode device,  $N_{\rm A}=10^{17}\,$  cm<sup>-3</sup>, the flatband voltage  $(V_{\rm FB})$  is  $-0.8\,$  V and  $V_{\rm G}=V_{\rm FB}+1.03\,$  V. In the junctionless device,  $N_{\rm D}=10^{19}\,$  cm<sup>-3</sup>,  $V_{\rm FB}=0.8\,$  V, and  $V_{\rm G}=V_{\rm FB}$ .

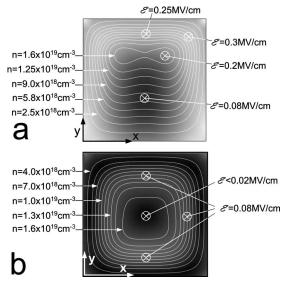

mode device is chosen in such a way that the electron concentration, n(x,y), integrated over the device cross section, is equal to that in the junctionless device. Thus, if mobility was constant and equal in both devices, they would carry exactly the same drain current. Figure 1 shows a three-dimensional view of the electron concentration profile in the two devices. Both devices have a peak concentration of approximately  $1.6 \times 10^{19}$  cm<sup>-3</sup>. Figure 2 shows the electron concentration in the form of isoconcentration contour lines, superimposed to a grayscale representation of the norm of the electric field. The lower the field, the darker the gray shading, and the higher the field the lighter the gray shading. Some particular values of the field are given at locations marked by the symbol "8." In the inversion-mode device, the majority of the inversion carriers, and in particular the points of peak electron concentration, are located in high electric field regions. This is quite normal, considering that inversion electrons are present because they are attracted by the electric field emanating from the gate. Accumulation-mode devices show results that are basically identical to those of inversion-mode devices. In the junctionless transistors, on the other hand, the

FIG. 2. Electron concentration contour lines superimposed to a grayscale representation of the amplitude of the electric field. The lower the field, the darker the gray shading, and the higher the field the lighter the gray shading. Field values are given at locations marked by the symbol " $\otimes$ ." (a) Inversion-mode device and (b) junctionless device. Same parameters as in Fig. 1.

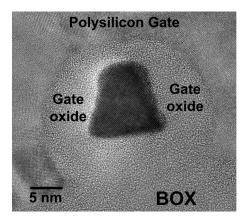

FIG. 3. Transmission electron microscope photograph of a junctionless nanowire transistor.

peak electron concentration coincides with the region of lowest electric field. The field is not quite equal to zero but it is much lower ( $\mathcal{E} < 0.02~\text{MV/cm}$ ) than in the inversion-mode device ( $\mathcal{E} \ge 0.2~\text{mV/cm}$ ). This may offer an advantage to junctionless transistors in terms of current drive, once device size reaches the nanoscale level.

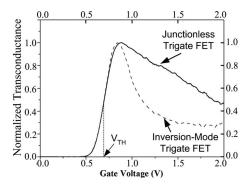

Both inversion-mode and junctionless devices were fabricated using the process described in Ref. 5. The channel length is 1  $\mu$ m, the gate oxide thickness is 5 nm and the doping concentration is  $10^{17}$  cm<sup>-3</sup> ( $N_A$ ) and  $10^{19}$  cm<sup>-3</sup> ( $N_D$ ) in the inversion-mode and junctionless FETs, respectively. The cross section of a junctionless device is shown in Fig. 3. Figure 4 shows the normalized transconductance,  $g_m/g_{mmax}$ in the two types of devices as a function of gate voltage. The transconductance was measured at low drain voltage (50 mV), and is, therefore, proportional to the electron mobility. Both devices have a threshold voltage,  $V_{\rm TH}$ , of approximately 0.7 V. As gate voltage is increased beyond  $V_{\rm TH}$ , the mobility in the inversion-mode device reaches a peak and then decreases rapidly because of the high electric field in the channel. In the junctionless transistor, the decrease in mobility with gate voltage is much less pronounced, as a result of the lower electric field perpendicular to the current flow. The peak mobility in the junctionless is difficult to estimate from measurements. The simple resistor equation  $I_{\rm D} = q \mu N_{\rm D} (T_{\rm Si} W_{\rm Si} / L) V_{\rm DS}$  is valid in flatband only, i.e., for a gate voltage significantly higher than that at which the peak of transconductance occurs. It is also difficult to measure the mobility in the regular trigate device because the gate oxide thickness varies with the crystal orientation of the different sides of the nanowire (Fig. 3). From comparison between

FIG. 4. Normalized transconductance  $g_{\rm m}/g_{\rm mmax}$  vs gate voltage in inversion-mode and junctionless trigate nanowire transistors.

measurements simulation results, however, we estimate that the mobility in the junctionless device is approximately  $80\ cm^2/V$  s when the device is turned on.

Doping fluctuations are a concern for devices with small dimensions. For example considering  $T_{Si} = W_{Si} = 10$  nm and a gate length of 20 nm, the statistical number of doping atoms in the channel region is 0.002, 2, and 20 for doping concentrations of  $10^{15}$ ,  $10^{18}$ , and  $10^{19}$  cm<sup>-3</sup>. "Undoped" devices have a typical doping concentration of 1019 cm<sup>-3</sup> which means that, statistically, every device in 500 will contain a doping atom and, therefore, have a threshold voltage different from that of the other devices. In a moderately doped device  $(N_A = 10^{18} \text{ cm}^{-3})$ , there is an average of two doping atoms in the channel. In practice, many devices will have one or three doping atoms, which has a significant impact on variability. In a heavily doped junctionless device  $(N_D)$ =  $10^{19}$  cm<sup>-3</sup>), the average number of doping atoms is 20. This relatively large number should render junctionless devices less sensitive to doping impurity fluctuation problems than other types of MOSFETs.

In conclusion, we observe that, in inversion-mode and accumulation mode trigate nanowire MOSFETs, the peak electron concentration coincides with the presence high electric fields, while the opposite is seen in heavily doped junctionless transistors. Since high electric fields are known to reduce mobility, this gives an advantage to junctionless devices in terms of current drive.

This work is supported by the Science Foundation Ireland Grant No. 05/IN/I888: Advanced Scalable Silicon-on-

Insulator Devices for Beyond-End-of-Roadmap Semiconductors. This work has also been enabled by the Programme for Research in Third-Level Institutions. This work was supported in part by the European Community (EC) Seventh Framework Program through the Networks of Excellence NANOSIL and EUROSOI+under Contract Nos. 216171 and 216373. The authors also wish to thank Dr. N. Petkov for taking the TEM picture.

- <sup>1</sup>S. Takagi, A. Toriumi, M. Iwase, and H. Tango, IEEE Trans. Electron Devices 41, 2357 (1994).

- <sup>2</sup>S. Takagi, A. Toriumi, M. Iwase, and H. Tango, IEEE Trans. Electron Devices 41, 2363 (1994).

- <sup>3</sup>S. E. Thompson, M. Armstrong, C. Auth, M. Alavi, M. Buehler, R. Chau, S. Cea, T. Ghani, G. Glass, T. Hoffman, C. H. Jan, C. Kenyon, J. Klaus, K. Kuhn, Z. Ma, B. Mcintyre, K. Mistry, A. Murthy, B. Obradovic, R. Nagisetty, P. Nguyen, S. Sivakumar, R. Shaheed, L. Shifren, B. Tufts, S. Tyagi, M. Bohr, and Y. El-Mansy, IEEE Trans. Electron Devices **51**, 1790 (2004).

- <sup>4</sup>C. Jacoboni, C. Canali, G. Ottaviani, and A. A. Quaranta, Solid-State Electron. **20**, 77 (1977).

- <sup>5</sup>C. W. Lee, A. Afzalian, N. Dehdashti Akhavan, R. Yan, I. Ferain, and J. P. Colinge, Appl. Phys. Lett. **94**, 053511 (2009).

- <sup>6</sup>J. P. Colinge, C. W. Lee, A. Afzalian, N. Dehdashti, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A. M. Kelleher, B. McCarthy, and R. Murphy, Proceedings of IEEE International SOI Conference, 2009 (unpublished), Vol. 11.1.

- K. W. Su and J. B. Kuo, IEEE Trans. Electron Devices 44–5, 832 (1997).

J. P. Colinge, J. C. Alderman, W. Xiong, and C. R. Cleavelin, IEEE Trans. Electron Devices 53, 1131 (2006).

- <sup>9</sup>F. J. G. Ruiz, I. M. Tienda-Luna, A. Godoy, IEEE Trans. Electron Devices **56**, 2711 (2009).

- <sup>10</sup>J. P. Colinge, Solid-State Electron. **51**, 1153 (2007).