| Title                       | Impact of forming gas annealing on the performance of surface-<br>channel In0.53Ga0.47As MOSFETs with an ALD Al2O3 gate<br>dielectric                                                                                                                                                                                                                                                                           |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Djara, Vladimir;Cherkaoui, Karim;Schmidt, Michael;Monaghan,<br>Scott;O'Connor, Éamon;Povey, Ian;O'Connell, Dan;Pemble, Martyn<br>E.;Hurley, Paul K.                                                                                                                                                                                                                                                             |

| Publication date            | 2012-02-17                                                                                                                                                                                                                                                                                                                                                                                                      |

| Original Citation           | Djara, V., Cherkaoui, K., Schmidt, M., Monaghan, S., O'Connor,<br>É., Povey, I. M., O'Connell, D., Pemble, M. E. and Hurley, P. K.<br>(2012) 'Impact of forming gas annealing on the performance of<br>surface-channel In0. 53Ga0. 47As MOSFETs with an ALD Al2O3<br>gate dielectric', IEEE Transactions on Electron Devices, 59(4), pp.<br>1084-1090. doi: 10.1109/TED.2012.2185242                            |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                         |

| Link to publisher's version | 10.1109/TED.2012.2185242                                                                                                                                                                                                                                                                                                                                                                                        |

| Rights                      | © 2012, IEEE. Personal use of this material is permitted.<br>Permission from IEEE must be obtained for all other uses, in any<br>current or future media, including reprinting/republishing this<br>material for advertising or promotional purposes, creating new<br>collective works, for resale or redistribution to servers or lists, or<br>reuse of any copyrighted component of this work in other works. |

| Download date               | 2025-08-01 14:35:17                                                                                                                                                                                                                                                                                                                                                                                             |

| Item downloaded<br>from     | https://hdl.handle.net/10468/13324                                                                                                                                                                                                                                                                                                                                                                              |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# Impact of Forming Gas Annealing on the Performance of Surface-Channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs With an ALD Al<sub>2</sub>O<sub>3</sub> Gate Dielectric

Vladimir Djara, *Student Member, IEEE*, Karim Cherkaoui, Michael Schmidt, Scott Monaghan, *Member, IEEE*, Éamon O'Connor, Ian M. Povey, Dan O'Connell, Martyn E. Pemble, and Paul K. Hurley

Abstract-We investigated the effect of forming gas (5%  $H_2/95\%$  N<sub>2</sub>) annealing on surface-channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs with atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> as the gate dielectric. We found that a forming gas anneal (FGA) at 300 °C for 30 min was efficient at removing or passivating positive fixed charges in Al<sub>2</sub>O<sub>3</sub>, resulting in a shift of the threshold voltage from -0.63 to 0.43 V and in an increase in the  $I_{\rm on}/I_{\rm off}$  ratio of three orders of magnitude. Following FGA, the MOSFETs exhibited a subthreshold swing of 150 mV/dec, and the peak transconductance, drive current, and peak effective mobility increased by 29%, 25%, and 15%, respectively. FGA significantly improved the source- or drain-to-substrate junction isolation, with a reduction of two orders of magnitude in the reverse bias leakage exhibited by the Si-implanted  $In_{0.53}Ga_{0.47}As n^+/p$  junctions, which is consistent with passivation of midgap defects in In<sub>0.53</sub>Ga<sub>0.47</sub>As by the FGA process.

*Index Terms*—Forming gas anneal (FGA), high-k, InGaAs, metal–oxide–semiconductor field-effect transistor (MOSFET), surface channel.

# I. INTRODUCTION

N RECENT years, surface-channel In<sub>0.53</sub>Ga<sub>0.47</sub>As metaloxide-semiconductor field-effect transistors (MOSFETs) have attracted considerable research attention as silicon technology is gradually reaching the limits of dimensional scaling [1]-[4]. One major obstacle to the development of these devices is the integration of high-k gate oxides on the  $In_{0.53}Ga_{0.47}As$ surface with sufficiently low density of interface states  $(D_{it})$ and fixed oxide charges. Various methods such as  $(NH_4)_2S$ passivation [5]-[8], silicon interlayer [9], [10], interface control layer [11], [12], and InP capping [13] have been explored to reduce  $D_{it}$ . Forming gas  $(H_2/N_2)$  annealing, which is well known for passivating  $P_b$ -like defects in SiO<sub>2</sub>/Si and high- $k/SiO_x/Si$  systems [14], [15], represents an alternative or complimentary approach for reducing defects in high- $k/In_{0.53}Ga_{0.47}As$  structures subsequent to the gate oxide deposition.

The authors are with Tyndall National Institute, University College Cork, Cork, Ireland (e-mail: vladimir.djara@tyndall.ie).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2012.2185242

Si-implanted  $1.5 \ \mu\text{m}$  4  $\mu\text{m}$ Source Pd gate Drain 10 nm Al<sub>2</sub>O<sub>3</sub> 2  $\mu\text{m} p$ -ln<sub>0.53</sub>Ga<sub>0.47</sub>As (4×10<sup>17</sup>/cm<sup>3</sup>)  $p^+$  lnP Substrate

1

Fig. 1. Schematic cross-sectional diagram of a surface-channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET with a 10-nm-thick ALD Al<sub>2</sub>O<sub>3</sub> gate dielectric. The gate overlap is 1.5  $\mu$ m, and the separation between the gate contact and the source or drain contact is 4  $\mu$ m.

Recent studies using metal–oxide–semiconductor capacitors (MOSCAPs) have shown that a forming gas anneal (FGA) can reduce the fixed oxide charge density in  $Al_2O_3/In_{0.53}Ga_{0.47}As$  systems [16], [17] and reduce  $D_{it}$  near the  $In_{0.53}Ga_{0.47}As$  conduction band in  $HfO_2/n-In_{0.53}Ga_{0.47}As$  systems [18]. However, results reported to date do not indicate any significant influence of FGA on the prominent donor-like defects near midgap [5].

In this paper, we extend on the work reported to date on the effect of FGA on  $In_{0.53}Ga_{0.47}As$  MOSCAPs [16], [17] to investigate the impact of FGA on surface-channel  $In_{0.53}Ga_{0.47}As$  MOSFETs. The availability of  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOSFETs allows not only to study the impact of FGA on the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  gate stack but also to investigate its effect on carrier transport at the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  interface and on the Si-implanted  $In_{0.53}Ga_{0.47}As$  n<sup>+</sup>/p junctions.

# II. DEVICE FABRICATION

Surface-channel MOSFETs (see Fig. 1) and MOSCAPs were fabricated on a 2- $\mu$ m-thick Zn-doped (4 × 10<sup>17</sup> /cm<sup>3</sup>) p-In<sub>0.53</sub>Ga<sub>0.47</sub>As layer grown on a 2-in p<sup>+</sup> InP wafer by metal–organic vapor phase epitaxy. The In<sub>0.53</sub>Ga<sub>0.47</sub>As surface passivation prior to gate oxide deposition was an immersion in 10% (NH<sub>4</sub>)<sub>2</sub>S at room temperature for 20 min, which was found to be an optimum in terms of  $D_{\rm it}$  reduction and native oxide suppression [5], [6]. The transfer time to the atomic layer

Manuscript received November 21, 2011; revised January 13, 2012; accepted January 13, 2012. This work was supported by Science Foundation Ireland under FORME Strategic Research Cluster Award 07/SRC/I1172F. The review of this paper was arranged by Editor A. Haque.

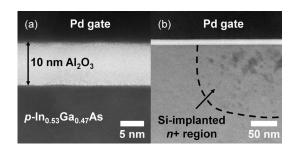

Fig. 2. Cross-sectional TEM images (a) through the gate stack region of the MOSFET confirming the 10-nm  $Al_2O_3$  gate oxide thickness and (b) through the gate overlap region, showing the implant defects in the Si-implanted  $n^+$  region.

deposition (ALD) reactor after surface passivation was less than 5 min. A 10-nm-thick Al<sub>2</sub>O<sub>3</sub> gate oxide film was formed by ALD using alternating pulses of  $Al(CH_3)_3$  (TMA) and H<sub>2</sub>O precursors at 250 °C. The source and drain (S/D) regions were selectively implanted with a Si dose of  $1 \times 10^{14}$  /cm<sup>2</sup> at 80 keV and  $1 \times 10^{14}$  /cm<sup>2</sup> at 30 keV. Implant activation was achieved by rapid thermal annealing at 600 °C for 15 s in a N<sub>2</sub> atmosphere. A 140-nm-thick SiO<sub>2</sub> field oxide was formed by electron-beam evaporation and liftoff to minimize the gate pad capacitance. Nonself-aligned ohmic contacts were defined by lithography, selective wet etching of Al<sub>2</sub>O<sub>3</sub> in dilute HF, and electron-beam evaporation of a Au (14 nm)/Ge (14 nm)/Au (14 nm)/Ni (11 nm)/Au (200 nm) metal stack [19]. A 200-nmthick Pd gate was defined by electron-beam evaporation and liftoff. Forming gas  $(5\% H_2/95\% N_2)$  annealing was carried out at 300 °C for 30 min in an open tube furnace. Tests confirmed the absence of delamination of the Pd metal following FGA.

The finished devices had a nominal gate length (L) of 1, 2, 3, 5, 10, 20, and 40  $\mu$ m with a 1.5- $\mu$ m gate metal overlap on the Si-implanted S/D regions, a 4- $\mu$ m gate-contact-to-sourceor drain-contact separation, and a 50- $\mu$ m gate width. Relatively long-channel-length MOSFETs were intentionally selected to allow the effect of the FGA process on the electrical properties to be examined in the absence of short-channel effects.

#### **III. RESULTS AND DISCUSSION**

## A. TEM Analysis of Gate Stack and Si-Implanted Regions

Cross-sectional transmission electron microscopy (TEM) images through the gate stack region and through the gate overlap region at the end of the MOSFET fabrication are shown in Fig. 2(a) and (b), respectively. Fig. 2(a) confirms the 10-nm Al<sub>2</sub>O<sub>3</sub> film thickness, which corresponds to the nominal value from the ALD process and a growth rate per cycle of 1 Å/cycle. There is no evidence of an interface oxide between the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface and the Al<sub>2</sub>O<sub>3</sub> film, consistent with previous reports for the optimized (NH<sub>4</sub>)<sub>2</sub>S process and subsequent ALD Al<sub>2</sub>O<sub>3</sub> formation [5], and with the reported "self-cleaning" effect of Al<sub>2</sub>O<sub>3</sub> formed by ALD on GaAs [20] and In<sub>0.15</sub>Ga<sub>0.85</sub>As [21] surfaces. Fig. 2(b) shows the remaining implant defects in the gate overlap region after activation anneal and FGA, indicating that these two anneals are not sufficient to fully remove the defects caused by the Si implantation process.

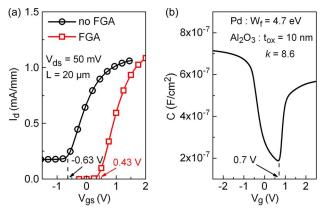

Fig. 3. (a)  $I_d-V_{gs}$  obtained on 20- $\mu$ m-gate-length and 50- $\mu$ m-gate-width MOSFETs at  $V_{ds} = 50 \text{ mV}$  before and after FGA. The MOSFETs feature a  $V_t$  of -0.63 and 0.43 V before and after FGA, respectively. (b) Quasi-static C-V simulation of the Pd/Al<sub>2</sub>O<sub>3</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stack obtained using a Poisson–Schrödinger simulator [22]. The ideal  $V_t$  of 0.7 V was obtained based on a Pd work function of 4.7 eV [24], a 10-nm-thick Al<sub>2</sub>O<sub>3</sub> film with a k-value of 8.6, and a p-In<sub>0.53</sub>Ga<sub>0.47</sub>As doping level of  $4 \times 10^{17}$  /cm<sup>3</sup>.

# B. Fixed Oxide Charge Passivation, Threshold Voltage Shift, OFF-State Leakage, and Subthreshold Swing Reduction

Fig. 3(a) shows the  $I_d - V_{gs}$  characteristics at  $V_{ds} =$ 50 mV obtained on 20- $\mu$ m-gate-length and 50- $\mu$ m-gate-width MOSFETs before and after FGA. The threshold voltage  $(V_t)$ shifts from -0.63 V before FGA to 0.43 V after FGA. The negative  $V_t$  before FGA indicates the presence of fixed positive charges within the Al<sub>2</sub>O<sub>3</sub>. Fig. 3(b) shows the quasistatic capacitance versus voltage (C-V) simulation of the  $Pd/Al_2O_3/p-In_{0.53}Ga_{0.47}As$  gate stack obtained using a selfconsistent Poisson-Schrödinger simulator [22]. The asymmetric shape of the simulated quasi-static C-V response, due to the very low density of states of the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band, is not experimentally observed. This absence of asymmetry has been attributed to the presence of additional interface defect states in the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band [23]. In the simulation, the work function  $(W_f)$ of Pd on  $Al_2O_3$ , the thickness ( $t_{ox}$ ) and k-value of the  $Al_2O_3$  film, and the  $p\text{-}In_{0.53}Ga_{0.47}As$  doping level were set to 4.7 eV [24], 10 nm, 8.6,<sup>1</sup> and  $4 \times 10^{17}$  /cm<sup>3</sup>, respectively. Considering an ideal  $V_t$  of 0.7 V [see Fig. 3(b)] and an oxide capacitance ( $C_{\rm ox}$ ) of 7.6 × 10<sup>-7</sup> F/cm<sup>2</sup>, we calculated an equivalent density of fixed positive oxide charge at the Al<sub>2</sub>O<sub>3</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As interface before and after FGA of  $6.3 \times 10^{12}$  /cm<sup>2</sup> and  $1.3 \times 10^{12}$  /cm<sup>2</sup>, respectively. Recent studies of  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOSCAPs over n- and p-In<sub>0.53</sub>Ga<sub>0.47</sub>As prior to FGA reported fixed positive oxide charge densities of  $\sim 1 \times 10^{19}$  /cm<sup>3</sup> distributed throughout the Al<sub>2</sub>O<sub>3</sub> layer [16]. A density of  $\sim 1 \times 10^{19}$  /cm<sup>3</sup> throughout a 10-nm-thick Al<sub>2</sub>O<sub>3</sub> film corresponds to an equivalent surface density at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface of  $\sim$  $1 \times 10^{13}$  /cm<sup>2</sup>, which is in close agreement with our pre-FGA value of  $6.3 \times 10^{12}$  /cm<sup>2</sup>. The reduction in the fixed positive oxide charge after FGA is also in agreement with [16] and [17].

<sup>&</sup>lt;sup>1</sup>The *k*-value of 8.6 for Al<sub>2</sub>O<sub>3</sub> was obtained from the slope of the capacitance equivalent thickness in accumulation versus the oxide thickness for Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS structures with Al<sub>2</sub>O<sub>3</sub> thicknesses ranging from 5 to 20 nm.

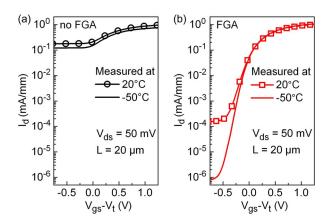

Fig. 4. Comparison of the 20 °C and -50 °C log  $I_d-V_{gs}$  measured at  $V_{ds} = 50$  mV on 20- $\mu$ m-gate-length and 50- $\mu$ m-gate-width MOSFETs (a) before and (b) after FGA. The log  $I_d-V_{gs}$  values are shown with matched gate overdrive  $(V_{gs} - V_t)$ .

The origin of the fixed positive charge has been assigned to Al dangling bonds based on theoretical modeling [17], and its reduction following FGA is consistent with hydrogen passivation of the dangling bond sites in  $Al_2O_3$ .

The fixed charge within the Al<sub>2</sub>O<sub>3</sub> gate oxide can have a significant impact on the MOSFET behavior. We calculated that, for a  $4 \times 10^{17}$  /cm<sup>3</sup> p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As doping, fixed positive charge densities in excess of  $2 \times 10^{12}$  /cm<sup>2</sup> are sufficient to create an inversion layer at the Al<sub>2</sub>O<sub>3</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As interface.<sup>2</sup> This indicates that the fixed positive oxide charge density of  $6.3 \times 10^{12}$  /cm<sup>2</sup> before FGA is sufficient to invert the p-In\_{0.53}Ga\_{0.47}As surface, whereas the fixed positive oxide charge density of  $1.3\times10^{12}~/cm^2$  after FGA is not. The strong inversion layer before FGA can be modulated in the region under the Pd gate. However, this inversion charge is also present in the region outside the area defined by the gate and is subsequently referred to as the "peripheral inversion region." We suggest that the high OFF-state leakage and poor subthreshold swing (SS) of the MOSFET before FGA [see Fig. 4(a)] are due to the presence of a peripheral inversion region that cannot be controlled by the gate voltage. The log  $I_d$ - $V_{qs}$  characteristics measured at 20 °C and -50 °C before FGA [see Fig. 4(a)] reveals that the OFF-state leakage ( $I_d$  at  $V_{gs} - V_t < 0$  V) is only weakly temperature dependent, which further indicates that the OFF-state leakage before FGA is due to the peripheral inversion region. It is noted that the formation of a peripheral inversion depends on the substrate doping concentration, the oxide capacitance, and the density and sign of the fixed oxide charge. Moreover, a high leakage current due to a peripheral inversion region will not be observed on a "ringgate" MOSFET, where the gate encircles the drain and obviates the need for isolation [26]. Fig. 4(b) shows an OFF-state leakage reduction of three orders of magnitude  $(I_{\rm on}/I_{\rm off} \sim 10^4)$  due to the removal of the peripheral inversion region following

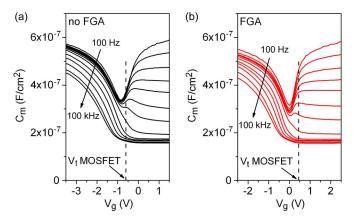

Fig. 5. Multifrequency C-V characteristics of Pd/Al<sub>2</sub>O<sub>3</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSCAPs measured from 100 Hz to 100 kHz (a) before and (b) after FGA. The  $V_t$  of the corresponding MOSFETs is highlighted on the C-V characteristics.

FGA. The temperature dependence of the OFF-state leakage after FGA is evident, and the  $I_{\rm on}/I_{\rm off}$  ratio at -50 °C is  $\sim 10^6$ .

Following FGA, a reasonable SS of 150 mV/dec is obtained. This SS yields a midgap  $D_{\rm it}$  value of  $\sim 5.8 \times 10^{12}$  /cm<sup>2</sup> · eV, which is consistent with our previous work on In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSCAPs fabricated with the same surface passivation, transfer time to the ALD reactor after surface passivation, and Al<sub>2</sub>O<sub>3</sub> gate oxide [5]. Moreover, the midgap  $D_{\rm it}$  value of  $\sim 5.8 \times 10^{12}$  /cm<sup>2</sup> · eV is in the range typically reported for high- $k/In_{0.53}Ga_{0.47}As$  MOSCAPs [27] and MOSFETs [28]. It is noted that, for the pre-FGA case, the SS is dominated by the peripheral leakage current and cannot be used for interface state density determination.

# C. MOSCAPs Behavior and Density of Interface States

Fig. 5(a) and (b) shows the multifrequency C-V characteristics of Pd/Al<sub>2</sub>O<sub>3</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSCAPs before and after FGA. The MOSCAPs are adjacent to the MOSFETs. The passivation of fixed positive charges within the Al<sub>2</sub>O<sub>3</sub> after FGA results in a voltage shift of the C-V characteristics, consistent with the voltage shift observed on the  $I_d-V_{gs}$  characteristics shown in Fig. 3(a). The comparison of the 100-Hz C-V responses at the onset of inversion shows a steeper slope after FGA, indicating a  $D_{it}$  reduction near the p-In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band, consistent with [18].

There has been debate over the expected C-V response of In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSCAPs in inversion and the method to identify genuine surface inversion [27]. The availability of the MOSCAPs and adjacent MOSFETs on the same wafer allows the  $V_t$  obtained from the MOSFETs to be identified on the multifrequency C-V response of the MOSCAPs. Fig. 5(a) and (b) show that, beyond inversion ( $V_g > V_t$ ), the capacitance as a function of applied voltage increases and then acquires an approximately constant value. The value of the capacitance in inversion increases with decreasing ac signal frequency up to a maximum value set by the oxide capacitance. This frequencydependent C-V behavior has been also obtained following an optimized (NH<sub>4</sub>)<sub>2</sub>S treatment of n- and p-In<sub>0.53</sub>Ga<sub>0.47</sub>As prior to ALD Al<sub>2</sub>O<sub>3</sub> deposition [7].

$<sup>^2</sup> For~a$  doping concentration of  $4 \times 10^{17}~/cm^3$ , the maximum depletion width for  $In_{0.53}Ga_{0.47}As$  is 50 nm (where the intrinsic carrier concentration for  $In_{0.53}Ga_{0.47}As$  is taken as  $6.3 \times 10^{11}~/cm^3$  [25]). Hence, the total density of charge resulting from the ionized acceptor at the onset of inversion is  $2 \times 10^{12}~/cm^2$ . Positive oxide charge densities in  $Al_2O_3$  in excess of  $2 \times 10^{12}~/cm^2$  will result in inversion of the p-In\_{0.53}Ga\_{0.47}As surface.

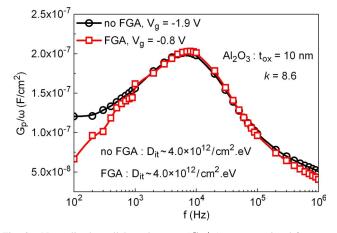

Fig. 6. Normalized parallel conductance  $(G_p/\omega)$  versus ac signal frequency (f) obtained with the conductance method for a 10-nm-thick Al<sub>2</sub>O<sub>3</sub> film with a *k*-value of 8.6 and considering the nonzero deviation in the semiconductor band bending [29], [30]. The midgap  $D_{\rm it}$  before and after FGA is ~ 4.0 ×  $10^{12}$  /cm<sup>2</sup> · eV.

Fig. 6 shows the normalized parallel conductance  $(G_p/\omega)$  versus ac signal frequency (f) for a selected gate voltage giving the peak  $G_p/\omega$ , before and after FGA. The peak  $G_p/\omega$  was observed for a  $V_g$  of -1.9 V before FGA and -0.8 V after FGA, corresponding to a  $V_g - V_t$  of  $\sim -1.25$  V before and after FGA. The conductance method accounting for the nonzero deviation in the semiconductor band bending [29], [30] was applied for the extraction of the values of midgap  $D_{it}$  and trap response time  $(\tau)$ . FGA did not reduce the midgap  $D_{it}$  and after FGA. Moreover, the midgap  $D_{it}$  value obtained from the conductance method is in reasonable agreement with the midgap  $D_{it}$  value of  $\sim 5.8 \times 10^{12} / \text{cm}^2 \cdot \text{eV}$  extracted from the SS of the MOSFETs post FGA. FGA did not have a significant impact on  $\tau$  as values of  $\sim 48.5$  and  $\sim 43.8 \ \mu\text{s}$  were obtained before and after FGA, respectively.

# D. Transconductance, Drive Current, and Effective Mobility Improvement

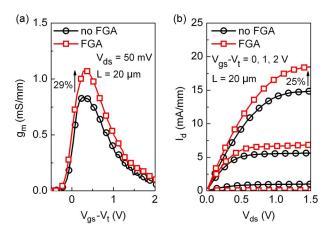

Fig. 7(a) compares the transconductance  $(g_m)$  versus gate overdrive  $(V_{gs} - V_t)$  obtained on 20- $\mu$ m-gate-length and 50- $\mu$ m-gate-width MOSFETs before and after FGA. Whereas the peak  $g_m$  increases by 29% after FGA, the higher field values of  $g_m$  only slightly improve with FGA.

Fig. 7(b) compares the  $I_d-V_{ds}$  output characteristics of 20- $\mu$ m-gate-length and 50- $\mu$ m-gate-width MOSFETs before and after FGA. The MOSFETs exhibit well-behaved output characteristics with drain current saturation for  $V_{ds} > V_{gs} - V_t$ . The drive current at a 2-V gate overdrive was 14.8 mA/mm before FGA and 18.5 mA/mm after FGA, representing a 25% improvement with FGA. These drive current values are comparable with, or slightly higher than, other published values for surface-channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs [9], [31], assuming drive current scaling with 1/L.

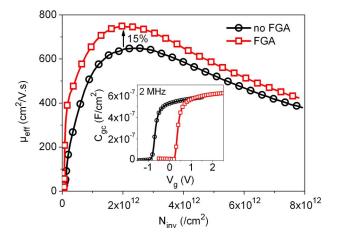

Fig. 8 shows the effective mobility ( $\mu_{eff}$ ) as a function of the inversion charge density ( $N_{inv}$ ) extracted using the  $I_d-V_{gs}$  characteristics [see Fig. 3(a)] and the 2-MHz gate-tochannel split C-V characteristics (see the inset in Fig. 8). The parasitic overlap capacitances were removed from the

Fig. 7. (a) Transconductance  $(g_m)$  versus gate overdrive  $(V_{gs} - V_t)$  and (b)  $I_d-V_{ds}$  characteristics obtained on 20- $\mu$ m-gate-length and 50- $\mu$ m-gate-width MOSFETs before and after FGA. After FGA, the peak  $g_m$  and drive current increase by 29% and 25%, respectively.

Fig. 8. Effective mobility ( $\mu_{\rm eff}$ ) versus inversion charge density ( $N_{\rm inv}$ ) before and after FGA. The peak  $\mu_{\rm eff}$  increases by 15% after FGA. (Inset) 2-MHz gate-to-channel  $C_{gc}$  split C-V characteristics before and after FGA.

measured gate-to-channel capacitance  $(C_{gc})$  using the method reported in [32]. MOSFETs with L ranging from 1 to 40  $\mu$ m were used to extract the S/D resistance  $(R_{sd})$  values used in the mobility correction.  $R_{sd}$  values were evaluated at  $V_{ds} =$ 50 mV to ensure device operation in the linear region. The MOSFETs featured a  $R_{sd}$  of 235 and 103  $\Omega$  before and after FGA, respectively. The peak  $\mu_{\rm eff}$  increased from 650 to 750  $\text{cm}^2/\text{V} \cdot \text{s}$  with FGA. This 15% improvement in the peak  $\mu_{\text{eff}}$  after FGA is consistent with a reduction of the positive fixed charge density in the Al<sub>2</sub>O<sub>3</sub> gate oxide along with a reduction of  $D_{it}$  at the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interface near the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band. The peak  $\mu_{\text{eff}}$  after FGA is comparable with other published values for Al<sub>2</sub>O<sub>3</sub>-gate surface-channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs, where the following peak  $\mu_{\rm eff}$  values are reported: 725 cm<sup>2</sup>/V · s for a 10-nmthick Al<sub>2</sub>O<sub>3</sub> gate oxide and  $1 \times 10^{17}$  /cm<sup>3</sup> p-type doping in the  $In_{0.53}Ga_{0.47}As$  channel region [9], 847 cm<sup>2</sup>/V · s for a 9-nm-thick  $Al_2O_3$  gate oxide and  $2 \times 10^{16}$  /cm<sup>3</sup> p-type doping in the In<sub>0.53</sub>Ga<sub>0.47</sub>As channel region [31], and 1100 cm<sup>2</sup>/V  $\cdot$  s for a 8-nm-thick Al<sub>2</sub>O<sub>3</sub> gate oxide and  $1 \times 10^{17}$  /cm<sup>3</sup> p-type doping in the  $In_{0.53}Ga_{0.47}As$  channel region [33]. It is noted that, for the comparative publications cited above, the

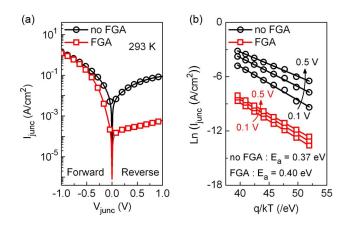

Fig. 9. (a) I-V characteristics of the n<sup>+</sup>/p In<sub>0.53</sub>Ga<sub>0.47</sub>As junction measured at 293 K before and after FGA. (b) Arrhenius plot from 223 to 293 K for reverse bias going from 0.1 to 0.5 V applied to implanted n<sup>+</sup>/p junctions before and after FGA. The area of the n<sup>+</sup>/p junction diodes is 10<sup>4</sup>  $\mu$ m<sup>2</sup>. The activation energy ( $E_a$ ) values are 0.37 and 0.40 eV before and after FGA, respectively.

$In_{0.53}Ga_{0.47}As$  channel doping was 4–20 times lower than the value of  $4 \times 10^{17}$  /cm<sup>3</sup> used in this paper.

The published experimental values for the peak  $\mu_{eff}$  in surface-channel inversion-mode In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs remain well below the theoretical values expected for reasonable values of fixed oxide charge, interface states, and surface roughness, where peak values of  $\sim 4000~\text{cm}^2/\text{V}\cdot\text{s}$  are calculated [34]. This discrepancy could relate to the approach typically employed to determine  $\mu_{\text{eff}}$ . Indeed, for the calculation of  $N_{\rm inv}$  on the x-axis in Fig. 8, it is assumed that the integral of  $C_{qc}$  above the threshold voltage yields  $N_{inv}$  and is unaffected by trapped charges in interface states or in bulk oxide traps. A number of recent publications have provided evidence that interface states exist with energies aligned with the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band [18], [23], [35]. In this case, the integral of  $C_{gc}$  will contain contributions from both trapped and free charges, which will result in an overestimation of  $N_{inv}$ and a corresponding underestimation of  $\mu_{\rm eff}$ . No corrections for the effect of bulk oxide charge trapping or interface states with energies aligned with the  $In_{0.53}Ga_{0.47}As$  conduction band have been applied in this paper, in line with the majority of literature to date [9], [31], [33].

#### E. Junction Leakage Reduction

FGA also improves the current–voltage behavior of the source- or drain-to-substrate  $In_{0.53}Ga_{0.47}As n^+/p$  junctions. Fig. 9(a) shows the current density versus voltage (I-V) characteristics for the  $n^+/p$  junctions before and after FGA. The saturation current in reverse bias is reduced by more than two orders of magnitude as a result of FGA. The measurement temperature (223–293 K) and applied bias (0.1–0.5 V) dependence of the  $n^+/p$  junction characteristics before and after FGA is shown in Fig. 9(b). The activation energy ( $E_a$ ) extrapolated to zero bias from Fig. 9(b) yields values of 0.37 and 0.40 eV before and after FGA, respectively. The extracted  $E_a$  indicates thermal generation of electron–hole pairs through midgap states in the  $In_{0.53}Ga_{0.47}As$  depletion region as the mechanism of the reverse bias leakage both before and after FGA. The reduction of leakage current density is consistent with the passivation of

midgap states by FGA. Both before and after FGA,  $E_a$  decreases with increasing reverse bias, which is characteristic of a field-enhanced (Poole–Frenkel)-type emission process [36].

## **IV. CONCLUSION**

We have demonstrated that a FGA  $(5\%H_2/95\%N_2)$  at 300 °C for 30 min dramatically improved the performance of surfacechannel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs with Al<sub>2</sub>O<sub>3</sub> as the gate dielectric. The FGA process reduced the density of fixed positive charges in Al<sub>2</sub>O<sub>3</sub>, which removed a parasitic peripheral inversion region and resulted in an increase in  $I_{\rm on}/I_{\rm off}$  by three orders of magnitude. FGA improved the peak  $g_m$ , drive current, and peak  $\mu_{\text{eff}}$  by 29%, 25%, and 15%, respectively. Multifrequency C-V measurements of MOSCAPs revealed that FGA reduced the  $D_{it}$  value near the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band but did not reduce the midgap  $D_{it}$  value. The reduction of the fixed positive charge in the gate oxide combined with the reduction of  $D_{it}$  near the In<sub>0.53</sub>Ga<sub>0.47</sub>As conduction band is consistent with the peak  $\mu_{\rm eff}$  improvement. A reduction of two orders of magnitude was observed in the reverse bias leakage current density in the Si-implanted  $In_{0.53}Ga_{0.47}As n^+/p$ junctions in the S/D regions of the MOSFETs, consistent with the passivation of near midgap defects in the  $In_{0.53}Ga_{0.47}As$ by FGA.

## ACKNOWLEDGMENT

The authors would like to thank Y. Y. Gomeniuk of the Lashkaryov Institute of Semiconductor Physics, Ukraine, for the unpublished experimental determination of the k-value of Al<sub>2</sub>O<sub>3</sub>.

#### REFERENCES

- [1] M. Yokoyama, R. Iida, S. Kim, N. Taoka, Y. Urabe, H. Takagi, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, and S. Takagi, "Sub-10-nm extremely thin body InGaAson-insulator MOSFETs on Si wafers with ultrathin Al<sub>2</sub>O<sub>3</sub> buried oxide layers," *IEEE Electron Device Lett.*, vol. 32, no. 9, pp. 1218–1220, Sep. 2011.

- [2] H.-C. Chin, X. Liu, X. Gong, and Y.-C. Yeo, "Silane and ammonia surface passivation technology for high-mobility In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs," *IEEE Trans. Electron Devices*, vol. 57, no. 5, pp. 973–979, May 2010.

- [3] U. Singisetti, M. A. Wistey, G. J. Burek, A. K. Baraskar, B. J. Thibeault, A. C. Gossard, M. J. W. Rodwell, B. Shin, E. J. Kim, P. C. McIntyre, B. Yu, Y. Yuan, D. Wang, Y. Taur, P. Asbeck, and Y.-J. Lee, "In<sub>0.53</sub>Ga<sub>0.47</sub>As channel MOSFETs with self-aligned InAs source/drain formed by MEE regrowth," *IEEE Electron Device Lett.*, vol. 30, no. 11, pp. 1128–1130, Nov. 2009.

- [4] N. Goel, D. Heh, S. Koveshnikov, I. Ok, S. Oktyabrsky, V. Tokranov, R. Kambhampatic, M. Yakimov, Y. Sun, P. Pianetta, C. K. Gaspe, M. B. Santos, J. Lee, S. Datta, P. Majhi, and W. Tsai, "Addressing the gate stack challenge for high mobility In<sub>x</sub>Ga<sub>1-x</sub>As channels for NFETs," in *IEDM Tech. Dig.*, 2008, pp. 1–4.

- [5] É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, "A systematic study of (NH<sub>4</sub>)<sub>2</sub>S passivation (22%, 10%, 5%, or 1%) on the interface properties of the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP system for n-type and p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial layers," J. Appl. Phys., vol. 109, no. 2, pp. 024 101-1–024 101-10, Jan. 2011.

- [6] B. Brennan, M. Milojevic, C. L. Hinkle, F. S. Aguirre-Tostado, G. Hughes, and R. M. Wallace, "Optimisation of the ammonium sulphide (NH<sub>4</sub>)<sub>2</sub>S passivation process on In<sub>0.53</sub>Ga<sub>0.47</sub>As," *Appl. Surf. Sci.*, vol. 257, no. 9, pp. 4082–4090, Feb. 2011.

- [7] É. O'Connor, S. Monaghan, K. Cherkaoui, I. M. Povey, and P. K. Hurley, "Analysis of the minority carrier response of n-type and

p-type Au/Ni/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As capacitors following optimized (NH<sub>4</sub>)<sub>2</sub>S treatment," *Appl. Phys. Lett.*, vol. 99, no. 21, pp. 212901-1–212901-3, Nov. 2011.

- [8] J. J. Gu, A. T. Neal, and P. D. Ye, "Effects of (NH<sub>4</sub>)<sub>2</sub>S passivation on the OFF-state performance of 3-dimensional InGaAs metal–oxide–semiconductor field-effect transistors," *Appl. Phys. Lett.*, vol. 99, no. 15, pp. 152113-1–152113-3, Oct. 2011.

- [9] A. M. Sonnet, C. L. Hinkle, M. N. Jivani, R. A. Chapman, G. P. Pollack, R. M. Wallace, and E. M. Vogel, "Performance enhancement of n-channel inversion type In<sub>x</sub>Ga<sub>1-x</sub>As metal-oxide-semiconductor field effect transistor using *ex situ* deposited thin amorphous silicon layer," *Appl. Phys. Lett.*, vol. 93, no. 12, pp. 122109-1–122109-3, Sep. 2008.

- [10] F. Zhu, H. Zhao, I. Ok, H. S. Kim, J. Yum, J. C. Lee, N. Goel, W. Tsai, C. K. Gaspe, and M. B. Santos, "Effects of anneal and silicon interface passivation layer thickness on device characteristics of In<sub>0.53</sub>Ga<sub>0.47</sub>As metal–oxide–semiconductor field-effect transistors," *Electrochem. Solid-State Lett.*, vol. 12, no. 4, pp. H131–H134, Mar. 2009.

- [11] A. O'Mahony, S. Monaghan, G. Provenzano, I. M. Povey, M. G. Nolan, É. O'Connor, K. Cherkaoui, S. B. Newcomb, F. Crupi, P. K. Hurley, and M. E. Pemble, "Structural and electrical analysis of the atomic layer deposition of HfO<sub>2</sub>/n – In<sub>0.53</sub>Ga<sub>0.47</sub>As capacitors with and without an Al<sub>2</sub>O<sub>3</sub> interface control layer," *Appl. Phys. Lett.*, vol. 97, no. 5, pp. 052904-1–052904-3, Aug. 2010.

- [12] S. Monaghan, A. O'Mahony, K. Cherkaoui, É. O'Connor, I. M. Povey, M. G. Nolan, D. O'Connell, M. E. Pemble, P. K. Hurley, G. Provenzano, F. Crupi, and S. B. Newcomb, "Electrical analysis of three-stage passivated In<sub>0.53</sub>Ga<sub>0.47</sub>As capacitors with varying HfO<sub>2</sub> thicknesses and incorporating an Al<sub>2</sub>O<sub>3</sub> interface control layer," *J. Vac Sci. Technol. B*, vol. 29, no. 1, pp. 01A807-1–01A807-8, Jan. 2011.

- [13] M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and R. Chau, "Advanced high-k gate dielectric for high-performance short-channel In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well field effect transistors on silicon substrate for low power logic applications," in *IEDM Tech. Dig.*, 2009, pp. 1–4.

- [14] A. Stesmans and V. V. Afanas'ev, "Si dangling-bond-type defects at the interface of (100)Si with ultrathin layers of SiO<sub>x</sub>, Al<sub>2</sub>O<sub>3</sub>, and ZrO<sub>2</sub>," *Appl. Phys. Lett.*, vol. 80, no. 11, pp. 1957–1959, Mar. 2002.

- [15] R. J. Carter, E. Cartier, A. Kerber, L. Pantisano, T. Schram, S. De Gendt, and M. Heyns, "Passivation and interface state density of SiO<sub>2</sub>/HfO<sub>2</sub>based/polycrystalline-Si gate stacks," *Appl. Phys. Lett.*, vol. 83, no. 3, pp. 533–535, Jul. 2003.

- [16] R. D. Long, B. Shin, S. Monaghan, K. Cherkaoui, J. Cagnon, S. Stemmer, P. C. McIntyre, and P. K. Hurley, "Charged defect quantification in Pt/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitors," *J. Electrochem. Soc.*, vol. 158, no. 5, pp. G103–G107, Mar. 2011.

- [17] B. Shin, J. R. Weber, R. D. Long, P. K. Hurley, C. G. Van de Walle, and P. C. McIntyre, "Origin and passivation of fixed charge in atomic layer deposited aluminum oxide gate insulators on chemically treated InGaAs substrates," *Appl. Phys. Lett.*, vol. 96, no. 15, pp. 152908-1–152908-3, Apr. 2010.

- [18] É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev, and P. K. Hurley, "Temperature and frequency dependent electrical characterization of HfO<sub>2</sub>/In<sub>x</sub>Ga<sub>1-x</sub>As interfaces using capacitance-voltage and conductance methods," *Appl. Phys. Lett.*, vol. 94, no. 10, pp. 102902-1–102902-3, Mar. 2009.

- [19] P. A. F. Herbert, L. P. Floyd, J. I. Braddell, E. M. Baldwin, and W. M. Kelly, "The application of ohmic contacts to nanometric structures," *Microelectron. Eng.*, vol. 17, no. 1–4, pp. 541–545, Mar. 1992.

- [20] M. M. Frank, G. D. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y. J. Chabal, J. Grazul, and D. A. Muller, "HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics on GaAs grown by atomic layer deposition," *Appl. Phys. Lett.*, vol. 86, no. 15, pp. 152904-1–152904-3, Apr. 2005.

- [21] M. L. Huang, Y. C. Chang, C. H. Chang, Y. J. Lee, P. Chang, J. Kwo, T. B. Wu, and M. Hong, "Surface passivation of III–V compound semiconductors using atomic-layer-deposition-grown Al<sub>2</sub>O<sub>3</sub>," *Appl. Phys. Lett.*, vol. 87, no. 25, pp. 252104-1–252104-3, Dec. 2005.

- [22] [Online]. Available: http://www.nd.edu/~gsnider/

- [23] G. Brammertz, H.-C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, "On the interface state density at In<sub>0.53</sub>Ga<sub>0.47</sub>As/oxide interfaces," *Appl. Phys. Lett.*, vol. 95, no. 20, pp. 202109-1–202109-3, Nov. 2009.

- [24] A. Diligenti and M. Stagi, "Tunnelling in aluminium/aluminiumoxide/palladium junctions: Hydrogen-induced variations," *Electron. Lett.*, vol. 19, no. 18, pp. 717–718, Sep. 1983.

- [25] [Online]. Available: www.ioffe.ru

- [26] F. Zhu, H. Zhao, I. Ok, H. S. Kim, J. Yum, J. C. Lee, N. Goel, W. Tsai, C. K. Gaspe, and M. B. Santos, "A high performance In<sub>0.53</sub>Ga<sub>0.47</sub>As metal–oxide–semiconductor field effect transistor with silicon interface passivation layer," *Appl. Phys. Lett.*, vol. 94, no. 1, pp. 013511-1– 013511-3, Jan. 2009.

- [27] R. Engel-Herbert, Y. Hwang, and S. Stemmer, "Comparison of methods to quantify interface trap densities at dielectric/III–V semiconductor interfaces," *J. Appl. Phys.*, vol. 108, no. 12, pp. 124101-1–124101-15, Dec. 2010.

- [28] A. Ali, H. Madan, S. Koveshnikov, S. Oktyabrsky, R. Kambhampati, T. Heeg, D. Schlom, and S. Datta, "Small-signal response of inversion layers in high-mobility In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs made with thin high-*K* dielectrics," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 742–748, Apr. 2010.

- [29] E. H. Nicollian and J. R. Brews, MOS Physics and Technology. New York: Wiley, 1982, pp. 212–218.

- [30] E. H. Nicollian and A. Goetzberger, "The Si-SiO<sub>2</sub> interface—Electrical properties as determined by the metal-insulator-silicon conductance technique," *Bell Syst. Tech. J.*, vol. 46, no. 6, pp. 1055–1133, Jul. 1967.

- [31] H. Zhao, F. Zhu, Y.-T. Chen, J. H. Yum, Y. Wang, and J. C. Lee, "Effect of channel doping concentration and thickness on device performance for In<sub>0.53</sub>Ga<sub>0.47</sub>As metal–oxide–semiconductor transistors with atomiclayer-deposited Al<sub>2</sub>O<sub>3</sub> dielectrics," *Appl. Phys. Lett.*, vol. 94, no. 9, pp. 093505-1–093505-3, Mar. 2009.

- [32] K. Romanjek, F. Andrieux, T. Ernst, and G. Ghibaudo, "Improved split C-V method for effective mobility extraction in sub-0.1-µm Si MOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 8, pp. 583–585, Aug. 2004.

- [33] Y. Xuan, Y. Q. Wu, H. C. Lin, T. Shen, and P. D. Ye, "Submicrometer inversion-type enhancement-mode InGaAs MOSFET with atomic-layerdeposited Al<sub>2</sub>O<sub>3</sub> as gate dielectric," *IEEE Electron Device Lett.*, vol. 28, no. 11, pp. 935–938, Nov. 2007.

- [34] T. P. O'Regan, M. V. Fischetti, B. Sorée, S. Jin, W. Magnus, and M. Meuris, "Calculation of the electron mobility in III–V inversion layers with high-κ dielectrics," J. Appl. Phys., vol. 108, no. 10, pp. 103705-1– 103705-11, Nov. 2010.

- [35] P. K. Hurley, R. D. Long, T. O'Regan, É. O'Connor, S. Monaghan, V. Djara, M. A. Negara, A. O'Mahony, I. M. Povey, A. Blake, R. E. Nagle, D. O'Connell, M. E. Pemble, and K. Cherkaoui, "Equivalent oxide thickness correction in the high-k/In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP system," *ECS Trans.*, vol. 33, no. 3, pp. 433–444, Oct. 2010.

- [36] S. D. Ganichev, E. Ziemann, W. Prettl, I. N. Yassievich, A. A. Istratov, and E. R. Weber, "Distinction between the Poole–Frenkel and tunneling models of electric-field-stimulated carrier emission from deep levels in semiconductors," *Phys. Rev. B*, vol. 61, no. 15, pp. 10361–10365, Apr. 2000.

Vladimir Djara (S'12) received the M.Sc. degree in physics with photonics from St. Andrews University, St. Andrews, U.K., in 2003 and the M.Eng. degree in electronics and optics from the University of Orléans, Orléans, France, in 2005. He is currently working toward the Ph.D. degree in the physics of n-channel III–V metal–oxide–semiconductor field-effect transistors in Tyndall National Institute, University College Cork, Cork, Ireland.

He has been a Process Engineer with Tyndall National Institute since 2005.

Karim Cherkaoui received the Ph.D. degree from the Institut National des Sciences Appliquées of Lyon, Lyon, France, in 1998.

During his Ph.D., he gained experience in the spectroscopy of point defects in semi-insulating materials. In 1999, he joined Tyndall National Institute, University College Cork, Cork, Ireland, where he has established and developed several low-temperature electrical metrology techniques. His current research interests include the process development and characterization of high dielectric constant materials on

Si and III-V materials for future MOS devices.

6

DJARA et al.: IMPACT OF FGA ON InGaAs MOSFETs WITH AN ALD GATE DIELECTRIC

Michael Schmidt received the M.Sc. degree in physics from Otto-von-Guericke-University, Magdeburg, Germany, in 1998. He is currently working toward the Ph.D. degree in the application of advanced electron microscopy on nanostructured materials in Tyndall National Institute, University College Cork, Cork, Ireland.

Since 2009, he has been an Electron Microscopy Technician with Tyndall National Institute, where his main responsibilities include transmission electron microscopy sample preparation and electron-beam

lithography.

Scott Monaghan (M'11) received the first-class honors degree in mathematics and physics from The Open University, Ireland, in 1999 and the M.Eng.Sc. and Ph.D. degrees in the area of materials science from the University College Cork, Cork, Ireland, in 2002 and 2007, respectively.

He currently specializes in the electrical characterization and modeling of devices primarily employing dielectrics deposited by atomic layer deposition. He has coauthored more than 20 technical papers in peer-reviewed international journals. He is the holder

of one patent. His scientific areas of interest are high dielectric constant materials and III–V semiconductors, metal–insulator–metal capacitors, and metal–oxide–semiconductor capacitors and field-effect transistors.

Éamon O'Connor received the B.E. and M.Eng.Sc. degrees in 2002 and 2005, respectively, from the University College Cork, Cork, Ireland, where he is currently working toward the Ph.D. degree in Tyndall National Institute.

His research is focused on the formation of devices employing high-*k* dielectric materials on high-mobility III–V compound semiconductors for future CMOS applications, particularly with regard to passivation and characterization of electrically active defects at the high-*k*/III–V interface.

Ian M. Povey received the B.Sc.(Hons.) degree in chemistry from the University of Manchester, Manchester, U.K., in 1989, the M.Sc. degree in environmental studies (engineering) from the University of Southampton, Southampton, U.K., in 2003, and the Ph.D. degree in "spectroscopic studies of III–V semiconductor growth mechanisms" from the University of Manchester in 1994.

In 2004, he was appointed to a Staff Research Scientist position with Tyndall National Institute, University College Cork, Cork, Ireland, where his

current research focuses on the chemical vapor deposition and atomic layer deposition of metals and metal oxides, studying aspects of process control, materials properties, and mechanisms of growth.

**Dan O'Connell** received the B.Sc. degree in physics, material science, and analog and digital electronics from The Open University, Ireland.

Since 1993, he has been a Senior Process Engineer with the III–V Laboratory, Tyndall National Institute, University College Cork, Cork, Ireland, where he is responsible for a wide range of thin-film deposition and patterning processes.

Martyn E. Pemble received the B.Sc. and Ph.D. degrees from the University of Southampton, Southampton, U.K., in 1976 and 1981, respectively.

In 1995, he was appointed to the Chair of Physical Chemistry with the University of Salford, Manchester, U.K. In 2004, he was awarded a substantial grant by Science Foundation Ireland to work at Tyndall National Institute, University College Cork (UCC), Cork, Ireland, as an SFI Investigator, where he now heads the Advanced Materials and Surfaces Group. In November 2008, he was

appointed as the Stokes Professor of Materials Chemistry, a joint position between Tyndall National Institute and the UCC Chemistry Department. He has published more than 240 papers in peer-reviewed scientific journals and supervised 10 Master's and 37 Ph.D. students. His group studies the areas of chemical vapor deposition and atomic layer deposition, including the use of passivation of III–V semiconductors, the growth of high-*k* dielectrics for advanced CMOS applications, and the ALD growth of metals.

**Paul K. Hurley** received the B.Eng. degree (with first-class honors) and the Ph.D. degree in electronic engineering from the University of Liverpool, Liverpool, U.K., 1985 and 1990, respectively.

He is currently a Senior Research Scientist with Tyndall National Institute, University College Cork, Cork, Ireland. He leads a research team of approximately ten Ph.D. students, postdoctoral researchers, visiting students, and Tyndall Research staff who perform basic research on high-*k* thin films for applications in nanoelectronics, where the current

research work is focused on the use of high-*k* in conjunction with III–V semiconductor materials for future logic devices. In addition to research activities, he is a part-time Lecturer with the Department of Electrical Engineering, University College Cork. He has published more than 80 papers in the field of micro- and nanoelectronics and has given over 20 invited presentations and seminars in the high-*k* area from 2006 to 2010.

Dr. Hurley is a member of the Technical Committee of the Insulating Films on Semiconductors (INFOS) Conference and the International Workshop on Dielectrics in Microelectronics (WoDiM).