| Title                       | Examining the relationship between capacitance-voltage hysteresis and accumulation frequency dispersion in InGaAs metal-oxide-semiconductor structures based on the response to post-metal annealing                                                                                                                                                                          |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Authors                     | Lin, Jun;Monaghan, Scott;Cherkaoui, Karim;Povey, Ian<br>M.;Sheehan, Brendan;Hurley, Paul K.                                                                                                                                                                                                                                                                                   |  |  |  |

| Publication date            | 2017-05-13                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Original Citation           | Lin, J., Monaghan, S., Cherkaoui, K., Povey, I. M., Sheehan, B. and Hurley, P. K. (2017) 'Examining the relationship between capacitance-voltage hysteresis and accumulation frequency dispersion in InGaAs metal-oxide-semiconductor structures based on the response to post-metal annealing', Microelectronic Engineering, 178, pp. 204-208. doi:10.1016/j.mee.2017.05.020 |  |  |  |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Link to publisher's version | 10.1016/j.mee.2017.05.020                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Rights                      | © 2017, Elsevier Ltd. All rights reserved. This manuscript version is made available under the CC-BY-NC-ND 4.0 license http://creativecommons.org/licenses/by-nc-nd/4.0/                                                                                                                                                                                                      |  |  |  |

| Download date               | 2024-04-26 21:26:46                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Item downloaded from        | https://hdl.handle.net/10468/4601                                                                                                                                                                                                                                                                                                                                             |  |  |  |

### Accepted Manuscript

Examining the relationship between capacitance-voltage hysteresis and accumulation frequency dispersion in InGaAs metal-oxide-semiconductor structures based on the response to post-metal annealing

Town to the hydron State and State a

Jun Lin, Scott Monaghan, Karim Cherkaoui, Ian M. Povey, Brendan Sheehan, Paul K. Hurley

PII: S0167-9317(17)30217-4

DOI: doi: 10.1016/j.mee.2017.05.020

Reference: MEE 10573

To appear in: Microelectronic Engineering

Received date: 27 February 2017

Revised date: 9 May 2017

Accepted date: 10 May 2017

Please cite this article as: Jun Lin, Scott Monaghan, Karim Cherkaoui, Ian M. Povey, Brendan Sheehan, Paul K. Hurley, Examining the relationship between capacitance-voltage hysteresis and accumulation frequency dispersion in InGaAs metal-oxide-semiconductor structures based on the response to post-metal annealing, *Microelectronic Engineering* (2017), doi: 10.1016/j.mee.2017.05.020

This is a PDF file of an unedited manuscript that has been accepted for publication. As a service to our customers we are providing this early version of the manuscript. The manuscript will undergo copyediting, typesetting, and review of the resulting proof before it is published in its final form. Please note that during the production process errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

# Examining the relationship between capacitance-voltage hysteresis and accumulation frequency dispersion in InGaAs metal-oxide-semiconductor structures based on the response to post-metal annealing

Jun Lin, Scott Monaghan, Karim Cherkaoui, Ian M. Povey, Brendan Sheehan, and Paul K. Hurley *Tyndall National Institute, University College Cork, Cork, Ireland*

#### Abstract

In this work, we investigated the effect of forming gas annealing (FGA, 5%  $H_2/95\%$   $N_2$ , 250 °C to 450 °C) on border trap density in high-k/InGaAs metal-oxide-semiconductor (MOS) systems using accumulation frequency dispersion and capacitance-voltage (CV) hysteresis analysis. It is demonstrated that the optimum FGA temperature that reduces the accumulation frequency dispersion is 350 °C for  $HfO_2/n$ -InGaAs and 450 °C for  $Al_2O_3/n$ -InGaAs MOS system. Volume density of border traps ( $N_{bt}$ ) is estimated using the accumulation frequency dispersion based on a distributed model for border traps. It is shown that for  $HfO_2/n$ -InGaAs MOS system,  $N_{bt}$  is reduced from  $9.4\times10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> before FGA to  $6.3\times10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> following FGA at 350 °C. For the case of  $Al_2O_3/n$ -InGaAs MOS system,  $N_{bt}$  is reduced from  $5.7\times10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> for no FGA to  $3.4\times10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> for FGA at 450 °C. Furthermore, it is shown that the most pronounced reduction in border trap density estimated from CV hysteresis analysis is observed at the same optimum FGA temperature that reduces the accumulation frequency dispersion, indicating that these two techniques for border trap analysis are correlated.

Keywords – border traps; high-k; InGaAs; CV hysteresis; accumulation frequency dispersion; forming gas annealing

#### 1. Introduction

One of the main challenges facing the development of metal-oxide-semiconductor field effect transistors (MOSFETs) and Tunnel FETs based on InGaAs channels is the understanding and passivation of border traps which are predominantly located near the high-k/InGaAs interface layer and can exchange charges with the semiconductor bands via a tunnelling process [1, 2]. Border traps have now been understood to result in accumulation frequency dispersion in InGaAs MOS structures, leading to a drop in measured total capacitance (C<sub>tot</sub>) with frequency (ω) [3], and the impact of border traps is evident up to 1 GHz and beyond [4]. Border traps with relatively long time constants can also be manifest as capacitancevoltage (CV) hysteresis. In this work, we reported on the effect of forming gas annealing (FGA) on border trap density estimated from accumulation frequency dispersion and CV hysteresis in high-k/InGaAs MOS structures. Furthermore, we examined the correlation between accumulation frequency dispersion and CV hysteresis.

#### 2. Experimental

The samples used in this work were n-doped and p-doped InP (100) substrates with 2  $\mu$ m n-type (S at  $4\times10^{17}$  cm<sup>-3</sup>) and p-type (Zn at  $4\times10^{17}$  cm<sup>-3</sup>) In<sub>x</sub>Ga<sub>1-x</sub>As (x = 0.53) epitaxial layers, respectively, grown by metal organic vapour phase epitaxy (MOVPE). Prior to oxide deposition, all the samples were treated in the optimized 10% (NH<sub>4</sub>)<sub>2</sub>S passivation and then transferred to the atomic layer deposition (ALD) chamber within a minimum time (~ 3 min) as described in [5]. Either Al<sub>2</sub>O<sub>3</sub> or HfO<sub>2</sub> was deposited as the high-k oxide on the InGaAs surface. The Al<sub>2</sub>O<sub>3</sub> has a nominal thickness of 8 nm and was deposited by ALD at 300 °C using Al(CH<sub>3</sub>)<sub>3</sub> (TMA) and H<sub>2</sub>O. The HfO<sub>2</sub> has a nominal thickness of 8 nm and was

deposited by ALD at 250 °C using Hf[N(CH<sub>3</sub>)C<sub>2</sub>H<sub>5</sub>]<sub>4</sub> (TEMAH) and H<sub>2</sub>O. Ni(70 nm)/Au(90 nm) was used as the metal gate and was formed by electron beam evaporation and a lift-off process. Both the Au/Ni/Al<sub>2</sub>O<sub>3</sub>/InGaAs and Au/Ni/HfO<sub>2</sub>/InGaAs MOS capacitors were treated by post-metal FGA (5% H<sub>2</sub> / 95% N<sub>2</sub>) at a series of temperatures (250 °C, 300 °C, 350 °C, 400 °C and 450 °C) for 30 min, and one sample from each MOS structure was not treated by FGA as a control sample. Annealing after metal deposition is beneficial as the metal plays a role in dissociating H<sub>2</sub> into atomic H which is needed for the passivation of defects.

All the CV measurements were recorded at room temperature using an E4980 LCR meter. The CV hysteresis sweeps were measured starting from inversion and sweeping upwards to accumulation, and without a stress time, subsequently sweeping downwards to inversion. In addition, all CV hysteresis sweeps were recorded at 1 MHz in order to minimize the interface state responses. The surface charge trapping density is quantified using the equation

$Q_{trapped} = (\Delta V \times C_{ox})/q \qquad \qquad (1)$  where  $Q_{trapped}$  is the density of trapped charge in cm<sup>-2</sup>,  $\Delta V$  is the CV hysteresis in V,  $C_{ox}$  is the oxide capacitance in F/cm<sup>2</sup>, and q is the elementary charge in C. Equation (1) assumes the trapped charge is located at the high-k/InGaAs interface.

### 3. Results and Discussion

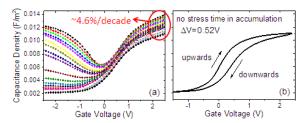

The multi-frequency (20 Hz to 1 MHz) CV characteristics for Au/Ni/HfO<sub>2</sub>(8nm)/n-InGaAs MOS structure (no FGA) and the corresponding CV hysteresis are illustrated in Fig. 1, demonstrating a large frequency dispersion of ~4.6%/decade estimated at the maximum voltage (V<sub>max</sub>) in accumulation and a surface border trap density (Q<sub>trapped</sub>) of  $5.9 \times 10^{12}$  cm<sup>-2</sup> from the CV hysteresis.

Fig. 1: (a) Multi-frequency (20 Hz to 1 MHz) CV characteristics, and the corresponding (b) CV hysteresis (1 MHz) for Au/Ni/HfO<sub>2</sub>(8nm)/n-InGaAs MOS capacitor with no FGA. The frequency dispersion estimated in accumulation (at  $V_{max} = 2.5 \text{ V}$ ) in (a) is ~4.6%/decade and the CV hysteresis ( $\Delta V$ ) in (b) corresponds to a surface trapping density of  $5.9 \times 10^{12} \text{ cm}^{-2}$ .

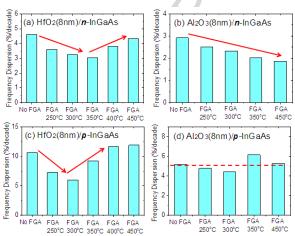

In order to reduce the density of border traps, which cause both accumulation frequency dispersion and CV hysteresis, FGA with a temperature series was performed. Accumulation frequency dispersion for HfO<sub>2</sub>(8nm)/n-InGaAs MOS structures treated by FGA temperature series is shown in Fig. 2 (a), illustrating that the accumulation frequency dispersion goes through a valley with the increasing FGA temperature, and the optimum FGA temperature (T<sub>opt</sub>) is observed to be 350 °C. The increase in frequency dispersion above 350 °C could be due to diffusion of As and In into the oxide, which is known to occur at  $\geq$ 350 °C [6, 7] and can create more oxide defects. For  $Al_2O_3(8nm)/n$ -InGaAs MOS structure, accumulation frequency dispersion decreases with increasing FGA temperature up to 450 °C as shown in Fig. 2 (b). This suggests that Al<sub>2</sub>O<sub>3</sub> can suppress elemental diffusion compared to HfO<sub>2</sub>. For the case of p-InGaAs, increase in accumulation frequency dispersion is also observed in HfO2(8nm)/p-InGaAs (Fig. 2 (c)) at higher FGA temperatures due to elemental diffusion, and for Al<sub>2</sub>O<sub>3</sub>(8nm)/p-InGaAs (Fig. 2 (d)), no clear trend is observed and the average frequency dispersion is ~5.2%/decade.

Fig. 2: Accumulation frequency dispersion for Au/Ni gate over (a) HfO<sub>2</sub>(8nm)/n-InGaAs, (b) Al<sub>2</sub>O<sub>3</sub>(8nm)/n-InGaAs, (c) HfO<sub>2</sub>(8nm)/p-InGaAs and (d) Al<sub>2</sub>O<sub>3</sub>(8nm)/p-InGaAs MOS capacitors treated by FGA temperature series. The Al<sub>2</sub>O<sub>3</sub> samples treated by FGA 400 °C exhibits non-regular behavior in terms of gate leakage and CV responses and are therefore omitted in the discussions.

Moreover, a significant accumulation frequency dispersion is observed in HfO<sub>2</sub>/p-InGaAs and Al<sub>2</sub>O<sub>3</sub>/p-InGaAs when compared to their *n*-type InGaAs counterparts. This indicates that the Fermi level movement is strongly restricted in the InGaAs lower bandgap and is even being pinned (especially for HfO<sub>2</sub>/InGaAs); therefore accumulation of holes is unlikely achieved. Hence, the discussion of border traps will be focused only on *n*-InGaAs.

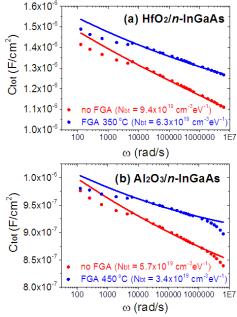

Based on a distributed model for border traps using the measured total capacitance (Ctot) and measured total conductance (Gtot) in accumulation as a function of frequency (\omega) [3], the volume density of border traps (N<sub>bt</sub>) is estimated for HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> n-type samples treated with the optimum FGA temperatures compared to the no FGA samples as shown in Fig. 3 ( $G_{tot}$  versus  $\omega$  not shown). The fitting was performed using equation (2) and the fitting parameters are listed in Table I. It is demonstrated that  $N_{\text{bt}}$  is reduced from  $9.4 \times 10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> to  $6.3 \times 10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> following FGA at 350 °C for HfO<sub>2</sub> sample, and N<sub>bt</sub> is reduced from  $5.7 \times 10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> to  $3.4 \times 10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> following FGA at 450 °C for Al<sub>2</sub>O<sub>3</sub> sample. Based on the model, border traps located ~ 1 nm to 2 nm into the oxide are probed under the frequency range investigated. The drop in capacitance below  $\omega = 6283$ rad/s (i.e. 1 kHz) for both HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> samples is possibly due to the effect of noise at low frequencies. Moreover, it is observed that for Al<sub>2</sub>O<sub>3</sub> sample in Fig. 3 (b) above 300 kHz the experimental data deviates from the fitting and exhibits a higher slope of Ctot versus  $\log(\omega)$ . This abrupt increase in the gradient of the capacitance versus log (\omega) at higher frequencies is consistent with the measurement frequency range probing the border trap population located at < 1 nm from the oxide/InGaAs interface, where very large N<sub>bt</sub> values (>  $1 \times 10^{21}$  cm<sup>-3</sup>eV<sup>-1</sup>) are reported [4]. It is noted that this high density of border traps located at < 1 nm from the oxide/InGaAs interface will also respond at all frequencies lower than 300 kHz. However, for frequencies of 300 kHz and below, there is no change in the response of these near interface border traps with reducing frequency, and consequently they are not manifest in the gradient  $C_{tot}$  versus  $log(\omega)$  from which N<sub>bt</sub> is determined. The abrupt change in gradient of C<sub>tot</sub> versus log(ω) above 300 kHz in the Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS is consistent with the sharp increase in N<sub>bt</sub> towards oxide/InGaAs interface in the HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/InGaAs gate stack reported in [4]. It is noted that this gradient change is not detected for the HfO<sub>2</sub>/InGaAs MOS structure within the measurement window (20 Hz to 1 MHz), indicating that the increase in N<sub>bt</sub> towards the oxide/InGaAs interface is not as large, or that the peak density is located outside the measurement window for the HfO<sub>2</sub>/InGaAs samples studied.

Fig. 3: Measured C<sub>tot</sub> versus frequency (solid symbols) for Au/Ni gate over (a) HfO<sub>2</sub>(8nm)/n-InGaAs and (b) Al<sub>2</sub>O<sub>3</sub>/(8nm)/n-InGaAs MOS. The fittings (solid lines) were performed based on the border trap model in [3].

Table I: Ref. [3] fitting parameters for Fig. 3 for HfO<sub>2</sub>/n-InGaAs and Al<sub>2</sub>O<sub>3</sub>/n-InGaAs MOS systems

| mount induits and migoria mounts with a systems |                            |                                               |                                          |                                                             |  |

|-------------------------------------------------|----------------------------|-----------------------------------------------|------------------------------------------|-------------------------------------------------------------|--|

| Sample /parameter                               | HfO <sub>2</sub><br>no FGA | HfO <sub>2</sub><br>FGA<br>350 <sup>o</sup> C | Al <sub>2</sub> O <sub>3</sub><br>no FGA | Al <sub>2</sub> O <sub>3</sub><br>FGA<br>450 <sup>o</sup> C |  |

| N <sub>bt</sub>                                 | 9.4×10 <sup>19</sup>       | 6.3×10 <sup>19</sup>                          | 5.7×10 <sup>19</sup>                     | 3.4×10 <sup>19</sup>                                        |  |

| tox (cm)                                        | 7.5×10 <sup>-7</sup>       | 7.5×10 <sup>-7</sup>                          | 7.38×10 <sup>-7</sup>                    | 7.38×10 <sup>-7</sup>                                       |  |

| $\kappa_{ox}$                                   | 12                         | 13.45                                         | 8.6                                      | 8.6                                                         |  |

| C <sub>s</sub><br>(F/cm <sup>2</sup> )          | 2.2×10 <sup>-6</sup>       | 4.2×10 <sup>-6</sup>                          | 3.4×10 <sup>-6</sup>                     | 6.5×10 <sup>-6</sup>                                        |  |

| m*                                              | 0.22                       | 0.22                                          | 0.23                                     | 0.23                                                        |  |

| E <sub>ox</sub> -E<br>(eV)                      | 1.5                        | 1.5                                           | 2.2                                      | 2.2                                                         |  |

| $\tau_0(s)$                                     | 2.9×10 <sup>-10</sup>      | 2.9×10 <sup>-10</sup>                         | 2.8×10 <sup>-10</sup>                    | 4.8×10 <sup>-11</sup>                                       |  |

$$\frac{dY}{dx} = -\frac{Y^2}{j\omega\kappa_{ox}\varepsilon_{0}} + \frac{q^2N_{bt}\ln(1+j\omega\tau_{0}e^{2(\sqrt{2m^*m_{0}(E_{ox}-E)}/\hbar)x})}{\tau_{0}e^{2(\sqrt{2m^*m_{0}(E_{ox}-E)}/\hbar)x}}$$

(2)

where Y(x): the equivalent admittance at a point x looking into the semiconductor,  $\omega$ : angular frequency,  $\kappa_{ox}$ : relative permittivity of the high-k oxide,  $\varepsilon_0$ : vacuum permittivity, q: elementary charge, border traps =  $N_{bt} \times (1/q)$  cm<sup>-3</sup>eV<sup>-1</sup>,  $m^*(m_0=9.11\times10^{-31}$  kg): effective mass of electron in the oxide,  $E_{ox}$  - E: energy level of border traps near  $E_C$  with respect to the energy of the top of the dielectric tunnelling barrier [8],  $\tau_0$ : time constant associated with the tunnelling process. The boundary condition is  $Y(x=0)=j\omega C_s$ , where  $C_s$ : InGaAs semiconductor capacitance. Equation (2) is solved from x=0 to  $x=t_{ox}$ , where  $t_{ox}$ : oxide thickness. Equation (2) is reproduced from [3] equation (7).

The effect of FGA on CV hysteresis ( $\Delta V$ ) was also analyzed based on a study of  $\Delta V$  (or  $Q_{trapped}$ ) versus overdrive voltage ( $V_{ov}$ ), where  $V_{ov} = V_{max} - V_{fb}$  and  $V_{fb}$  is the nominal flatband capacitance.  $Q_{trapped}$  versus  $V_{ov}$  is plotted in a log-log scale in Fig. 4 (a) for HfO<sub>2</sub>(8nm)/n-InGaAs and Fig. 4 (b) for

Al<sub>2</sub>O<sub>3</sub>(8nm)/n-InGaAs. The power law exponent is referred to as the voltage acceleration factor ( $\gamma$ -factor) [9, 10]. A higher  $\gamma$ -factor is required as this indicates a reduced trap density at operating voltage. The γ-factor and  $Q_{\text{trapped}}$  (at  $V_{\text{ov}}\!=2$  V) are also presented for  $HfO_2$ (Fig. 4 (c) and (e)) and for  $Al_2O_3$  (Fig. 4 (d) and (f)). For the HfO<sub>2</sub>/*n*-InGaAs MOS structure, improvement in γ-factor is observed at intermediate FGA temperatures ( $T_{opt} = 350$  °C), indicating that the width of the energy distribution of trapping defects is narrower, resulting in a lower trap density that the Fermi level can access near the conduction band edge. Therefore this results in a significant reduction in Q<sub>trapped</sub> as shown in Fig. 4 (e). For the case of Al<sub>2</sub>O<sub>3</sub>/n-InGaAs, γ-factor stays almost a constant following FGA at 250 °C and 300 °C, however, Qtrapped is decreased. This suggests that the distribution of border traps remains unchanged but the density of total border traps is reduced. Following FGA at  $\geq 350$ °C, y-factor is improved, resulting in a further reduction in Q<sub>trapped</sub> as shown in Fig. 4 (f). It is noted that the most pronounced improvement in  $\gamma$ -factor and reduction in Qtrapped based on CV hysteresis measurements are observed at the same FGA temperature that reduces the accumulation frequency dispersion, where  $T_{opt} = 350$  °C for  $HfO_2/n$ -InGaAs and  $T_{opt} = 450$  °C for  $Al_2O_3/n$ -InGaAs. This observation implies that CV hysteresis accumulation frequency dispersion are likely probing the same underlying oxide defects, even though the probing distance into oxide varies between the two analysis techniques.

Fig. 4:  $Q_{trapped}$  (from CV hysteresis) versus overdrive voltage ( $V_{ov}$ ), voltage acceleration factor ( $\gamma$ -factor) versus FGA temperature and  $Q_{trapped}$  (at  $V_{ov}=2$  V) versus FGA temperature for Au/Ni gate over HfO<sub>2</sub>(8nm)/n-InGaAs and Al<sub>2</sub>O<sub>3</sub>/(8nm)/n-InGaAs MOS. Note that the improvement in  $\gamma$ -factor results in significant reduction in  $Q_{trapped}$ .

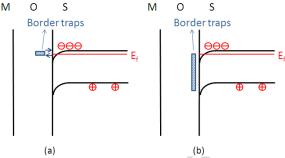

The optimum Q<sub>trapped</sub> for HfO<sub>2</sub> sample (Fig. 4 (e)) and Al<sub>2</sub>O<sub>3</sub> sample (Fig. 4 (f)) corresponds to a volume density of  $1.57 \times 10^{19}$  cm<sup>-3</sup> and  $5.39 \times 10^{18}$  cm<sup>-3</sup>, respectively, assuming the CV probes defects over a distance of 1 nm within the oxide with a spatially uniform trap density. These values are lower than those estimated from Fig. 3 using accumulation frequency dispersion ( $V_{ov} \sim 2 V$ ). The discrepancy between accumulation frequency dispersion and CV hysteresis is due to the fact each technique is partially probing border traps, which can have a wide distribution in energy levels and also a spatial distribution into the oxide [11]. As illustrated in Fig. 5, accumulation frequency dispersion only probes border traps around a single energy level (with N<sub>bt</sub> in unit of cm<sup>-3</sup> per eV) at V<sub>max</sub>. However, CV hysteresis arises from the filling the border trap energy levels below the Fermi level  $(E_f)$  at  $V_{max}$ , and at distances into the oxide, which do not re-emit the trapped charge during the reverse sweep of the CV response. The calculation of N<sub>bt</sub> from the accumulation capacitance frequency dispersion at various values of V<sub>max</sub> in accumulation yields the energy distribution of N<sub>bt</sub>, which can be subsequently be integrated to obtain the  $N_{bt}$  value in units [cm<sup>-3</sup>]. This analysis allows a more detailed correlation analysis to be undertaken, and is the subject of on-going studies.

Fig. 5: Band diagram for n-InGaAs MOS capacitor showing (a) accumulation frequency dispersion which probes border traps at a single energy level at  $V_{max}$ , and (b) CV hysteresis measures border traps filled with electrons below  $E_f$  (at  $V_{max}$ ).

### 5. Conclusion

The effect of FGA (5% H<sub>2</sub> / 95% N<sub>2</sub>) on border trap density in high-k/InGaAs MOS systems was studied using accumulation frequency dispersion and CV hysteresis. The optimum FGA temperature to reduce accumulation frequency dispersion is observed to be 350 °C for HfO<sub>2</sub>/n-InGaAs, where N<sub>bt</sub> is reduced from 9.4×10<sup>19</sup> cm<sup>-3</sup>eV<sup>-1</sup> to 6.3×10<sup>19</sup>cm<sup>-3</sup> eV<sup>-1</sup>. For the case of Al<sub>2</sub>O<sub>3</sub>/n-InGaAs, continuous reduction in N<sub>bt</sub> with FGA temperature is recorded, where N<sub>bt</sub> is reduced from 5.7×10<sup>19</sup> cm<sup>-3</sup>eV<sup>-1</sup> for no FGA, to 3.4×10<sup>19</sup> cm<sup>-3</sup>eV<sup>-1</sup> for a 450 °C FGA. Moreover, the most pronounced reduction in border trap density estimated from CV hysteresis is observed at the same optimum FGA temperature that reduces the accumulation frequency dispersion, suggesting the two techniques,

even though they probe different distances into the oxide, are correlated.

#### Acknowledgements

The authors thank Dan O'Connell, Tyndall National Institute, for the metallization and forming gas annealing. The authors acknowledge Science Foundation Ireland through the INVENT project (09/IN.1/I2633) and the European Commission entitled "Compound through the projects Semiconductors for 3D Integration COMPOSE3" (FP7-ICT-2013-11-619325) and "Integration of III-V Nanowire Semiconductors for next Generation High Performance CMOS SOC Technologies INSIGHT" (688784) for financial support.

#### References

[1] J. Lin, Y. Y. Gomeniuk, S. Monaghan, I. M. Povey, K. Cherkaoui, É. O'Connor, M. Power and P. K. Hurley, J. Appl. Phys. 114, 144105 (2013).

[2] J. Lin, S. Monaghan, K. Cherkaoui, I. M. Povey, É. O'Connor, B. Sheehan, and P. K. Hurley, Microelectronic Engineering, 147 (2015) 273–276.

[3] Y. Yuan, B. Yu, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell and Y. Taur, IEEE Transactions on Electron Devices **59** (8), 2100 (2012). [4] S. Johansson, M. Berg, K-M. Persson, and E. Lind, IEEE Trans. on Electron Devices, **60**, (2), 776 (2013).

[5] E. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, J. Appl. Phys. **109**, 024101 (2011). [6] W. Cabrera, B. Brennan, H. Dong, T. P. O'Regan, I. M. Povey, S. Monaghan, E. O'Connor, P. K. Hurley, R. M. Wallace, Y. J. Chabal, Appl. Phys. Lett. **104**, 011601 (2014).

[7] J. Franco, A. Vais, S. Sioncke, V. Putcha, B. Kaczer, B.-S. Shie, X. Shi, R. Mahlouji, L. Nyns, D. Zhou, N. Waldron, J.W. Maes, Q. Xie, M. Givens, F. Tang, X. Jiang, H. Arimura, T. Schram, L.-Å Ragnarsson, A. Sibaja Hernandez, G. Hellings, N. Horiguchi, M. Heyns, G. Groeseneken, D. Linten, N. Collaert and A. Thean, IEEE Symposium on VLSI Technology, 2016.

[8] Igor Krylov, Dan Ritter, and Moshe Eizenberg, J. Appl. Phys. **117**, 174501 (2015).

[9] J. Franco, A. Alian, B. Kaczer, D. Lin, T. Ivanov, A. Pourghaderi, K. Martens, Y. Mols, D. Zhou, N. Waldron, S. Sioncke, T. Kauerauf, N. Collaert, A. Thean, M. Heyns, and G. Groeseneken, Tech. Dig. - Int. Reliab. Phys. Symp. 2014, 6A.2.1.

[10] A. Vais, J. Franco, H-C Lin, N. Collaert, A. Mocuta. K. De Meyer, and A. Thean, Appl. Phys. Lett. **107**, 233504 (2015).

[11] C. Dou, D. Lin, A. Vais, T. Ivanov, H.-P. Chen, K. Martens, K. Kakushima, H. Iwai, Y. Taur, A. Thean, G. Groeseneken, Microelectronics Reliability **54**, 746–754 (2014).

### Graphical abstract

C-V hysteresis probes the border trap energy levels below E<sub>f</sub> at V<sub>max</sub>, and at distances into the oxide, which do not re-emit the trapped charge during the reverse tween of the C-V response. Units of cm<sup>3</sup>

Highlights

- Border traps in HfO<sub>2</sub>/InGaAs and Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS structures were studied

- Forming gas annealing temperature series was performed

- C-V hysteresis and accumulation frequency dispersion were analysed and compared

- C-V hysteresis probes the border traps below the Fermi level

- Accumulation frequency dispersion probes border traps at a single energy level