| Title                   | Cryptographic coprocessors for embedded systems                                                          |

|-------------------------|----------------------------------------------------------------------------------------------------------|

| Authors                 | Hamilton, Mark                                                                                           |

| Publication date        | 2014                                                                                                     |

| Original Citation       | Hamilton, M. 2014. Cryptographic coprocessors for embedded systems. PhD Thesis, University College Cork. |

| Type of publication     | Doctoral thesis                                                                                          |

| Rights                  | © 2014, Mark Hamilton - http://creativecommons.org/licenses/<br>by-nc-nd/3.0/                            |

| Download date           | 2025-09-07 19:55:49                                                                                      |

| Item downloaded<br>from | https://hdl.handle.net/10468/1770                                                                        |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# Cryptographic Coprocessors for Embedded Systems

Mark Hamilton Department of Electrical and Electronic Engineering National University of Ireland, Cork

Research Supervisor : Dr. William P. Marnane Head of Department : Prof. Nabeel Riza

> A thesis submitted for the degree of *Doctor of Philosophy* January 24, 2014

# Abstract

In the field of embedded systems design, coprocessors play an important role as a component to increase performance. Many embedded systems are built around a small *General Purpose Processor* (GPP). If the GPP cannot meet the performance requirements for a certain operation, a coprocessor can be included in the design. The GPP can then offload the computationally intensive operation to the coprocessor; thus increasing the performance of the overall system. A common application of coprocessors is the acceleration of cryptographic algorithms. The work presented in this thesis discusses coprocessor architectures for various cryptographic algorithms that are found in many cryptographic protocols. Their performance is then analysed on a *Field Programmable Gate Array* (FPGA) platform.

Firstly, the acceleration of *Elliptic Curve Cryptography* (ECC) algorithms is investigated through the use of instruction set extension of a GPP. The performance of these algorithms in a full hardware implementation is then investigated, and an architecture for the acceleration the ECC based digital signature algorithm is developed.

Hash functions are also an important component of a cryptographic system. The FPGA implementation of recent hash function designs from the SHA-3 competition are discussed and a fair comparison methodology for hash functions presented.

Many cryptographic protocols involve the generation of random data, for keys or nonces. This requires a *True Random Number Generator* (TRNG) to be present in the system. Various TRNG designs are discussed and a secure implementation, including post-processing and failure detection, is introduced.

Finally, a coprocessor for the acceleration of operations at the protocol level will be discussed, where, a novel aspect of the design is the secure method in which private-key data is handled. I, Mark Hamilton, certify that this thesis is my own work and I have not obtained a degree in this university or elsewhere on the basis of the work submitted in this thesis.

Mark Hamilton

# Acknowledgements

I would like to thank all those who have helped me during the course of completing this thesis, including, but not limited to, my supervisor Liam Marnane for giving me the opportunity to pursue this PhD, and for his guidance over the past few years; Christophe Negre and Emanuel Popovici for taking the time to read this thesis; the staff of the electrical engineering department in UCC; all of the postgraduate students and postdocs that I have worked with over the past few years; Arnaud Tisserand for inviting me to collaborate with him in Lannion; and my family for their support over the last few years.

# Contents

| Contents i |      |                                       |   |  |

|------------|------|---------------------------------------|---|--|

| 1          | Intr | roduction 1                           |   |  |

|            | 1.1  | Motivation                            | 1 |  |

|            | 1.2  | Contribution                          | 3 |  |

|            | 1.3  | Publications                          | 4 |  |

| <b>2</b>   | Cry  | ptography for Embedded Systems        | 6 |  |

|            | 2.1  | Introduction                          | 6 |  |

|            | 2.2  | Introduction to Cryptographic Systems | 7 |  |

|            | 2.3  | Mathematical Background               | 8 |  |

|            |      | 2.3.1 Groups                          | 8 |  |

|            |      | 2.3.2 Rings                           | 9 |  |

|            |      | 2.3.3 Fields                          | 9 |  |

|            |      | 2.3.4 Finite Fields 10                | C |  |

|            | 2.4  | Generating Random Numbers             | C |  |

|            | 2.5  | Private-Key Cryptography              | 1 |  |

|            | 2.6  | Public-Key Cryptography               | 2 |  |

|            |      | 2.6.1 Public Key Infrastructure       | 3 |  |

|            |      | 2.6.1.1 Digital Signatures            | 3 |  |

|            |      | 2.6.1.2 Digital Certificates          | 6 |  |

|            | 2.7  | Cryptographic Protocols               | 6 |  |

|            | 2.8  | Transport Layer Security              | 7 |  |

|            |      | 2.8.1 TLS Record Protocol             | 8 |  |

|            |      | 2.8.2 TLS Alert Protocol              | 3 |  |

|            |      | 2.8.3 TLS ChangeCipherSpec Protocol   | 9 |  |

|            |      | 2.8.4 TLS Application Data Protocol   | 9 |  |

|   |      | 2.8.5 TLS Handshake Protocol                                                                        | 20 |

|---|------|-----------------------------------------------------------------------------------------------------|----|

|   | 2.9  | Field Programmable Gate Arrays                                                                      | 22 |

|   |      | 2.9.1 Microblaze Processor                                                                          | 23 |

|   |      | 2.9.2 FSL Bus                                                                                       | 24 |

|   | 2.10 | FPGAs and Cryptography                                                                              | 25 |

|   | 2.11 | Side Channel Attacks                                                                                | 27 |

|   | 2.12 | Related Work                                                                                        | 28 |

|   |      | 2.12.1 Isobe et al                                                                                  | 28 |

|   |      | 2.12.2 Wang et al. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 29 |

|   |      | 2.12.3 Instruction Set Extension                                                                    | 30 |

|   |      | 2.12.4 Secure Key Management                                                                        | 30 |

|   | 2.13 | Discussion                                                                                          | 32 |

| 3 | Har  | dware-Software Co-Design for Elliptic Curve Cryptography                                            | 34 |

|   | 3.1  | Introduction                                                                                        | 34 |

|   | 3.2  | Background to ECC                                                                                   | 35 |

|   |      | 3.2.1 Group operations on Elliptic Curves                                                           | 35 |

|   |      | 3.2.2 Jacobian Coordinates                                                                          | 36 |

|   |      | 3.2.3 Co- $Z$ Arithmetic                                                                            | 38 |

|   | 3.3  | Point Scalar Multiplication                                                                         | 39 |

|   |      | 3.3.1 SPA Resistant Point Scalar Multiplication                                                     | 40 |

|   |      | 3.3.1.1 Combined double-add operation                                                               | 43 |

|   |      | 3.3.1.2 $(X, Y)$ -only operations                                                                   | 43 |

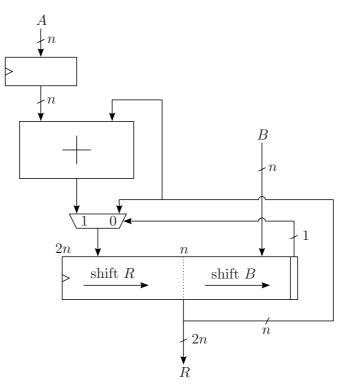

|   | 3.4  | Montgomery Multiplication                                                                           | 45 |

|   | 3.5  | Instruction Set Extension for ECC                                                                   | 47 |

|   |      | 3.5.1 Software                                                                                      | 47 |

|   | 3.6  | Custom Hardware Acceleration                                                                        | 49 |

|   |      | 3.6.1 Montgomery Multiplication in Hardware                                                         | 49 |

|   |      | 3.6.2 Instruction Set Extension Results                                                             | 50 |

|   | 3.7  | Optimisations for the $q = 2^n - 1$ case                                                            | 53 |

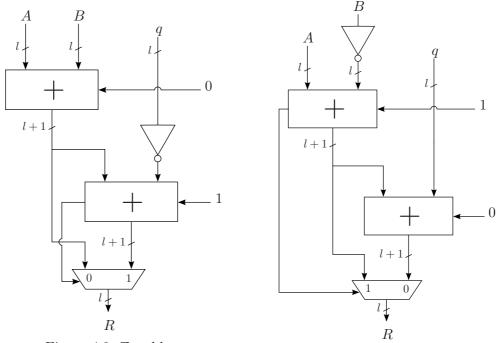

|   |      | 3.7.1 Serial Multiplier                                                                             | 54 |

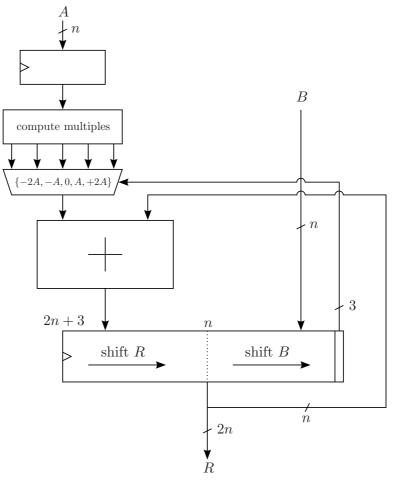

|   |      | 3.7.2 Booth Multiplier                                                                              | 55 |

|   |      | 3.7.3 Multiplier with BRAMs and DSP48Es                                                             | 56 |

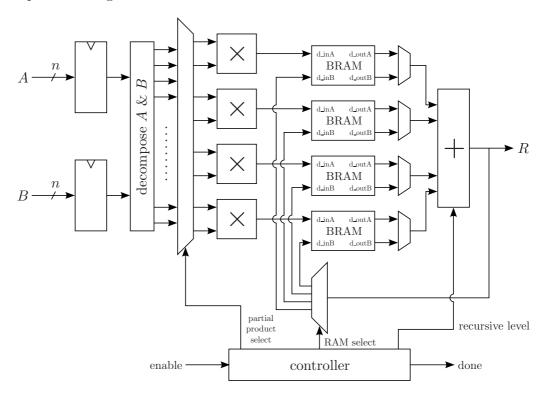

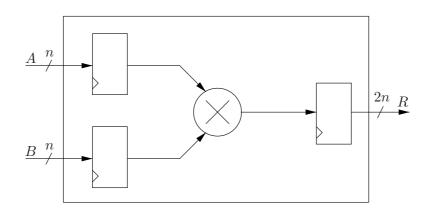

|   |      | 3.7.3.1 Multiplier Architecture                                                                     | 58 |

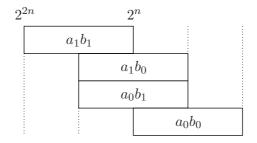

|   |      | 3.7.3.2 Decomposing the Multiplicands                                                               | 59 |

|   |      | 3.7.3.3 DSP Blocks                                                                                  | 61 |

|          |     | 3.7.3.4 Block RAM                                                                                                                              | 62 |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          |     | 3.7.3.5 The Adder                                                                                                                              | 62 |

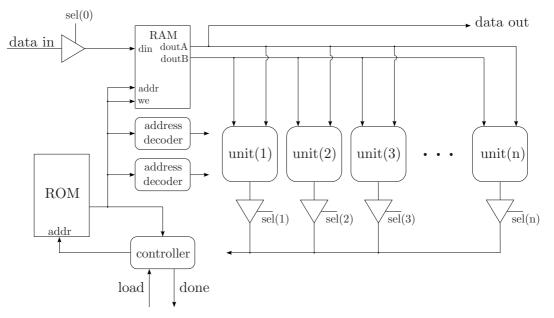

|          |     | $3.7.3.6  \text{Controller} \dots \dots$ | 63 |

|          |     | 3.7.3.7 Multiplier Operation                                                                                                                   | 64 |

|          |     | 3.7.4 Results                                                                                                                                  | 64 |

|          | 3.8 | Discussion                                                                                                                                     | 66 |

| 4        | FPO | GA Implementation of an ECDSA Coprocessor                                                                                                      | 68 |

|          | 4.1 | Introduction                                                                                                                                   | 68 |

|          | 4.2 | ECC Processor                                                                                                                                  | 68 |

|          |     | 4.2.1 $\mathbb{F}_q$ Addition/Subtraction                                                                                                      | 69 |

|          |     | 4.2.2 $\mathbb{F}_q$ Inversion                                                                                                                 | 70 |

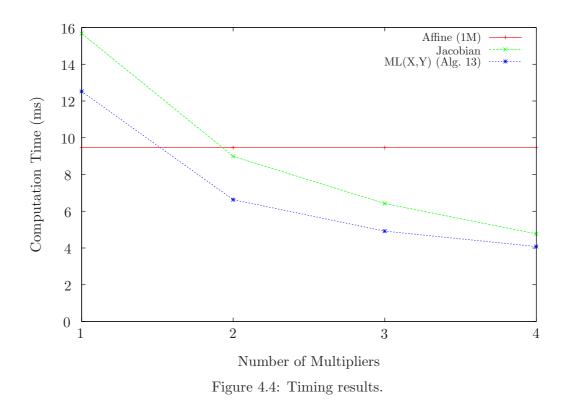

|          | 4.3 | Comparing Coordinate Performance                                                                                                               | 71 |

|          | 4.4 | Applications of Elliptic Curves in TLS                                                                                                         | 76 |

|          |     | 4.4.1 Elliptic Curve Diffie-Hellman Key Exchange (ECDH)                                                                                        | 77 |

|          |     | 4.4.2 Elliptic Curve Digital Signature Algorithm (ECDSA)                                                                                       | 78 |

|          |     | 4.4.3 DPA resistant ECDSA                                                                                                                      | 80 |

|          |     | 4.4.4 Simultaneous multiple point multiplication                                                                                               | 80 |

|          | 4.5 | Related Work                                                                                                                                   | 81 |

|          | 4.6 | ECDSA Processor Architecture                                                                                                                   | 83 |

|          | 4.7 | Implementation Results                                                                                                                         | 84 |

|          | 4.8 | Discussion                                                                                                                                     | 87 |

| <b>5</b> | Has | sh Functions and their Applications                                                                                                            | 89 |

|          | 5.1 | Introduction                                                                                                                                   | 89 |

|          | 5.2 | Hash Function Design                                                                                                                           | 90 |

|          |     | 5.2.1 Implementation Options                                                                                                                   | 90 |

|          | 5.3 | Hash Function Usage                                                                                                                            | 91 |

|          | 5.4 | Hash Functions and TLS                                                                                                                         | 92 |

|          |     | 5.4.1 HMAC Function                                                                                                                            | 92 |

|          |     | 5.4.2 TLS Pseudorandom Function                                                                                                                | 93 |

|          |     | 5.4.3 Key derivation $\ldots$                                                                                                                  | 94 |

|          |     | 5.4.4 Finished Message Calculation                                                                                                             | 94 |

|          | 5.5 | SHA Algorithms                                                                                                                                 | 95 |

|          |     | 5.5.1 SHA256 $\ldots$                                         | 95 |

|          | 5.6 | SHA-3 Competition                                                                                                                              | 97 |

|   | 5.7  | Blue Midnight Wish                                                                                                                                                    |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.8  | Hamsi                                                                                                                                                                 |

|   | 5.9  | CubeHash                                                                                                                                                              |

|   | 5.10 | Fair Comparison Methodology                                                                                                                                           |

|   |      | 5.10.1 Wrapper Overview $\ldots \ldots \ldots$        |

|   |      | 5.10.2 Communications Protocol $\ldots \ldots \ldots$ |

|   |      | 5.10.3 Padding Protocol                                                                                                                                               |

|   | 5.11 | Implementation Results                                                                                                                                                |

|   | 5.12 | Discussion                                                                                                                                                            |

| 6 | Tru  | e Random Number Generators 109                                                                                                                                        |

|   | 6.1  | Introduction                                                                                                                                                          |

|   | 6.2  | Implementation of TRNGs                                                                                                                                               |

|   |      | 6.2.1 Analysing the Quality of TRNG Output Data                                                                                                                       |

|   | 6.3  | Vasyltsov et al                                                                                                                                                       |

|   | 6.4  | Varchola and Drutarovský                                                                                                                                              |

|   | 6.5  | Dichtl and Golić                                                                                                                                                      |

|   | 6.6  | Comparing the Results                                                                                                                                                 |

|   | 6.7  | TRNG Failure Detection                                                                                                                                                |

|   |      | 6.7.1 FPGA Implementation                                                                                                                                             |

|   | 6.8  | Post-processing of TRNGs                                                                                                                                              |

|   | 6.9  | Secure Architecture Implementation Results                                                                                                                            |

|   | 6.10 | Discussion                                                                                                                                                            |

| 7 | Сор  | rocessor Design For the Protocol Level 128                                                                                                                            |

|   | 7.1  | Introduction                                                                                                                                                          |

|   | 7.2  | Designing a Secure Coprocessor                                                                                                                                        |

|   | 7.3  | Requirements of a TLS Coprocessor                                                                                                                                     |

|   |      | 7.3.1 Public-key algorithms                                                                                                                                           |

|   |      | 7.3.2 Private-key Algorithms                                                                                                                                          |

|   |      | 7.3.3 Hashing Operations                                                                                                                                              |

|   |      | 7.3.4 Operations Involving Private Keys                                                                                                                               |

|   | 7.4  | Encryption for TLS                                                                                                                                                    |

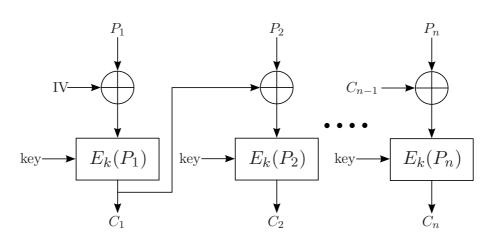

|   |      | 7.4.1 Cipher Block Chaining $\ldots \ldots 134$                            |

|   |      | 7.4.2 AES Implementation $\ldots \ldots 135$                               |

|   | 7.5  | SHA256 Implementation for TLS                                                                                                                                         |

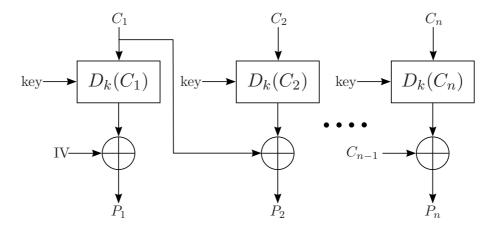

|              | 7.6    | Design Overview                                                                   | 137 |

|--------------|--------|-----------------------------------------------------------------------------------|-----|

|              | 7.7    | Hardware/Software Partition                                                       | 137 |

|              | 7.8    | Coprocessor Operation                                                             | 139 |

|              | 7.9    | Test Platform                                                                     | 141 |

|              |        | 7.9.1 Microblaze Configuration                                                    | 141 |

|              | 7.10   | Implementation Results                                                            | 142 |

|              | 7.11   | Conclusions                                                                       | 143 |

| 8            | Con    | clusions and Future Work                                                          | 145 |

|              | 8.1    | Contribution to the Field                                                         | 145 |

|              | 8.2    | Future Work                                                                       | 147 |

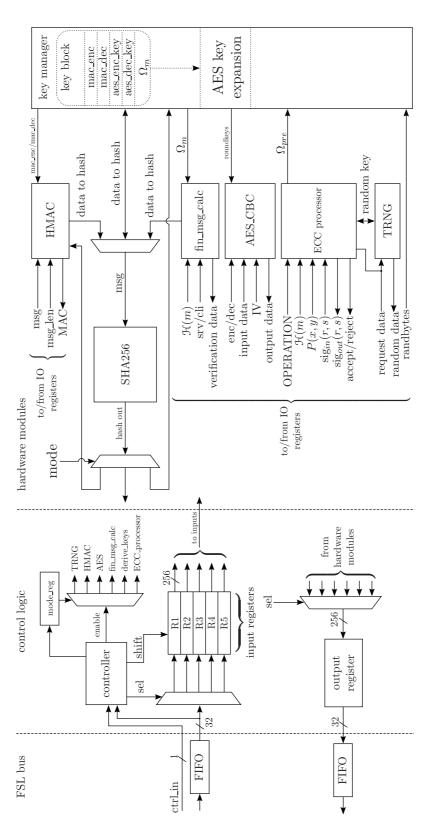

| $\mathbf{A}$ | Co-2   | Z Algorithms                                                                      | 148 |

|              | A.1    | Point Doubling Formulæ with Update in Homogeneous Coordinates                     | 152 |

|              | A.2    | Full Coordinate Recovery                                                          | 153 |

|              | A.3    | Point doubling and tripling with co-Z update $\ldots \ldots \ldots \ldots \ldots$ | 154 |

| Li           | st of  | Abbreviations                                                                     | 156 |

| Re           | eferei | nces                                                                              | 161 |

# Chapter 1

# Introduction

#### 1.1 Motivation

The emergence of ubiquitous computing has led to increasing amounts of data being transmitted over a wide range of media; ranging from fiber optic links over distances of hundreds of miles, to wireless transmissions over several centimetres. The transmission of sensitive information is no longer exclusive to large businesses using expensive and computationally powerful equipment. Today, small embedded devices, such as smart cards and mobile phones, also require the ability to transmit data securely. These small devices provide a completely different design challenge than that of large high-speed applications. When implementing cryptographic protocols on embedded devices, a designer must take into consideration the computational power, logic resources available in the device, and power consumption. A trade-off must be made in these areas in order to achieve acceptable performance in terms of computation time, while also minimising the area and power consumption.

Cryptographic protocols can be used to ensure that data is transmitted securely over an unsecured channel. The increase in transmission of financial and other sensitive information across the Internet has led to the definition of many cryptographic standards. Currently, one of the most widely supported cryptographic standards, for use on the Internet, is the *Transport Layer Security* (TLS) protocol. The TLS protocol allows for secure communication over *Virtual Private Networks* (VPNs); is used extensively in securing online financial transactions and also plays an important role in embedded applications, such as wireless sensor networks. However, embedded devices tend to be very constrained in terms of computing power, as many of them are battery powered and do not require a powerful processor to perform their primary task. This can be problematic as the TLS protocol supports a wide array of encryption and key exchange algorithms, many of which are very computationally intensive as they include large finite field multiplications. These types of computations are not suited to small *General-Purpose Processors* (GPPs) found in embedded devices and can lead to unacceptably poor performance. To alleviate this problem a coprocessor can be used to accelerate cryptographic computations and allow for GPPs to be used for other tasks.

Field Programmable Gate Arrays (FPGAs) are a popular choice for embedded systems as they have a faster time to market than Application Specific Integrated Circuit (ASIC) based solutions, and are also more flexible than a design based around a microprocessor Integrated Circuit (IC). An FPGA consists of a large array of user programmable Lookup Tables (LUTs), memory elements, and routing logic; allowing a designer to implement any logic required for the system, inside the FPGA. This has the advantage that a customised system can be built, without the need to manufacture new hardware components. Another benefit of FPGAs is their reconfigurability, which allows for hardware updates to be made without replacing components in the system. The configurability of FPGAs and the abundance of Intellectual Property (IP) cores, that can perform a wide array of tasks, makes it possible to construct a System on Chip (SoC) consisting of a microprocessor and also some extra logic, for whatever application is required, all inside the same chip.

The advantage of FPGAs for cryptographic applications is that they are much more suited to processing data in parallel than a GPP. A small processor usually has a datapath in the range of 8 to 32 bits and an *Arithmetic Logic Unit* (ALU) capable of performing operations on data of the same size. This structure works well when processing general data, such as checking message fields in packets of information received over a network. However, an FPGA can be configured in such a way that it can process large data structures in parallel, which allows for the implementation of a cryptographic processor that consists of a datapath of several hundred bits, and also an ALU capable of processor can reduce the cost and power consumption of the embedded device, while increasing the performance.

When designing cryptographic applications for an embedded system, security is an important factor. The security needs are very different from that of large systems that are intended for use in a fixed location, such as a web or mail server. In server applications the hardware will usually be physically protected to a much higher degree than in an embedded device. This can include the servers being kept inside a secure room. An embedded device however may have very little, to no physical protection.

This allows the attacker to mount different forms of attacks against the device, such as monitoring the power consumption of the device in order to retrieve secret key information; this form of side channel attack is known as *Simple Power Analysis* (SPA). An attacker might also try to influence how the device generates random numbers, or how the device processes data, possibly compromising the security of cryptographic algorithms running on the device. With the extent of physical access an attacker has, it is critically important to protect the device in some way from these attacks. One of the easiest ways an attacker can recover the secret keys is by attempting some form of software based attack, through which the secret keys would be extracted from the GPPs internal working registers. These sort of attacks can be prevented by segmenting the system into a secure and non-secure areas. The GPP would be placed in the nonsecure zone and would not have access to the secret keys, thus removing the option of a software based attack.

### **1.2** Contribution

In this thesis, a secure architecture for a cryptographic coprocessor will be presented. The goal of the design is to derive an architecture that securely manages the private keys and is resistant against side channel attacks. Firstly, the requirements of a coprocessor for the TLS protocol will be analysed; specific operations will be chosen for implementation in the coprocessor, with the aim of improving overall system performance and security. Much of the previous work in the area has focused on very large and high speed designs. In contrast, the architecture presented in this work will focus on embedded applications, where an efficient implementation of all operations is critical. Having identified the components required for the implementation of a TLS coprocessor, a thorough analysis of each of the components will be conducted in order to derive efficient and secure architectures.

Side channel resistance will be built into the system at an architecture and algorithmic level. The use of secure logic styles such as dual rail logic has been avoided in order keep the design portable across a range of platforms. It is not possible to fully protect a device from attack but the goal is to reduce the number of attacks that are feasible and to increase both the computational power and time required to extract the private keys.

The remainder of this thesis is organised as follows: Chapter 2 introduces the background information and theory required for the remaining chapters. Chapter 3 introduces *Elliptic Curve Cryptography* (ECC) theory and its implementation in a

hardware-software co-design setting. The acceleration of ECC algorithms through the use of *Instruction Set Extension* (ISE), and the design of finite field multipliers for this purpose will also be examined. Chapter 4 builds on the results from the previous chapter and explores the design of ECC coprocessors constructed from FPGA resources. Chapter 5 discusses the implementation of hash functions on FPGAs and introduces a fair comparison methodology for different hash function structures. Chapter 6 introduces *True Random Number Generators* (TRNGs) and how they can be implemented on an FPGA platform. Post-processing and failure detection of TRNGs will also be investigated; thus, allowing the construction of a secure TRNG suitable for use as a coprocessor. Chapter 7 details the design of the TLS coprocessor, which incorporates the components discussed in the previous chapters. The final coprocessor is a novel architecture that incorporates secure key management and securely partitions TLS operations between software and hardware.

## 1.3 Publications

The following papers were published during the course of the research conducted for this thesis:

- Brian Baldwin, Andrew Byrne, Mark Hamilton, Neil Hanley, Robert P. McEvoy, Weibo Pan, and William P. Marnane. FPGA Implementations of SHA-3 Candidates: CubeHash, Grøstl, LANE, Shabal and Spectral Hash. In *Euromicro Conference on Digital System Design (DSD)*, pages 783–790, August 2009.

- Brian Baldwin, Andrew Byrne, Liang Lu, Mark Hamilton, Neil Hanley, Maire O'Neill, and William P. Marnane. A Hardware Wrapper for the SHA-3 Hash Algorithms. In Signals and Systems Conference (ISSC 2010), IET Irish, pages 1–6. IET, 2010.

- Brian Baldwin, Andrew Byrne, Liang Lu, Mark Hamilton, Neil Hanley, Maire O'Neill, and William P. Marnane. FPGA Implementations of the Round Two SHA-3 Candidates. In *International Conference on Field Programmable Logic and Applications* (FPL 2010), pages 400–407. IEEE, 2010.

- Brian Baldwin, Andrew Byrne, Liang Lu, Mark Hamilton, Neil Hanley, Maire O'Neill, and William P. Marnane. FPGA Implementations of the Round Two SHA-3 Candidates. In *The Second SHA-3 Candidate Conference*, August 2010.

- Brian Baldwin, Raveen R. Goundar, Mark Hamilton, and William P. Marnane. Co-Z ECC Scalar Multiplications for Hardware, Software and Hardware-Software Co-

Design on Embedded Systems. *Journal of Cryptographic Engineering*, 2(4):221–240, 2012.

- Mark Hamilton and William P. Marnane. FPGA implementation of an Elliptic Curve Processor using the GLV Method. In International Conference on ReConFigurable Computing and FPGAs (ReConFig), pages 249–254, 2009.

- Mark Hamilton, William P. Marnane, and Arnaud Tisserand. A Comparison on FPGA of Modular Multipliers Suitable for Elliptic Curve Cryptography over GF(p) for Specific p values. In 21st International Conference on Field Programmable Logic and Applications (FPL), pages 273–276, 2011.

# Chapter 2

# Cryptography for Embedded Systems

# 2.1 Introduction

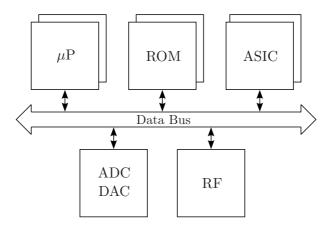

An embedded system is a subsection of a larger system that is designed to perform a specific task. Examples include the *Global Positioning System* (GPS) transceiver in a mobile phone or the traction control system of a car. An embedded system contains at least one processor in its architecture and might also contain several other hardware modules, as shown in Figure 2.1, where  $\mu$ P denotes a microprocessor. The embedded system architecture consists of software running on the  $\mu$ P, which interfaces with the various hardware modules in order to perform its specified task.

Figure 2.1: Generic architecture of an embedded system.

Embedded devices are usually more constrained in terms of computing power than general purpose devices, such as a desktop computer, as they are optimised to perform one specific task. When adding support for cryptographic protocols, one can therefore not take a generic library of code, compile it for the embedded system, and expect to achieve the required performance. The designer must take into consideration the resources available and optimise the implementation of the cryptographic primitives accordingly. In certain situations, the embedded system may simply not contain the requisite hardware to achieve acceptable performance. The inclusion of a coprocessor can solve this problem.

This chapter introduces the basic cryptographic algorithms and the mathematical concepts that they are based on. It will then be shown how these algorithms are combined into a cryptographic protocol that can be used to secure communications across an unsecured channel. Finally, an outline of the security requirements of embedded systems today and how FPGAs can be used to solve some of the problems that arise when implementing cryptographic algorithms in an embedded environment will be discussed.

#### 2.2 Introduction to Cryptographic Systems

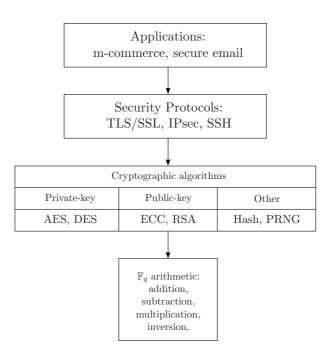

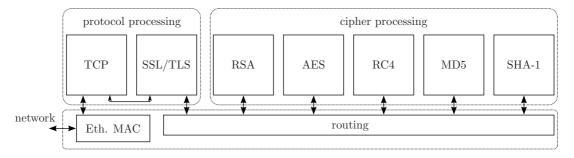

Figure 2.2 shows how the layers of a typical cryptographic system are arranged; the top level layer is where user applications reside. Secure email and mobile commerce are two examples of applications that are highly dependent on the services that the lower layers provide. Many different cryptographic algorithms exist that supply the security protocols with services such as sender authenticity, encryption, non-repudiation, and data integrity. Using a combination of these algorithms, it is possible to transfer data securely over an unsecured channel.

At the lowest layer of the system the core operations are based on finite field arithmetic. The efficient implementation of these operations is very important for overall system performance, as some of these operations need to be executed thousands of times during the processing of an algorithm. A small saving at this level can therefore lead to a large reduction in latency in the upper layers [7].

Cryptographic algorithms generally fall in two main categories, private-key cryptography and public-key cryptography. In private-key cryptography, two entities use an identical shared secret to communicate across an unsecured channel; this form of cryptosystem is discussed in Section 2.5. This approach, however, assumes that both parties have been able to establish a shared secret between them. In practice, this process is not a trivial task. However, the invention of public-key cryptography has provided a

Figure 2.2: Hierarchical model of a cryptographic system.

solution by defining mathematical constructions that allow both keys and encrypted messages to be exchanged securely. Public-key algorithms are generally the most computationally intensive in the system as they require the most arithmetic operations per bit during their execution. Public-key cryptography will be discussed in Section 2.6, but first an introduction to some of the mathematics involved in cryptography will be given.

### 2.3 Mathematical Background

Many cryptographic primitives are based on the principles of finite field arithmetic; therefore, in this section the construction of finite fields and their associated properties will be discussed. In order to define a finite field, the general concepts of groups, rings, and fields must first be introduced.

#### 2.3.1 Groups

A group is a set of elements G together with an operation "." which when applied to elements of G, the following properties hold:

1. The group operation "." is closed. That is,  $a \cdot b = c \in G$  for all  $a, b \in G$ .

- 2. The group operation is associative. That is,  $a \cdot (b \cdot c) = (a \cdot b) \cdot c$  for all  $a, b, c \in G$ .

- 3. There is an identity element (or neutral element)  $\mu \in G$ , where  $a \cdot \mu = \mu \cdot a = a$  for all  $a \in G$ .

- 4. For each  $a \in G$  there exists an element  $a^{-1} \in G$ , where  $a \cdot a^{-1} = a^{-1} \cdot a = \mu$ . The element  $a^{-1}$  is known as the inverse of a.

- 5. A group G can be referred to as abelian (or commutative) if the property  $a \cdot b = b \cdot a$ , for all  $a, b \in G$ , is satisfied.

#### 2.3.2 Rings

- A ring  $(R, +, \cdot)$  is a set R, together with two binary operations "+" and ".", where:

- 1. R forms an abelian group with respect to "+", where "+" is usually referred to as addition.

- 2. The associative property holds for the the "." operation. i.e.,  $a \cdot (b \cdot c) = (a \cdot b) \cdot c$  for all  $a, b, c \in R$ .

- 3. The distributivity law holds i.e.,  $a \cdot (b+c) = a \cdot b + a \cdot c$  and  $(b+c) \cdot a = b \cdot a + c \cdot a$ .

#### 2.3.3 Fields

If we refer to "+" as addition and "." as multiplication, a field  $\mathbb{F}$  is a ring where the multiplication is commutative and a multiplicative inverse exists for every nonzero element of  $\mathbb{F}$ . The properties of a field are therefore:

- 1. The elements of  $\mathbb{F}$  form an additive group with the group operation "+" for which the identity element is 0.

- 2. All elements of  $\mathbb{F}$  except for 0 form a multiplicative group with respect to the group operation "·" and corresponding identity element 1.

- 3. The distributivity law holds for both multiplication, addition, and their combination. i.e., for all  $a, b, c \in \mathbb{F}$ ,  $a \cdot (b + c) = (a \cdot b) + (a \cdot c)$ .

#### 2.3.4 Finite Fields

Finite fields are of great importance to cryptography, as many cryptographic primitives can be defined using arithmetic over finite fields. In particular ECC, which will be discussed in Chapter 3, and *Rivest-Shamir-Adleman* (RSA) [106] are two examples of algorithms that are derived from this area of mathematics.

A finite field is simply a field  $\mathbb{F}$  that has a finite number of elements. It has been shown that a finite field can only exist if the number of elements in the field (also known as the *order* of the field) is the power of a prime p. That is, given a prime p and a positive integer m a finite field has  $q = p^m$  elements and is denoted  $\mathbb{F}_q$ . This result was derived by the mathematician Évariste Galois and hence a finite field is sometimes referred to as a Galois field, with the notation GF(q).

Having introduced some of the mathematical principles used in cryptography, the following sections address how these principles are used in cryptographic algorithms.

#### 2.4 Generating Random Numbers

As will be shown in subsequent sections, many cryptographic algorithms require the generation of random data for keys or nonces. Therefore, in this section a brief introduction into the generation of random data will be presented.

Regardless of how mathematically secure a cryptographic algorithm is, it can still be defeated if its implementation is not secure. This has been shown to be true in the past where cryptosystems were broken due to poorly initialised random data [45, 67]. In this case, an attacker can predict the keys; therefore, breaking the cipher itself is not necessary.

In order for a *Random Number Generator* (RNG) to be secure, random data should be generated in such a way that it's unpredictable, even if an attacker has knowledge of all previously generated data and the physical implementation of the RNG. Ideally, the RNG should produce random data uniformly distributed in the required range and each random bit should be independent. This amounts to the RNG having good statistical properties. In order to achieve this, the RNG must sample some unpredictable source to generate a stream of random bits. The more unpredictable the source, the more entropy will be present in the output bitstream; where entropy is a measure of the uncertainty of a random bit. The quality of the RNG is determined by its ability to extract randomness from the unpredictable source. RNG designs vary depending on the platform of implementation, a detailed discussion on implementing RNGs on FPGAs will be given in Chapter 6. In the following sections it will be assumed that the keys and nonces have been generated in a secure manner.

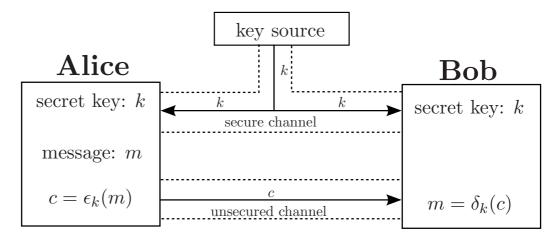

# 2.5 Private-Key Cryptography

A private-key (also known as symmetric-key) cryptosystem consists of two entities, say Alice and Bob, that both have knowledge of a secret key k. If Alice wants to send a message to Bob, Alice encrypts the message using the key k, and some encryption function  $\epsilon$ , where  $\epsilon$  is generally a stream cipher or a block cipher. Both stream ciphers and block ciphers are used to encrypt a string of data; stream ciphers encrypt the data one bit at a time, updating the key for each new bit of the plaintext. Block ciphers on the other hand fragment the data in blocks of fixed length and encrypt each block with the same key.

The encryption function  $\epsilon$  operates on the message and the key to produce the ciphertext c, that is  $c = \epsilon_k(m)$ . An example of this type of cryptosystem is shown in Figure 2.3, where  $\delta$  is the corresponding decryption function for  $\epsilon$ . The National Institute of Standards and Technology (NIST) block cipher currently recommended for use as the encryption algorithm is the Advanced Encryption Standard (AES) [91]. If the encryption function  $\epsilon$  is cryptographically strong, it is possible to securely exchange messages without an eavesdropper being able to decipher them. An example of a private-key system is Wi-Fi Protected Access (WPA) [2], which uses pre-shared keys.

Figure 2.3: Private-key cryptosystem.

Private-key cryptosystems offer high throughput for communications, however, securely distributing the secret key between the two communicating entities is a problem in certain situations. Over a large network, maintaining the key pairs for each connection is also problematic. Another downside is that private-key does not provide non-repudiation, which is of critical importance for online financial transactions. A solution to this can be found through the use of public-key cryptography for the distribution of keys. Once the secret key has been established, private-key algorithms can then be used for bulk data encryption. This combination of public-key and private-key systems combines the security and easy key distribution properties of public-key algorithms, with the high data throughput that is achievable with private-key algorithms.

# 2.6 Public-Key Cryptography

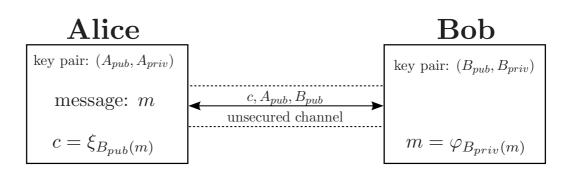

Public-key (also known as asymmetric-key) cryptography was introduced by Diffie and Hellman in 1976 in their paper "New Directions in Cryptography" [30]. Public-key cryptography provides a solution to setting up a shared secret key between two entities over an unsecured channel. The two communicating entities each have a key pair  $(K_{pub}, K_{priv})$ , where  $K_{pub}$  and  $K_{priv}$  are the public and private keys of that entity respectively. The keys are generated in such a way that if a message is encrypted using  $K_{pub}$ , it can be decrypted using  $K_{priv}$ . This allows for an easy key distribution scheme as  $K_{pub}$  can be made publicly available and anyone who wants to send an encrypted message only requires knowledge of the recipient's public key. In order for the protocol to be secure the key pair must be calculated in a way that makes it computationally infeasible to compute  $K_{priv}$ , given only  $K_{pub}$ .

Take as example two entities, Alice and Bob, that are connected by an unsecured channel, as shown in Figure 2.4. If Alice wants to send a message to Bob she first acquires a copy of Bob's public key,  $B_{pub}$ . Alice then encrypts the message m, using  $B_{pub}$  and some function  $\xi$  to obtain a ciphertext c, such that  $c = \xi_{B_{pub}}(m)$ . Alice then sends the ciphertext to Bob who can decrypt the ciphertext using his private key,  $B_{priv}$ , and a decryption function  $\varphi$ .

The main variants of public-key cryptography all stem from [30], they are ElGamal [34], RSA [106], and ECC [63, 81]. RSA uses the integer factorisation problem as its hard problem, whereas the others use the *Discrete Logarithm Problem* (DLP). The DLP is defined as the problem of finding an integer x such that  $\alpha^x \equiv \beta \pmod{q}$ , where  $1 \leq x \leq q - 1$ ,  $\alpha, \beta \in G$ , and G is a finite cyclic group.

Although public-key cryptography solves the secure key distribution problem, the system can easily be defeated by certain attacks without having to break the underlying mathematical principles. A *Man-in-the-middle* (MIM) attack [114, pages 48–49] can

Figure 2.4: Public-key cryptosystem.

be performed, where an attacker intercepts messages between the two communicating parties and impersonates each party by replacing their public keys with his own. To protect against this type of attack, some form of key authentication must be built into the system; this has lead to the definition of a *Public Key Infrastructure* (PKI).

#### 2.6.1 Public Key Infrastructure

PKI is the term given to the system that incorporates *Certificate Authorities* (CAs), *Registration Authorities* (RAs), and various public-key algorithms to achieve an authenticated distribution of keys. The purpose of the PKI is to bind a user's identity to their public key, this introduces a level of trust into the system. Digital certificates, which will be discussed in Section 2.6.1.2, are the mechanism used to bind a user to their public key. For the PKI to be possible, there must be at some level a trusted source of certificates; this trusted source is known as the root CA. The root CA has the ability to verify other CAs by signing their certificates. This method of trust being passed down to the end user is known as a certificate chain, and is present as it allows many different organisations to issue certificates. This also results in a reduction in the amount of data that an end user would need to store if they were required to possess the public keys of all the CAs.

When a user receives a certificate they must be able to verify the signature of one of the CAs in the chain in order to ensure that the certificate is in fact legitimate. An important process in the distribution of certificates is the ability to digitally sign a piece of data.

#### 2.6.1.1 Digital Signatures

Digital signatures provide a method by which the receiver of a message, that has been digitally signed, can verify the source of the message i.e., data origin authenticity.

Digital signatures are based on pubic-key methods and were introduced in [30]. Many other schemes have been proposed such as ElGamal [34, 106], and the elliptic curve based variant which will be discussed in Chapter 4.

In contrast to how the Diffie-Hellman key exchange works, by using an entity's public key to encrypt a message, digital signatures are produced by generating the signatures based on some operation and the sender's private key. The signature can then be verified through the use of the sender's public key. As an example the *Digital Signature Algorithm* (DSA) [89] is presented here. The sender generates a public key that consists of four parameters  $(p, q, \alpha, \beta)$ . The values p and q are primes, and are generated such that  $q \mid (p-1)$ . The value of  $\alpha$  is given by  $\alpha = g^{p-1/q}$ , where g is chosen at random such that  $\alpha \neq 1$  and  $g \in [1, p-1]$ . The value of  $\beta$  is given by  $\beta = \alpha^d \pmod{p}$ , where  $d \in [1, q-1]$  is the sender's private key.  $\mathcal{H}$  is a cryptographically secure hash function, which calculates a fixed length string for the input message m of arbitrary length. This string is effectively a fingerprint of the input message. A detailed description of the design and implementation of hash functions will be given in Chapter 5.

The signature generation process is given in Algorithm 1. In step 1 the value of k should be generated in a secure manner, such as that described in Section 2.4. A hash function  $\mathcal{H}$  is used in step 2 to calculate a fixed length string based on the input message m. The hash of the input message, the value k, and the sender's private key d are then combined using some finite field arithmetic which results in a digital signature consisting of two elements r and s.

| Algorithm 1 Digital signature generation                                    |  |  |

|-----------------------------------------------------------------------------|--|--|

| <b>Input:</b> private key d, public key $(p, q, \alpha, \beta)$ , message m |  |  |

| <b>Output:</b> Signature $(r, s)$                                           |  |  |

| 1: generate random integer $k \in [1, q-1]$                                 |  |  |

| 2: compute $e = \mathcal{H}(m)$                                             |  |  |

| 3: compute $r \equiv (\alpha^k \pmod{p}) \pmod{q}$                          |  |  |

| 4: compute $s \equiv (e + dr)k^{-1} \pmod{q}$                               |  |  |

| 5: the signature for message $m$ is then $(r, s)$                           |  |  |

|                                                                             |  |  |

Algorithm 2 shows the steps required to verify the signature of a received message. Using the same hash function as that of Algorithm 1, the receiver calculates the hash of the received message. Steps 3 to 6 of the algorithm then use some finite field arithmetic to generate values based on  $r, s, \mathcal{H}(m)$ , and the sender's public key. If the signature is correct, the resulting value v should equal that of r from the received signature.

Algorithm 2 Digital signature verification

Input: signature (r, s), senders public key  $(p, q, \alpha, \beta)$ , message m

Output: accept or reject signature

1: verify  $r, s \in [1, q - 1]$

2: compute  $e = \mathcal{H}(m)$

3: compute  $\lambda = s^{-1} \pmod{q}$

4: compute  $u_1 = e\lambda \pmod{q}$

5: compute  $u_2 = r\lambda \pmod{q}$

6: compute  $v \equiv (\alpha^{u_1}\beta^{u_2} \pmod{p}) \pmod{q}$

7: accept signature if  $v \equiv r \pmod{q}$  else reject

This can be shown by observing that in Algorithm 1, the sender computes the value

$$s \equiv (e+dr)k^{-1} \pmod{q},\tag{2.1}$$

where,  $e = \mathcal{H}(m)$ . Therefore, the correctness of Algorithm 2 can shown, as

$$k \equiv es^{-1} + drs^{-1} \pmod{q},$$

$$\equiv e\lambda + dr\lambda \pmod{q}.$$

(2.2)

Using the notation from Algorithm 2 this can be rewritten as

$$k \equiv u_1 + du_2 \pmod{q}. \tag{2.3}$$

Raising  $\alpha$  to the power of both sides gives

$$\alpha^{k} \equiv \alpha^{u_{1}+du_{2}} \pmod{p},$$

$$\equiv \alpha^{u_{1}}\alpha^{du_{2}} \pmod{p},$$

$$\equiv \alpha^{u_{1}}\beta^{u_{2}} \pmod{p}.$$

(2.4)

Finally,

$$r \equiv (\alpha^k \pmod{p}) \pmod{q},$$

$$\equiv (\alpha^{u_1} \beta^{u_2} \pmod{p}) \pmod{q},$$

$$\equiv v \pmod{q}.$$

(2.5)

#### 2.6.1.2 Digital Certificates

Digital certificates, standardised in [56], are used to link a specific public key to its user. A *Certificate Authority* (CA) is a registered organisation (trusted third party) that verifies the identities of the owners of public keys and issues certificates accordingly. To create a certificate, the sender uses a digital signature algorithm to sign a combination of the sender's ID and public key. Web browsers contain a list of trusted CAs. When a browser tries to access a website, the website sends the browser a certificate that it has obtained from a CA. If the certificate can be verified i.e., the signature is valid for the website domain name and the accompanying public key, the browser can infer that the website is genuine.

#### 2.7 Cryptographic Protocols

In the previous sections, the underlying mathematical principles used in cryptography were introduced, this was followed by a discussion of the different forms of cryptographic algorithms. This section deals with the use of these cryptographic algorithms as part of a cryptographic protocol.

Cryptographic protocols define how the cryptographic algorithms are combined in order to achieve a specific security goal, such as secure data transmission over a network. They define how data should be encapsulated and give a framework for how the different forms of messages should be exchanged i.e., the exchange of keys or application data. Many cryptographic protocols exist, however, they are all based upon the same underlying cryptographic primitives, such as public-key and private-key cryptography. The *Internet Protocol Security* (IPsec) protocol [96] operates at the IP layer of the TCP/IP model [17, 18] and is used extensively in securing VPNs. *Secure Shell* (SSH) [135] operates at the application layer and allows for secure command-line login and file transfers over a network. Although IPsec and SSH are used for different applications and operate at a different layer of the TCP/IP model, they both use standard public-key and private-key algorithms to achieve their security goals.

One of the most common cryptographic protocols is TLS, which operates at the transport layer of the TCP/IP model. TLS is not application specific and is therefore widely used to establish secure data transmission. For this reason a detailed description of TLS will be given in the following sections. It should be noted however that TLS is just one application of the cryptographic algorithms that will be discussed throughout this thesis. The architectures may be applied to whatever cryptographic application is

required.

## 2.8 Transport Layer Security

The TLS protocol [29] supports a suite of cryptographic algorithms that can be used in many combinations to achieve the secure transfer of data. The fact that so many cryptographic algorithms are supported, with a varying degree of security levels, means that TLS is suitable for use on a wide range of devices. TLS is based around the privatekey and public-key algorithms that were discussed in the previous sections. A detailed description of TLS is given in the following sections, as the processes and algorithms used determine the requirements of a TLS coprocessor.

The TLS protocol operates at the transport layer of the TCP/IP model. As an example, data may be received over a network through the use of the *Transmission Control Protocol* (TCP) [102]. This data is then passed to the TLS record protocol which is responsible for the fragmentation, compression, and encryption of data. The TLS record protocol encapsulates four higher level TLS protocols: the TLS handshake protocol, TLS application data protocol, TLS ChangeCipherSpec Protocol, and the TLS Alert protocol, as shown in Figure 2.5. The TLS handshake protocol is used for setting up a shared secret between two parties and is based around public-key algorithms, such as the Diffie-Hellman key exchange [30]. The TLS record protocol is used to send encrypted data between two communicating parties that have already established a shared secret in some way (possibly through use of the the TLS handshake protocol). The TLS record protocol is based around private-key algorithms, which use block ciphers or stream ciphers to encrypt and decrypt the messages, while digital signatures are used to provide message authenticity and non-repudiation.

The TLS protocol uses different message types to transfer application data or information related to the protocol itself; each message is referred to as a TLS record. Each record has its own header and may be encrypted and protected by a *Message Authentication Code* (MAC). A MAC is a tag that can be appended to a message and allows the receiver to verify the message's integrity and authenticity. A MAC algorithm can be constructed from a block cipher, in which case the algorithm is referred to as a *Cipher-based Message Authentication Code* (CMAC) [32], or more commonly they are constructed from hash functions and referred as a *Hash-based Message Authentication Code* (HMAC) algorithm [68]. The HMAC algorithm generates a MAC based on the hash of the message and the sender's public key; thus, combining the ability of hash functions to provide message integrity, with the ability of public-key algorithms

Users Applications (TCP/IP Application Layer) TCP/IP transport layer TLS TLS TLS TLS App Data Handshake Change Cipher Alert Protocol Protocol Spec Protocol TLS Record Protocol TCP Data

to provide message authenticity.

Figure 2.5: Processing of a TLS message fragment.

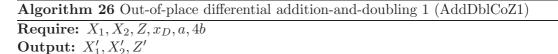

#### 2.8.1 TLS Record Protocol

The TLS record protocol uses private-key algorithms to encrypt messages sent between the two communicating parties. Once the handshake phase of the TLS protocol has been completed, some method of encrypting messages must be used. Public-key based systems are generally too computationally intensive for this type of application. A more common choice is to use either a stream cipher or block cipher to perform the bulk encryption operation. AES [91] in *Cipher Block Chaining* (CBC) mode [31, 33] is a popular choice for this purpose and is the current NIST standard block cipher. The TLS record protocol uses HMAC to provide message integrity and message authenticity.

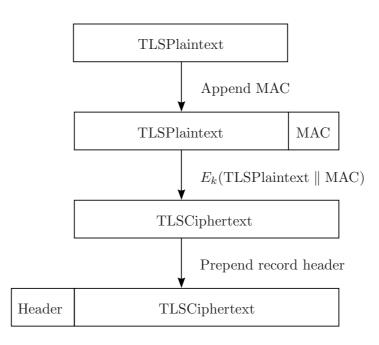

The process of encrypting a message begins by segmenting the data into blocks of  $2^{14}$  bytes or less. Each fragment to be encrypted is referred to as a *TLSPlaintext* fragment. At this point there is the option to compress the fragment; a process that is only executed if it was negotiated as part of the agreed cipher suite. A MAC is then calculated for the fragment and appended before encryption takes place. A TLS record header is prepended onto the encrypted *TLSCiphertext*; the data segment is now ready to be transmitted, this process is illustrated in Figure 2.6.

#### 2.8.2 TLS Alert Protocol

The TLS alert protocol allows each communicating party to signal that they have detected a problem with the session, or that they would like to close the session. The alert protocol supports two severity levels of alert messages: a warning message and a fatal error message. A *close notify* message is a type of alert message, with severity of

Figure 2.6: TLS protocol layers.

warning, that signifies that the sender is closing the connection. If either party detects an error in the TLS session, an alert message must be sent. If the error is considered fatal, the alert message is sent and the connection is immediately closed.

#### 2.8.3 TLS ChangeCipherSpec Protocol

The TLS ChangeCipherSpec protocol is used to notify the receiving party that the sender will be changing ciphering strategies. During the handshaking phase of setting up a TLS session, the initial messages exchanged are unencrypted. Once a party receives a *ChangeCipherSpec* message it signifies that all of the sender's communications, from this point forward, will be protected by the previously negotiated bulk encryption and MAC algorithms.

#### 2.8.4 TLS Application Data Protocol

The TLS application data protocol is simply the encrypted data carried by the TLS record protocol.

#### 2.8.5 TLS Handshake Protocol

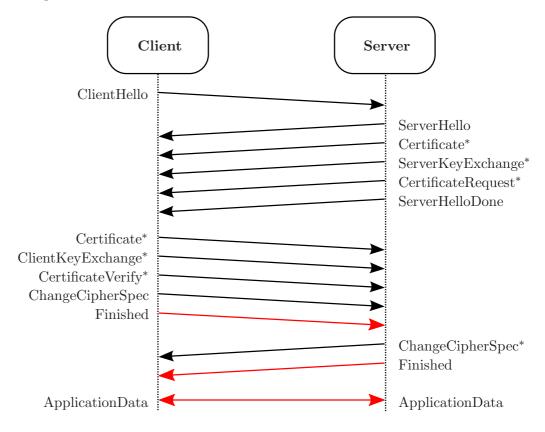

The TLS handshake protocol is used to establish a TLS session between two entities. The protocol supports many different algorithms for performing the negotiation of the shared secret. A typical handshake process, between a client and a server, is shown in Figure 2.7. The exact messages that are exchanged depend on the cipher suite that is negotiated by the first two *Hello* messages. Optional messages that are only sent by some cipher suites are shown with a "\*".

Figure 2.7: TLS handshake protocol.

The *ClientHello* message is sent by the client to notify the server of the cipher suites that it supports. Each cipher suite consists of a key exchange algorithm, a bulk encryption algorithm, a MAC algorithm and an algorithm to be used as the pseudorandom function. The client also generates a random number and sends it as part of the message. The *ServerHello* message is a response from the server that tells the client which security parameters it has accepted; the message also contains a random number generated by the server. These two messages also allow the client and server

to select which version of the TLS protocol is to be used. The descriptions that follow assume that the most recent version of the TLS protocol, TLSv1.2, is used.

The *ServerCertificate* message is sent if the algorithm parameters agreed upon support digital certificates for server side authentication. The certificate is an x.509 encoded data structure that contains the server's public key. Server side authentication is achieved through a trusted CA signing the certificate with the CA's private key.

The ServerKeyExchange message is only sent if the cipher suite that has been chosen allows for the negotiation of a shared secret based on a key that is different from the one contained in the server's certificate. This message is usually sent for cipher suites that make use of ephemeral keys. If ephemeral keys are not being used, the server's certificate should have contained all the information required to set up the premaster secret, and in this case the ServerKeyExchange message would not be sent. The premaster secret is used, along with the client and server random numbers, to derive the master secret and any keys required for the bulk encryption and HMAC functions.

The optional *CertificateRequest* message, sent by the server, is used if client side authentication is required by the negotiated cipher suite.

The *ServerHelloDone* message indicates that the server has sent all necessary data to the client in order for the client to continue with the key exchange process.

Once the client receives the *ServerHelloDone* message, it calculates its response and sends the data in the *ClientKeyExchange* message. The *ClientKeyExchange* message is always sent and contains the client's ephemeral public key. The client can, at this point, verify the certificate that has been sent by the server and generate the *master* secret based on the server's certificate or the data received in the *ServerKeyExchange* message, if it was sent. Once the server has processed the *ClientKeyExchange* message, both the server and client should have arrived at the same master secret.

The client then sends a *ChangeCipherSpec* message; this message notifies the server that all subsequent messages sent by the client will be encrypted with the agreed upon bulk encryption algorithm and authenticated with the HMAC algorithm.

This is then followed by the client's *Finished* message. This is the first encrypted message in the handshake process and contains a MAC and a hash of all previously exchanged handshake messages. Upon receiving the client's *Finished* message, the server can authenticate that the handshake was performed correctly by decrypting the *Finished* message and verifying that the MAC and the hash of handshake messages contained in the message matches the values that it has calculated.

The server then responds with its own *ChangeCipherSpec* and *Finished* messages.

Once the client has processed these messages, the handshake is complete and application data can then be exchanged through the use of the application data protocol.

#### 2.9 Field Programmable Gate Arrays

Throughout this thesis, designs will be implemented and tested on reconfigurable logic devices known as FPGAs. Therefore, an introduction into their structure will be discussed in this section.

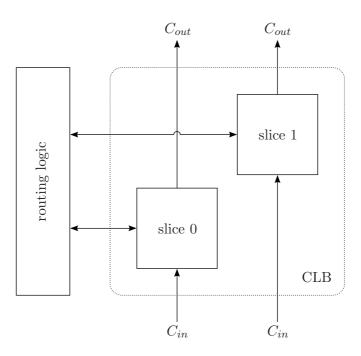

Field Programmable Gate Arrays (FPGAs) are a flexible platform that offer the ability to quickly test designs. Modern FPGAs contain not only large amounts of user programmable logic, but also dedicated hardware blocks that offer a high level of performance for specific applications, such as *Digital Signal Processing* (DSP) [134]. Some Xilinx Virtex 5 devices also contain PowerPC processors, Ethernet MACs, and high speed *Input/Output* (I/O) transceivers [131]. FPGAs consist of an array of *Configurable Logic Blocks* (CLBs) and routing logic that can be combined and configured to form complex combinational circuits. The CLBs and routing logic are arranged in columns throughout the FPGA chip. The internal structure of CLBs varies with different vendors and FPGA versions, however, all designs presented in this thesis are generated for members of the Xilinx Virtex 5 family of FPGAs [132]; hence, their structure will be discussed here.

In a Virtex 5 FPGA each CLB consists two slices, as shown in Figure 2.8. Each slice consists of four 6 input LUTs. The number of slices in a Virtex 5 FPGA ranges from 4,800 to 51,840, however, the version used for most of the results in this thesis is the XC5VLX110T, which has 17,280 slices. Each slice also incorporates fast carry chain logic which is designed to improve the performance of arithmetic circuitry. This is achieved by providing a dedicated path between slices for the carry signal, instead of having to route it through the standard routing logic. The carry chain connects slices in two vertically adjacent CLBs, as shown in Figure 2.8.

Each Virtex 5 FPGA also contains between 936 kbit and 18,576 kbit of *Block* RAM (BRAM) which is split into 36 kbit blocks. These blocks, however, can be combined in order to achieve larger memory sizes. BRAM resources are not part of the slice logic on the FPGA; therefore, they are presented as a separate result when used in any design in the following chapters.

Figure 2.8: Virtex 5 CLB structure.

#### 2.9.1 Microblaze Processor

Much of the work presented in this thesis concerns the design of coprocessors. In order to test the performance of these coprocessors in a real world environment, they must be implemented in a system where a GPP is also present. As the target platform for implementations are Xilinx devices, a Microblaze processor [130] is used as the GPP. A Microblaze is soft-core processor designed by Xilinx and is thus easily implemented on Xilinx devices. The Microblaze has a *Reduced Instruction Set Computing* (RISC) architecture and can be implemented using slice logic and BRAM resources on Xilinx FPGAs. The Microblaze can be configured to achieve different levels of performance by incorporating a floating point unit, dedicated multiply instruction, or a *Memory Management Unit* (MMU).

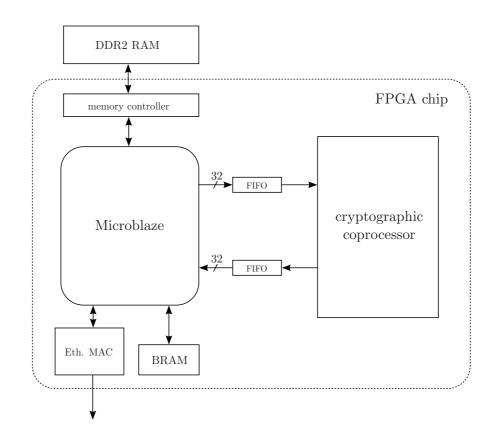

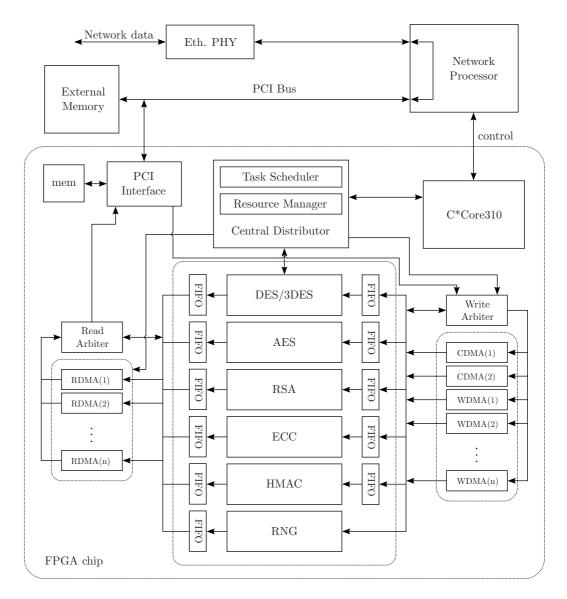

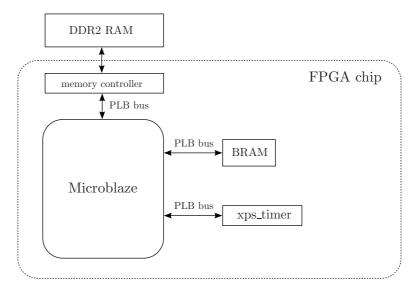

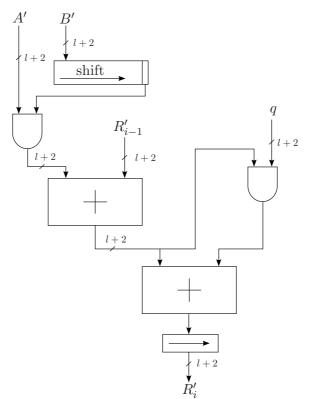

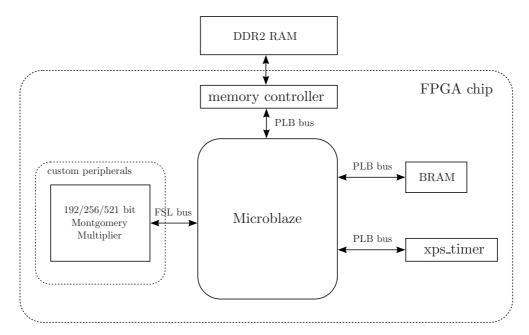

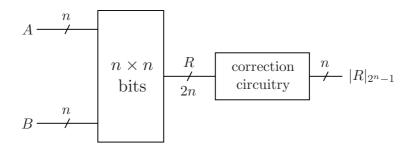

The test system used for many of the designs in the following chapters of this thesis is shown in Figure 2.9. The system is configured to include access to 256 MB of *Double Data Rate* (DDR2) *Random Access Memory* (RAM) through an external memory controller. The Microblaze also has access to a configurable amount of memory internal to the FPGA; this memory is implemented in BRAM. In some designs the system requires access to an Ethernet connection. This is done by utilising one of the embedded Ethernet *Media Access Controller* [133] modules present in the XC5VLX110T FPGA.

Figure 2.9: Example of an embedded SoC with a GPP and a coprocessor.

Each coprocessor is connected to the Microblaze via a Fast Simplex Link (FSL) bus.

#### 2.9.2 FSL Bus

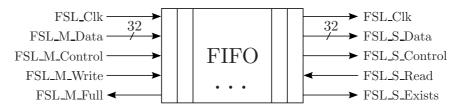

The FSL bus [129] is a high speed interconnect offered by Xilinx that allows the Microblaze processor to communicate with custom logic elsewhere in the FPGA. An FSL bus is unidirectional; hence, two FSL buses are required for two way communication with the coprocessor. The FSL bus consists of a *First In, First Out* (FIFO), of configurable depth, and 32 bits in width. The master side of the FSL bus controls the clock frequency, and writes data into the FIFO; while the slave side reads from the FIFO. An illustration of the FSL bus is shown in Figure 2.10. Data is sent from the master, into the FIFO, 32 bits at a time on the FSL\_M\_Data signal; the slave can then read from the FIFO. Valid data in the FIFO is indicated by the FSL\_S\_Exists signal being set high. A control signal, FSL\_M\_Control, is also present that is used to signal that a specific 32 bit block in the FIFO is a control word. The same setup is used in the opposite direction, for the coprocessor to send data to the Microblaze.

The clock signal, FSL\_Clk, is provided by the Microblaze; hence, the coprocessor must run at the same clock frequency as the Microblaze. The FSL bus used in the design presented in this work was configured to have a depth of 16, and to use LUT RAMs, as opposed to block RAMs. Each 32 bit data block takes 1 clock cycle to be written to the FSL FIFO.

Figure 2.10: FSL bus.

### 2.10 FPGAs and Cryptography

FPGAs have been a popular choice for implementing cryptographic systems in recent years. This mainly stems from their suitability for implementing large parallel bitwise operations and lower development costs than ASIC based solutions. FPGAs also tend to have lower energy consumption per bit than *Central Processing Unit* (CPU)/*Graphics Processing Unit* (GPU) based designs [117], as they can be configured for a specific task; this is of particular interest to designers of embedded systems. An overview of the area of implementing cryptographic algorithms on FPGAs can be found in [107].

Embedded systems generally contain a small processor and some custom hardware to perform their task. Unfortunately, a small GPP is not the ideal device for implementing cryptographic algorithms. Cryptographic algorithms usually have operands with bitlengths in the range of 128 to 1024 bits, and above, whereas GPPs are designed to work with data of bitlengths in the range of 8 to 64 bits. Embedded systems processors usually fall into the lower end of this range. To execute operations on operands of this size, a GPP will have to decompose the operands until they are sufficiently small so that the processor's ALU can operate on them. This decomposition increases the number of clock cycles required to process the data, which thus increases the overall computation time and can result in a computation time of over a second on small devices [49]. Although this length of time might be acceptable for certain applications, FPGAs offer a solution for reducing the computation time. FPGAs have the advantage that they can be configured to operate on the data in parallel. This makes them much more efficient than small GPPs for performing cryptographic operations. An added benefit is that an FPGA can be used to implement both the processor and the extra logic for performing cryptographic algorithms, all inside the same chip, as illustrated in Figure 2.9. This type of design is known as an SoC. FPGAs, however, have a limited amount of internal memory and for this reason, memory placed in an external chip is common practice. This can be done by implementing a memory controller inside the FPGA and having an external connection to a DDR RAM or *Static Random Access Memory* (SRAM) module.

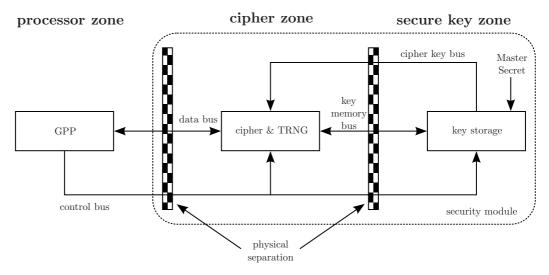

This poses a problem when the processor has to perform operations on any secret data stored in the FPGA, as the processor will have to have access the secret keys or secret data in cleartext, in order for it to operate on it. As a result, unless precautions are taken, the secret data will have to be transferred to the main memory, external to the chip. An attacker could simply read this data as it's transferred from the FPGA to the memory module. There are several solutions to this problem:

- 1. The system can be designed so that all data sent to and from the memory module is encrypted. This solution, however, is not very efficient and will have a big impact on the overall performance of the system. This is caused by the overhead involved in encrypting data before transferring it to and from the memory module, and is inefficient as not all data being processed needs to be kept secure. This solution also increases the logic resources required on the FPGA and does not protect against software based attacks [52, 54, 94].

- 2. The processor can be implemented such that it has a section of working memory implemented internally to the FPGA and when secure data must be processed, all calculations use this secure internal memory. However, this solution does not protect against the possibility of software based attacks, as the processor still has access to the secret data.

- 3. The other solution, the one presented in this work, is to design the SoC such that the processor never has to operate on the secret key data. In order to achieve this, all operations requiring the secret key data can be done inside a coprocessor. This has several advantages over the two previous solutions. Firstly, a small GPP is not a very secure platform to implement cryptographic algorithms. If an attacker gains the ability to execute code on the processor, the attacker could simply retrieve the secret keys from memory. With this solution, however, software

based attacks are negated. Secondly, in this design the coprocessor can be used to increase the performance of the system and also add resistance against attackers extracting the secret keys, thus adding protection against hardware based attacks such as *Side Channel Attack* (SCA).

## 2.11 Side Channel Attacks

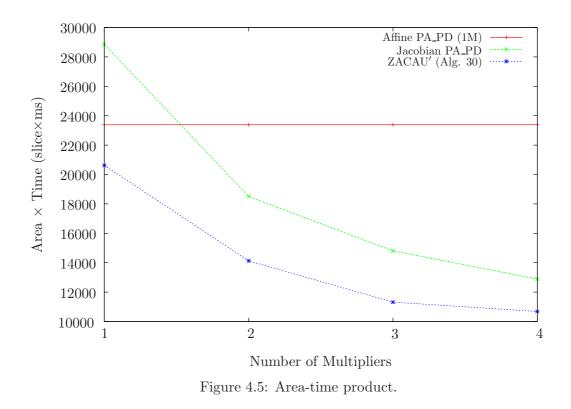

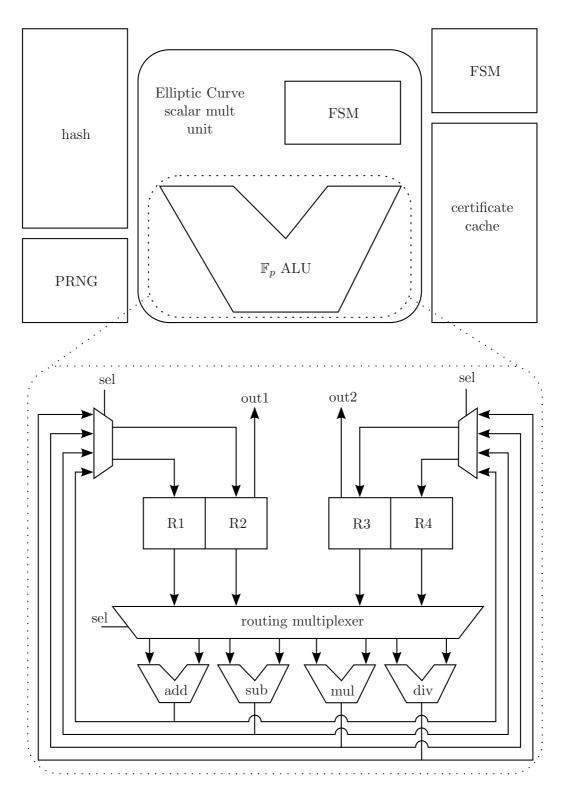

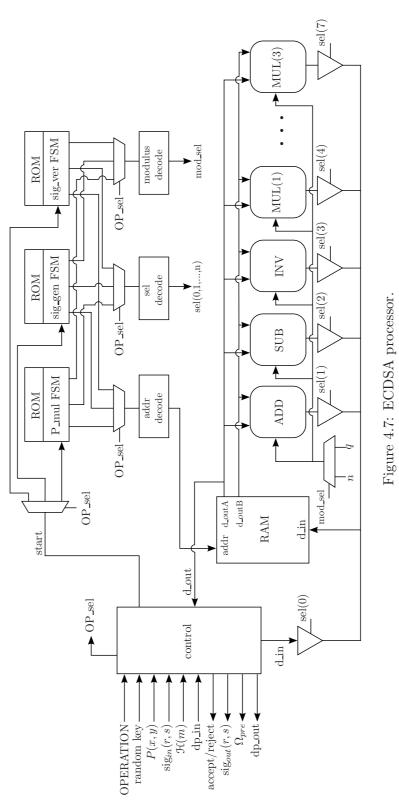

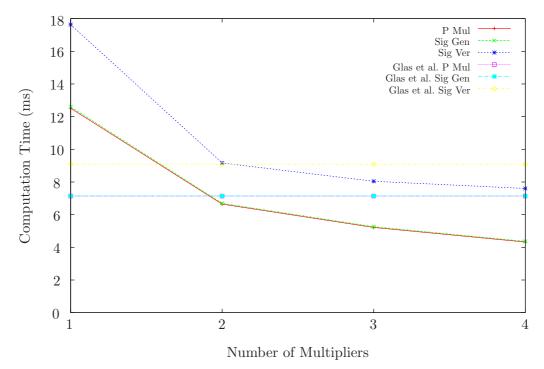

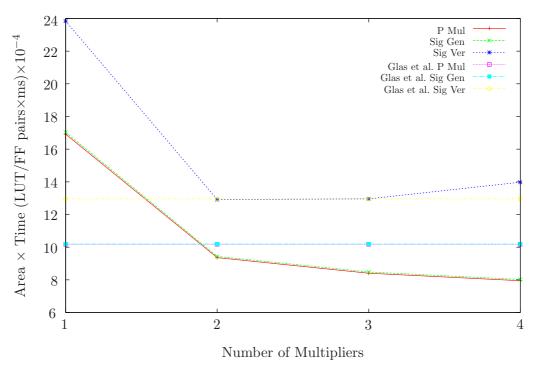

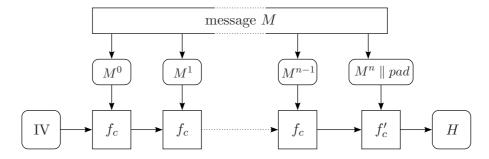

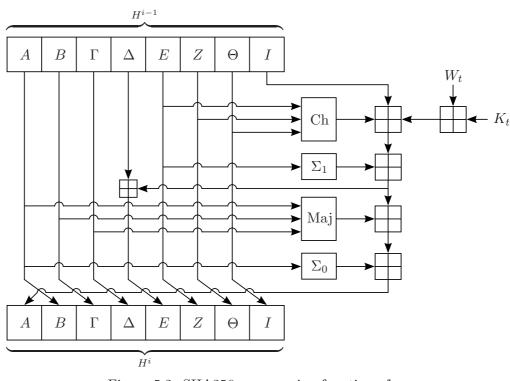

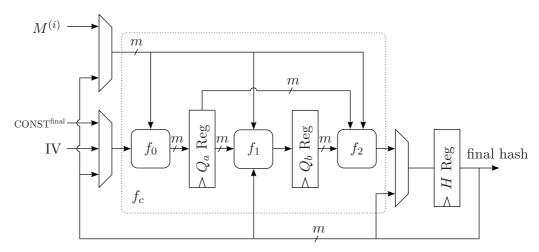

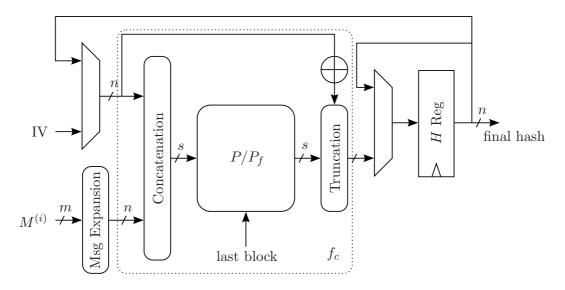

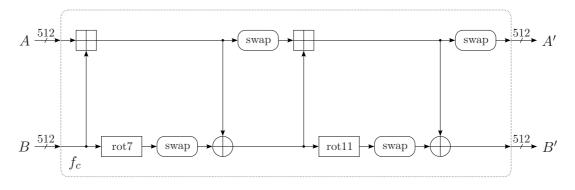

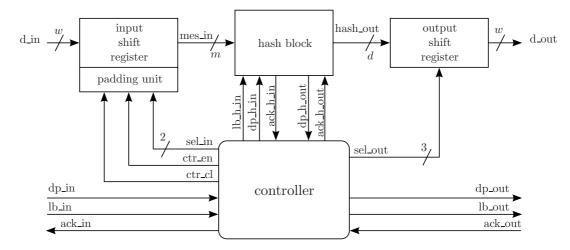

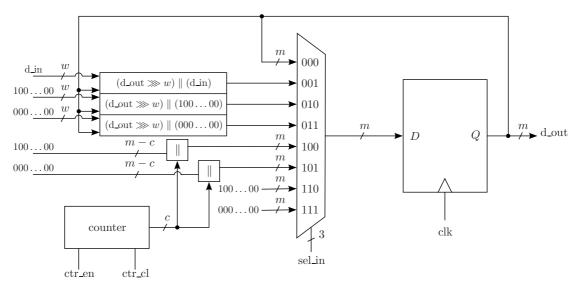

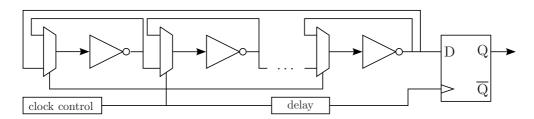

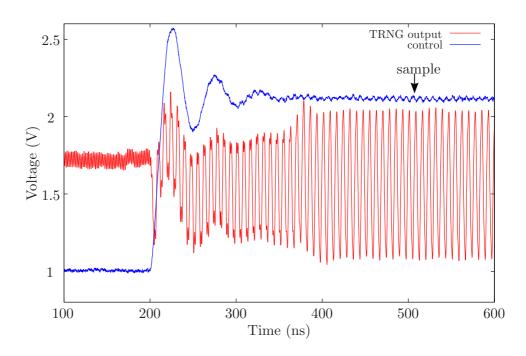

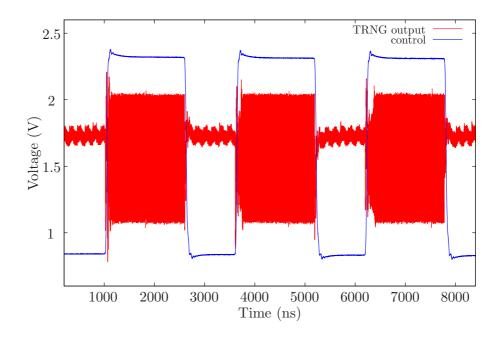

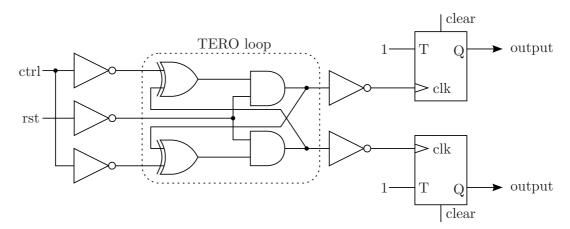

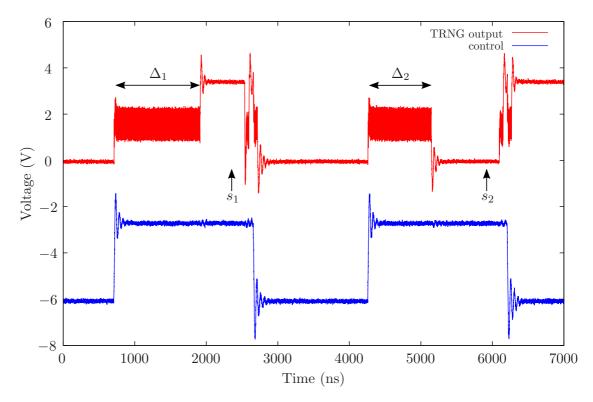

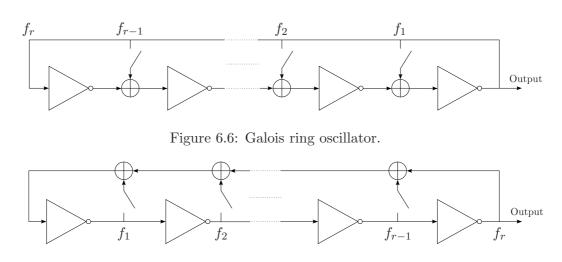

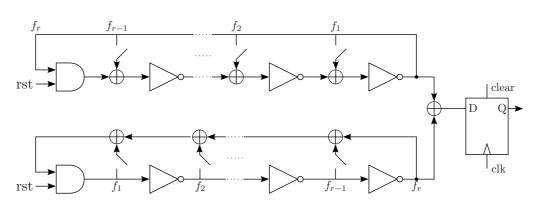

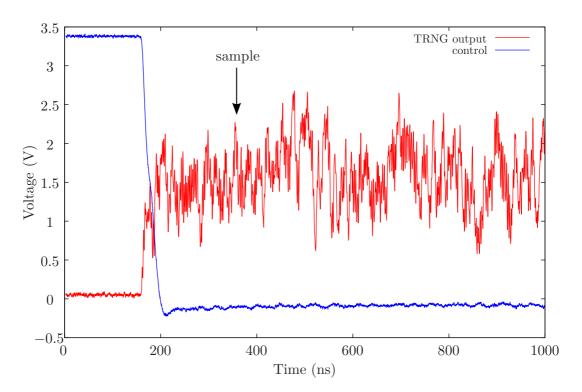

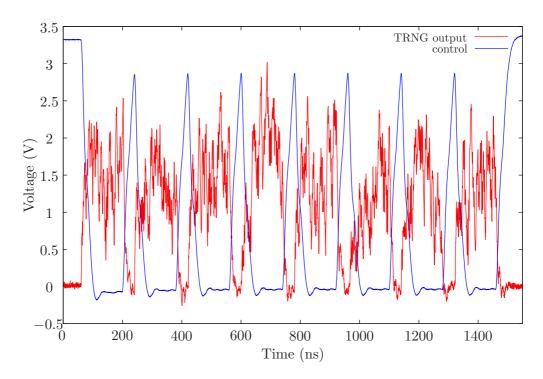

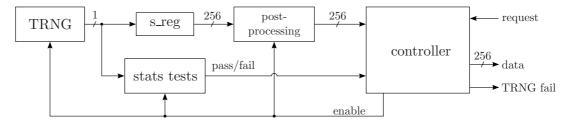

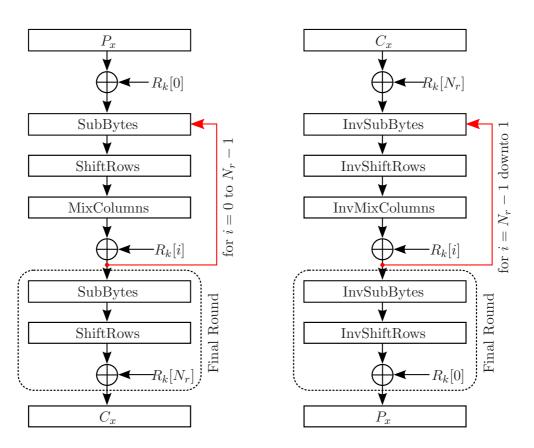

A secure cryptosystem relies not only on the theoretical security of cryptographic algorithms, but also on their secure implementation. In Section 2.4, the effect of a weak RNG implementation was discussed, where an adversary does not need to break the cryptographic algorithm if they can predict the secret keys that will be used. A generalisation of this approach can be applied to an entire cryptosystem and is referred to as an SCA. SCAs attempt to infer from physical emissions of the cryptosystem, sensitive information that the cryptosystem is operating on. This can be in the form of variations in the time it takes to perform a specific task [64], electromagnetic emissions [39], or the power consumption of the device [65].