| Title                | Conformal and non-destructive doping towards gate-all-around nanowire devices                                                         |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Authors              | Meaney, Fintan                                                                                                                        |

| Publication date     | 2020-09-01                                                                                                                            |

| Original Citation    | Meaney, F. 2020. Conformal and non-destructive doping towards gate-all-around nanowire devices. MRes Thesis, University College Cork. |

| Type of publication  | Masters thesis (Research)                                                                                                             |

| Rights               | © 2020, Fintan Meaney https://creativecommons.org/licenses/by-nc-sa/4.0/                                                              |

| Download date        | 2024-05-08 08:09:57                                                                                                                   |

| Item downloaded from | https://hdl.handle.net/10468/10585                                                                                                    |

# OLLSCOIL NA HÉIREANN, CORCAIGH NATIONAL UNIVERSITY OF IRELAND, CORK

# CONFORMAL AND NON-DESTRUCTIVE DOPING TOWARDS GATE-ALL-AROUND NANOWIRE DEVICES

THESIS PRESENTED BY

**FINTAN MEANEY**

FOR THE DEGREE OF

M.ENG.SC

UNIVERSITY COLLEGE CORK

SCHOOL OF ELECTRICAL ENGINEERING

TYNDALL NATIONAL INSTITUTE

HEAD OF SCHOOL: PROF. JORGE OLIVEIRA

SUPERVISOR: DR RAY DUFFY

### **Table of Contents**

| CHAPTER 1: INTRODUTION1 |                                                                    |    |  |

|-------------------------|--------------------------------------------------------------------|----|--|

| 1.1                     | Motivation and background                                          | 1  |  |

| 1 2                     | Silicon Doping                                                     | 3  |  |

| 1.2                     |                                                                    |    |  |

|                         | 2.2 Alternative Doping Strategies                                  |    |  |

|                         | 2.3 Alternative Annealing Strategies                               |    |  |

|                         | Alternative Affileating Strategies                                 | 11 |  |

|                         | Characterisation                                                   |    |  |

| 1.3                     | 7 1 OHI 1 1000 EACCHICH CHAIACICH SAHOH                            | 13 |  |

| 1.3                     | EJECHOCHEHIICAL CADACHANCE VOHASE UX.VI                            | 14 |  |

| 1.3                     | Secondary Ion Mass Spectroscopy (SIMS)                             | 16 |  |

| 1.3                     | Atomic Force Microscopy (AFM)                                      | 17 |  |

| 1.3                     | Secondary Electron Microscopy (SEM) and Energy-dispersive X-ray    |    |  |

|                         | spectroscopy (EDX)                                                 |    |  |

| 1.3                     | 3.6 Transmission Electron Microscopy (TEM) and EDX                 | 21 |  |

| IAN                     | VERAGE OF SUBSTRATE-RELEASED HORIZONTAL NOWIRES                    | 26 |  |

| 1                       | Background And Motivation                                          | 27 |  |

| 2.2                     | Experimental                                                       | 29 |  |

|                         | Results and Discussion                                             | 33 |  |

| 2.3                     | Dopain chemical and earner proming on planta samples               |    |  |

| 2.3                     | Electrical characterisation of CTENT device structures             | 37 |  |

| 2.3                     | Applicability analysis for Gate-Alf-Around (GAA) hallowire devices |    |  |

| 2.3                     | Spike anneal of TBA doped silicon                                  | 43 |  |

| .4                      | Conclusions                                                        | 44 |  |

| НА                      | APTER 3: ONE STEP LOW TEMPERATURE DOPANT                           | •  |  |

| ·CT                     | TIVATION OF THIN FILM SILICON DEVICES                              | 48 |  |

| 3.1                     | Introduction                                                       | 49 |  |

| 3.2                     | Experimental                                                       | 51 |  |

|                         | Proof of concept results                                           |    |  |

| 3.3                     | Results and Discussion                                             | 55 |  |

| 3.3                     |                                                                    |    |  |

| 3.4                     | Conclusion                                                         | 62 |  |

| 'HA                     | APTER 4: CONCLUSION                                                | 64 |  |

This work is adapted from the following journal publications, proceedings and conferences:

#### **Journal Publications:**

**F. Meaney**, K. Thomas, J. MacHale, G. Mirabelli, N. Kennedy, J. Connolly, C. Hatem, N. Petkov, B. Long, E. Pelucchi, R. Duffy, Applied Surface Science 508, 145147 (2020).

- J. MacHale, F. Meanev, N. Kennedy, L. Eaton, G. Mirabelli, M. White, K. Thomas,

- E. Pelucchi, D. H. Petersen, R. Lin, N. Petkov, J. Connolly, C. Hatem, F. Gity, L. Ansari,

- B. Long, and R. Duffy, Journal of Applied Physics 125, 225709 (2019).

- N. Kennedy, S. Garvey, B.M. Maccioni, L. Eaton, M. Nolan, R. Duffy, F. Meaney,

- M. Kennedy, J. Holmes, B. Long, Langmuir (2020) *In Review*.

#### **Conference Proceedings:**

- J. MacHale, **F. Meaney**, B. Sheehan, R. Duffy, N. Kennedy, B. Long, 2018 22nd International Conference on Ion Implantation Technology (IIT), 82-85.

- R. Duffy, <u>F. Meaney</u>, E. Galluccio, 237th ECS Meeting with the 18th International Meeting on Chemical Sensors (IMCS) (2020)

#### **Conference Presentations:**

**F.** Meaney, J. MacHale, B. Sheehan, R. Duffy, N. Kennedy, B. Long, 22nd International Conference on Ion Implantation Technology (IIT) (2018) Würzburg Germany. September 2018.

| This is to certify that the work I am submitting is my own and has not been subridegree, either at University College Cork or elsewhere. All external reference clearly acknowledged and identified within the contents. I have read an regulations of University College Cork concerning plagiarism. | s and sources are |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                                                                                                                                                                                                                                                                       |                   |

|                                                                                                                                                                                                                                                                                                       |                   |

|                                                                                                                                                                                                                                                                                                       |                   |

### **ACKNOWLEDGEMENTS**

I want to express my sincere appreciation to my supervisor Dr. Ray Duffy; his support and guidance were invaluable throughout my 2 years at Tyndall.

I would like to express my thanks to both Applied Materials and Enterprise Ireland for making it possible to pursue my research.

I would like to thank everyone in Tyndall and UCC, whose individual contributions are too long to list, for providing the excellent framework, research support, and kind words of motivation in moments when they were all needed.

Thank you to all my collaborators, both internal and external, for insight and expertise. Good research requires many people working together, and I have been lucky to have had some of the best.

I would like to thank my family whose emotional and daily support, from which I rely heavily on in all aspects.

### LIST OF ABBREVIATIONS

1D One Dimensional

2D Two Dimensional

3D Three Dimensional

μ-4PP Micro Four Point Probe

ADP Allyldiphenylphosphine

AFM Atomic force Microscopy

As Received

BOE Buffered Oxide Etchant

CMOS Complementary Metal Oxide Semiconductor

CTLM Circular Transfer Length Method

DIBL Drain-Induced Barrier-Lowering

DoS Density of States

EBL Electron Beam Lithography

ECV Electrochemical Capacitance Voltage

EDX Energy-dispersive X-ray spectroscopy

ERDF European Regional Development Fund

FET Field Effect Transistor

FinFET Fin Field effect Transistor

GAA Gate All Around

HAADF High Angle Annular Dark Field

HF Hydrofluoric Acid high-k High Dielectric Constant HMDS hexamethyldisilazane

HRTEM High Resolution Transmission Electron Microscope

HSQ Hydrogen Silsesquioxane ICP Inductively Coupled Plasma

I/O Input / Output

I-V Current-Voltage

IPA Isopropyl Alcohol

IRDS International Roadmap for Devices and Systems

LTA Laser Thermal Anneal

n-MOS n-Type Metal Oxide Semiconductor

NVM Non-Volatile Memory MLD Monolayer Doping

MOSFET Metal Oxide Semiconductor Field-Effect Transistor

MOVPE Metal Organic Vapour Phase Epitaxy p-MOS p-Type Metal Oxide Semiconductor

RF Radio Frequency

RIE Reactive Ion Etch

RMS Root Mean Squared

R<sub>sd</sub> Source-Drain Series Resistance

RTA Rapid Thermal Anneal

SEM Scanning Electron Microscopy

SLM Standard Litres per Minute

SSRM Scanning Spreading Resistance Microscopy

STEM Scanning Transmission Electron Microscopy

Si Silicon

SIMS Secondary Ion Mass Spectrometry

SOD Spin on doping SOI Silicon on insulator

SPER Solid Phase Epitaxial Recrystallization

SRAM Static Random Access Memory

TBA Tertiarybutylarsine

TED Transient Enhanced Diffusion

TEM Transmission Electron Microscopy

USJ Ultra Shallow Junction

UV Ultraviolet

XTEM Cross Sectional Transmission Electron Microscopy

XSTEM Cross Sectional Scanning Transmission Electron Microscopy

### **Candidates Contributions**

Sample processing and characterisation during this project was a joint effort of myself and other member of Tyndall and UCC.

Interpretation of results and experimental planning was a joint effort of all members of the CONDUCT2 project, with insight from collaborators both internal and external.

Any work completed outside of Tyndall/UCC is clearly stated within the text.

Thesis creation was primarily my responsibility, with crucial editing and suggestion for colleagues.

#### **Abstract**

Due to the approach of fundamental 2D topological limits, scaling of silicon transistors towards GAA devices will be required.

This thesis will discuss why continued scaling towards GAA devices will require novel doping processes and suggest possible technologies to suit this application.

Chapter 1 will detail an introduction to this topic and discuss current possible solution to 3D doping as well as explain some of the different techniques uses throughout the work

Chapter 2 discusses gas phase doping as a promising candidate as it has a superior ability to conformally dope tight 3D architectures, when compared to ion implantation. This process needs to be optimised to find a balance between the potential to etch on one hand and deposit potentially unwanted layers on the other. Further work currently ongoing to limit the thermal budget of these process will also play a critical role in their applications in modern semiconductor processing where temperature sensitive materials are ever more present.

Chapter 3 presents a one step process that simplifies traditional ion implantation while also displaying a possible route toward high levels of activation at lower temperatures. The electrical characterisation of these devices will show how this process needs further optimisation to reach conductivity levels required for GAA transistors.

#### 1.1 MOTIVATION AND BACKGROUND

The semiconductor industry has matched the pace of that predicted by Moore's Law for over 50 years, doubling the number of transistors every two years on average<sup>1</sup>. As a consequence, as transistors became smaller, they could also be switched from the off to the on state at faster rates while simultaneously they became cheaper to manufacture.

Fundamental 2D topological limits have been threatening the ability of the semiconductor industry to continue scaling at these historical rates. The FinFET structure was developed to provide better electrostatic control of properties such as subthreshold leakage and saturation current over planar devices while permitting the use of sufficient device current drive. However, as the advanced silicon patterning technologies are shrinking devices down to a 5 nm technology node and below, subthreshold leakage and drain-induced barrier-lowering (DIBL) are imposing the need for a new type of MOSFET. GAA field effect transistors are shown to be the potential candidates for these advanced nodes, due to the presence of the gate on all sides of the channel. This allows even greater electrostatic control than that offered by FinFET architectures.

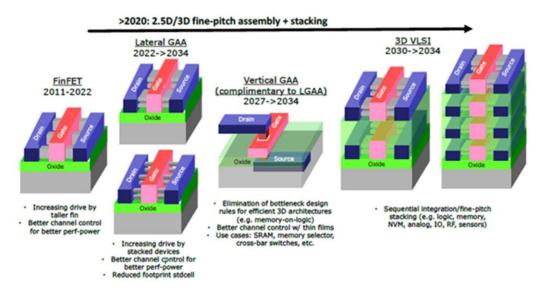

Shown in Figure 1, the international roadmap for devices and system (IRDS) 2018 update anticipates FinFET production is likely to sustain until 2025<sup>2</sup>. Beyond 2022 a transition to GAA devices is expected to begin, potentially for 3D hybrid memory-on-logic applications. After 2031 there is no longer room for 2D geometry scaling, where 3D stacking/integration will be the driving force for the continuation of scaling. This is due to performance decreases from scaling beyond this point counteracting any perceived benefits of device scaling. Benefits of scaling channel length below 12 nm would be counteracted by

negative electrostatics, while gate pitch scaling would therefore saturate around 40 nm, allowing enough room for two 14 nm contacts necessary to keep contact resistance to an acceptable level. For the vertical GAA (projected advent ~2027), physical gate length scaling could be relaxed as the gate length is measured in the vertical direction with respect to the substrate instead of contributing to the device 2D footprint. But the advantage of this is constrained by the power penalty as a result of the increase in the channel capacitance due to increased gate lengths. After ~2031 it is theorised 2D scaling will have run out of its bag of tricks. If scaling is to continue 3D geometries must be considered.

Continuation of scaling is for the most part achieved through the optimization of established processing techniques. The advantages of this continual optimisation are obvious as it allows the production of more advanced devices without the need to reinvent the wheel. This premise has been a roadblock for technologies which have shown potential advantages over current methods, requiring these technologies not only to be advantageous to current methods but generally to address some unassailable bottlenecks in current methodologies.

Figure 1 IRDS MOSFET Predicted Timeline<sup>2</sup>

#### 1.2 SILICON DOPING

One such bottleneck, predicted to limit the scaling of devices, is the requirement to conformally and non-destructively dope sub 10 nm 3D Gate All Around (GAA) devices. Traditionally ion implantation is used to dope devices. This process rapidly accelerates single ions of dopant and "implants" the devices with these ions. This process has many advantages such as high level of control over dopant dose and concentration, high level of control over the depth of dopant atoms, and relativity low process complexity. A major challenge for GAA devices is the increase in parasitic effects as the nanowire dimensions are scaled. This results in large part from the difficulty to achieve a high active dopant concentration while maintaining junction abruptness in such a small three-dimensional (3D) Si area. Optimising device resistance requires high levels of control over dopant incorporation, diffusion and activation.

Ion implant has disadvantages for the doping of sub 10 nm GAA devices. Some of these are damage caused to the semiconductor crystal caused by ion bombardment and an inability to dope outside the line of sight on the ion beam. These problems are manageable in larger, planar devices however for scaled GAA devices the percentage of the device crystal that is damaged

increases and may be difficult to anneal out, and when GAA devices are stacked accessing the devices with the beam becomes difficult due to shadowing.

#### 1.2.1 **Implant Damage**

One of the issues for the future use of ion implantation in the semiconductor industry is the surface damage to crystalline Si caused by the implantation process itself<sup>4</sup>. Ion implantation dopes materials by accelerating a beam of the dopant ions at a target, giving the ions enough kinetic energy to embed themselves in the target material. In the case of crystalline materials, this addition of dopant ions causes physical damage the crystal lattice. The kinetic energy allows the ions to break the surface of the crystal, colliding with atoms deeper within the crystal until the ions lose their momentum through collision. The ions then come to rest within the substrate crystal. During this process, the destructive force supplied by the ions creates silicon vacancies and interstitials within the crystal. These silicon defects change the electronic properties of the crystal, such as conductivity and mobility. Coupled with this, the dopant ions are only electrically active when they substitutional dope the silicon crystal. If the dopant ion is not sitting in a crystal lattice location, it is said to be inactive and does not contribute to the electronic properties of the substrate.

Currently in industry, substrates are annealed after ion implantation in an attempt to repair damage caused to the crystalline silicon by the implantation process and give the dopant ions sufficient energy to find a substitutional location within the crystal, electrically activating the dopants to give the required electrical properties.

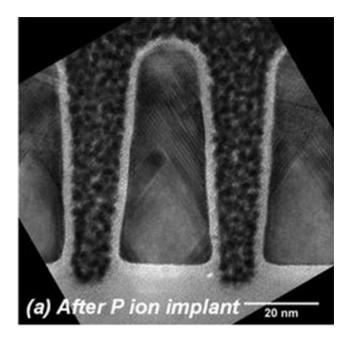

The damage caused by ion implant is often extensive enough that the subsequent annealing step does not remove all crystal defects and instead defects evolve from simple point defects into {311} rod-like defects and eventually into dislocation loops, or as in Figure 3 of an ion implanted fin<sup>5</sup>, into twin boundary or stacking fault type defects.

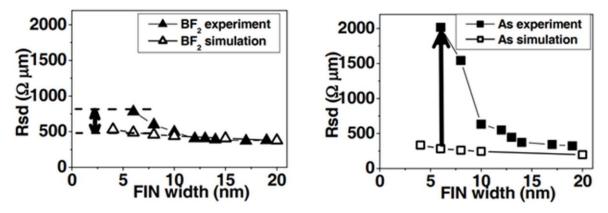

Annealing the substrate can also drive the dopant ions deeper into the sample, which is an unwanted effect when trying to generate ultra-shallow junctions (USJs) necessary for modern transistor devices. Post-implantation annealing is also affected by transient-enhanced diffusion (TED). TED is an effect still under investigation, where it is thought that the large excess of crystal defects like vacancies or interstitials increases the dopant's ability to locally diffuse, leading to a broader junction than classical interpretations would predict<sup>6-8</sup>. Additionally, as transistors scale down, these process issues become more significant, and have become a limiting factor to device performance. Implant amorphisation in 3D silicon devices can be more detrimental than would be expected in planar devices. It is proposed that this is due to the fact that in planar devices there is a very large amount of silicon that the device silicon area can seed from opposed to a geometrically isolated fin which has to recrystallize from a damaged or absent seed. This leads to a defect rich or polycrystalline device area and a corresponding increase in source-drain series resistance (R<sub>sd</sub>) shown in Figure 3<sup>9-11</sup>.

Figure 2 TEM images taken after implantation and RTA of a Si nanowire. The phosphorus implantation was performed at room temperature at 45° tilts left and right. Twin boundary defects are still evident post RTA likely to affect electrical behaviour<sup>5</sup>

Figure 3 Rsd vs. fin width for pMOS FinFETs with a) BF2 self-amorphising extension implants and b) As self-amorphising extension implants. Simulations match experiments for Fins wider than 10nm. Below 10nm, a clear deviation is observed believe to be caused by poor recrystallization due to a large area of the device amorphising. pMOS FETs were affected less as the implant was less amorphizing  $^{11}$

#### 1.2.2 Alternative Doping Strategies

One method investigated to tackle issues with ion implantation for GAA devices, was to test other methods of introducing silicon dopants.

#### 1.2.2.1 Gas Phase Doping

Gas-phase doping was tested as a 3D silicon device doping method. Unlike ion implantation, gas-doping is not beamline limited. Gas doping can be a conformal method, as the gas has equal access to all surfaces of the Si device. This contrasts with ion implantation, which is a line-of-sight limited. GAA devices can suffer severe shadowing effects when using ion implantation, as the device topography and vertical stacking limits the effective doping of devices. Gas-phased doping was tested for uniformity of dopant deposition in 3D geometries during this project, to overcome this current bottleneck.

Gas phase doping was also investigated with respect to silicon surface damage caused by the doping process. A well-studied issue is damage to the silicon crystal caused by physical ion implantation. As devices scale down, the effects of crystal damage become more severe, and can become a limiting factor in device manufacturing 12,13. Gas-phase doping is being investigated as a damage-free method of introducing dopants to Si devices. This is necessary in industry as all Si damage in manufacturing can lead to irregularities or failures in device performance and introduces uncertainty to the production yield.

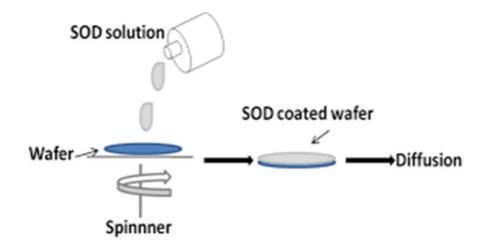

#### 1.2.2.2 Spin on Doping

Figure 4 Spin on doping process. A mixture of a solution of SiO2 and dopant containing molecule is dispensed on the wafer and spun to distribute. The wafer is then subjected to a high temperature anneal to drive in and activate the dopant  $^{14}$

Spin on-doping (SOD) is a process where dopant containing solution is spun onto the substrates, which is followed by an RTA step where the dopants diffuse into the substrate. The dopant-containing solution comprises a mixture of SiO<sub>2</sub> (glass) in solution and dopant molecule which is why the process can also be called spin-on-glass (SOG). SiO<sub>2</sub> solutions are typically used as they can be readily formed, resist high annealing temperature, and theoretically removed using standard semiconductor processing.

Advantages of SOD are process simplicity, low toxicity, low cost, and no explicit substrate damage this has historically made the process attractive to solar cell manufacturing where wafer cost is of utmost importance<sup>15,16</sup>. However, these dopant containing glasses are sometimes not easily removed as the high concentration of dopant molecules inhibit the etching of the SiO<sub>2</sub> using standard HF chemistries. This can lead to damage to the substrate if more aggressive chemistries are used or residues if the SOD is not completely removed. SOD also suffers from conformity issues when dealing with high aspect ratio or 3D devices.

#### 1.2.2.3 Plasma Doping

Plasma doping is where a Si wafer was directly immersed in plasma containing doping species. Most applications of plasma doping are to form an ultra-shallow junction (USJ)<sup>17,18</sup>. This is due to advantages Plasma doping has over ion implantation, as by immersing the samples in a dopant containing plasma the issues surrounding low energy implants such as low ion flux can be avoided. However, contamination is sometimes an issue with plasma implantation when compared to ion implantation<sup>19</sup>. Substrate bias is used to accelerate and implant the ions into the sample this can lead to similar issues as with ion implantation such as directionally and therefore lack of conformity and damage induced by ion implantation<sup>20</sup>. Generally, a high temperature anneal is performed post plasma immersion to anneal out the damage caused and activate the dopants.

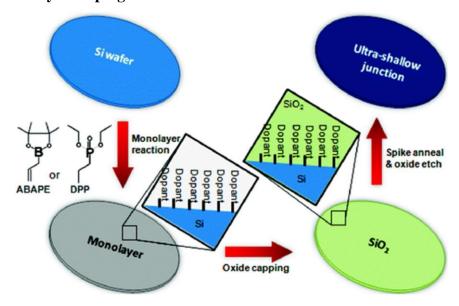

#### 1.2.2.4 Monolayer Doping

Figure 5 MLD Process. The sample is degreased, then a monolayer of the molecule that contains the target dopant is attached to the surface of the sample. A capping layer is applied to encapsulate the dopant containing monolayer and prevent it from volatising during the high temperature anneal.<sup>21</sup>

MLD involves the use of wet chemistry to dope the substrate. The primary method of doping silicon using MLD involves the hydrosilylation reaction. This reaction covalently bonds an organic dopant molecule to a hydrogen-terminated silicon surface prepared by etching the native silicon oxide and h-terminating the surface with a HF treatment. MLD typically then requires a capping layer to prevent volatilisation of the dopant molecule during the high temperate annealing step used to drive in and activated the dopants.

MLD has the advantage of being potentially conformal, damage free, and highly controlled. However, MLD still suffers from an inability to get dopant dose required for source and drain implants in transistors where it's potential to create damage free USJ is of most interest.

#### 1.2.3 Alternative Annealing Strategies

#### **1.2.3.1 Spike RTA**

Spike annealing is similar to that of furnace annealing in that it used conventional means of heating to achieve activation and diffusion of dopants. The difference is in the ramp rate of the temperature with modern spike anneals is much higher (>400°C/s) than that of conventional processing allowing less time at peak temperatures and reducing diffusion. The issue with this is being able to both have high ramp rates but also get high control over the peak temperature and ramp rate enabling junction doping control<sup>22</sup>. This high ramp annealing also causes massive thermal strain on the wafer and can lead to wafer breakages.

#### 1.2.3.2 Laser Thermal Anneal (LTA)

Laser thermal annealing involves using laser pulses to locally melt the silicon and incorporate dopants and then the silicon recrystallizes as it solidifies. Dopant activation in this way can be effectively diffusion-less and incorporation greater than that of the solid solubility can be achieved in the liquid phase. However, this process has some important integration issues as it can cause deformation of materials that have melting points below that of silicon that don't recrystallize in the same way silicon does. Materials with different light adsorption properties will also lead to cross wafer temperature variations that can build stress and lead to wafer breakages<sup>23</sup>. Metastable materials could also potentially revert to more stable forms under the energy supplied from the laser.

#### 1.2.3.3 Solid Phase Epitaxial Recrystallization (SPER)

Solid phase epitaxial recrystallization takes advantage of the greater rate of dopant incorporation that is seen while amorphous silicon is recrystallizing. Ion implantation is typically used to amorphise the silicon and low thermal budget recrystallization anneals (~600°C) can be used to recrystallize the silicon while incorporating dopants. This technique

has been shown to activate dopant to metastable levels far above their solid solubility at their recrystallization temperature and can even activate dopants to similar or greater levels than that of other techniques using much higher thermal budgets. However, this metastable activation is as the same suggests quite often not stable and subsequent annealing can deactivate the dopants.<sup>24</sup>

#### 1.3 CHARACTERISATION

In the following section the analytical techniques used during the Masters project are detailed.

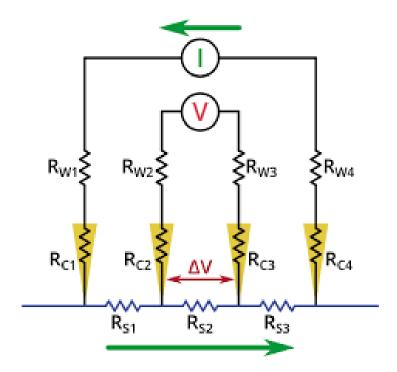

#### 1.3.1 4-Point Probe Electrical Characterisation

Figure 6 4-Point Probe setup. A known current is applied across the sample using the outside probes. The voltmeter shown V has a very high impedance meaning practically no current flows through the two inner probe circuit. This means that the measured decrease in voltage  $(\Delta V)$  is only dependant on Rs2 (the sample resistance) impeding the flow of current. Applying ohms law resistance can be calculated trivially<sup>25</sup>

The four-point probe is commonly used to measure the semiconductor resistivity. Two-point probe methods would appear to be simpler to conduct, because only two probes need to be used. But the interpretation of the measured data is more difficult. In two-point probe measurement each contact serves as a current and a voltage probe. The total measured resistance is a sum of the probe resistance, the contact resistance, and the resistance of the device. It would be very difficult to separate the resistance of the device in this test. The solution to this is the four-point probe. The current path setup is identical to that as the 2-

point probe; however, the voltage is now measured with two additional contacts. Although the voltage path still contains the probe and contact resistances, the current flowing through this path is very low due to the high input impedance of the voltmeter. The parasitic resistances are therefore negligible, and the measured resistance is dominated by that of the device of interest. In this way we can calculate the devices sheet resistance, and this can be easily converted to resistivity in confined 2D devices as with the Circular Transfer Length Method (CTLM) devices in this study.

#### 1.3.2 Electrochemical Capacitance Voltage (ECV)

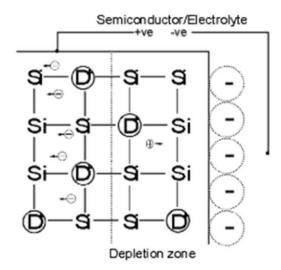

Figure 7 ECV setup for n-type semiconductor. A negative applied voltage is applied to create a depletion region by repelling donor electrons. The capacitance of this depletion region is measured to calculate carrier concentration<sup>26</sup>

ECV is a tool to measure active doping profiles in semiconductors. The semiconductor sample is attached to an electrochemical cell, creating a depletion region between the sample and the electrode. The capacitance of this depletion region is measured, and information of the doping and electrically active defect densities can

be extracted from the relationship:

$$N = \frac{1}{q \,\varepsilon_0 \,\varepsilon_r A^2} \times \frac{C^3}{\frac{dC}{dV}}$$

N = Carrier concentration

q = Electron charge

$\epsilon_0$  = Permittivity of free space

$\epsilon_r$  = Relative permittivity of the

semiconductor

A = Contact area

C = Depletion region capacitance

V = Applied voltage

Depending on the dopant type of the semiconductor, different conditions must be used to introduce positive or negative ions to the electrolyte. For p-type semiconductors (where the charge carriers are holes) positive ions are introduced via electrical current. For n-type semiconductors (charge carriers are electrons), a UV light is used to introduce a positive charge. ECV is a destructive process as etching of the semiconductor allows for depth profiling of dopants within the semiconductor device.

#### 1.3.3 Secondary Ion Mass Spectroscopy (SIMS)

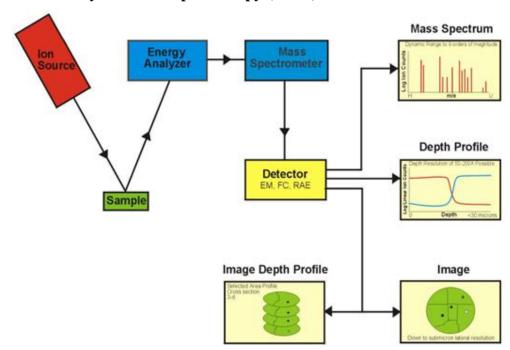

Figure 8 Schematic of a SIMS instrument.<sup>27</sup>

SIMS focuses an ion source to sputter the surface of the sample by bombardment. The atoms or "secondary ions" that were sputtered are then collected, focused, filtered based on their kinetic energy in the energy analyser, and based on their mass to charge ratio at a defined kinetic energy in the mass spectrometer. Finally, the filtered ions are collected and detected and depending on the arrangement being used can be displayed in a variety of ways. Dynamic SIMS is a mode where the primary ion beam has a continuous beam of (relatively) high energy, allowing to study the ion concentration at the depths of nanometers to microns within a sample by sputtering deeper into the sample<sup>28</sup>.

#### 1.3.4 Atomic Force Microscopy (AFM)

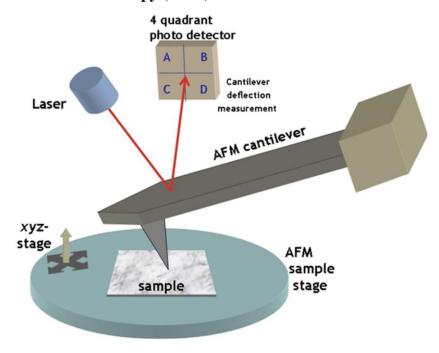

Figure 9 Atomic Force Microscope Setup.<sup>29</sup>

AFM is a form of scanning probe microscopy. A cantilever with a very sharp tip is brought near or in contact with a surface, and scans over the surface using piezo control units. As the tip approaches the surface the attractive force between the surface and the tip cause the cantilever to deflect towards the surface. However, as the cantilever is brought closer to the sample the repulsive "contact" force takes over and causes the cantilever to deflect away from the surface. A laser beam focused on the cantilever is used to detect deflections towards or away from the surface. If the AFM tip passes a surface feature, the resulting cantilever deflection, and the subsequent deflection of the laser is recorded via a light sensitive detector, allowing accurate tracking of the change in height of the sample, or roughness.

Tapping mode (also known as intermittent contact mode) was used over the course of the project. The tip is driven to oscillate near its natural resonance frequency. As the tip approaches the sample surface, it interacts with the surface via non-contact forces, either Van

der Walls forces, electrostatic forces or dipole-dipole forces. This force interaction measured as a deflection on the light sensor also provides an electronic signal to the system informing it whether the cantilever height needs to be changed to be kept at a constant distance to the sample. Tapping mode was preferred as it can lessen surface damage to the sample compared to contact AFM mode. The tip is in contact with the surface for a shorter period, and with less force, leading to fewer issues with sticking of the tip on a rouge surface or "gouging" of the surface if it is less hard than the tip.

## 1.3.5 Secondary Electron Microscopy (SEM) and Energy dispersive X-ray spectroscopy (EDX)

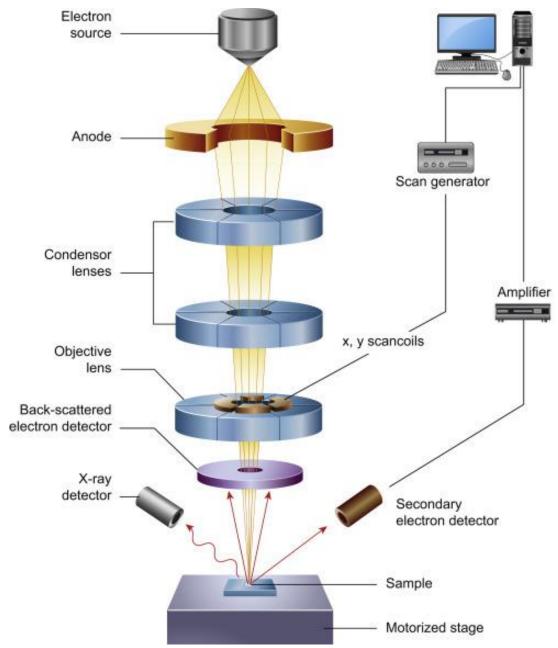

Figure 10 Cross section of a SEM setup.<sup>30</sup>

SEM is an electron microscopy technique where the electron source generates electrons that are attracted to the anode and accelerated towards the sample. The beam of electrons is focused and shaped to a small circular probe on its path as it passes through the condenser lenses.

The objective lens focuses the beam on the sample while the scanning coils raster the beam over the sample. The beam interacts with the sample resulting in secondary electron produced from the sample surface containing topographical information. The secondary electrons are released from atoms in the sample which were excited by the electron beam. SEM was used in this project to get overview images of fabricated nanowires and CTLM devices and a higher resolution compared to conventional light microscopy images. Secondary electrons are generated close to the surface of the sample (few nanometres below the surface), thus contains a lot of information on the surface quality of devices imaged<sup>31</sup>.

In EDX imaging as the electrons scan the sample, energy is absorbed by the sample, exciting the electrons. This energy is then re-emitted as characteristic x-rays when the electrons drop back to their ground state. An x-ray detector measures the energy and number of x-rays emitted. The energy of the x-ray is a unique characteristic to the change in energy shells of the element in which the x-ray was produced. This allows the generation of an elemental composition of the sample surface.

### Electron source Anode Condensor lenses Condensor aperture STEM scan coils X-ray detector Objective lens Sample Objective aperture Selected area aperture Projector lenses BF, ADF, HAADF detectors Viewing screen CCD camera or photographic plates **EELS** detector

#### 1.3.6 Transmission Electron Microscopy (TEM) and EDX

Figure 11 Cross section of a TEM setup<sup>30</sup>

Magnetic prism

TEM is a form of microscopy where an electric field directs an electron beam onto a thin sample, with nanometre scale precision. The electron source generates electrons that are attracted to the anode and accelerated towards the sample. The beam of electrons is focused and shaped to a small circular probe on its path as it passes

CCD camera

through the condenser system. In STEM imaging mode as in SEM the scanning coils scan the beam over the sample. The beam is then transmitted through the sample and the resulting through beam is focused using the objective system on the detectors. An image of the sample's atomic structure can, therefore, undergo construction through the information gathered from the electrons<sup>32</sup>.

For EDX as in SEM the x-rays are collected near the sample, along with the imaging information this can be used for elemental mapping. Also shown in Figure 11 is an EELS detector which gathers information about electrons that interacted with the sample losing kinetic energy, which again can be linked to various information about the sample. Not shown in Figure 11 are the aberration correctors and monochromator used to obtain higher spatial and energy resolution respectively. This is a simplified explanation of a TEM, which can come in several different forms, using different electron beams and configurations to gather different information about a sample.

Scanning transmission electron microscopy (STEM) is a form of TEM which can also reach a high resolution, sometimes even higher than high resolution TEM. For STEM, the electron beam is passed through a condenser system to make an electron probe that can vary in diameter size from 0.1-10 nm<sup>33</sup>. This probe is then scanned over the sample so that the probe passes through the rows of atoms. The STEM setting has advantages over the conventional TEM of being able, apart from reaching a very high resolution, able to record secondary and backscattered electrons and being very useful in analytical microscopy. STEM mode is used for EDX (energy dispersive x-ray spectroscopy), which was used during the project. Since a scanning electron probe is used in STEM-EDX, the location of each characteristic X-Ray source is known, allowing elemental maps to be built of the sample. EDX in TEM has some

advantages over its use in SEM with higher beam energy 300 kV TEM beam energy allowing excitation of emission lines not possible at 30 kV used in SEM and increasing x-ray count numbers allowing qualification of elements with otherwise overlapping peaks and quantification of composition at lower atomic percentages.

- <sup>1</sup> G. E. Moore, "Cramming More Components Onto Integrated Circuits," Proceedings of the IEEE, vol. 86, pp. 82-85, 1998.

- <sup>2</sup> The International Roadmap For Devices And Systems (2018)

- <sup>3</sup> J. Zhuge, R. Wang, R. Huang, X. Zhang, Y. Wang, IEEE Transactions on Electron Devices, 55 (2008)

- <sup>4</sup> M. I. Current, Ion Implantation Technology 2014 Conference School Chapter 'New Applications for Ion Implantation: Life In A Vertical CMOS World, Materials Modification And Deep Proton Implant' (2014)

- <sup>5</sup> R. Duffy, A. Ricchio, R. Murphy, G. Maxwell, R. Murphy, G. Piaszenski, N. Petkov, A. Hydes, D. O'Connell, C. Lyons, N. Kennedy, B. Sheehan, M. Schmidt, F. Crupi, J. D. Holmes, P. K. Hurley, J. Connolly, C. Hatem, B. Long, Journal of Applied Physics 123 (2018)

- <sup>6</sup> S. C. Jain, W. Schoenmaker, and R. Lindsay, Journal of Applied Physics, 91, 8919 (2002)

- <sup>7</sup> A. Vanderpool, A. Budrevich, and M. Taylor, AIP Conference Proceedings 866, 41 (2006)

- <sup>8</sup> Z. Zhao, J. Y. Tang, G. Zhao, ECS Transactions 34, 769 (2011)

- <sup>9</sup> A. Veloso, A. De Keersgieter, P. Matagne, N. Horiguchi, N. Collaert, Materials Science in Semiconductor Processing, 62 (2017)

- <sup>10</sup> R. Duffy, M. J. H. Van Dal, B. J. Pawlak, M. Kaiser, R. G. R. Weemaes, B. Degroote, E. Kunnen, E. Altamiran, Applied Physics Letters, 90 (2007)

- <sup>11</sup> M. J. H. van Dal, R. Duffy, B. J. Pawlak, N. Collaert, M. Jurczak, R. J. P. Lander, MRS Spring Meeting Proc. 1070 (2008)

- <sup>12</sup> C. Nyamhere, F. Cristiano, F. Olivie, E. Bedel-Pereira, J. Boucher, Z. Essa, D. Bolze, Y. Yamamoto, AIP Conference Proceedings 1496 (2012)

- <sup>13</sup> F. D. Auret, P. J. Janse van Rensburg, M. Hayes, J. M. Nel, S. Coelho, W. E. Meyer, S. Decoster, V. Matias, A.Vantomme, D. Smeets, 15th International Conference on Ion Beam Modification of Materials, 257 (2007)

- <sup>14</sup> N. Akter, S. Roy, Microelectronics and Solid State Electronics, 7 (2019)

- <sup>15</sup> S. M. Ahmad, S. L. Cheow, N. A. Ludin, K.Sopian, S. H. Zaidi, Results in Physics, 7 (2017)

- <sup>16</sup> S.T. The, and D. G. S. Chuah, Solar Energy Materials, 19 (1989)

- <sup>17</sup> F. Lallement, B. Duriee, A. Grouillet, F. Amaud, B. Tavel, F. Wacquant, P. Stalk, M. Woo. Y. Erokhin. J. Scheuer, L. Gadet, J. Weeman, D. Distaso, D. Lenoble, Symposium on VLS1 Technology Digest of Technical Papers (2004)

- <sup>18</sup> L. Godet, G. D. Papasouliotis, A. Kontos, T. Miller, V. Singh, 9th International Workshop on Junction Technology (2009)

- <sup>19</sup> M. Takase, B. Mizuno, IEEE International Symposium on Semiconductor Manufacturing (1997)

- <sup>20</sup> D. Raj, J. S. Lee, H. Maynard, K. Lacey, 20<sup>th</sup> International Conference on Ion Implantation Technology (IIT) (2014)

- <sup>21</sup> J. C. Ho, R. Yerushalmi, G. Smith, P. Majhi, J. Bennett, J. Halim, V. N. Faifer, A. Javey, Nano Lett. (2009)

- <sup>22</sup> S. Chen, J. Hebb, A. Jain, S. Shetty, Y. Wang, 15th IEEE Conference on Adv. Thermal Processing of Semi. (2007)

- <sup>23</sup> Y. Wang, S. Chen, M. Shen, X. Wang, S. Zhou, J. Hebb, D. Owen, 8th IWJT Symposium (2008)

- <sup>24</sup> R. Duffy, W. Skorupa, H. Schmidt, "Subsecond Annealing of Advanced Materials" Chapter 3 (2014)

- <sup>25</sup> See https://www.ossila.com/pages/sheet-resistance-theory

- <sup>26</sup> See https://www.probion.fr/en/tutorials/ecvp/ecvprofiling.html

- <sup>27</sup> See http://www.cityu.edu.hk/phy/appkchu/AP5301/AP5301\_lecture8\_SIMS.pdf

- <sup>28</sup> A. Benninghoven, J. Giber, J. Laszlo, M. Riedel, H.W. Werner, "Secondary Ion Mass Spectrometry SIMS III" 1st Edition (1982)

- <sup>29</sup> See https://simple.wikipedia.org/wiki/Atomic\_force\_microscope

- <sup>30</sup> B.J.Inkson, Materials Characterization Using Nondestructive Evaluation Methods (2016)

- <sup>31</sup> J. I. Goldstein, D. E. Newbury. J. R. Michael, N. W. M. Ritchie, J. H. J. Scott, D. C. Joy, "Scanning Electron Microscopy and X-Ray Microanalysis" 4th Edition (2018)

- <sup>32</sup> D. B. Williams, and C. B. Carter, "Transmission Electron Microscopy" 2nd Edition (2009)

- <sup>33</sup> L. Reimer, and H. Kohl "Transmission Electron Microscopy Physics of Image Formation" 5th Edition (2008)

# Chapter 2: TERTIARYBUTY-LARSINE DAMAGE-FREE THIN-FILM DOPING AND CONFORMAL SURFACE COVERAGE OF SUBSTRATE-RELEASED HORIZONTAL SI NANOWIRES

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

#### 2.1 BACKGROUND AND MOTIVATION

Conformal damage-free doping is the holy grail for 3D semiconductor device structures, such as those used in multi-gate and nanowire-based field effect transistors (FETs). The shape, dimension, pitch, and spacing of parallel conduction paths introduce increased complexity in a number of ways, but particularly in the area of intentional impurity introduction for doping. To this end, gas-phase doping using tertiarybutylarsine (TBA) was employed to dope silicon-on-insulator (SOI) thin films based circular transfer length measurement (CTLM) devices. Damage-free doping processes are desirable as crystal defects or surface roughness can, not only, negatively impact individual transistor device performance, but can also introduce an uncontrolled variability among devices. A conformal process implies access to all surfaces equally in order to, in this case, uniformly and reliably modify the material. Uniformity is necessary as it reduces local resistance variation which again can lead to poor electrical behaviour. As we transition to Gate-All- Around (GAA) device architectures, <sup>34-36</sup> where all sides of the semiconductor are accessible in theory, having processes that can demonstrate access to the bottom surface are becoming increasingly sought after.

Gas-phase doping has the potential to be less damaging to the crystal structure than that of beamline implant<sup>37</sup>. As Si devices scale, the effect of beamline induced crystal damage compounds as a greater percentage of the device's area will consist of damaged crystal<sup>38</sup>. Beamline induced surface damage will become a more prominent issue with increasing surface to volume ratios of Si devices. Sputtering of the Si surface by the ion beam is likely to become more of a limiting factor once device pitch scaling limits the acceptable implantation angles<sup>39</sup>. Limitation of the beamline angles will lead to shadowing of the Si devices, and therefore asymmetrical dopant levels. With the projected advent of GAA devices, line-of-sight implantation methodologies will be unsuitable for the doping of 3D, stacked devices.

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

Gas-phase doping has a greater potential than liquid phase processes to dope the increasingly complex 3D geometries of Si devices as liquid coverage can be limited by wetting. For GAA and 3D Si nanowires, more study is necessary to see how wetting of the complex surface structure would affect dopant concentration and patterning. Surface tension effects present in liquid-based processes also have the potential to damage these fragile devices<sup>40</sup>.

The science of dopant diffusion and activation is multi-variable, <sup>41-51</sup> especially in the case of arsenic in silicon <sup>52-56</sup>. When dealing with 3D structures the impact of surface effects becomes crucial in determining the active dopant levels. These surface effects lead to problems for dopant incorporation/activation or as gettering points where dopants pile up <sup>57-62</sup>. Another problem with the greater exposure to the perimeter of the 3D devices is when the doping process etches the available surface severely damaging or destroying these devices.

Gas-phase doping of silicon has been reported by several groups using various sources<sup>63-73</sup>, and our recent work on gas-phase doping of silicon was performed using arsine (AsH<sub>3</sub>) gas to dope Si nanowires<sup>74</sup>, where suitability for doping was shown. However severe attack of Si nanowires was seen for flowrates of 50 sccm and 250 sccm, while flowrates of 10 sccm and 20 sccm showed moderate etching. It is believed that this Si attack was in part due to the etching caused by atomic hydrogen released in the cracking of arsine. Cracking of TBA is expected to release less free hydrogen<sup>75</sup>. In this work we consider TBA as an alternative doping source to AsH<sub>3</sub>, for damage-free conformal doping of thin Si films and 3D device structures. Finally, Ransom et al. used TBA in a helium carrier gas to gas-phase dope Si substrates with As<sup>76</sup> and they showed some very promising doping profiles, however electrical device evaluation was not conducted and the processes were not applied to thin-films or 3D structures such as nanowires, which are our primary aims here.

#### 2.2 EXPERIMENTAL

This section contains information about the fabrication of first the nanowire and then the CTLM devices.

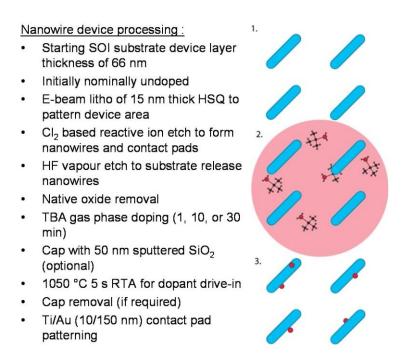

The nanowire devices consist of multi-finger nanowires. This creates a two-pad test structure where current/voltage characteristics are measured to characterise resistance. Different mask layout designs can be used to vary nanowire width (W), length (L), and spacing (S). The metal contact pads consist of a 10 nm Ti adhesion layer with a thicker 150 nm Au layer on top. For all nanowire devices in this project, nominally undoped (100) SOI substrates were used, with a Si thickness of 66 nm and a buried SiO<sub>2</sub> thickness of 145 nm. The unpatterned witness pieces used for carrier profiling were standard (100) lowly doped p-type Si wafers. For nanowire processing, the SOI substrates were patterned using the Raith VOYAGER electron beam lithography (EBL) system with a beam energy of 50 keV, and the high-resolution EBL resists hydrogen silsesquioxane (HSQ, XR1541, 2%) from Dow Corning. Sample etching took place in an Oxford Instruments System 100 ICP etcher operating in Reactive Ion Etch (RIE) mode. The etch chemistry was a Cl<sub>2</sub>/N<sub>2</sub> gas mixture at flows of 20 and 40 sccm, respectively, with a chamber pressure of 10 mTorr and an RF power of 80W yielding a DC bias of 220 V. These nanowire devices are released from the substrate by means of a HF vapour etch.

CTLM devices were fabricated using a bi-layer lift off technique. Nominally undoped (100) SOI substrates were used, with Si thicknesses ranging from 4.5 nm - 66 nm and a buried SiO<sub>2</sub> thickness of 145 nm. First samples were primed for resist by spin coating of HMDS for 1 min at 3000 rpm. This priming modifies the surface to become hydrophobic and aids the resist adhesion. After this step LOR-3A lift of resist was spun on the samples at 3000 rpm for 50 seconds. The LOR-3A then needed to be baked at 170°C for 3 minutes to drive off the solvent and harden the resist. S1805 imaging resist was then spun on at 3000 rpm and baked at 115°C for 2 minutes

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

to drive off the solvent and harden the resist.

Samples were then exposed in a Karl Suss MA6 mask aligner for 4 seconds. Samples were then developed in MF-319 for 1 minute 15 seconds. Each sample was examined under an optical microscope post development. After development 10:100 Ti:Au was deposited coating the sample. Lift off was then performed by immersion in "Microposit 1165" resist remover for 2 hours. On all samples, prior to application of the doping process, samples were degreased, and native oxide was removed.

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

Figure 1: Process flow for nanowire formation, graphic indicates gas phase doping mechanism where arsenic containing gas is passed over nanowire devices and is cracked depositing a free arsenic layer on the surface of the devices later incorporated by rapid thermal annealing.

Gas-phase doping of all samples was carried out using a metalorganic vapour phase epitaxy (MOVPE) system. The reactor pressure was set to 700 Torr with purified hydrogen carrier gas at a flow rate of 16 standard litres per minute (SLM). Liquid tertiarybutylarsine (TBA) was used as the dopant source. Samples were heated in the reactor under hydrogen carrier gas, from 20°C to 850°C, over 15 minutes. TBA was then switched into the reactor with a controlled flow rate of  $4.56\times10^{-2}$  moles/minute and the sample were held under these conditions for 1, 10, or 30 minutes before heating was switched off. TBA was switched out of the reactor and the sample could cool to 200°C under hydrogen at a flow rate of 2 SLM. The gas was then switched to nitrogen and the sample could cool to room temperature before unloading from the reactor.

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

Two separate process runs were conducted. In run 1, two bulk silicon witness pieces were processed for each of the 1, 10, and 30-minute exposure times. For each exposure time one sample had a sputtered SiO<sub>2</sub> capping layer prior to RTA to prevent dopant volatilisation and one did not. All samples then received a 1050°C 5 s RTA in N<sub>2</sub>. This process run was conducted to understand the effect on dopant incorporation and sample damage that different exposures and sample capping and cap removal would have. This information was then used to decide which process would be used for run 2. For run 2 CTLM and nanowire devices and a bulk silicon witness piece, for ECV, were exposed to 1 minute of TBA with no capping layer.

Electrochemical Capacitance Voltage (ECV) profiling was performed, on the bulk Si witness pieces, to determine the electrically active carrier concentration. Before ECV profiling the capping layer, when present, was removed with a 25:1 BOE solution applied for 2 minutes 30 seconds. Ammonium bifluoride was used as the electrolyte/etchant. XTEM and EDX analysis were carried out using the FEI Titan Themis (HRTEM) operated at 300 kV in HAADF-STEM imaging mode. Cross-section samples were prepared by focused ion beam etching using a FEI's Dual Beam Helios Nanolab system. Scanning electron microscopy (SEM) was done using a Zeiss Supra 40. Electrical measurements were performed using an Agilent B1500 parameter analyser, in a Cascade manual probe system under ambient conditions.

# 2.3 RESULTS AND DISCUSSION

#### 2.3.1 Dopant chemical and carrier profiling on planar samples

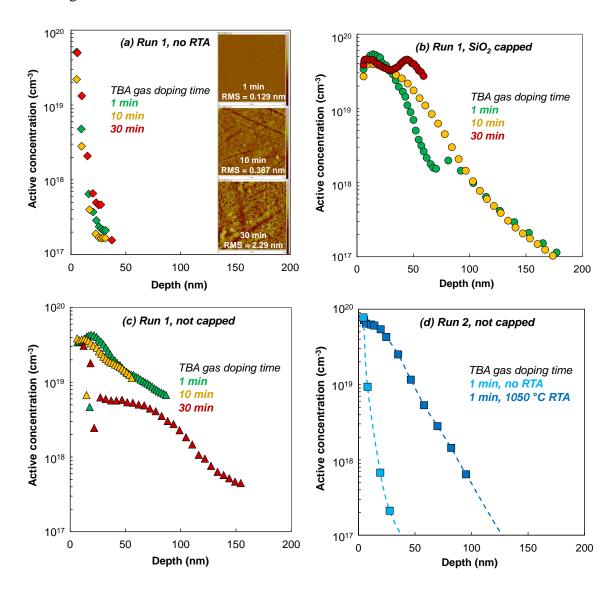

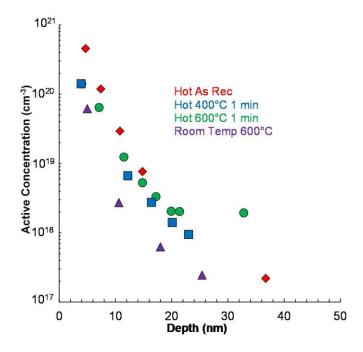

Figure 2 shows active carrier concentrations extracted after the process was applied to bulk substrates. In Figure 2(a) the process temperature of 850°C is sufficient to drive in and activate a certain amount of the dose. Comparing process exposure times in Figure 2(b) and Figure 2(c) exposure time had a negligible effect on active dopant concentration, suggesting the process is self-limiting.

Similar dopant levels are seen comparing Figure 2(b) and Figure 2(c) showing that the SiO<sub>2</sub> cap is not necessary to prevent volatilisation of the dopant molecule from the surface of the substrate and was therefore omitted on run 2. The abnormal near-surface points seen in Figure 2(c) are believed to have been caused by the ECV first profiling an arsenic rich oxide layer and then the silicon itself. This is reinforced by the observation of an arsenic rich oxide layer in STEM analysis of the nanowire devices seen in Figure 5. This effect is not seen in either the SiO<sub>2</sub> capped or run 2 samples, Figure 2(b) and Figure 2(d), as the removal process for the SiO<sub>2</sub> cap likely removed the oxide and run 2 bulk samples were therefore etched for 15 s in 25:1 BOE to prevent this ECV artefact. Comparison of the pre annealed and post annealed portions of the graph shows a different profile shape between pre-annealed and post annealed active dopant concentration. Post-annealed Si showed a Gaussian profile distribution, while pre-annealed Si showed a more exponential profile. This may be useful for Si devices where a specific dopant profile is necessary. The active concentration seen here could be redistributed by using a faster ramp rate RTA tool. Redistributing the dopant can give a higher surface concentration by limiting dopant diffusion. The RTA used in this work has a maximum ramp rate of 10°C/s giving dopant enough time to diffuse into the sample limiting the surface concentration and increasing the junction depth. With optimized annealing, diffusion could be controlled

such that the dopant is more concentrated at the surface optimizing the profile for smaller device geometries. Subsequent runs of the process are planned to use such optimised annealing.

The unusual active profile shapes, especially seen for the longer process times are possibly linked to extreme surface roughness, which can affect the carrier profiling by ECV. This was studied in more detail by AFM.

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

Figure 2: Representative ECV carrier profiles showing active carrier concentration. These profiles are extracted from the Si witness pieces for the process on the CTLM devices. (a) Electrically active carrier profiles extracted from process run 1 ECV conducted directly after MOVPE exposure with no post anneal. Inset: Roughness (RMS) of bulk Si witness pieces measured using AFM, RMS values are 0.129, 0.387, 2.29 nm for the 1, 10, 30 minute processes respectively. This analysis is showing clear etching of the silicon for the 10 minute and 30 minute processes. However, for the lower exposure of 1 minute the witness piece is showing no observable etching, and thus was chosen for the run 2 set of experiments. (b) Profiles extracted post 1050°C 5 s anneal on samples with SiO2 cap. (c) Profiles extracted post 1050°C 5 s anneal for process run 2 (applied to CTLM and nanowire devices).

Figure 2(a) shows AFM conducted on the Si witness pieces from run 1 in order to access the damage caused by the doping process. Tapping mode AFM was used, to limit probe induced damage to the surface. An RMS value of 0.129 nm for the 1 minute exposure time, shows limited to

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

no etching has occurred on the surface for a low process time. In comparison, the 10 minute and 30 minute exposure times gave RMS values of 0.387 nm and 2.29 nm respectively. This shows the surface roughness increases with increased exposure to TBA gas. Since the dopant concentration has been shown to be self-limiting, keeping the exposure time short is advised to limit surface etching. It is worth noting that the AFM measurements are possibly of the conformal oxide layer on the Si surface. This means our RMS values from the AFM may not be a true indicator of the Si surface roughness. However, it is assumed that the trend in the oxide layer roughness will reflect the underlying trend of the Si surface roughness. However, we can see that both the 10 and 30 minute exposures show obvious etching of the substrate. Therefore, to reduce etching in run 2, which was applied to the CTLM and nanowire devices, a 1 minute exposure was used.

In relation to the electrical devices in this study, we have performed AFM analysis (multiple sites per sample) of the surfaces of all Si thicknesses used in this study. The surface roughness is summarised in the table below. The Si films are continuous in all cases. Overall, the roughness doesn't appear to vary significantly as we scale the Si thickness on the SOI samples, although one could argue the ratio of roughness to overall thickness is increasing. This roughness will affect the carrier scattering at the surfaces and can affect carrier mobility.

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

| SOI Thickness (nm) | Roughness RMS (nm) |

|--------------------|--------------------|

| 66                 | 0.259              |

| 30                 | 0.171              |

| 20                 | 0.221              |

| 10.5               | 0.165              |

| 4.5                | 0.207              |

Figure 3: AFM roughness RMS measurements conducted on SOI thin films used for electrical characterisation.

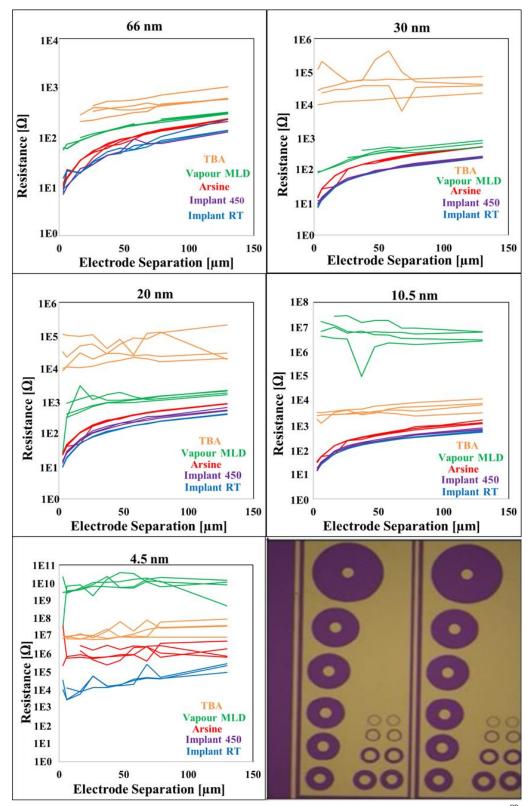

#### 2.3.2 Electrical characterisation of CTLM device structures

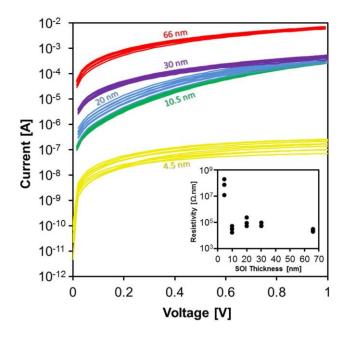

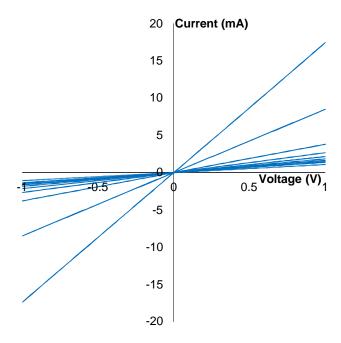

The electrical properties of the SOI samples, with Si film thickness ranging 4.5 to 66 nm, were measured using the circular transfer length method. Sets of concentric metal circular electrode pairs were deposited on the Si surface using optical lithography, metal evaporation and lift-off. The electrode metal was 100 nm thick Au on a 10 nm thick Ti adhesion layer, with electrode pair separations between 2  $\mu$ m and 130  $\mu$ m as described in previous work<sup>77</sup>.

The current-voltage characteristics were measured between -1 V and +1 V and the material resistivity for each film thickness was determined by analysing the resistance with respect to electrode separation. The raw I-V data are shown in Figure 3 resistivity for each Si film thickness is presented in the inset. The material resistivity is observed to increase with decreasing film thickness, with a significant increase in resistivity at 4.5 nm. The pronounced increase in resistivity may be as a result of an undesirable doping profile in the first few nanometres of depth, or indeed low overall doping levels, which may have a more pronounced effect at thinner Si film thicknesses. Another relevant effect on the increase in resistivity is the expected sharp drop in the density of states for electron and hole conduction due to quantum confinement effects in these thin Si structures. The density of states (DoS) per unit volume for a 3D semiconductor,

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

a sub-10nm thin-film quantum well, and a sub-10nm quantum wire will not be the same. In effect the physical confinement produces discreteness of allowed electron energies leading to quantum effects. Moreover, the DoS could potentially drop dramatically in going from 3D to 1D, depending on the dimensions. The lower the DoS then the lower the current in the device, and hence there will be an increase in resistivity <sup>78-80</sup>.

Figure 4: Representative current-voltage data from the CTLM measurements for each Si film thickness. Note these data are not normalized to thickness. Inset: Extracted resistivity values vs. Si thickness.

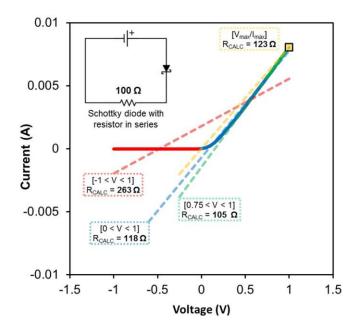

It should be noted that in some cases, the I-V characteristics were non-linear due to the possible presence of a Schottky barrier at the metal-Si interface. In such cases, caution is needed when attributing a single representative resistance value, from which resistivity can then be extracted. The electrode/interface/silicon can be thought of as being similar to a Schottky diode in series with a resistor, the resistance of which varies with CTLM electrode separation and is characteristic of the material under test. As such, representative resistance was determined by performing a linear regression on the current data over the voltage range of +0.75 V to +1 V

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

where this diode is "more switched on" and the I-V characteristics are less affected by the effects of the Schottky barrier, and more by the series resistance.

While not entirely perfect, this approach gives a more accurate determination of the series material resistance than performing a linear fit over the entire voltage range. This conclusion is based on trying to calculate the resistance of the resistor from the I-V data from the simulated diode-resistor circuit. It can be seen from Figure 5 that calculating the resistance by using data from different voltage ranges, gives different results. The full range [-1 < V < +1] gives the highest error (163%) while the lowest error (5%) was achieved using the range of [0.75 < V < 1]. We do not claim that this method increases the accuracy of reporting the material resistance, rather it decreases the inaccuracy that would be introduced by incorporating characteristics that are dominated by the effects of the metal-Si interface.

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

Figure 5: Simulated I-V response from the Schottky diode with series resistance circuit (inset). The trend lines and annotations display the resistance value extracted using linear regression over different voltage ranges. The actual value of the resistor used in the simulation was  $100~\Omega$ .

#### 2.3.3 Applicability analysis for Gate-All-Around (GAA) nanowire devices

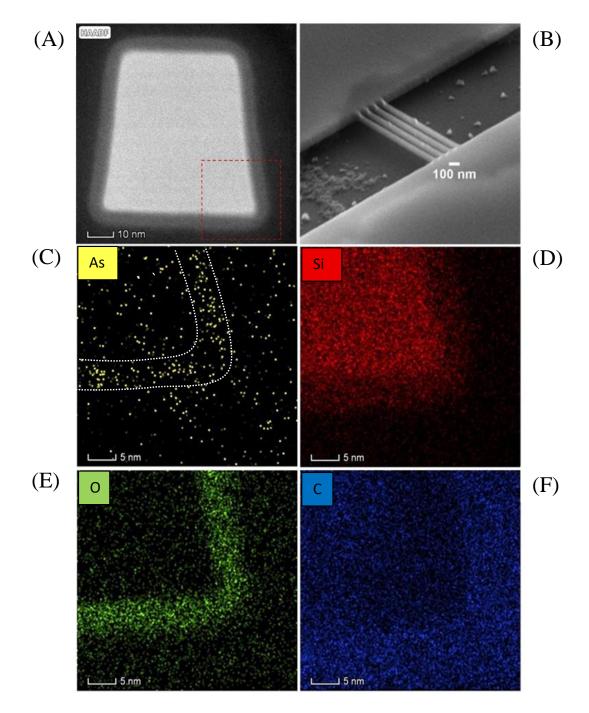

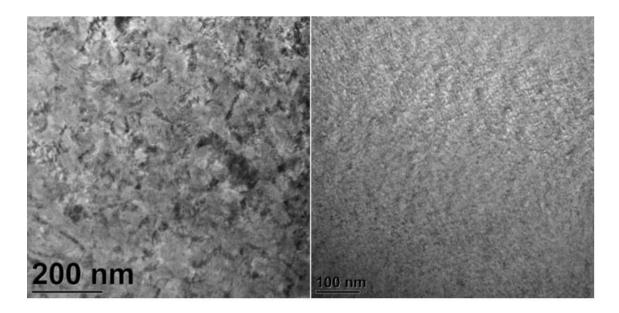

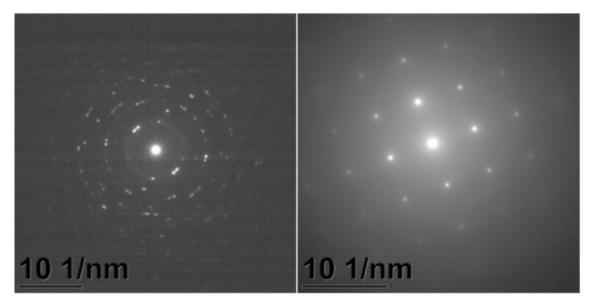

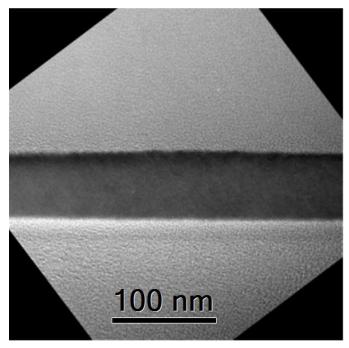

Figure 6 shows a SEM image of "4-finger" nanowires released from the substrate that also received the 1 minute TBA processing. No visible etching is noted. Figure 6 also shows a representative XSTEM of one of the nanowires, again showing no evidence of damage in the crystal structure internally in the wire or externally on the surfaces.

Line edge roughness (as a function of the lithography, etch, and subsequent processing) will be an important factor for any future electrical characterisation of theses nanowires due to its effect on carrier mobility.

In future work we will be characterising the nanowire electrical behaviour and line edge roughness measurements will be included with that electrical data. An approximately 4 nm arsenic containing oxide layer, a dark grey conformal layer surrounding the light grey Si nanowire, is seen in the STEM image. EDX analysis shows the presence of arsenic in the layer. From the EDX analysis it seems like this layer is an arsenic-rich silicon oxide with little carbon

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

being incorporated. This layer was also seen in the XTEM analysis of the CTLM devices (not shown). This layer may explain the non-linear behaviour seen in the electrical characterisation, as any current would have to travel though this likely semi-insulating layer.

The Si was cleaned with 2% HF for 15 s prior to the MOVPE to remove all SiO<sub>2</sub> from the device surface. The processing in the MOVPE reactor used highly pure gasses with no presence of O, the post-anneal was completed under N<sub>2</sub> not allowing the growth of oxides, and the transfer of the samples from the MOVPE to the annealing chamber was quick enough to not allow for the significant growth of an oxide conformal layer. Native oxide growth will occur in contact with ambient, and it is known that oxide growth is strongly enhanced by high carrier concentrations. It is more likely that the conformal oxide layer formed after the RTA. Future work will be completed to confirm when the conformal layer forms on the Si, as if the oxide forms prior to the final anneal, it may act as a limiting factor to the maximum active dopant concentration.

Chapter 2: Tertiarybutylarsine Damage-Free Thin-Film Doping And Conformal Surface Coverage Of Substrate-Released Horizontal Si Nanowires

Figure 6: (A) XSTEM image showing nanowire with conformal doping layer with red enclosed area indicated for EDX scan area, (B) Representative "4-finger" released nanowire device from which one nanowire was imaged, (C)-(F) EDX analysis showing presence of arsenic containing oxide layer formed (enclosed by white curves in image (C)) with minimal carbon incorporation

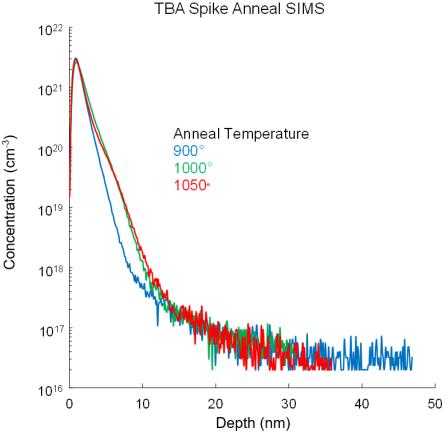

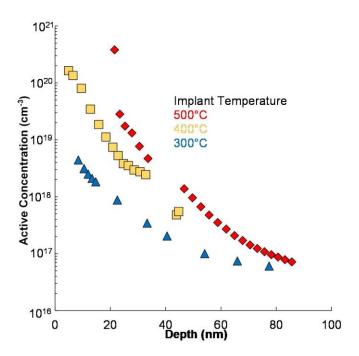

### 2.3.4 Spike anneal of TBA doped silicon

Figure 7: Spike Anneal performed on planer silicon substrates doped using optimised TBA process.  $1000^{\circ}\text{C}$  and  $1050^{\circ}\text{C}$  show similar greater levels on in diffusion compared with the  $900^{\circ}\text{C}$  anneal. Overall this process limits the in diffusion when compared to conventional RTA as in Figure 2.

Due to the use of an RTA at Tyndall with relatively low ramp up and ramp down rates, the amount of As diffusion was ~100 nm in the previous experiment (see Figure 2). This might be considered too much for USJ applications. A preliminary exploration into the control of diffusion was then carried out, using the TBA process as before but with a different RTA tool, this one with >100°C/s ramp up capability. Shown in Figure 7 are the data for anneals at 900, 1000, and 1050°C, 0 s hold time RTA. It can be seen the diffusion is greatly reduced created USJs of < 20 nm. This result shows promise, and in future work should be explored in greater detail in order to characterise fully and optimise the entire process flow.

# 2.4 CONCLUSIONS

In this work we investigated TBA as an alternative doping source for damage-free conformal doping of thin Si films and 3D device structures. Using an optimised process high levels of active As doping concentrations (close to  $10^{20}$  cm<sup>-3</sup>) were achieved in functional 3D devices, and could be further optimised by applying a spike-RTA demonstrated on planer silicon. For the optimised doping process, no evidence was observed of damage to the crystal structure, either internally in the wire or externally on the surfaces, which makes this technique compatible with GAA device architectures. An approximately 4 nm arsenic containing oxide layer was observed on the Si test structures, conformal to all 4 surfaces on substrate-released nanowires, and it is thought to be linked to exposure to the ambient.

#### **ACKNOWLEDGEMENTS**

This work is supported by Enterprise Ireland through the project IP-2017-0605, by the European Union's Horizon 2020 Research and Innovation programme via the ASCENT Access Network (grant agreement no. 654384), and through the European Regional Development Fund (ERDF) under Ireland's European Structural and Investment Funds Programmes 2014-2020. The authors would like to acknowledge the TEMUL group in the University of Limerick for the acquisition and assistance interrupting of the HAADF-STEM and EDX analysis. The authors would like to acknowledge Fearghal Donnellan for the graphic used to represent the process in Figure 1.

- <sup>34</sup> N. Singh, A. Agarwal, L. K. Bera, T. Y. Liow, R. Yang, S. C. Rustagi, C. H. Tung, R. Kumar, G. Q. Lo, N. Balasubramanian, and D.-L. Kwong, IEEE Electron Device Lett. 27, 383 (2006).

- <sup>35</sup> R. Gandhi, Z. Chen, N. Singh, K. Banerjee, and S. Lee, IEEE Electron Device Lett. 32, 1504 (2011).

- <sup>36</sup> K. J. Kuhn, IEEE Trans. Electron Devices 59, 1813 (2012).

- <sup>37</sup> E. Y.-J. Kong, P. Guo, X. Gong, B. Liu, and Y.-Chia Yeo IEEE Trans. Electron Devices 61, 4 (2014).

- M. J. H. Van Dal, N. Collaert, G. Doornbos, G. Vellianitis, G. Curatola, B. J. Pawlak, R. Duffy, C. Jonville, B. Degroote, E. Altamirano, E. Kunnen, M. Demand, S. Beckx, T. Vandeweyer, C. Delvaux, F. Leys, A. Hikavyy, R. Rooyackers, M. Kaiser, R. G. R. Weemaes, S. Biesemans, M. Jurczak, K. Anil, L. Witters, R. J. P. Lander, 2007 Digest of Technical Papers Symposium on VLSI Technology, 110 (2007).

- Y. Sasaki, A. D. Keersgieter, C. S. Aik, T. Chiarella, G. Hellings, M. Togo, G. Zschatzsch, A. Thean, and N. Horiguchi, Ext. Abs. the 13th IWJT, S2-2 (2013).

- Niels Tas, Tonny Sonnenberg, Henri Jansen, Rob Legtenberg, and Miko Elwenspoek J. Micromech. Microeng. 6, 385–397 (1996).

- <sup>41</sup> R. Chiarcos, V. Gianotti, M. Cossi, A. Zoccante, D. Antonioli, K. Sparnacci, M. Laus, F. E. Caligiore, and M. Perego, ACS Appl. Electron. Mater., 1, 1807 (2019).

- P. Tejedora, M. Drescherb, L. Vázqueza, L. Wilde, Applied Surface Science 496, 143721 (2019).

- <sup>43</sup> F. A. Trumbore, Bell Syst. Tech. J. 39, 205 (1960).

- P. Pichler, *Intrinsic point defects, impurities, and their diffusion in silicon*, Springer, Berlin (2004).

- M. Ferri, S. Solmi, D. Giubertoni, M. Bersani, J. J. Hamilton, M. Kah, K. Kirkby, E. J. H. Collart, and N. E. B. Cowern, J. Appl. Phys. 102, 103707 (2007).

- D. Hiller, J. López-Vidrier, S. Gutsch, M. Zacharias, K. Nomoto, D. König, Sci. Rep. 7, 863 (2017).

- D. König, S. Gutsch, H. Gnaser, M. Wahl, M. Kopnarski, J. Göttlicher, R. Steininger, M. Zacharias, D. Hiller, Sci. Rep. 5, 9702 (2015).

- <sup>48</sup> C. Song, J. Xu, G. Chen, H. Sun, Y. Liu, W. Li, L. Xu, Z. Ma, K. Chen, Applied Surface Science 257, 1337 (2010)

- M. T. Björk, H. Schmid, J. Knoch, H. Riel and W. Riess, Nature Nanotech. 4, 103 (2009).

- R. Milazzo, G. Impellizzeri, D. Piccinotti, D. De Salvador, A. Portavoce, A. La Magna, G. Fortunato, D. Mangelinck, V. Privitera, A. Carnera, E. Napolitani, Applied Physics

#### Letters 110, 011905 (2017).

- M. Shayesteh, D. O'Connell, F. Gity, P. Murphy-Armando, R. Yu, K. Huet, I. Toque-Tresonne, F. Cristiano, S. Boninelli, H. H. Henrichsen, P. F. Nielsen, D. H. Petersen, R. Duffy, IEEE Transactions on Electron Devices 61, 6945879, 4047 (2014).

- <sup>52</sup> A. Nylandsted Larsen, K. Kyllesbech Larsen, and P. E. Andersen, J. Appl. Phys. 73, 691 (1993).

- <sup>53</sup> M. J. P. Hopstaken, Y. Tamminga, M. A. Verheijen, R. Duffy, V. C. Venezia, A. Heringa, Applied Surface Science, 231-232, 688 (2004).

- <sup>54</sup> F. Corsetti and A. A. Mostofi, Journal of Physics Condensed Matter 26, 055002 (2014).

- N. Kong, T. A. Kirichenko, G. S. Hwang, S. K. Banerjee, Physical Review B Condensed Matter and Materials Physics 80, 205328 (2009).

- <sup>56</sup> M. Ferri, S. Solmi, A. Parisini, M. Bersani, D. Giubertoni, M. Barozzi, Journal of Applied Physics 99, 113508 (2006).

- See irds.ieee.org for semiconductor technology trends and projections.

- <sup>58</sup> M. Diarra, Y. M. Niquet, C. Delerue, and G. Allan, Phys. Rev. B 75 (4), 045301 (2007).

- <sup>59</sup> M. T. Bjork, H. Schmid, J. Knoch, H. Riel, and W. Riess, Nat. Nanotechnol. 4 (2), 103 (2009).

- <sup>60</sup> T. L. Chan, M. L. Tiago, E. Kaxiras, and J. R. Chelikowsky, Nano Lett. 8 (2), 596 (2008).

- <sup>61</sup> M. V. Fernández-Serra, C. Adessi, and X. Blase, Phys. Rev. Lett. 96 (16), 166805 (2006).

- <sup>62</sup> L. Lin, Z. Li, J. Feng, and Z. Zhang, Phys. Chem. Chem. Phys. 15 (16), 6063 (2013).

- <sup>63</sup> Y.-H. Song, K. –T. Park, H. Kurino and M. Koyanagi, Jpn. J. Appl. Phys. 39, 26 (2000).

- B. Kalkofen, M. Lisker, E. P. Burte, Materials Science and Engineering B 114–115, 362 (2004).

- <sup>65</sup> Y. Kiyota, T. Nakamura, K. Muraki, T. Inada, J. Electrochem. Soc, 141, 2241 (1994).

- <sup>66</sup> Y. Kiyota, T. Inada, J. Vac. Sci. Technol. A 19, 2441 (2001).

- <sup>67</sup> P. Taheri, H. M. Fahad, M. Tosun, M. Hettick, D. Kiriya, K. Chen, and A. Javey, ACS Appl. Mater. Interfaces 9, 20648 (2017).

- <sup>68</sup> M. J. J. Theunissen, C. E. Timmering, J.G. van Berkum, and Y. J. Mergler, Jpn. J. phys. 38, 5805 (1999).

- <sup>69</sup> J. Nishizawa, K. Aoki and T. Akamine, Appl. Phys. Lett. 56, 1334, (1990).

- Y. A. Astrov, L. M. Portsel, A. N. Lodygin and V. B. Shuman, Semicond. Sci. Technol. 26, 055021 (2011).

- Y. A. Astrov, V. B. Shuman , L. M. Portsel, and A. N. Lodygin, Semiconductors, 48, 413 (2014).

- <sup>72</sup> M. Takenaka, K. Morii, M. Sugiyama, Y. Nakano, and S. Takagi, Optics Express 20, 8718 (2012).

- R. Duffy, M. Shayesteh, K. Thomas, E. Pelucchi, R. Yu, A. Gangnaik, Y. M. Georgiev, P. Carolan, N. Petkov, B. Long and J. D. Holmes, J. Mater. Chem. C, 2, 9248 (2014).

- <sup>74</sup> R. Duffy, K. Thomas, E. Galluccio, G. Mirabelli, M. Sultan, N. Kennedy, N. Petkov, G. Maxwell, A. Hydes, D. O'Connell, C. Lyons, Brendan Sheehan, Michael Schmidt, J. D. Holmes, P. K. Hurley, E. Pelucchi, J. Connolly, C. Hatem, and B. Long, Journal of Applied Physics 124, 045703 (2018).

- <sup>75</sup> G.B. Stringfellow, Organometallic Vapor-Phase Epitaxy, 2 Edt. P 170-195 (1999).

- <sup>76</sup> C. M. Ransom, T. N. Jackson, J. F. DeGelormo, C. Zeller, D. E. Kotecki, C. Graimann, D. K. Sadana, and J. Benedic, J. Electrochem. Soc.,141, 1378 (1994)

- J. MacHale, F. Meaney, N. Kennedy, L. Eaton, G. Mirabelli, M. White, K. Thomas, E. Pelucchi, D. H. Petersen, R. Lin, N. Petkov, J. Connolly, C. Hatem, F. Gity, L. Ansari,

- B. Long, and R. Duffy, Journal of Applied Physics 125, 225709 (2019)

- <sup>78</sup> S. Kyogoku, J.-I. Iwata, A. Oshiyama, Physical Review B Condensed Matter and Materials Physics 87, 165418 (2013).

- <sup>79</sup> M. Kobayashia and T. Hiramoto, Journal of Applied Physics 103, 053709 (2008).

- <sup>80</sup> K. S. Yi, K. Trivedi, H. C. Floresca, H. Yuk, W. Hu, M. J. Kim, Nano Letters 11, 5465 (2011).

- F. Meirer, E. Demenev, D. Giubertoni, S. Gennaro, L. Vanzetti, G. Pepponi, and M. Bersani, AIP Conference Proceedings 1496, 183 (2012)

# Chapter 3: ONE STEP LOW LOW-TEMPERATURE DAMAGE FREE DOPANT ACTIVATION OF THIN THINFILM SILICON DEVICES

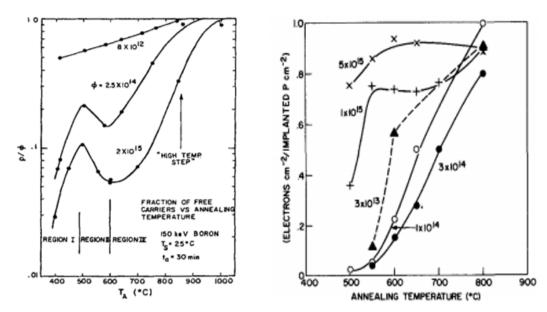

#### 3.1 INTRODUCTION

Ultra-shallow, high activation implantation is a key step to produce modern semiconductor devices. Ion implant is still the most widely used method for introducing dopant atoms due to it being well understood, very controlled, and has a high level of adjustment to control dopant concentration and depth.

A disadvantage of this method is the damage it causes to the silicon lattice along with the need for a high temperature anneal not compatible with some modern semiconductor materials. The process is also complex in comparison with some other doping technologies such as SOD and MLD.

In this chapter a method of low temperature activation of dopants by dynamic annealing during implant is discussed. This allows us to activate high levels of dopant at a significantly reduced temperature and without the need for the additional processing necessity of a high temperature anneal.