| Title                          | High aspect ratio iridescent three-dimensional metal–insulator–<br>metal capacitors using atomic layer deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                        | Burke, Micheal;Blake, Alan;Djara, Vladimir;O'Connell, Dan;Povey,<br>Ian M.;Cherkaoui, Karim;Monaghan, Scott;Scully, Jim;Murphy,<br>Richard;Hurley, Paul K.;Pemble, Martyn E.;Quinn, Aidan J.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Publication date               | 2014-07-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Original Citation              | Burke, M., Blake, A., Djara, V., O'Connell, D., Povey, I. M.,<br>Cherkaoui, K., Monaghan, S., Scully, J., Murphy, R., Hurley,<br>P. K., Pemble, M. E. and Quinn, A. J. (2014) 'High aspect ratio<br>iridescent three-dimensional metalinsulatormetal capacitors<br>using atomic layer deposition', Journal of Vacuum Science and<br>Technology A, 33(1), 01A103 (5pp). doi: 10.1116/1.4891319                                                                                                                                                                                                                                                                |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Link to publisher's<br>version | 10.1116/1.4891319                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Rights                         | © 2014, American Vacuum Society. This article may be<br>downloaded for personal use only. Any other use requires<br>prior permission of the author and AIP Publishing. This article<br>appeared as: Burke, M., Blake, A., Djara, V., O'Connell, D., Povey,<br>I. M., Cherkaoui, K., Monaghan, S., Scully, J., Murphy, R., Hurley,<br>P. K., Pemble, M. E. and Quinn, A. J. (2014) 'High aspect ratio<br>iridescent three-dimensional metalinsulatormetal capacitors<br>using atomic layer deposition', Journal of Vacuum Science and<br>Technology A, 33(1), 01A103 (5pp), doi: 10.1116/1.4891319, and<br>may be found at: https://doi.org/10.1116/1.4891319 |

| Download date                  | 2025-08-03 01:44:43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Item downloaded<br>from        | https://hdl.handle.net/10468/13311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# High aspect ratio iridescent threedimensional metal-insulator-metal capacitors using atomic layer deposition

Cite as: J. Vac. Sci. Technol. A 33, 01A103 (2015); https://doi.org/10.1116/1.4891319 Submitted: 31 March 2014 • Accepted: 15 July 2014 • Published Online: 28 July 2014

Micheal Burke, Alan Blake, Vladimir Djara, et al.

# **ARTICLES YOU MAY BE INTERESTED IN**

Conformality in atomic layer deposition: Current status overview of analysis and modelling Applied Physics Reviews 6, 021302 (2019); https://doi.org/10.1063/1.5060967

Atomic layer deposition of metals: Precursors and film growth Applied Physics Reviews 6, 041309 (2019); https://doi.org/10.1063/1.5087759

Crystallinity of inorganic films grown by atomic layer deposition: Overview and general trends Journal of Applied Physics 113, 021301 (2013); https://doi.org/10.1063/1.4757907

+ end point detection in ion beam etch

elemental imaging - surface mapping

SIMS

#### partial pressure measurement and control of process gases reactive sputter process control vacuum diagnostics vacuum coating process monitoring

J. Vac. Sci. Technol. A 33, 01A103 (2015); https://doi.org/10.1116/1.4891319

catalysis and thermal analysis

fermentation, environmental and ecological studies

molecular beam studies

dissolved species probes

Contact Hiden Analytical for further details:

Info@hideninc.com

www.HidenAnalytical.com

Micheal Burke,<sup>a)</sup> Alan Blake, Vladimir Djara, Dan O'Connell, Ian M. Povey, Karim Cherkaoui, Scott Monaghan, Jim Scully, Richard Murphy, Paul K. Hurley, Martyn E. Pemble, and Aidan J. Quinn<sup>b)</sup> *Tyndall National Institute, University College Cork, Cork, Ireland*

(Received 31 March 2014; accepted 15 July 2014; published 28 July 2014)

The authors report on the structural and electrical properties of TiN/Al<sub>2</sub>O<sub>3</sub>/TiN metal-insulator-metal (MIM) capacitor structures in submicron three-dimensional (3D) trench geometries with an aspect ratio of ~30. A simplified process route was employed where the three layers for the MIM stack were deposited using atomic layer deposition (ALD) in a single run at a process temperature of 250 °C. The TiN top and bottom electrodes were deposited via plasma-enhanced ALD using a tetrakis(dimethylamino)titanium precursor. 3D trench devices yielded capacitance densities of 36 fF/ $\mu$ m<sup>2</sup> and quality factors >65 at low frequency (200 Hz), with low leakage current densities (<3 nA/cm<sup>2</sup> at 1 V). These devices also show strong optical iridescence which, when combined with the covert embedded capacitance, show potential for system in package (SiP) anticounterfeiting applications. © 2014 American Vacuum Society. [http://dx.doi.org/10.1116/1.4891319]

# I. INTRODUCTION

Methods for on-chip fabrication of high surface area three-dimensional 3D electrodes and device architectures at mesoscopic length scales  $(10 \text{ nm}-10 \mu \text{m})$  are of significant interest for a range of applications, including energy storage, radio-frequency communications, memory devices, and anticounterfeiting.<sup>1–14</sup> With the demand for continued electronic device miniaturization, integration of metal-insulator-metal (MIM) capacitor architectures with such high surface area electrodes is of great importance, particularly in boosting overall capacitance while reducing device footprint.<sup>1-11</sup> Moving from two-dimensional (2D) planar device structures to three-dimensional (3D) structures is obviously attractive in terms of the associated increase in capacitance density. However, significant fabrication challenges remain. A key challenge is conformally coating high-aspect ratio structures using conventional physical vapor deposition or chemical vapor deposition techniques at deep submicron critical dimensions.

Atomic layer deposition (ALD), which is based on alternating self-limiting surface reactions, whereby films are fabricated submonolayer at a time by repeating two subsequently executed half-cycle reactions, remains the only thin film technique, which can provide the necessary conformity and thickness control required for coating both metal and dielectric films in high aspect ratio structures. Additional benefits of all-ALD processing for MIM device architectures include the ability to form successive layers without breaking vacuum, thus minimizing the unwanted introduction of atmospheric impurities and contaminants.<sup>3,7,8</sup> However, while there has been a strong focus on achieving large capacitance densities with such architectures, there has been little in the way of assessing the performance of all-ALD 3D capacitors for such applications. For a comprehensive overview of device performance, the quality factor (*Q*-factor) or related equivalent series resistance (ESR) should be characterized alongside capacitance density, leakage current density, and breakdown voltage.<sup>3–6,11</sup> Here we present a detailed study of the structural and electrical properties of TiN/Al<sub>2</sub>O<sub>3</sub>/TiN metal–insulator–metal capacitor structures in 3D trench geometries with high aspect ratio (~30) and narrow trench widths (<500 nm). We discuss the benefits and challenges associated with all-ALD processing of metal–insulator–metal device structures.

CrossMark

# **II. EXPERIMENT**

Sets of both planar and trench capacitors were designed side by side on the same mask set, enabling both device types to be fabricated in the same process flow and characterized under identical conditions. The substrate was n-type Si(100), As surface doping,  $\sim 5 \times 10^{19}$  cm<sup>-3</sup>. For photolithographic patterning of the trench arrays, Fujifilm HiPR6512 photoresist was spun at 5000 rpm for 30 s followed by a 90 s soft-bake at 90 °C. The trench arrays (nominally 1  $\mu$ m line/ space) were defined using a  $SF_6/C_4F_8$  plasma etch followed by resist removal. Prior to MIM processing, the silicon trench features and the unpatterned Si substrate were coated with  $\sim 610 \text{ nm}$  of  $Al_2O_3$  via thermal ALD (Cambridge Nanotech Fiji system) using trimethylaluminum and water precursors. This step was undertaken to increase the aspect ratio by a factor of  $\sim$ 3 to assess the conformity and electrical performance of thin MIM capacitor stacks (<150 nm) in high aspect ratio geometries. Next, a metal/insulator/metal stack of TiN (20 nm)/Al<sub>2</sub>O<sub>3</sub> (10 nm)/TiN (100 nm) was deposited in succession in the same ALD chamber at a constant temperature of 250 °C. Plasma-enhanced ALD (300 W) at 300 mTorr was employed for the TiN layers using a tetrakis (dimethylamino) titanium precursor with 60 SCCM N<sub>2</sub> flow

<sup>&</sup>lt;sup>a)</sup>Electronic mail: micheal.burke@tyndall.ie

<sup>&</sup>lt;sup>b)</sup>Electronic mail: aidan.quinn@tyndall.ie

and 200 SCCM Ar carrier gas. Thermal ALD was used for the  $Al_2O_3$  layer. The thickness of the top TiN layer (100 nm) was chosen in order to seal the top of the trenches and thus obviate the need for a planarization layer for subsequent lithographic patterning.

In order to lithographically pattern the MIM capacitors, the top TiN electrodes [marked *S* in Fig. 1(e)] were etched using a Cl<sub>2</sub> etch process, which is highly selective to the underlying Al<sub>2</sub>O<sub>3</sub>. A via to the bottom planar TiN electrode [marked *D* in Fig. 1(e)] was then opened using a nonselective BCl<sub>3</sub> etch process. Capacitance and quality factor versus voltage measurements (*C*–*V*, *Q*–*V*) were performed using an Agilent E4980A Precision LCR Meter. Current–voltage (*I*–*V*) measurements were performed using a HP4156A Semiconductor Parameter Analyzer. All measurements were performed in a vacuum probe station (~10<sup>-6</sup> mbar, Lakeshore TTPX) at 25 °C. Scanning electron microscopy (SEM) imaging of mechanically cleaved cross sections was performed on a JEOL 7500F cold-cathode field-emission scanning electron microscope with an in-lens detector.

## **III. RESULTS AND DISCUSSION**

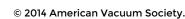

Figures 1(a)-1(c) show cross-sectional X-SEM images for a typical metal-insulator-metal trench capacitor. The 610 nm

FIG. 1. (Color online) (a) Cross section X-SEM images of a trench array capacitor. Higher magnification images showing the  $TiN/Al_2O_3/TiN$  MIM stack: (b) top of trench; (c) bottom of trench. (d) Side-view schematic. (e) Top-view microscope image of a trench capacitor structure showing an etched rectangular via to the planar bottom TiN contact (*D*) and the patterned top TiN electrode (*S*) with top metal probe pads. (f) Photograph of a tilted device chip with arrays of 3D trench capacitors (bright squares) and logos (via capacitors).

layer of Al<sub>2</sub>O<sub>3</sub> deposited by ALD on the lithographically patterned Si trenches significantly increases the aspect ratio from  $\sim 10$  to  $\sim 30$  while also reducing sidewall roughness through cumulative smoothing of the original trench features. Highly conformal step coverage of the 610 nm layer of Al<sub>2</sub>O<sub>3</sub> is also evident at both the top and bottom of the trenches. However, analysis of measured SEM images using ImageJ reveals a significantly smaller average layer thickness for the TiN bottom electrodes at the bottom of each trench  $(15 \pm 2 \text{ nm})$  versus the measured values at the top of the trench  $(20 \pm 1 \text{ nm})$ . While care need to be taken in the accuracy of thickness measurements using this approach (due to the resolution limit of  $\sim$ 1 nm for the SEM), this trend in thickness reduction has been reported and modeled for plasma-enhanced ALD in high aspect ratio structures and attributed to unwanted recombination of plasma radicals at trench sidewalls leading to recombination-limited growth toward the bottom of the trenches.<sup>15,16</sup> By contrast, image analysis reveals that the average thickness of the Al<sub>2</sub>O<sub>3</sub> layer deposited using thermal ALD is only slightly smaller at the bottom of the trenches  $(9 \pm 1 \text{ nm})$  compared to the top of the trenches  $(10 \pm 1 \text{ nm})$ .

Optical micrographs and photographs [Figs. 1(e)-1(g)] reveal that the ALD layers enable retention (and even enhancement) of the iridescence of the micropatterned Si features. The observed intense rainbow pattern, arising from the periodic array of vertical (square footprint) and horizontal (logo footprint) etched trenches show potential for anticounterfeiting applications whereby an overt optical signature could be combined with a covert embedded electrical signature derived from conformal coatings of metal-insulator-metal layers via atomic layer deposition.<sup>13,14</sup> The iridescence signature could be achieved from either lithographically patterned or self-assembled photonic crystal templates, e.g., anodized aluminium oxide.17 Roll-to-roll fabrication of anodic alumina honeycomb templates,<sup>18</sup> together with spatial ALD methods compatible with large area processing,<sup>19,20</sup> show great promise for development of these devices on flexible and low-cost substrates.

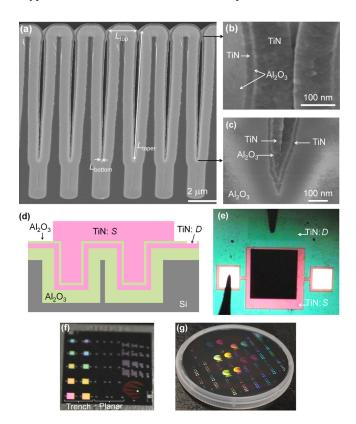

Figure 2 shows the frequency dependence of capacitance density for both trench and planar MIM capacitors. A

FIG. 2. (Color online) Dependence of zero-bias capacitance density (filled symbols) and ESR (open symbols) on frequency for trench and planar MIM capacitor with the same footprint area  $(0.33 \text{ mm}^2)$ .

significant high capacitance of  $36.2 \text{ fF}/\mu m^2$  is measured at 200 Hz for the trench capacitor in comparison to  $7.3 \text{ fF}/\mu\text{m}^2$ for its planar equivalent with the same surface footprint  $(A_{\rm pl} = 0.33 \,\mathrm{mm}^2)$ . This increase in capacitance of ~5 shows potential for system in package (SiP) anticouterfeit applications when considered from the perspective of footprint reduction. The capacitance densities for both planar and trench devices remain almost constant from 200 Hz to 10 kHz. At frequencies between 10 and 100 kHz the capacitance density for the planar device remains relatively unchanged (0.2% drop); however, a roll-off in capacitance density is observed for the trench device (12% drop). The ESR data for both planar and trench devices is also shown in Fig. 2. The ESR data does not vary significantly from 10 to 100 kHz (<5% drop) with measured values at 100 kHz of 740  $\Omega$  for the planar device and 820  $\Omega$  for the trench device. The large ESR values are likely due to the sheet resistance of the TiN electrodes,  $R_{\Box} \approx 400 \ \Omega/\Box$  for a 25 nm thick film on the same substrate and also the access track design for the top contact [see Fig. 1(e)]. Subsequent process development has led to sheet resistance values  $\sim$ 70  $\Omega/\Box$  for 20 nm thick planar TiN films,<sup>21</sup> future devices shall employ this development where we expect to see an appreciable reduction in ESR.

The total impedance (Z) for the planar device follows the expected  $\log(|\mathbf{Z}|) \propto -\log(f)$  dependence for a simple RC circuit. However, the roll-off in capacitance for the trench device cannot be adequately described using a single RC relaxation time and suggests the presence of a parasitic element. A likely cause is the presence of recombinationlimited ALD reaction by-products formed during deposition of the TiN electrodes in the high-aspect ratio trench structures.<sup>15,16</sup> These contaminants could then lead to a higher density of impurities and interface traps at the TiN surface prior to deposition of the Al<sub>2</sub>O<sub>3</sub> insulating layer, analogous to CVD growth of TiN,<sup>4</sup> or ALD growth of TiN on planar surfaces with insufficient plasma duration.<sup>22</sup> Recent time-offlight mass spectrometry data on planar films grown with similar process parameters showed significant carbon levels, which would be expected to increase for films grown in high aspect-ratio structures.<sup>21</sup> Thus, increased access resistance resulting from plasma radical recombination losses may set a limit on the aspect ratio for 3D devices with plasma enhanced ALD metal electrodes, therefore future work will focus on thermal titanium nitride ALD processing routes.

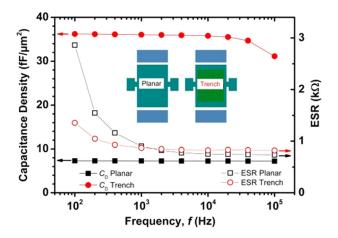

Figure 3 shows the measured capacitance values (at 200 Hz) for both planar and trench capacitors with increasing surface footprint area  $(A_{\rm pl})$ . The capacitance values estimated from Eqs. (1) and (2), respectively, show good agreement with the measured values for the planar  $(C_{\rm pl})$  and trench devices  $(C_{\rm tr})$

$$C_{\rm pl} = \varepsilon_0 \, k A_{\rm pl} / d, \tag{1}$$

$$C_{\rm tr} = \varepsilon_0 k [A_{\rm per} + W_{\rm tr} n_{\rm tr} (L_{\rm bottom} + L_{\rm top} + 2L_{\rm taper})]/d, \quad (2)$$

where  $\varepsilon_0$  is the permittivity of free space (8.85 × 10<sup>-12</sup> F/m); *d* is the thickness of the Al<sub>2</sub>O<sub>3</sub> layer (measured by X-SEM as being ~10 nm); and *k* is the dielectric constant of Al<sub>2</sub>O<sub>3</sub> (~8.3), extracted from the measured  $C_{\rm pl}$  vs  $A_{\rm pl}$  data taking

JVST A - Vacuum, Surfaces, and Films

FIG. 3. (Color online) Measured vs estimated capacitance values for planar devices ( $C_{pl}$ ) and trench devices ( $C_{tr}$ ) vs increasing device footprint area.

d = 10 nm. For the trench capacitors, estimated values for capacitance were derived using Eq. (2), where  $A_{per}$  is the planar perimeter area (including the bond pads) surrounding each trench array [see Fig. 1(e)];  $W_{tr}$  is the width of the trench region;  $n_{tr}$  is the number of trenches;  $L_{bottom}$ ,  $L_{top}$ , and  $L_{taper}$  are the lengths along the bottom; the top and the tapered walls of the trench, respectively.

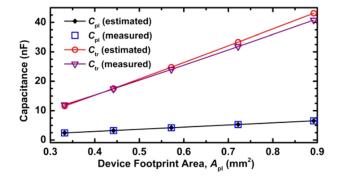

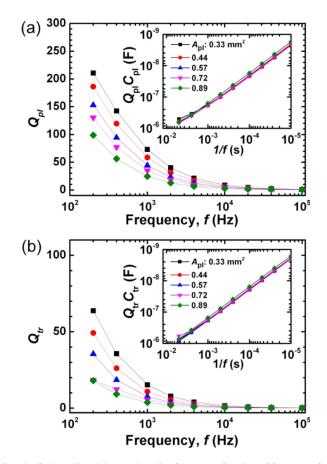

Figure 4(a) shows the quality factor  $(Q_{\rm pl})$  versus frequency (f) data for planar capacitors with increasing footprint area. There is a consistent reduction in quality factor at 200 Hz from  $Q_{\rm pl} \approx 210$  to  $Q_{\rm pl} \approx 100$  as the device footprint

FIG. 4. (Color online) Measured quality factor as a function of frequency for (a) planar capacitors  $(Q_{pl})$ , (b) trench capacitors  $(Q_{tr})$  of increasing footprint area  $(A_{pl})$ . Insets:  $Q_{pl}C_{pl}$  and  $Q_{tr}C_{tr}$  products, respectively, plotted vs inverse frequency.

increases from 0.33 to 0.89 mm<sup>2</sup>. This trend is mirrored in Fig. 4(b) for trench capacitors with the exception that lower quality factors are observed ( $Q_{tr} \le 65$ ). The log–log plots of the capacitance-quality factor products ( $Q_{pl}C_{pl}$  and  $Q_{tr}C_{tr}$ ) shown in the insets demonstrate that the quality factors for both trench and capacitor devices scale inversely with both capacitance and frequency, as expected,  $Q \propto (fRC)^{-1}$ . This would suggest a suitable application for such high aspect ratio MIM devices may lie in the low frequency (<100 kHz) regime.

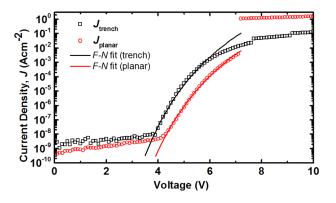

Figure 5 shows the leakage current density versus voltage data for both planar and trench capacitors (bottom electrode injection). The device footprint,  $A_{pl}$ , was used as the area for the planar device and the area of the trench device was estimated using Eq. (2). The planar capacitors exhibit a conventional leakage profile with a clear breakdown at ~6.8 V and low leakage current density at 1 V ( $J_{pl} \approx 7 \times 10^{-10} \text{ A cm}^{-2}$ ), in agreement with reports for TiN/Al<sub>2</sub>O<sub>3</sub>/Si MOS capacitors deposited using single-reactor ALD.<sup>23</sup> In the high-bias range, 4.2 V < V < 6.8 V, the  $J_{pl}$ –V data are well described by a simple Fowler–Nordheim fit

$$\ln \left( J_{\rm FN} / E^2 \right) \propto -\phi_0^{3/2} E^{-1},\tag{3}$$

for E = V/d, where  $\phi_0$  is the TiN/Al<sub>2</sub>O<sub>3</sub> barrier offset energy.<sup>4</sup>

The trench devices show higher leakage current density at low bias,  $J_{tr} \approx 3 \times 10^{-9} \,\mathrm{A \, cm^{-2}}$  at 1 V. The  $J_{tr}$ -V data can only be fit with the simple Fowler-Nordheim model in Eq. (3) for a narrower voltage window (4.2 V < V < 5.7 V). The fits over this range suggest a reduction in work function for the trench device,  $\phi_0^{tr} \approx 0.95 \phi_0^{pl}$ , consistent with trapping at the TiN/Al<sub>2</sub>O<sub>3</sub> electrode interface,<sup>4</sup> as discussed for the trench capacitance data presented in Fig. 2. There are several step-changes in the high-bias leakage data for the trench device, in contrast to the single breakdown step in the planar device. The gradual breakdown profile for the trench device, together with the increased leakage  $(J_{tr} > J_{pl})$  at low bias suggest contributions from multiple processes. The leakage could result from incorporation of carbon contaminants in the dielectric toward the bottom of the trenches due to radical recombination during TiN deposition, slight

FIG. 5. (Color online) Current density vs voltage breakdown measurements for typical planar and trench capacitors having the same device footprint (0.57 mm<sup>2</sup>), together with Fowler–Nordheim fits.

reductions in the dielectric thickness or local field enhancement due to asperities at the sidewalls and bottom of trench, or additionally due to series resistance effects. Further work will focus on assessing the relative magnitude of these effects and their implications for device performance. For example, because the power density in supercapacitors is inversely proportional to the equivalent series resistance, a trade-off is required between trench depth (aspect ratio), trench pitch and metal thickness.<sup>12,24</sup> For the proposed iridescent capacitor structures, where contactless reading via RF is desirable, capacitance density is not the dominant figure of merit. Lower aspect ratio structures may suffice to achieve suitable performance at frequencies up to several GHz, enabling contactless authentication at larger readerlabel separations.

## **IV. SUMMARY AND CONCLUSIONS**

All-ALD TiN/Al<sub>2</sub>O<sub>3</sub>/TiN MIM capacitors have been demonstrated for both planar and 3D configurations over frequency ranges from 200 Hz to 100 kHz. The large capacitance density and low leakage of these all-ALD 3D MIM devices shows promise for energy storage applications at low frequency and radio-freqency identification at intermediate frequency (125 kHz). Capacitance roll-off in 3D devices at frequencies above 10 kHz suggest that contaminants from recombination-limited plasma enhanced ALD in ultranarrow 3D structures may inhibit development of ultrahigh aspect ratio, all-plasma enhanced ALD TiN/Al<sub>2</sub>O<sub>3</sub>/TiN MIM capacitors for RF or memory applications at deep submicron critical dimensions. However, the lower thermal budget achieved using plasma enhanced ALD would be of benefit in back end of line processing for integrated lower aspect ratio (<20) 3D MIM devices. Challenges will include process optimization to reduce sheet resistance and also ensure thickness uniformity in high aspect ratio trenches for the metal electrodes, coupled with fabrication improvements for reducing sidewall roughness and asperities. Recently developed roll-to-roll templating methods together with spatial ALD offer exciting prospects for development of energy storage and anticounterfeiting devices on flexible and low-cost substrates.

#### ACKNOWLEDGMENTS

This work was supported by Science Foundation Ireland under the National Access Programme (NAP-411) and the Strategic Research Cluster "Functional Oxides and Related Materials for Electronics (FORME)" (Grant No. 07/SRC/ 11172); by the Irish Higher Education Authority PRTLI programs (cycle 4 "INSPIRE" and cycle 5 "TYFFANI").

<sup>&</sup>lt;sup>1</sup>F. Roozeboom, R. Elfrink, J. Verhoeven, J. van den Meerakker, and F. Holthuysen, Microelectron. Eng. **53**, 581 (2000).

<sup>&</sup>lt;sup>2</sup>A. Bajolet *et al.*, Proceedings of the ESSDERC 2005, Grenoble, 2005 (unpublished).

<sup>&</sup>lt;sup>3</sup>S. J. Ding et al., IEEE Trans. Electron Devices **51**, 886 (2004).

<sup>&</sup>lt;sup>4</sup>A. Bajolet *et al.*, Microelectron. Eng. **83**, 2189 (2006).

<sup>&</sup>lt;sup>5</sup>K. H. Cho, C. H. Choi, K. P. Hong, J. Y. Choi, Y. H. Jeong, S. Nahm, C. Y. Kang, S. J. Yoon, and H. J. Lee, IEEE Electron Device Lett. **29**, 684 (2008).

#### 01A103-5 Burke et al.: High aspect ratio iridescent three-dimensional MIM capacitors

- <sup>6</sup>M. Lukosius, C. Wenger, S. Pasko, L. Costina, J. Dabrowski, R. Sorge, H.

- J. Mussig, and C. Lohe, IEEE Trans. Electron Devices 55, 2273 (2008).

- <sup>7</sup>J. H. Klootwijk *et al.*, IEEE Electron Device Lett. **29**, 740 (2008).

- <sup>8</sup>P. Banerjee, I. Perez, L. Henn-Lecordier, S. B. Lee, and G. W. Rubloff, Nat. Nanotechnol. **4**, 292 (2009).

- <sup>9</sup>H. Johari and F. Ayazi, IEEE Trans. Compon. Packag. Technol. **32**, 808 (2009).

- <sup>10</sup>"Process integration, devices, and structures," in *International Technology Roadmap for Semiconductors*, 2011 ed., pp. 8–19.

- <sup>11</sup>S. Monaghan and I. M. Povey, Electron. Lett. 48, 230 (2012).

- <sup>12</sup>M. Meyyappan, J. Vac. Sci. Technol., A **31**, 050803 (2013).

- <sup>13</sup>Y. Bo and H. Guangwen, International Seminar on Business and Information Management, ISBIM (2008), p. 392.

- <sup>14</sup>M. Burke, M. Manning, and A. J. Quinn, European patent application EP13172247.2 (17 June 2013).

- <sup>15</sup>H. C. M. Knoops, E. Langereis, M. C. M. van de Sanden, and W. M. M. Kessels, J. Electrochem. Soc. **157**, G241 (2010).

- <sup>16</sup>M. Kariniemi, J. Niinisto, M. Vehkamaki, M. Kemell, M. Ritala, M. Leskela, and M. Putkonen, J. Vac. Sci. Technol., A **30**, 01A115 (2012).

- <sup>17</sup>H. Masuda, M. Ohya, H. Asoh, M. Nakao, M. Nohtomi, and T. Tamamura, Jpn. J. Appl. Phys., Part 2 38, L1403 (1999).

- <sup>18</sup>M. H. Lee *et al.*, Nano Lett. **11**, 3425 (2011).

- <sup>19</sup>D. H. Levy, D. Freeman, S. F. Nelson, P. J. Cowdery-Corvan, and L. M. Irving, Appl. Phys. Lett. **92**, 192101 (2008).

- <sup>20</sup>P. Poolt, A. Lankhorst, F. Roozeboom, K. Spee, D. Maas, and A. Vermeer, Adv. Mater. 22, 3564 (2010).

- <sup>21</sup>M. Burke, A. Blake, I. M. Povey, M. Schmidt, N. Petkov, P. Carolan, and A. J. Quinn, J. Vac. Sci. Technol., A 32, 031506 (2014).

- <sup>22</sup>J. Y. Kim, D. Y. Kim, H. O. Park, and H. Jeon, J. Korean Phys. Soc. 45, 1639 (2004).

- <sup>23</sup>D. Hoogeland, K. B. Jinesh, F. Roozeboom, W. F. A. Besling, M. de Sanden, and W. M. M. Kessels, J. Appl. Phys. **106**, 114107 (2009).

- <sup>24</sup>P. Banerjee, X. Y. Chen, K. Gregorczyk, L. Henn-Lecordier, and G. W. Rubloff, J. Mater. Chem. 21, 15391 (2011).