| Title                | Simulation of multigate SOI transistors with silicon, germanium and III-V channels                                                        |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Authors              | Razavi, Pedram                                                                                                                            |

| Publication date     | 2013                                                                                                                                      |

| Original Citation    | Razavi, P. 2013. Simulation of multigate SOI transistors with silicon, germanium and III-V channels. PhD Thesis, University College Cork. |

| Type of publication  | Doctoral thesis                                                                                                                           |

| Rights               | © 2013, Pedram Razavi http://creativecommons.org/licenses/by-nc-nd/3.0/                                                                   |

| Download date        | 2025-05-31 09:02:08                                                                                                                       |

| Item downloaded from | https://hdl.handle.net/10468/1287                                                                                                         |

# Simulation of Multigate SOI Transistors with Silicon, Germanium and III-V Channels

### Pedram Razavi

A thesis submitted in accordance with the requirements for the degree of Doctor of Philosophy

### NATIONAL UNIVERSITY OF IRELAND, CORK

School of Engineering

Department of Electrical and Electronic Engineering

August 2013

Supervisors: Prof. Jean-Pierre Colinge

Dr. Giorgos Fagas

Head of Department: Prof. Nabeel A. Riza

# **Table of Contents**

| DECLARATION                                                                          | 5  |

|--------------------------------------------------------------------------------------|----|

| ACKNOWLEDGEMENTS                                                                     | 6  |

| ABSTRACT                                                                             | 7  |

| LIST OF PUBLICATIONS                                                                 | 8  |

| JOURNAL PAPERS                                                                       | 8  |

| CONFERENCE PAPERS                                                                    | 12 |

| CHAPTER 1 : INTRODUCTION                                                             | 22 |

| 1.1. Scaling of CMOS technology                                                      | 22 |

| 1.2. Advanced CMOS technology                                                        | 23 |

| 1.3. New type of MOSFET                                                              | 24 |

| 1.4. Semiconductor device modeling                                                   | 26 |

| 1.5. Thesis organization                                                             | 27 |

| References                                                                           | 28 |

| CHAPTER 2 : SEMI-CLASSICAL AND QUANTUM TRANSPORT IN N-CHANNEL MOSFETS                | 30 |

| 2.1. Introduction                                                                    | 30 |

| 2.2. Semi-classical transport                                                        | 31 |

| 2.2.1 Drift-Diffusion simulations                                                    | 31 |

| 2.2.2 Hydrodynamic simulations                                                       |    |

| 2.2.3 Energy-Balance simulations                                                     |    |

| 2.3.1 Introduction                                                                   |    |

| 2.3.2 Real-Space vs. Mode-Space Approach                                             |    |

| 2.3.3 Self-consistent Simulations                                                    | 48 |

| 2.4. Conclusion                                                                      | 50 |

| References                                                                           | 50 |

| CHAPTER 3 : ELECTRON-PHONON INTERACTION IN POLAR AND NON-POLAR SEMICONDUCTOR DEVICES | 54 |

| 3.1. Introduction                                                                    | 54 |

| 3.2. Self-energy for intravalley acoustic phonon scattering                          | 57 |

| 3.3. Self-energy for intervalley optical phonon scattering                                                                                            | 58 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4. Self-energy for polar optical phonon scattering                                                                                                  | 60 |

| 3.5. Self-energy representation of phonon scattering in mode-space                                                                                    | 61 |

| 3.6. Conclusion                                                                                                                                       | 62 |

| References                                                                                                                                            | 62 |

| CHAPTER 4 : COMPARISON OF BREAKDOWN VOLTAGE IN BULK<br>AND SOI FINFETS                                                                                | 64 |

| 4.1. Introduction                                                                                                                                     | 64 |

| 4.2. Device structure and simulation parameters                                                                                                       | 65 |

| 4.3. Simulation results and discussion                                                                                                                | 66 |

| References                                                                                                                                            | 71 |

| CHAPTER 5 : PERFORMANCE INVESTIGATION OF SHORT-CHANNEL JUNCTIONLESS NANOWIRE TRANSISTORS VERSUS INVERSION- AND ACCUMULATION-MODE NANOWIRE TRANSISTORS | 72 |

| 5.1. Introduction                                                                                                                                     | 72 |

| 5.2. Intrinsic gate delay and energy-delay product: JNTs vs IM devices                                                                                | 73 |

| 5.2.1 Device structures and parameters                                                                                                                |    |

| around nanowire transistors                                                                                                                           | 79 |

| 5.3.1 Device structures and parameters                                                                                                                | 80 |

| 5.3.2 Results and discussion                                                                                                                          |    |

| 5.4. Short-channel effects: JNTs vs IM devices                                                                                                        |    |

| 5.4.1 Device structures and parameters                                                                                                                |    |

| 5.5. Short-channel effects: JNTs vs AM devices                                                                                                        | 88 |

| 5.5.1 Device structures and parameters                                                                                                                |    |

| 5.5.2 Results and discussion                                                                                                                          |    |

| References                                                                                                                                            | 96 |

|                                                                                                                                                       |    |

| CHAPTER 6 : INFLUENCE OF GERMANIUM CHANNEL PROPERTIES ON PERFORMANCE OF NANOWIRE TRANSISTORS                                                          | 98 |

| 6.1. Introduction                                                                                                                                     | 98 |

| 6.2. Device structures and parameters                                                                                                                 | 99 |

|                                                                                                                  | 103       |

|------------------------------------------------------------------------------------------------------------------|-----------|

| 6.4. Results and discussion                                                                                      | 107       |

| 6.4.1 Device characteristics                                                                                     | 107       |

| 6.4.2 Device physics                                                                                             | 112       |

| 6.5. Conclusion                                                                                                  | 116       |

| References                                                                                                       | 116       |

| CHAPTER 7 : PERFORMANCE INVESTIGATION OF III-V NANOWII TRANSISTORS                                               |           |

|                                                                                                                  |           |

| 7.1. Introduction                                                                                                | 120       |

| 7.1. Introduction                                                                                                |           |

|                                                                                                                  | 121       |

| 7.2. Device structure and simulation parameters                                                                  | 121       |

| <ul><li>7.2. Device structure and simulation parameters</li><li>7.3. Simulation results and discussion</li></ul> | 121123127 |

# **Declaration**

This thesis is the candidate's own work and has not been submitted for another degree, either at the University College Cork or elsewhere.

Pedram Razavi

## Acknowledgements

First, I would like to extend my sincerest thanks to my PhD supervisor Prof. Jean-Pierre Colinge for giving me the opportunity to carry out my PhD in his group at Tyndall National Institute. I am very grateful for his insightful guidance, priceless support and understanding. Without his constant guidance, encouragement, support, and a stress-free working environment, I could not reach this point. It was a great pleasure to work for him.

I am also very grateful to Dr. Giorgos Fagas that has been on my PhD supervision committee for the last two years of my PhD. His professional guidance and support encouraged my academic progress.

I am very thankful to Prof. Jean-Pierre Raskin and Dr. Ray Duffy for serving on my dissertation committee and especially for their encouragements and suggestions at my PhD review meetings.

Deeply thanks to my many former and current group members of the Ultimate Silicon Devices group in Tyndall National Institute: Dr. Aryan Afzalian, Dr. Isabelle Ferain, Dr. Chi-Woo Lee, Dr. Abhinav Kranti, Dr. Samaresh Das, Dr. Ran Yan, and Dr. Ran Yu.

I would like to thank all my colleagues and friends at the Tyndall National Institute, University College Cork: Prof. Cindy Colinge, Dr. Russell Duane, Prof. Jim Greer, Dr. Karim Cherkaoui, and John Kissane.

My huge thanks go to my parents, Parvaneh and Mozafar, and my sister, Pegah, for their love, support and encouragements during my studies. Without their encouragement and support I would have never reached this point.

#### **Abstract**

In this work by employing numerical three-dimensional simulations we study the electrical performance and short channel behavior of several multi-gate transistors based on advanced SOI technology. These include FinFETs, triple-gate and gate-allaround nanowire FETs with different channel material, namely Si, Ge, and III-V compound semiconductors, all most promising candidates for future nanoscale CMOS technologies. Also, a new type of transistor called "junctionless nanowire transistor" is presented and extensive simulations are carried out to study its electrical characteristics and compare with the conventional inversion- and accumulation-mode transistors. We study the influence of device properties such as different channel material and orientation, dimensions, and doping concentration as well as quantum effects on the performance of multi-gate SOI transistors. For the modeled n-channel nanowire devices we found that at very small cross sections the nanowires with silicon channel are more immune to short channel effects. Interestingly, the mobility of the channel material is not as significant in determining the device performance in ultrashort channels as other material properties such as the dielectric constant and the effective mass. Better electrostatic control is achieved in materials with smaller dielectric constant and smaller source-to-drain tunneling currents are observed in channels with higher transport effective mass. This explains our results on Si-based devices.

In addition to using the commercial TCAD software (Silvaco and Synopsys TCAD), we have developed a three-dimensional Schrödinger-Poisson solver based on the non-equilibrium Green's functions formalism and in the framework of effective mass approximation. This allows studying the influence of quantum effects on electrical performance of ultra-scaled devices. We have implemented different mode-space methodologies in our 3D quantum-mechanical simulator and moreover introduced a new method to deal with discontinuities in the device structures which is much faster than the coupled-mode-space approach.

# List of publications

# Journal papers

- (I) Based on results presented in this thesis:

- [1] "Performance comparison of III-V junctionless nanowire transistors and inversion-mode devices," **P. Razavi**, G. Fagas, *Applied Physics Letters*, vol. 103, p. 063506, 2013.

- [2] "Influence of channel material properties on performance of nanowire transistors," **P. Razavi**, G. Fagas, I. Ferain, R. Yu, S. Das, and J.-P. Colinge, *Journal of Applied Physics*, vol. 111, pp. 124509-124509-8, 2012.

- [3] "A Simulation Comparison between Junctionless and Inversion-Mode MuGFETs," J.-P. Colinge, A. Kranti, R. Yan, I. Ferain, N. D. Akhavan, <u>P. Razavi</u>, C.-W. Lee, , R. Yu, and C. Colinge, *ECS Trans.*, vol. 35, issue 5, pp, 63-72, 2011.

- [4] "Improvement of carrier ballisticity in junctionless nanowire transistors," N. D. Akhavan, I. Ferain, <u>P. Razavi</u>, R. Yu, and J.-P. Colinge, *Applied Physics Letters*, vol. 98, p. 103510, 2011.

- [5] "Junctionless Nanowire Transistor (JNT): Properties and design guidelines," J.-P. Colinge, A. Kranti, R. Yan, C. Lee, I. Ferain, R. Yu, N. D. Akhavan, <u>P. Razavi</u>, *Solid-State Electronics*, vol. 65-66, pp. 33-37, 2011.

- [6] "Performance estimation of junctionless multigate transistors," C.-W. Lee, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, <u>P. Razavi</u>, and J.-P. Colinge, *Solid-State Electronics*, vol. 54, pp. 97-103, 2010.

- [7] "LDD and Back-Gate Engineering for Fully Depleted Planar SOI Transistors with Thin Buried Oxide," R. Yan, R. Duane, **P. Razavi**, A. Afzalian, I. Ferain, C.-W. Lee, N. D. Akhavan, B.-Y. Nguyen, K.K. Bourdelle, and and J.-P. Colinge, *Electron Devices*, *IEEE Transactions on*, vol. 57, pp. 1319-1326, 2010.

- [8] "Nanowire transistors without junctions," J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, <u>P. Razavi</u>, B. O'Neill, A. Blake, and M. White, *Nature nanotechnology*, vol. 5, pp. 225-229, 2010.

- [9] "A new F (ast)-CMS NEGF algorithm for efficient 3D simulations of switching characteristics enhancement in constricted tunnel barrier silicon nanowire

MuGFETs," A. Afzalian, N. D. Akhavan, C.-W. Lee, R. Yan, I. Ferain, <u>P. Razavi</u>, and J.-P. Colinge, *Journal of computational electronics*, vol. 8, pp. 287-306, 2009.

#### (II) Other contributions of the author

- [10] "Impact ionization induced dynamic floating body effect in junctionless transistors," R. Yu, A. N. Nazarov, V. S. Lysenko, S. Das, I. Ferain, <u>P. Razavi</u>, M. Shayesteh, A. Kranti, R. Duffy, J-P. Colinge, Solid-State Electronics, (Article in press) 2013.

- [11] "Device Design and Estimated Performance for p-Type Junctionless Transistors on Bulk Germanium Substrates," R. Yu, S. Das, I. Ferain, <u>P. Razavi</u>, M. Shayesteh, A. Kranti, R. Duffy, and J-P. Colinge, Electron Devices, IEEE Transactions on, vol. 59, pp. 2308-2313, 2012.

- [12] "Mobility enhancement effect in heavily doped junctionless nanowire silicon-on-insulator metal-oxide-semiconductor field-effect transistors," T. Rudenko, A. Nazarov, I. Ferain, S. Das, R. Yu, S. Barraud, <u>P. Razavi</u>, Applied Physics Letters, vol. 101, p. 213502, 2012.

- [13] "Emission and absorption of optical phonons in Multigate Silicon Nanowire MOSFETs," N. Dehdashti Akhavan, I. Ferain, R. Yu, <u>P. Razavi</u>, and J.-P. Colinge, Journal of Computational Electronics, vol. 11, pp. 249-265, 2012.

- [14] "Influence of discrete dopant on quantum transport in silicon nanowire transistors," N. D. Akhavan, I. Ferain, R. Yu, <u>P. Razavi</u>, and J.-P. Colinge, *Solid-State Electronics*, vol. 70, pp. 92–100, 2012.

- [15] "Bipolar effects in unipolar junctionless transistors," M. S. Parihar, D. Ghosh, G. A. Armstrong, R. Yu, <u>P. Razavi</u>, and A. Kranti, Applied Physics Letters, vol. 101, pp. 093507-093507-3, 2012.

- [16] "Characterization of a junctionless diode," R. Yu, I. Ferain, N. D. Akhavan, **P. Razavi**, R. Duffy, and J.-P. Colinge, Applied Physics Letters, vol. 99, p. 013502, 2011.

- [17] "Investigation of high-performance sub-50 nm junctionless nanowire transistors," R. Yan, A. Kranti, I. Ferain, C.-W. Lee, R. Yu, N. Dehdashti, <u>P. Razavi</u>, and J.-P. Colinge, Microelectronics Reliability, vol. 51, pp. 1166-1171, 2011.

- [18] "Comparative Study of Random Telegraph Noise in Junctionless and Inversion-Mode MuGFETs," A. Nazarov, C.-W. Lee, A. Kranti, I. Ferain, R. Yan, N. D. Akhavan, P. Razavi, R. Yu, J.-P. Colinge, *ECS Trans.*, vol. 35, issue 5, pp.73-78, 2011.

- [19] "Analog Operation Temperature Dependence of nMOS Junctionless Transistors Focusing on Harmonic Distortion," R. T. Doria, M. A. Pavanello, R. D. Trevisoli, M. de Souza, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, P. Razavi, R. Yu, A. Kranti, and J.-P. Colinge, Journal of Integrated Circuits and Systems, vol. 6, pp. 114-121, 2011.

- [20] "Junctionless Multiple-Gate Transistors for Analog Applications," R. T. Doria, M. A. Pavanello, R. D. Trevisoli, M. de Souza, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, **P. Razavi**, R. Yu, A. Kranti, and J.-P. Colinge, Electron Devices, IEEE Transactions on, vol. 58, No. 8, pp. 2515-2519, 2011.

- [21] "Field-effect mobility extraction in nanowire field-effect transistors by combination of transfer characteristics and random telegraph noise measurements," A. Nazarov, I. Ferain, N. D. Akhavan, <u>P. Razavi</u>, R. Yu, and J. Colinge, Applied Physics Letters, vol. 99, p. 073502, 2011.

- [22] "Random telegraph-signal noise in junctionless transistors," A. Nazarov, I. Ferain, N. D. Akhavan, <u>P. Razavi</u>, R. Yu, and J.-P. Colinge, Applied Physics Letters, vol. 98, p. 092111, 2011.

- [23] "Nanowire to Single-Electron Transistor Transition in Trigate SOI MOSFETs," N. D. Akhavan, A. Afzalian, C.-W. Lee, R. Yan, I. Ferain, **P. Razavi**, R. Yu. G. Fagas, J-P. Colinge, Electron Devices, IEEE Transactions on, vol. 58, pp. 26-32, 2011.

- [24] "Junctionless Nanowire Transistor: Complementary Metal-Oxide-Semiconductor Without Junctions," J.-P. Colinge, I. Ferain, A. Kranti, C.-W. Lee, N. D. Akhavan, <u>P. Razavi</u>, R. Yan, and R. Yu, Science of Advanced Materials, vol. 3, pp. 477-482, 2011.

- [25] "Junctionless Transistors: Physics and Properties," J.-P. Colinge, C. Lee, N. Dehdashti Akhavan, R. Yan, I. Ferain, <u>P. Razavi</u>, A.Kranti, and R.Yu, Semiconductor-On-Insulator Materials for Nanoelectronics Applications, pp. 187-200, 2011.

- [26] "Influence of Elastic and Inelastic Electron-Phonon Interaction on Quantum Transport in Multigate Silicon Nanowire MOSFETs,"N. D. Akhavan, A. Afzalian,

- A. Kranti, I. Ferain, C.-W. Lee, R. Yan, <u>P. Razavi</u>, Ran Yu, and J.-P. Colinge, *Electron Devices, IEEE Transactions on*, vol. 58, pp. 1029-1037, 2011.

- "The Roles of the Electric Field and the Density of Carriers in the Improved Output Conductance of Junctionless Nanowire Transistors," R. T. Doria, M. A. Pavanello, R. D. Trevisoli, M. De Souza, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, **P. Razavi**, R. Yu, A. Kranti, J.-P. Colinge, ECS Trans., vol. 35, issue 5, pp, 283-288, 2011.

- [28] "Junctionless 6T SRAM cell," A. Kranti, C.-W. Lee, I. Ferain, R. Yan, N. Akhavan, <u>P. Razavi</u>, R. Yu, G.A. Armstrong, and J-P. Colinge, Electronics letters, vol. 46, pp. 1491-1493, 2010.

- [29] "Low subthreshold slope in junctionless multigate transistors," C.-W. Lee, A. N. Nazarov, I. Ferain, N. D. Akhavan, R. Yan, <u>P. Razavi</u>, R. Yu, R. T. Doria, J-P. Colinge, Applied Physics Letters, vol. 96, p. 102106, 2010.

- [30] "High-temperature performance of silicon junctionless MOSFETs," C.-W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. Dehdashti Akhavan, **P. Razavi**, and J.-P. Colinge, Electron Devices, IEEE Transactions on, vol. 57, pp. 620-625, 2010.

- [31] "Analog Operation and Harmonic Distortion Temperature Dependence of nMOS Junctionless Transistors," R. T. Doria, M. A. Pavanello, C.-W. Lee, I. Ferain, N. Dehdashti-Akhavan, R. Yan, <u>P. Razavi</u>, R. Yu, A. Kranti and J.-P. Colinge, ECS Trans., vol. 31, issue 1, pp, 13-20, 2010.

- [32] "Reduced electric field in junctionless transistors," J.-P. Colinge, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, <u>P. Razavi</u>, R. Yu, A. N. Nazarov, and R. T. Doria, Applied Physics Letters, vol. 96, p. 073510, 2010.

- [33] "Effect of intravalley acoustic phonon scattering on quantum transport in multigate silicon nanowire metal-oxide-semiconductor field-effect transistors," N. D. Akhavan, A. Afzalian, C.-W. Lee, R. Yan, I. Ferain, **P. Razavi**, R. Yu, G. Fagas, and J-P. Colinge, Journal of Applied Physics, vol. 108, pp. 034510-034510-8, 2010.

- [34] "Simulation of quantum current oscillations in trigate SOI MOSFETs," N. D. Akhavan, A. Afzalian, C.-W. Lee, R. Yan, I. Ferain, <u>P. Razavi</u>, G. Fagas, and J-P. Colinge, Electron Devices, IEEE Transactions on, vol. 57, pp. 1102-1109, 2010.

- [35] "NBTI and hot-carrier effects in accumulation-mode Pi-gate pMOSFETs," C.-W. Lee, I. Ferain, A. Afzalian, R. Yan, N. Dehdashti, **P. Razavi**, J-P. Colinge, and J. T. Park, Microelectronics Reliability, vol. 49, pp. 1044-1047, 2009.

# **Conference papers**

#### (I) Based on results presented in this thesis:

- [1] "Electron transport in germanium junctionless nanowire transistors," <u>P.</u> <u>Razavi</u>, G. Fagas, I. Ferain, R. Yu, and S. Das, *in Solid-State Device Research Conference (ESSDERC)*, 2012 Proceedings of the European, 2012, pp. 326-329. [Oral presentation]

- [2] "Intrinsic gate delay and energy-delay product in junctionless nanowire transistors," **P. Razavi**, I. Ferain, S. Das, R. Yu, N. D. Akhavan, and J.-P. Colinge, in *Ultimate Integration on Silicon (ULIS), 2012 13th International Conference on*, 2012, pp. 125-128. [Poster presentation]

- [3] "Performance investigation of short-channel junctionless multigate transistors," **P. Razavi**, G. Fagas, I. Ferain, N. D. Akhavan, R. Yu, and J.-P. Colinge, *in Ultimate Integration on Silicon (ULIS), 2011 12th International Conference on*, 2011, pp. 1-4. [Poster presentation]

- [4] "Investigation of Short-Channel Effects in Junctionless Nanowire Transistors," <u>P. Razavi</u>, N. Dehdashti-Akhavan, R. Yu, G. Fagas, I. Ferain, and J.-P. Colinge, *International Conference on Solid State Devices and Materials* (SSDM2011), Nagoya, Japan, 2011. [Poster presentation]

- [5] "Comparison of the switching speed in junctionless and accumulation-mode gate-all-around nanowire transistors," **P. Razavi**, R. Yan, I. Ferain, N. Dehdashti Akhavan, R. Yu, and J.-P. Colinge, *Proceedings of EUROSOI 2011*, *VII Workshop of the Thematic Network on Silicon On Insulator Technology, Devices and Circuits*, 2011. [Oral presentation]

- [6] "Comparison of Breakdown Voltage in Bulk and SOI FinFETs," <u>P. Razavi</u>, R.Duane, R. Yan, I. Ferain, N. Dehdashti Akhavan, R. Yu, C.-W. Lee, and J.-P. Colinge, *in Proceedings of EUROSOI Conference*, 2010. [Oral presentation]

- [7] "Short-channel junctionless nanowire transistors," C. Lee, I. Ferain, A. Kranti, N. D. Akhavan, <u>P. Razavi</u>, R. Yan, R. Yu, B. O'Neill, A. Blake, M. White, A.M. Kelleher, B. McCarthy, S. Gheorghe, R. Murphy, and J.-P. Colinge, *International Conference on Solid State Devices and Materials (SSDM 2010)*, pp. 1044-1045, 2010.

- [8] "Back-gate mirror doping for fully depleted planar SOI transistors with thin buried oxide," R. Yan, R. Duane, <u>P. Razavi</u>, A. Afzalian, I. Ferain, C.-W. Lee, N.

- Dehdashti, B.-Y. Nguten, K. K. Bourdelle, and J.-P. Colinge, in VLSI Technology Systems and Applications (VLSI-TSA), 2010 International Symposium on, 2010, pp. 76-77.

- [9] "A new F (ast)-CMS Algorithm for Efficient Three-Dimensional NEGF Simulations of Arbitrarily Shaped Silicon Nanowire MUGFETs," A. Afzalian, C.-W. Lee, N. D. Akhavan, R. Yan, I. Ferain, **P. Razavi**, and J.-P. Colinge, *in Simulation of Semiconductor Processes and Devices, 2009. SISPAD'09. International Conference on*, 2009, pp. 1-4.

- [10] "LDD depletion effects in thin-BOX FDSOI devices with a ground plane," R. Yan, R. Duane, <u>P. Razavi</u>, A. Afzalian, I. Ferain, C. Lee, N. Dehdashti-Akhavan, K. Bourdelle, B. Nguyen, and J.-P. Colinge, *in SOI Conference*, 2009 IEEE International, 2009, pp. 1-2.

- [11] "SOI gated resistor: CMOS without junctions," J.-P. Colinge, C. Lee, A. Afzalian, N. Dehdashti, R. Yan, I. Ferain, **P. Razavi**, B. O'Neill, A. Blake, and M. White, *in SOI Conference*, 2009 IEEE International, 2009, pp. 1-2.

#### (II) Other contributions of the author:

- [12] "Sensitivity analysis of steep subthreshold slope (S-slope) in Junctionless nanotransistors," M. S. Parihar, D. Ghosh, G. A. Armstrong, R. Yu, <u>P. Razavi</u>, S. Das, I. Ferain, and A. Kranti, *in Nanotechnology (IEEE-NANO), 2012 12th IEEE Conference on*, 2012, pp. 1-4.

- [13] "Top-down process of Germanium nanowires using EBL exposure of Hydrogen Silsesquioxane resist," R. Yu, S. Das, R. Hobbs, Y. Georgiev, I. Ferain, <u>P. Razavi</u>, N. D. Akhavan, C. A. Colinge, and J.-P. Colinge, *in Ultimate Integration on Silicon (ULIS)*, 2012 13th International Conference on, 2012, pp. 145-148.

- [14] "Extraction of channel mobility in nanowire MOSFETs using Id (Vg) characteristics and random telegraph noise amplitude," A. Nazarov, C. Lee, A. Kranti, I. Ferain, R. Yan, N. D. Akhavan, **P. Razavi**, R. Yu, and J.-P. Colinge, *in Ultimate Integration on Silicon (ULIS)*, 2011 12th International Conference on, 2011, pp. 1-3.

- [15] "Influence of single-atom impurity scattering on quantum transport in silicon nanowire transistors," N. Dehdashti Akhavan, I. Ferain, R. Yan, **P. Razavi**, R. Yu,

- and J.-P. Colinge, in Proceedings of EUROSOI Conference, VII Workshop of the Thematic Network on Silicon On Insulator Technology, Devices and Circuits, 2011.

- [16] "Random dopant variation in junctionless nanowire transistors," N. D. Akhavan, I. Ferain, <u>P. Razavi</u>, R. Yu, and J.-P. Colinge, *in SOI Conference (SOI)*, 2011 IEEE International, 2011, pp. 1-2.

- [17] "Junctionless nanowire transistor (JNT): Properties and design guidelines," A. Kranti, R. Yan, C.-W. Lee, I. Ferain, R. Yu, N. D. Akhavan, <u>P. Razavi</u>, and J. Colinge, in Solid-State Device Research Conference (ESSDERC), 2010 Proceedings of the European, 2010, pp. 357-360.

- [18] "Analog operation of junctionless transistors at cryogenic temperatures," R. Doria, M. Pavanello, R. Trevisoli, M. de Souza, C. Lee, I. Ferain, N. Dehdashti Akhavan, R. Yan, **P. Razavi**, R. Yu, A. Kranti, and J.-P. Colinge *in SOI Conference (SOI)*, 2010 IEEE International, 2010, pp. 1-2.

- [19] "Dissipative transport in Multigate silicon nanowire transistors," N. Dehdashti, A. Kranti, I. Ferain, C.-W. Lee, R. Yan, <u>P. Razavi</u>, R. Yu, and J.-P. Colinge, in Simulation of Semiconductor Processes and Devices (SISPAD), 2010 International Conference on, 2010, pp. 97-100.

- [20] "Emission and absorption of optical phonons in multigate silicon nanowire MOSFETs," N. Dehdashti, A. Kranti, I. Ferain, C. W. Lee, R. Yan, <u>P. Razavi</u>, R. Yu, and J.-P. Colinge, *in Computational Electronics (IWCE)*, 2010 14th International Workshop on, 2010, pp. 1-4.

- [21] "Electric Field in Junctionless MuGFETs," J.-P. Colinge, C.-W. Lee, I. Ferain, N. Dehdashti Akhavan, R. Yan, <u>P. Razavi</u>, R. Yu, A.N. Nazarov, and R. T. Doria, *in Proceedings of EUROSOI Conference*, 2010.

- [22] "Nanowire zero-capacitor DRAM transistors with and without junctions," C.-W. Lee, R. Yan, I. Ferain, A. Kranti, N. Akhvan, <u>P. Razavi</u>, R. Yu, and J.-P. Colinge, *in Nanotechnology (IEEE-NANO), 2010 10th IEEE Conference on*, 2010, pp. 242-245.

- [23] "Emission and absorption of optical phonons in multigate silicon nanowire MOSFETs," N. Dehdashti, A. Kranti, I. Ferain, C. Lee, R. Yan, <u>P. Razavi</u>, R. Yu, and J.-P. Colinge, *in Computational Electronics (IWCE)*, 2010 14th International Workshop on, 2010, pp. 1-4.

- [24] "Junctionless Multiple Gate Transistors Performance for Analog Applications," R.T. Doria, M.A. Pavanello, C.-W. Lee, I. Ferain, N. Dehdashti

- Akhavan, R. Yan, <u>P. Razavi</u>, R. Yu, and J.-P.Colinge, *in Proceedings of EUROSOI Conference*, 2010.

- [25] "3D Simulation of RTS Amplitude in Accumulation-Mode and Inversion-Mode Trigate SOI MOSFETs,"R. Yan, A. Cullen, A. Afzalian, I. Ferain, C.-W. Lee, N. Dehdashti Akhavan, <u>P. Razavi</u>, and J.-P. Colinge, *in Proceedings of EUROSOI Conference*, 2010.

- [26] "Substrate bias effects in MuGFETs," C.-W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. Dehdashti Akhavan, <u>P. Razavi</u>, and J.-P. Colinge, *in Proceedings of EUROSOI Conference*, 2010.

- [27] "Effect of intravalley acoustic phonon scattering on mobility in silicon nanowire transistor," N. Dehdashti Akhavan, A. Afzalian, C.-W. Lee, R. Yan, I. Ferain, **P. Razavi**, and J.-P. Colinge, *in Proceedings of EUROSOI Conference*, 2010. [28] "Hot carrier (HC) and bias-temperature-instability (BTI) degradation of MuGFETs on silicon oxide and silicon nitride buried layers," C.-W. Lee, I. Ferain, A. Afzalian, K.-Y. Byun, R. Yan, N. Dehdashti, **P. Razavi**, W. Xiong, J.-P. Colinge, and C. Colinge, *in Solid State Device Research Conference*, 2009. ESSDERC'09. Proceedings of the European, 2009, pp. 261-264.

- [29] "Variable-barrier tunneling SOI transistor (VBT),"A. Afzalian, N. Dehdashti, I. Ferain, C. Lee, R. Yan, <u>P. Razavi</u>, and J.-P. Colinge, *in SOI Conference, 2009 IEEE International*, 2009, pp. 1-2.

# **List of Figures**

| Figure 1.1 – Schematic of (a) bulk and SOI multi-gate FETS, as well as, (b) cross-                  |

|-----------------------------------------------------------------------------------------------------|

| section of different multi-gate FETS and their corresponding effective number of                    |

| gates                                                                                               |

| Figure 1.2 - Evaluation of potential solutions for logic CMOS [Source: ITRS Edition                 |

| 2011]                                                                                               |

| Figure 1.3 - Source and drain doping of inversion-mode and junctionless transiston                  |

| with short channel and ultra-short channel                                                          |

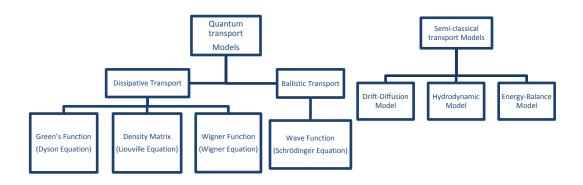

| Figure 1.4 - Diagram of some of the widely used semi-classical and quantum                          |

| transport models                                                                                    |

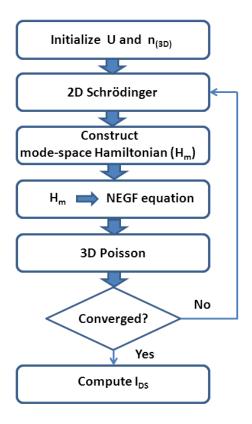

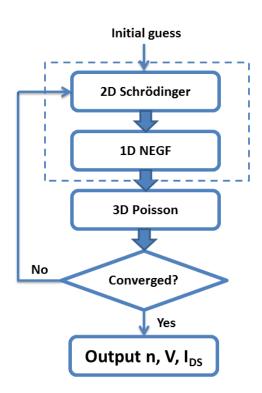

| Figure 2.1 - The flow chart of mode-space approach implemented in our simulator                     |

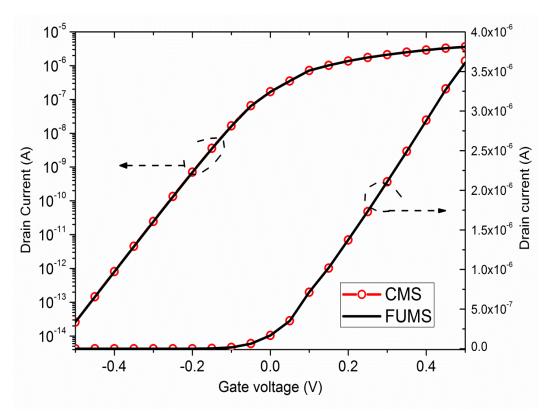

| Figure 2.2 - The $I_{DS}$ - $V_{GS}$ curves for silicon nanowire transistors in logarithm (left)    |

| and linear (right) scales (the circle symbols (red) and solid lines (black) represent               |

| results obtained by CMS approach, and the FUMS approach, respectively)45                            |

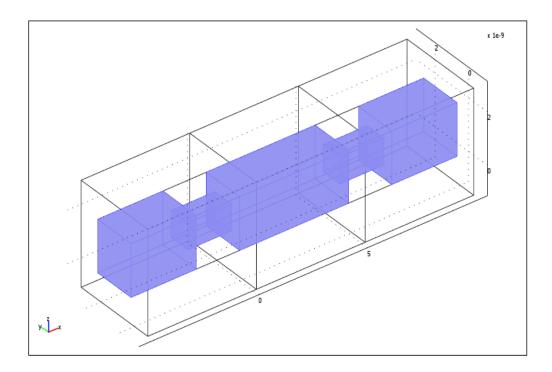

| Figure 2.3 – Device with variant body shape                                                         |

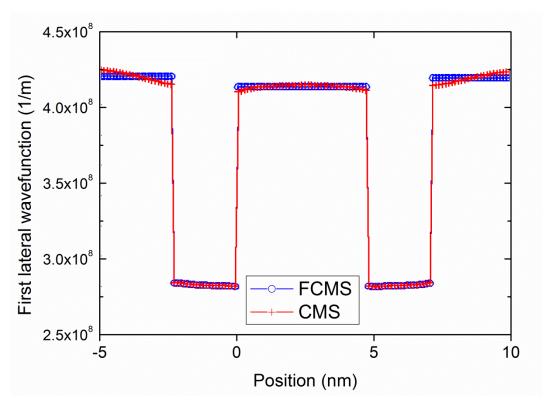

| Figure 2.4 - Evolution of first lateral wavefunction in the middle of the silicon                   |

| nanowire transistor with variant body structure obtained by FCMS (blue) and CMS                     |

| (red) approaches                                                                                    |

| Figure 2.5- The schematic representation of self-consistent solution between charge                 |

| density and electrostatic potential                                                                 |

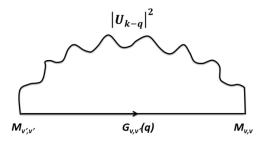

| Figure 3.1 - Feynman diagram representation for the first self-consistent Born                      |

| approximation of phonon scattering                                                                  |

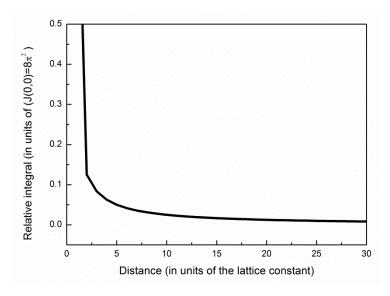

| Figure 3.2 - Relative values of the integral J (r,q ) for infinite screening length                 |

| (q0=0)61                                                                                            |

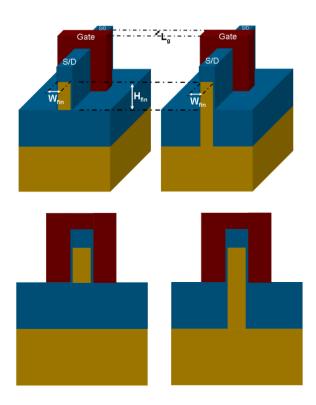

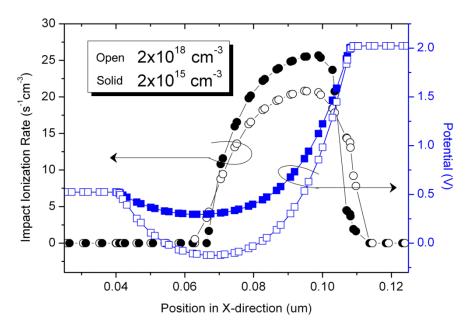

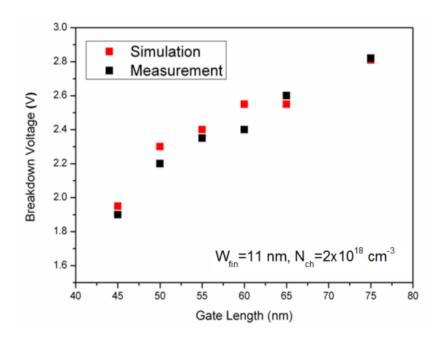

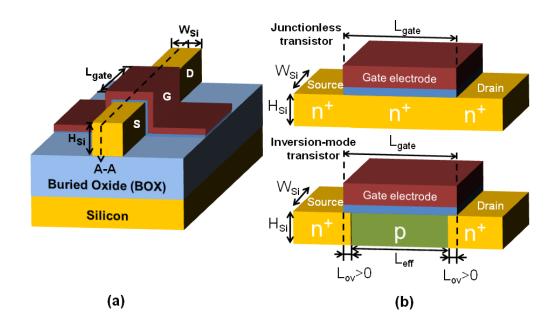

| Figure 4.1- (a) 3D schematics and (b) Cross-sectional view along the gate of bulk                   |

| and SOI FinFET structures65                                                                         |

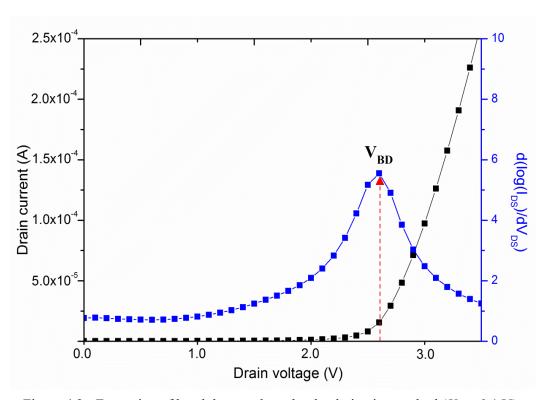

| Figure 4.2 - Extraction of breakdown voltage by the derivative method ( $V_{gs} = 0.1 \text{ V}$ ). |

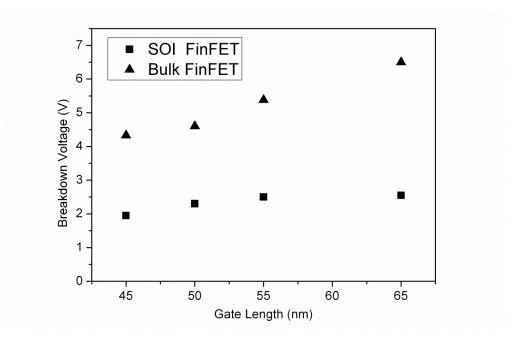

| Figure 4.3 - Breakdown voltage comparison of bulk and SOI FinFETs for different                     |

| gate lengths ( $W_{fin}$ =11 nm, $H_{fin}$ =60 nm)                                                  |

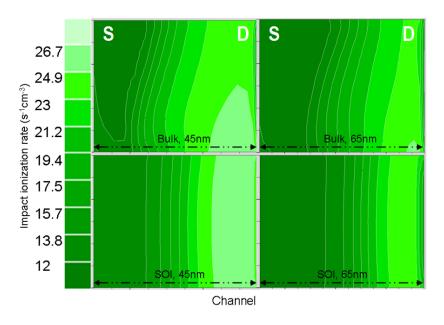

| Figure 4.4 - Impact ionization rate of bulk and SOI FinFETs for different gate                      |

| lengths (Vertical cut along source and drain, $V_{ds}$ =1.5 V)                                      |

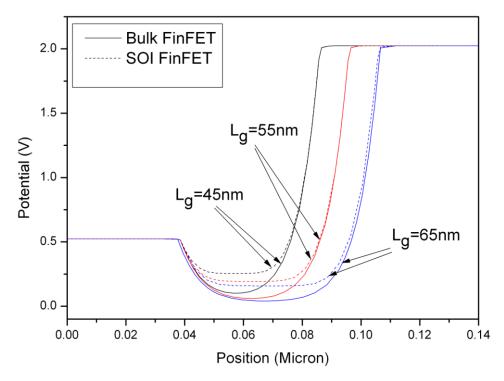

| Figure 4.5 - Potential barrier of bulk and SOI FinFETs for different gate lengths        |

|------------------------------------------------------------------------------------------|

| (vertical cut along source and drain, $V_{ds}$ =1.5V).                                   |

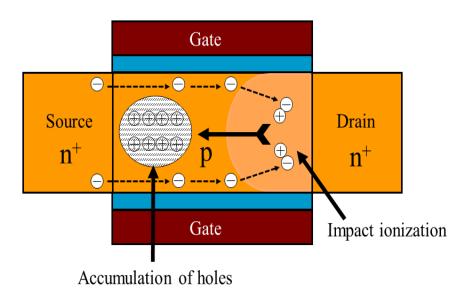

| Figure 4.6 - Cross-sectional schematics of floating-body effect in SOI MOSFETs68         |

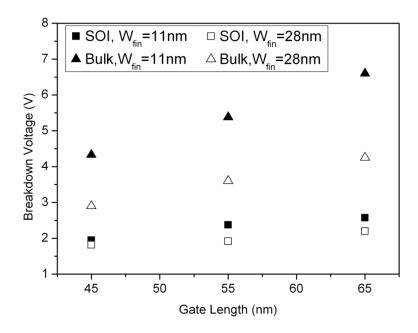

| Figure 4.7 - Breakdown voltage of bulk and SOI FinFETs for different fin widths in       |

| different gate lengths ( $N_{ch}$ =2×10 <sup>18</sup> cm <sup>-3</sup> )69               |

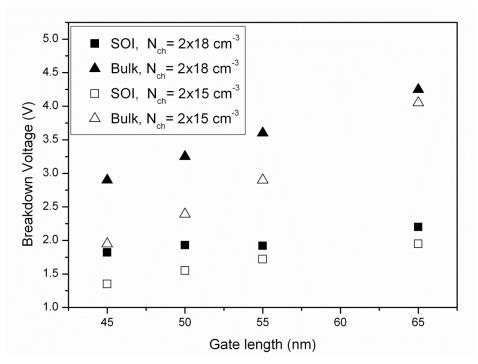

| Figure 4.8 - Breakdown voltage of bulk and SOI FinFETs for different channel             |

| doping in different gate lengths (W <sub>fin</sub> =28 nm)                               |

| Figure 4.9 - Impact ionization and potential barrier in the middle of the channel of     |

| the SOI device for different channel doping (Vertical cut along source and drain,        |

| $W_{fin}$ =28 nm, $Lg$ = 65 nm)                                                          |

| Figure 4.10 - Comparison of simulation and measured results for the SOI FinFET           |

| devices with different gate lengths                                                      |

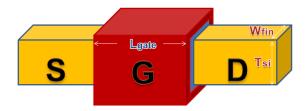

| Figure 5.1 - (a) Bird's eye view of a junctionless and IM triple-gate nanowire           |

| MOSFETs (b) doping profile in the longitudinal cross-sections of JNTs and IM             |

| devices74                                                                                |

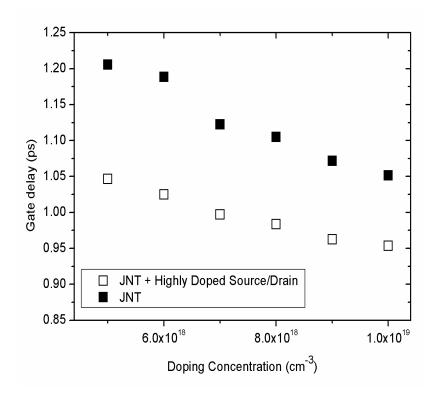

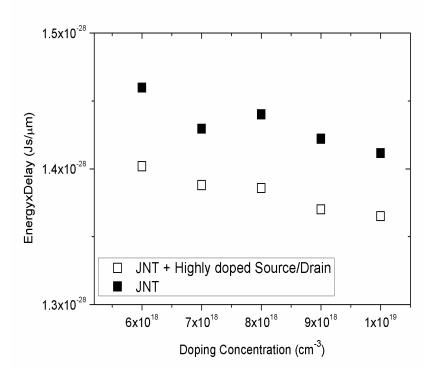

| Figure 5.2 - Intrinsic gate delay of junctionless nanowire transistors for different     |

| doping concentration values ( $L_{gate}$ =15 nm)                                         |

| Figure 5.3 - Energy-delay product of junctionless nanowire transistors for different     |

| doping concentration values ( $L_{gate}$ =15 nm)                                         |

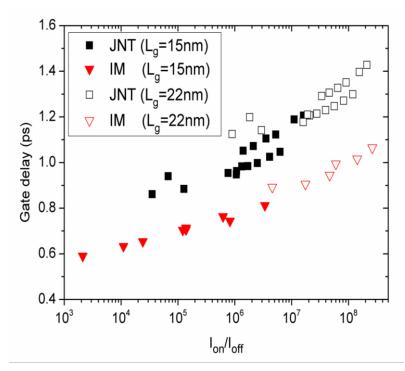

| Figure 5.4 - Comparison of intrinsic gate delay in JNTs and IM devices for gate          |

| lengths 15 nm and 22 nm                                                                  |

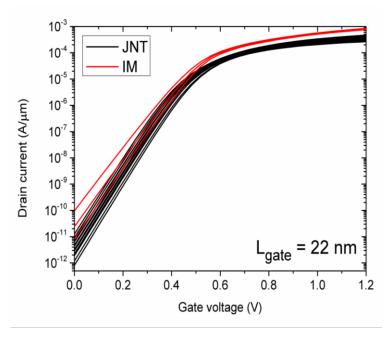

| Figure 5.5 - Comparison of drain current versus gate voltage in JNTs and IM devices      |

| $(L_{gate}=22 \text{ nm}).$                                                              |

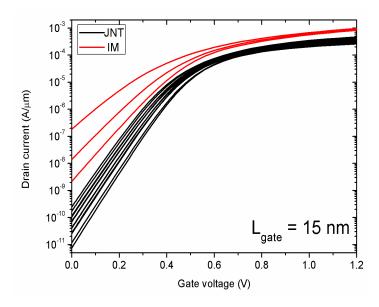

| Figure 5.6 - Comparison of drain current versus gate voltage in JNTs and IM devices      |

| $(L_{gate}=15 \text{ nm})$                                                               |

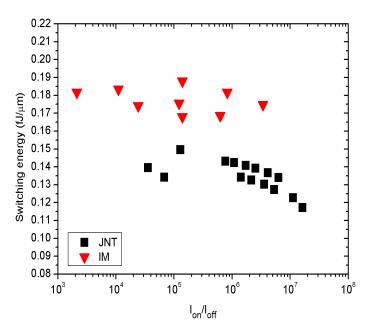

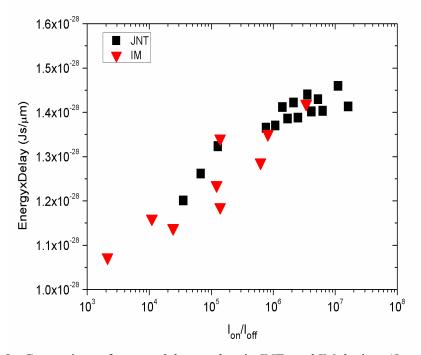

| Figure 5.7 - Comparison of switching energy in JNTs and IM devices ( $L_{gate}$ =15 nm). |

| Figure 5.8 - Comparison of energy-delay product in JNTs and IM devices ( $L_{gate}$ =15  |

| nm)                                                                                      |

| Figure 5.9 - 3D schematic of AM and junctionless GAA nanowire transistors 80             |

| Figure 5.10 - Longitudinal cross-section view of junctionless GAA nanowire               |

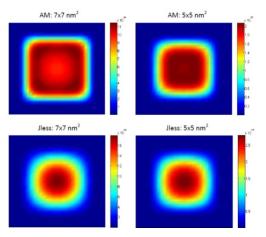

| transistor (top) and AM GAA nanowire transistor (bottom) used in this work80             |

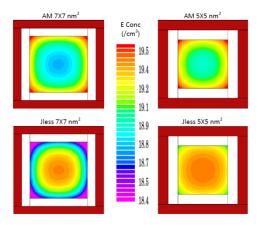

| Figure 5.11 - Electron density at the middle of junctionless and AM devices for          |

| different cross-section dimensions (quantum simulations)                                 |

| Figure 5.12 - Electron density at the middle of junctionless and AM devices for                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| different cross-section dimensions (classical simulations)                                                                                 |

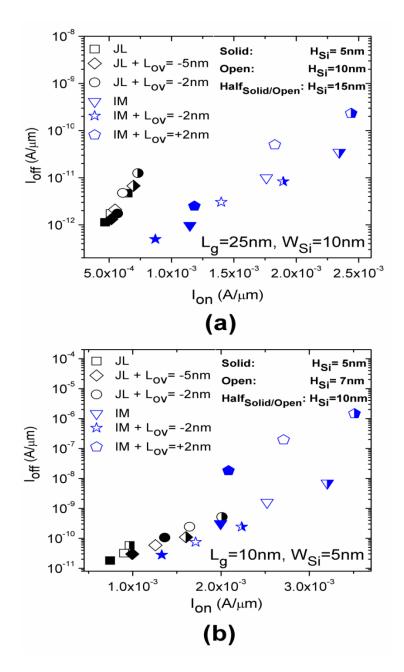

| Figure 5.13 - $I_{off}$ - $I_{on}$ plots of JNTs and IM devices for (a) $L_{gate}$ =25 nm and (b)                                          |

| $L_{gate}$ =10 nm. The nanowire pitch is equal to $2 \times W_{Si}$ , such that the current in A/ $\mu$ m is                               |

| equal to the current in a single nanowire times $1000/(2 \times W_{Si})$ . $I_{on}$ is extracted at                                        |

| $V_{gs}=V_{ds}=1\mathrm{V}$ while $I_{off}$ is extracted at $V_{gs}=0\mathrm{V}$ and $V_{ds}=1\mathrm{V}$ . ( $L_{ov}$ is the gate overlap |

| with the source and drain contact regions as shown in Figure 5.1)84                                                                        |

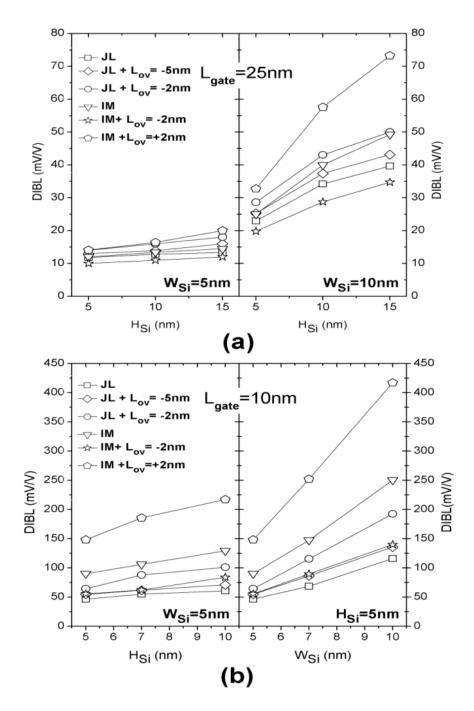

| Figure 5.14 - DIBL in JNTs and IM devices for (a) $L_{gate}$ =25 nm (b) $L_{gate}$ =10 nm.                                                 |

| DIBL is measured by the lateral shift of the transfer curves in the subthreshold                                                           |

| regime between $V_{ds}$ =50 mV and $V_{ds}$ =1V divided by the drain voltage difference of                                                 |

| the two curves (0.95V).                                                                                                                    |

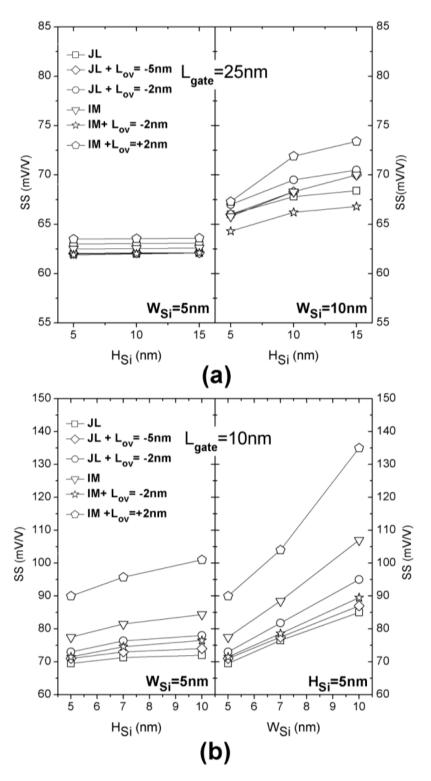

| Figure 5.15 - Subthreshold swing of junctionless and IM devices for (a) $L_{\it gate}$ =25 nm                                              |

| (b) $L_{gate} = 10 \text{ nm}$ 87                                                                                                          |

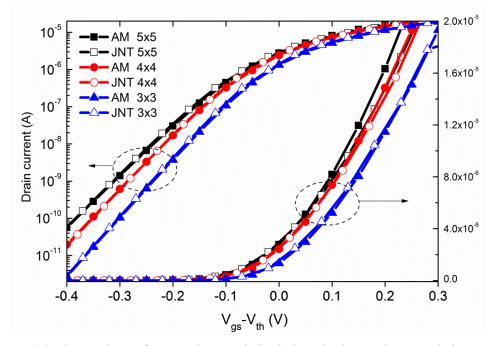

| Figure 5.16 - Comparison of $I_{ds}$ - $V_{gs}$ characteristics in junctionless and accumulation-                                          |

| mode GAA nanowire transistors for different cross-section dimensions ( $V_{ds}$ =0.4V).                                                    |

| 89                                                                                                                                         |

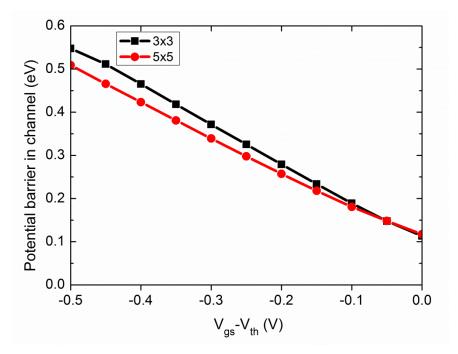

| Figure 5.17 - Potential barrier in the channel of the junctionless GAA nanowire                                                            |

| transistor for different cross-section dimensions in the subthreshold region90                                                             |

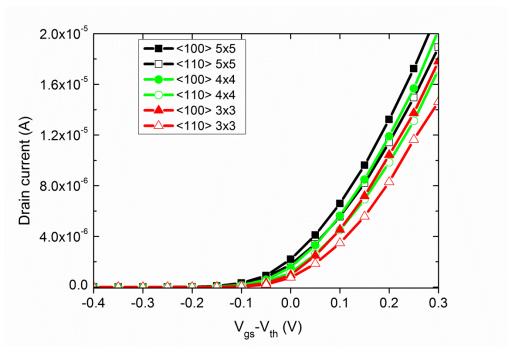

| Figure 5.18 - I-V characteristics of junctionless GAA nanowire transistors for <100>                                                       |

| and <110>channels (wafer orientation is (010), $V_{ds}$ =0.4V)91                                                                           |

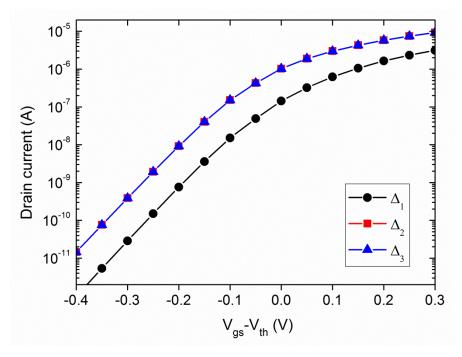

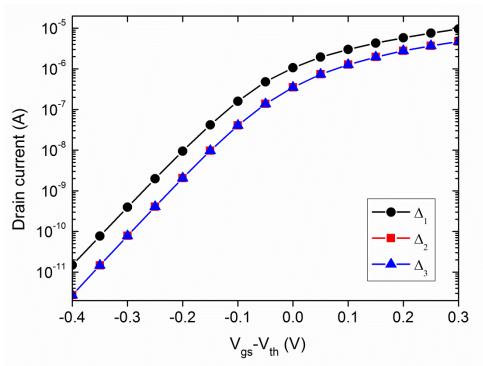

| Figure 5.19 - Contribution of different $\Delta$ valleys in total current of junctionless GAA                                              |

| nanowire transistor with cross-section of $5\times5$ nm <sup>2</sup> and <100>-oriented wire                                               |

| $(V_{ds}=0.4\text{V}, \text{ wafer orientation is } (010)).$                                                                               |

| Figure 5.20 - Contribution of different $\Delta$ valleys in total current of junctionless GAA                                              |

| nanowire transistor with cross-section of 5×5 nm <sup>2</sup> and <110>-oriented wire                                                      |

| $(V_{ds}=0.4V, \text{ wafer orientation is } (010)).$                                                                                      |

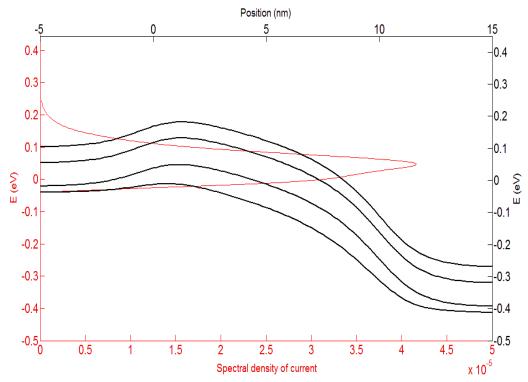

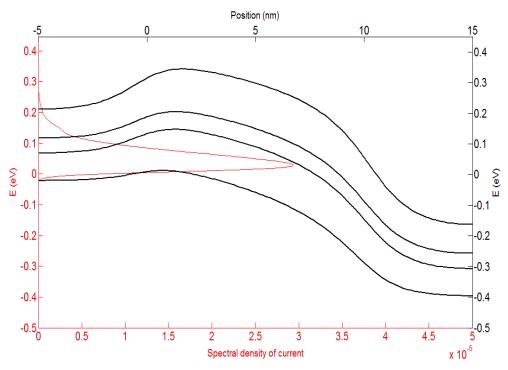

| Figure 5.21 - Four lowest conduction subbands (black) and spectral density of                                                              |

| current (red) at $V_{gs}$ - $V_{th}$ =0.3V for $\Delta_2$ and $\Delta_3$ valleys of <100> oriented junctionless                            |

| nanowire transistor. Wafer orientation is (010), $V_{ds}$ =0.4V, cross-section is 5×5 nm <sup>2</sup> ).                                   |

| 93                                                                                                                                         |

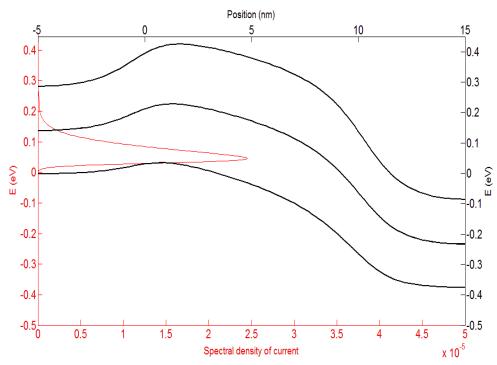

| Figure 5.22 - Four lowest conduction (black) and spectral density of current (red) at                                                      |

| $V_{gs}$ - $V_{th}$ =0.3V for $\Delta_1$ valley of <100> oriented junctionless nanowire transistor.                                        |

| Wafer orientation is (010), $V_{ds}$ =0.4V, cross-section is 5×5 nm <sup>2</sup> 94                                                        |

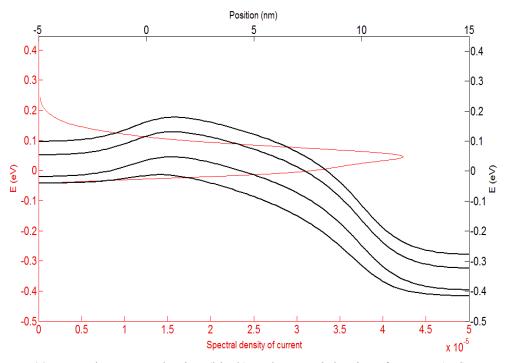

| Figure 5.23 - Four lowest conduction (black) and spectral density of current (red) at                           |

|-----------------------------------------------------------------------------------------------------------------|

| $V_{gs}$ - $V_{th}$ =0.3V for $\Delta_1$ valley of <110> oriented junctionless nanowire transistor.             |

| Wafer orientation is (010), $V_{ds}$ =0.4V, cross-section is 5×5 nm <sup>2</sup> 94                             |

| Figure 5.24 - Four lowest conduction subbands (black) and spectral density of                                   |

| current (red) at $V_{gs}$ - $V_{th}$ =0.3V for $\Delta_2$ and $\Delta_3$ valleys of <110> oriented junctionless |

| nanowire transistor Wafer orientation is (010), $V_{ds}$ =0.4V, cross-section is 5×5 nm <sup>2</sup> .95        |

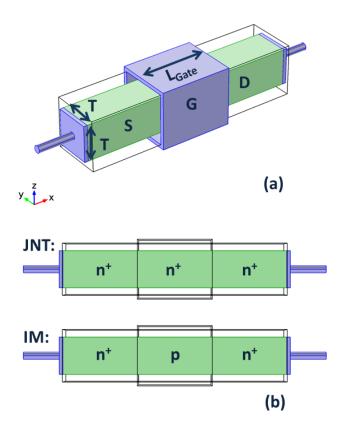

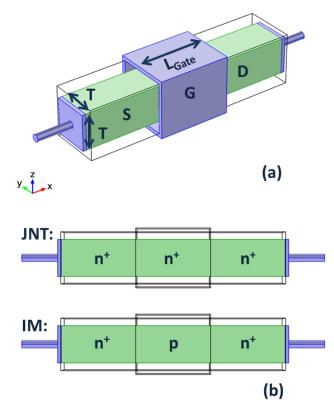

| Figure 6.6.1 - (a) Bird eye's view of a gate-all-around nanowire transistor and (b)                             |

| doping profile in the longitudinal direction in junctionless and inversion-mode                                 |

| devices                                                                                                         |

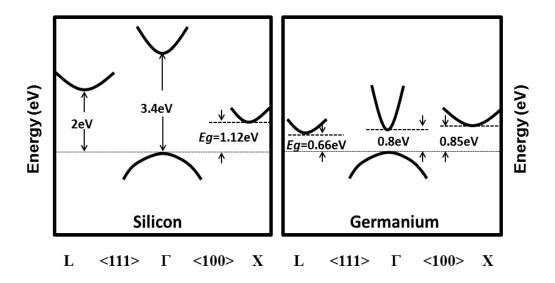

| Figure 6.6.2 - The values of direct and indirect gaps of Si and Ge devices (at                                  |

| Temp=300K) used in our simulations                                                                              |

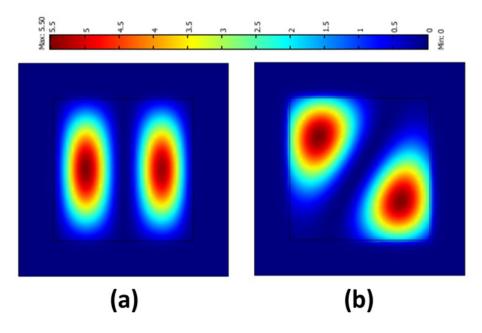

| Figure 6.3 - Square modulus of the 2nd wavefunctions of the (a) X-valley and (b) L-                             |

| valley of a Ge nanowire                                                                                         |

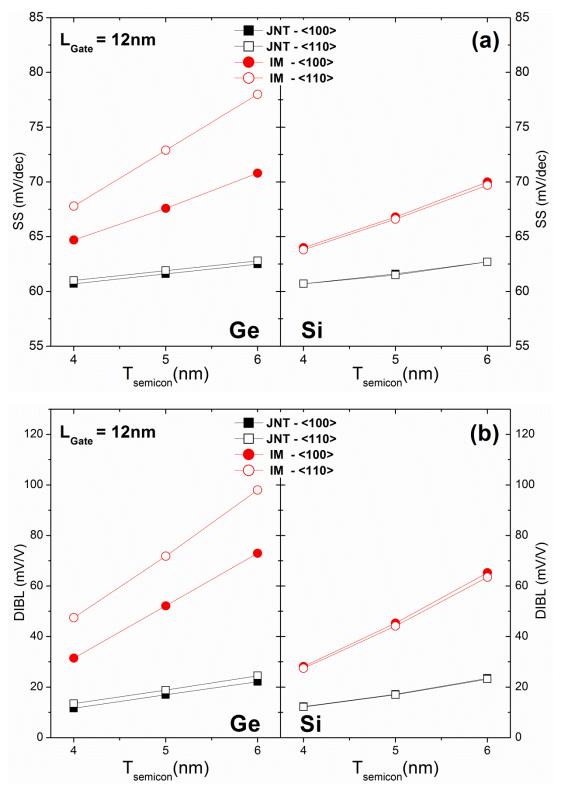

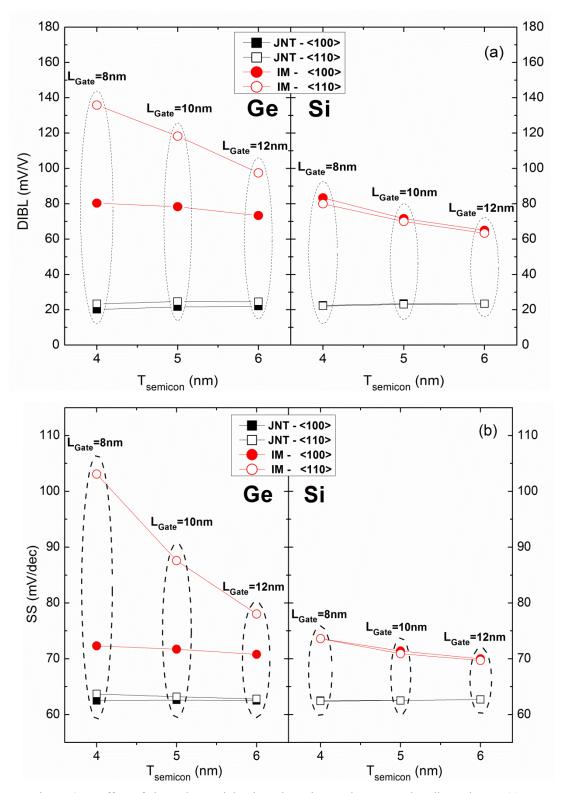

| Figure 6.4 - (a) Subthreshold swing and (b) DIBL in junctionless nanowire                                       |

| transistors and inversion-mode devices for germanium and silicon nanowire                                       |

| channels                                                                                                        |

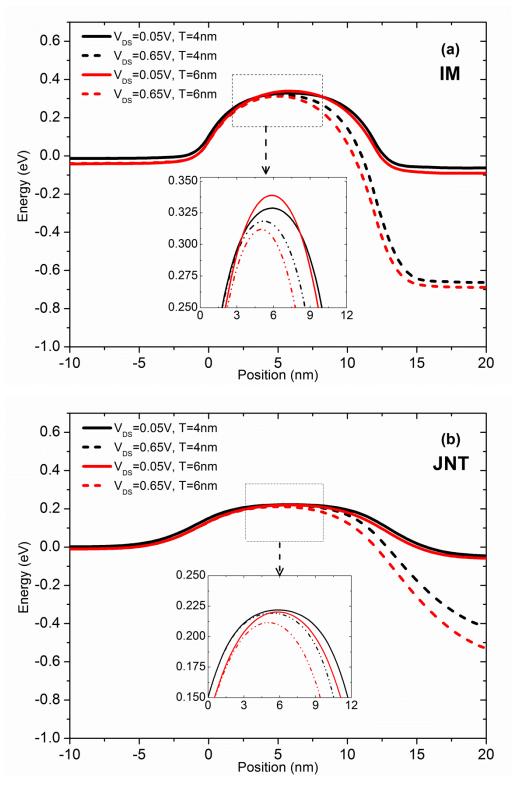

| Figure 6.5 - Source-channel potential barrier of <100>-oriented silicon nanowires in                            |

| (a) inversion-mode devices and (b) junctionless nanowire transistors. ( $L_{gate}$ =12 nm).                     |

|                                                                                                                 |

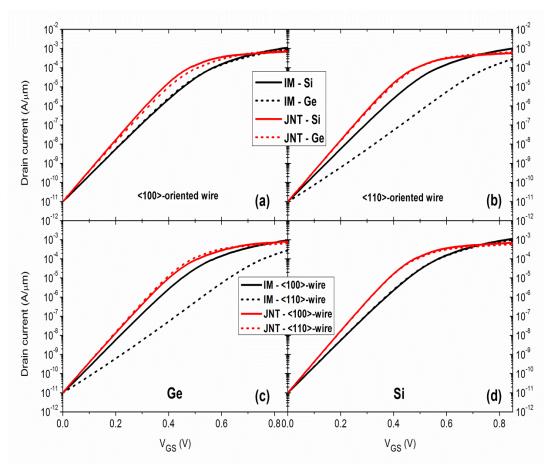

| Figure 6.6 - Comparison of transfer characteristics for (a) <100>-wire orientation,                             |

| (b) <110>-wire orientation and different channel material (c and d) in junctionless                             |

| nanowire transistors and inversion-mode devices. ( $L_{gate}$ =10 nm, $T_{semicon}$ =5 nm,                      |

| $V_{DS}$ =0.65V)                                                                                                |

| Figure 6.7 - Effect of channel material, wire orientation, and cross-section dimension                          |

| on (a) DIBL and (b) subthreshold swing in junctionless nanowire transistors and                                 |

| inversion-mode devices                                                                                          |

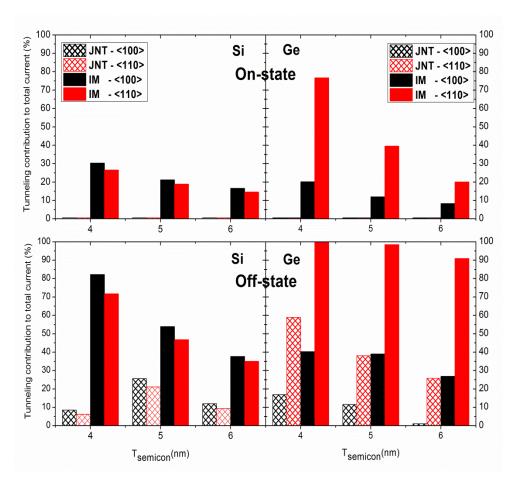

| Figure 6.8 - The source-to-drain tunneling current contribution to the total current in                         |

| the off- and the on-state regime for Si and Ge nanowires                                                        |

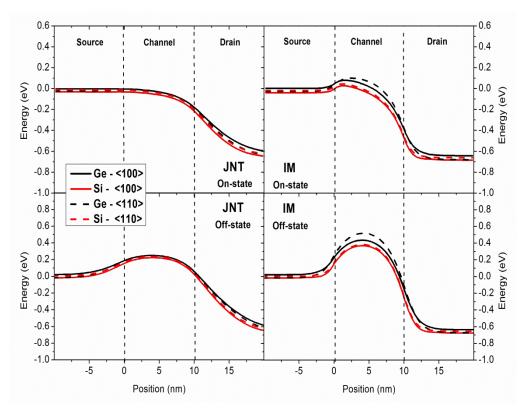

| Figure 6.9 - The first subband profile of junctionless nanowire transistors and                                 |

| inversion-mode devices in both off-state and on-state regime for silicon and                                    |

| germanium nanowire transistors and different wire orientations. ( $L_{gate}$ =10 nm,                            |

| $T_{semicond}$ =5 nm).                                                                                          |

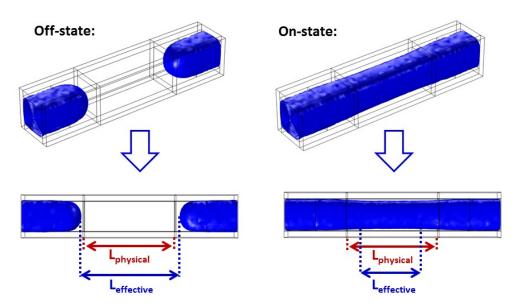

| Figure 6.10 - Effective gate length variation from the off-state to the on-state in a |

|---------------------------------------------------------------------------------------|

| junctionless nanowire transistor using the plot of charge carrier concentration. (The |

| depleted region is transparent and the dark areas are neutral)                        |

| Figure 7.1 - (a) Bird eye's view of a gate-all-around nanowire MOSFET and (b)         |

| doping profile in the longitudinal direction in junctionless nanowire transistors and |

| inversion-mode devices                                                                |

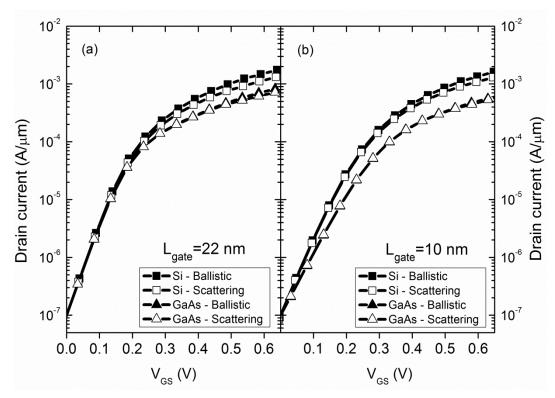

| Figure 7.2 - Transfer characteristics of Si and GaAs channels with gate length (a) 22 |

| nm and (b) 10 nm. A comparison between ballistic transport and transport including    |

| electron-phonon scattering is shown                                                   |

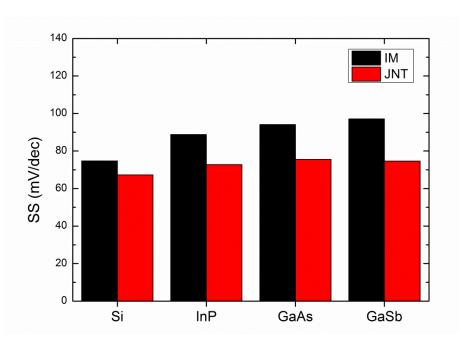

| Figure 7.3 -Subthreshold swing in IM and junctionless nanowire transistors made of    |

| Si and III-V compound semiconductors                                                  |

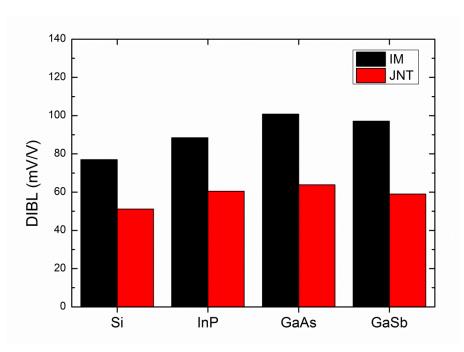

| Figure 7.4 - Comparison of DIBL in IM and junctionless nanowire transistors made      |

| of Si and III-V compound semiconductors (DIBL is defined as ( $Vth VDS$ =             |

| 0.05V - Vth VDS = 0.65V)/(0.65 - 0.05)                                                |

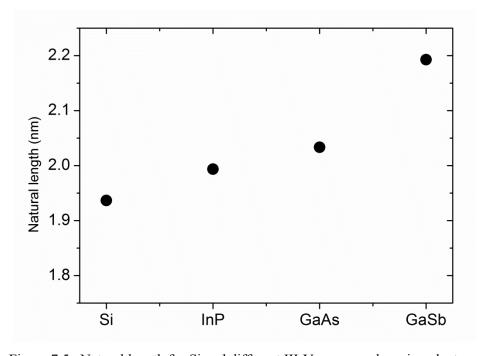

| Figure 7.5 -Natural length for Si and different III-V compound semiconductors125      |

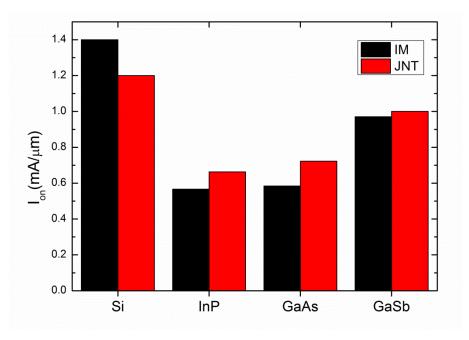

| Figure 7.6 - On current of different III-V nanowires compared to silicon nanowire     |

| with the same physical parameters ( $I_{on}$ extracted at $V_{GS}$ =0.65V)126         |

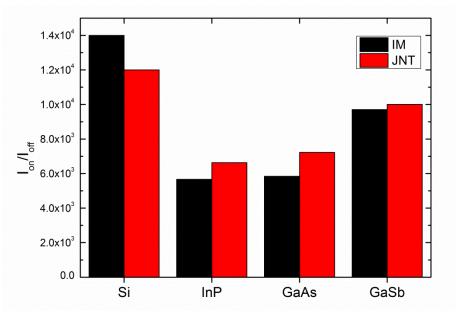

| Figure 7.7 - On-to-off current ratio of different III-V nanowires compared to silicon |

| nanowire with the same physical parameters126                                         |

|                                                                                       |

# **List of Tables**

| Table 2.1- Comparison of different 3D NEGF methods.                                                          |

|--------------------------------------------------------------------------------------------------------------|

| Table 3.1 - The acoustic phonon scattering rate (X and L reperesnts the related                              |

| values for X and L valleys)                                                                                  |

| Table 3.2 - The coupling constants and phonon energies for the X-X intervalley                               |

| scattering rate                                                                                              |

| Table 3.3 - The coupling constant and phonon energy for the L-L intervalley                                  |

| scattering rate                                                                                              |

| Table 5.1 - Switching time (ps) calculated by classical simulator at $V_{gs}=V_{th}+0.2$ (V).                |

| Table 5.2 - Switching time (ps) calculated by quantum simulator at Vgs=Vth+0.2                               |

| (V)                                                                                                          |

| Table 5.3 - Comparison of subthreshold swing and DIBL in junctionless and AM                                 |

| GAA nanowire transistors for different cross-sections. ( $L_{gate} = 10 \text{ nm}$ )90                      |

| Table 5.4 - Effective masses and subband degeneracies of $\Delta$ valleys for two                            |

| important semiconductor nanowire orientations. (Wafer orientation is (010), $m_0$ is                         |

| free electron mass)                                                                                          |

| Table 6.1 - General expressions of effective masses and subband degeneracy for                               |

| <100>- and <110>- oriented semiconductor nanowires on the (010)-oriented wafer.                              |

|                                                                                                              |

| Table 6.2 - Values of transverse and longitudinal effective masses for the X- and L-                         |

| valleys in bulk Si and Ge which have been used in our simulations                                            |

| Table 7.1 – Material properties for III-V compound semiconductors. (Eg $\Gamma$ is the                       |

| bandgap, $\Delta E_L$ and $\Delta E_X$ are the L- and X- valley band-offsets from the $\Gamma$ -valley, and  |

| $m_t$ , $m_l$ , and $m_\Gamma$ are transverse, longitudinal and isotropic $\Gamma$ -valley effective masses, |

| respectively; and $m_0$ is the free electron mass)                                                           |

| Table 7.2 - Material properties for Si. (EgX is the bandgap, $\Delta E_L$ is the L-valley band-              |

| offset from the X-valley, and $m_t$ , $m_l$ , and $m_\Gamma$ are transverse, longitudinal and isotropic      |

| $\Gamma$ -valley effective masses, respectively; and $m_0$ is the free electron mass)                        |

# **Chapter 1: Introduction**

#### 1.1. Scaling of CMOS technology

Electronics products and their related services hold considerable a share of today's world economy. Since the concept of an integrated circuit (IC) was introduced by J. Kilby in 1958, the number of electronic components on a microchip has increased exponentially with time while the performance of transistors on a microchip has also been improved. In 1965 Gordon Moore predicted that the number of transistors on a chip would be doubled every 18 month, which has been valid for the past four decades. However, conventional MOSFET structures are reaching scaling limits and short-channel effects (SCEs) have become a huge problem for end-of-the-roadmap technologies. In an ideal MOSFET the channel potential is controlled by the gate electrode only, however, in devices with a very short channel length the drain potential can significantly influence the channel potential and degrade the control of the gate on the channel potential. This causes the short-channel effects that degrade the device performance. This degradation includes the drain-induced barrier lowering (DIBL), increased off-state leakage current ( $I_{off}$ ) and subthreshold swing (SS), and the threshold voltage roll-off. These short-channel effects can jeopardize CMOS scaling. Decreasing the gate oxide thickness and the source/drain junction depth while decreasing the gate length, has been used to minimize these shortchannel effects in conventional bulk MOSFETs. However, scaling of the SiO<sub>2</sub> gate oxide reached a physical limitation at around ~2nm due to the increased gate leakage current caused by the tunneling through the oxide. For this reason higher permittivity materials were proposed to be used as gate dielectrics. These allow further reduction of the equivalent oxide thickness (EOT) while using a physically thicker oxide. This helps to prevent the gate tunneling and allows for further scaling of MOSFETs. Nevertheless, shrinking MOSFETs to the sub-10nm regime can lead to a huge direct tunneling between source and drain which degrades the subthreshold swing, increases the leakage current and limits further scaling due to a huge increase of power dissipation. These are some of the serious challenges for the scaling of nanotransistors.

#### 1.2. Advanced CMOS technology

Silicon-on-Insulator (SOI) technology is able to solve some of the physical limits of bulk CMOS [1-3]. In SOI technology, transistors are made in a thin silicon layer sitting on top of a silicon dioxide layer. SOI technology is being used in many major semiconductor companies such as IBM, AMD and ST Microelectronics. SOI technology can push CMOS scaling beyond the limits of classical silicon devices [4-6].

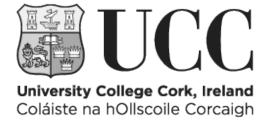

A schematic view of the bulk and SOI multi-gate FET, as well as, the cross-section of different multi-gate FET (MuGFET) structures and their effective number of gates are shown in Figure 1.1 [7-12].

Figure 1.1 – Schematic of (a) bulk and SOI multi-gate FETS, as well as, (b) cross-section of different multi-gate FETS and their corresponding effective number of gates.

The small silicon thickness of an SOI MOSFET can effectively suppress the leakage current compared to the conventional bulk MOSFET. This is done by eliminating the part of the channel region that cannot be effectively controlled by the gate. However, this may not be practical for very short devices as the channel thickness of a planar single gate SOI MOSFET needs to be ultra-thin  $(T_{si}/4 < L_{gate})$  to suppress SCEs. But increasing the number of gates can increase the gate control

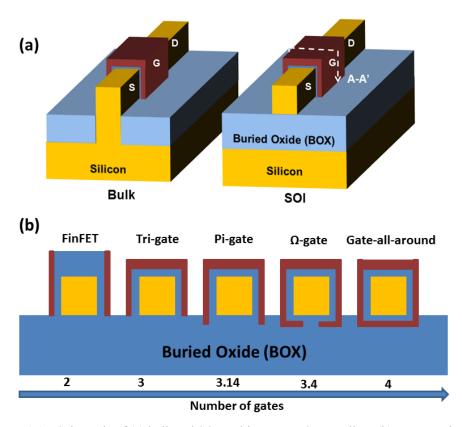

ability and relax the body thickness. In multiple-gate devices, the gate electrode is wrapped around a silicon wire to increase the gate control ability of the channel carriers. According to the International Technology Roadmap for Semiconductor (ITRS) the multiple-gate SOI MOSFETs can be scaled to sub-10nm dimensions and are promising candidates for future nanoelectronic devices (Figure 1.2 [13]).

Figure 1.2 - Evaluation of potential solutions for logic CMOS [Source: ITRS Edition 2011].

#### 1.3. New type of MOSFET

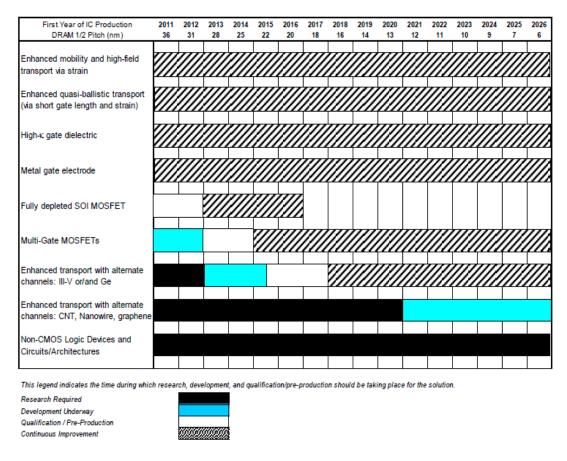

Conventional Metal Oxide Semiconductor (MOS) transistors are made of two PN junctions (the source-channel junction and the drain-channel junction). For example, the n-channel MOSFET has an N-P-N structure while the p-channel device has a P-N-P structure. To make faster and smaller devices for the electronic industry, scaling transistors down to the nano-scale regime is necessary. This scaling raises significant manufacturing challenges for semiconductor companies. Forming source/drain junctions in classical MOSFETs with very short channel length is very challenging because of the diffusion of source and drain dopant atoms in to the channel area of

these transistors, as shown in Figure 1.3. The diffusion of source and drain dopant atoms into the channel region becomes a bottleneck to the fabrication of transistors with very short channels, and as a result very low thermal budget processing techniques need to be used [14]. However, even with minimizing the diffusion of source/drain dopants to the channel region using of very costly techniques, the statistical variation of the impurity concentration caused by ion implantation or other doping techniques can cause variation of device parameters which is a problem.

Figure 1.3 - Source and drain doping of inversion-mode and junctionless transistor with short channel and ultra-short channel.

Julius Edgar Lilienfeld introduced the first transistor in 1925 [15]. His field-effect device was very similar to the modern metal-oxide-semiconductor devices. It consisted of a thin semiconductor film deposited on a thin insulator layer, which on itself was deposited a metal electrode. The metal electrode acted as the gate of the device. It worked pretty similar to the modern MOSFET. The current flew in the resistor between two contact electrodes. The Lilienfeld device was a simple resistor that used a gate voltage to deplete the semiconductor film from carriers and modulate its conductivity. His transistor, unlike all other types of transistors, did not have any junction. A transistor is a solid-state active device that controls current flow, and the word "transistor" derives from "trans-resistor". The Lilienfeld transistor was, technically, a gated resistor; its gate controlled the carrier density and the current flow. It is the simplest and first patented transistor structure, but it was never successfully fabricated.

As explained earlier, MuGFETs have an excellent gate-to-channel coupling and allow full depletion of the channel region even if it is heavily doped. The junctionless devices studied in this thesis do not need the formation of extremely abrupt source and drain junctions. The doping type and concentration in the channel region is equal to that in the source and drain regions, or at least to that in the source and drain extensions. This decreases the complexity and cost of the fabrication processes.

#### 1.4. Semiconductor device modeling

As we discussed earlier rapid shrinking of semiconductor devices has increased the cost and complexity of the fabrication processes. Due to this fact, the optimization of these devices by trial and error methods is not economical. Computers are much cheaper resources and can be used for device modeling. Device modeling allows evaluation of device performance before their manufacturing as well as better understanding of device behavior using the simulation results of phenomena that cannot be readily measured. Using simulation software, carrier transport in semiconductor devices can be modeled at different levels of sophistication. A pure semi-classical treatment is appropriate for devices with large dimensions while for ultra-small devices, quantum treatment needs to be employed. For example, for devices with very small dimensions where the active channel is smaller than 25 nm, the semi-classical approach may lose its validity. The semiclassical models (such as drift-diffusion, energy balance, hydrodynamic, etc.) which are most widely used in TCAD software to model carrier transport are derived from the solution of the Boltzmann Transport Equation (BTE). However, the BTE is not valid for devices with dimensions below the De Broglie wavelength. Some of the well-known methods which have been proposed to model carrier transport in semiconductor devices using the Schrödinger equation are Wigner transformations, Density Matrix approach and non-equilibrium Green's function technique [16-23]. These approaches are technically equivalent. However, their detailed methodology regarding the inclusion of the various quantum effects is different. The nonequilibrium Green's function (NEGF) formalism has been well established in the past decades and has a great numerical stability. It has been used extensively to model quantum transport in single and multiple-gate MOSFETs. Using NEGF, different

types of scattering can be included in the carrier transport of the semiconductor devices. Therefore, we choose this method as base of our 3D numerical simulation tool. Figure 1.4 shows the diagram of some of the widely used semi-classical and quantum models [24-26].

Figure 1.4 – Diagram of some of the widely used semi-classical and quantum transport models.

#### 1.5. Thesis organization

In this thesis we study the performance of different types of nano-scale multiplegate nanowire devices. To simulate devices with large dimensions, we use commercial TCAD software (Silvaco-TCAD and Synopsys-TCAD). We have also developed a three-dimensional quantum mechanical simulator based on the NEGF formalism and the effective mass approximation using MATLAB and COMSOL Multiphysics softwares to study the performance of different semiconductor (such as Silicon, Germanium and III-V materials) nanowire transistors in either the ballistic regime or in the presence of electron-phonon scattering. Chapter 2 introduces the quantum mechanical models which have been used in this thesis for the simulation of semiconductor devices with advanced device structures. Chapter 3 describes the principles and methods we have used to develop our 3D quantum-mechanical simulator which are based on non-equilibrium Green's functions. Chapter 4 presents the various electron-phonon scattering mechanisms in the framework of the NEGF formalism. In chapters 5-7, we present our simulation results on the investigation of the electrical performance in different Si, Ge, and III-V nanowire transistors. The influence of channel material on the performance of Si, Ge, III-V nanowire MOSFETs is studied and a comparison of the junctionless nanowire transistor versus

inversion-mode and accumulation nanowire transistors is presented. Finally, in chapter 8 conclusions are drawn and directions for the future research are suggested.

#### References

- [1] H. S. P. Wong, "Beyond the conventional transistor," *Solid-State Electronics*, vol. 49, pp. 755-762, May 2005.

- [2] S. Cristoloveanu, "Silicon on insulator technologies and devices: from present to future," *Solid-State Electronics*, vol. 45, pp. 1403-1411, 2001.

- [3] S. Cristoloveanu, "Future trends in SOI technologies," *Journal of the Korean Physical Society*, vol. 39, pp. S52-S55, Dec 2001.

- [4] R. H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: from bulk to SOI to bulk," *Electron Devices, IEEE Transactions on*, vol. 39, pp. 1704-1710, 1992.

- [5] S. R. N. Yun, W. S. Park, B. H. Lee, and J. T. Park, "Hot electron induced punchthrough voltage of p-channel SOI MOSFET's at room and elevated temperatures," *Microelectronics Reliability*, vol. 43, pp. 1477-1482, Sep-Nov 2003.

- [6] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFET's," *Electron Device Letters, IEEE*, vol. 18, pp. 74-76, 1997.

- [7] B. S. Doyle, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, *et al.*, "High performance fully-depleted tri-gate CMOS transistors," *Electron Device Letters, IEEE*, vol. 24, pp. 263-265, 2003.

- [8] P. Jong-Tae and J.-P. Colinge, "Multiple-gate SOI MOSFETs: device design guidelines," *Electron Devices, IEEE Transactions on*, vol. 49, pp. 2222-2229, 2002.

- [9] P. Jong-Tae, J.-P. Colinge, and C. H. Diaz, "Pi-Gate SOI MOSFET," *Electron Device Letters, IEEE*, vol. 22, pp. 405-406, 2001.

- [10] J. T. Park, C. A. Colinge, and J.-P. Colinge, "Comparison of gate structures for short-channel SOI MOSFETs," in *SOI Conference*, 2001 IEEE International, 2001, pp. 115-116.

- [11] Y. Fu-Liang, C. Hao-Yu, C. Fang-Cheng, H. Cheng-Chuan, C. Chang-Yun, C. Hsien-Kuang, et al., "25 nm CMOS Omega FETs," in *Electron Devices Meeting*, 2002. *IEDM '02. Digest. International*, 2002, pp. 255-258.

- [12] J.-P. Colinge, M. H. Gao, A. Romano-Rodriguez, H. Maes, and C. Claeys, "Silicon-on-insulator `gate-all-around device'," in *Electron Devices Meeting*, 1990. *IEDM* '90. Technical Digest., International, 1990, pp. 595-598.

- [13] <a href="http://public.itrs.net/">http://public.itrs.net/</a>.

- [14] S. H. Jain, P. B. Griffin, J. D. Plummer, S. McCoy, J. Gelpey, T. Selinger, *et al.*, "Low resistance, low-leakage ultrashallow p+ junction formation using millisecond flash anneals," *Electron Devices, IEEE Transactions on*, vol. 52, pp. 1610-1615, 2005.

- [15] J. E. Lilienfeld, "Method and apparatus for controlling electric current," US patent, 1,745,175 Patent, 1925.

- [16] S. Barraud, "Phase-coherent quantum transport in silicon nanowires based on Wigner transport equation: Comparison with the nonequilibrium-Green-function formalism," *Journal of Applied Physics*, vol. 106, 2009.

- [17] D. K. Blanks, G. Klimeck, R. Lake, D. Jovanovic, R. C. Bowen, C. Fernando, *et al.*, "NEMO: general release of a new comprehensive quantum device

- simulator," in *Compound Semiconductors, 1997 IEEE International Symposium on*, 1998, pp. 639-642.

- [18] G. Klimeck, R. Lake, M. J. Maclennan, and S. Datta, "QUEST user's manual," Technical Report TR-EE 93-17, Purdue University1993.

- [19] D. K. Ferry and H. L. Grubin, *Modeling of quantum transport in semiconductor devices*. Arizona State University, Tempe, AZ, 1994.

- [20] P. Bordone, M. Pascoli, R. Brunetti, A. Bertoni, C. Jacoboni, and A. Abramo, "Quantum transport of electrons in open nanostructures with the Wigner-function formalism," *Physical Review B*, vol. 59, pp. 3060-3069, Jan 15 1999.

- [21] M. V. Fischetti, "Master-equation approach to the study of electronic transport in small semiconductor devices," *Physical Review B*, vol. 59, pp. 4901-4917, Feb 15 1999.

- [22] R. Lake and S. Datta, "Nonequilibrium Green's-function method applied to double-barrier resonant-tunneling diodes," *Physical Review B*, vol. 45, p. 6670, 1992.

- [23] A. Svizhenko, M. P. Anantram, T. R. Govindan, B. Biegel, and R. Venugopal, "Two-dimensional quantum mechanical modeling of nanotransistors," *Journal of Applied Physics*, vol. 91, pp. 2343-2354, 2002.

- [24] A. Gehring and S. Selberherr, "Evolution of current transport models for engineering applications," in *Computational Electronics*, 2004. *IWCE-10* 2004. *Abstracts*. *10th International Workshop on*, 2004, pp. 20-21.

- [25] S. Jin, "Modeling of Quantum Transport in Nano-Scale MOSFET Devices," PhD, Seoul National University, Seoul, 2006.

- [26] M. Pourfath, "Numerical Study of Quantum Transport in Carbon Nanotube-Based Trabsistors," PhD, Institute for Microelectronics, Vienna University of Technology, Vienna, 2007.

# Chapter 2: Semi-classical and quantum transport in n-channel MOSFETS

#### 2.1. Introduction

Rapid shrinking of semiconductor feature sizes into the nanoscale regime, leads to complicated device behavior due to the occurrence of new physical phenomena at short dimensions and requires deeper understanding of actual operation of ultrascaled devices [1]. Moreover, the fabrication process becomes more complicated and time-consuming for devices at the nanoscale regime [2]. Due to this fact, optimizing these devices by pure trial-and-error methods is not economical and has to be done by other means. Technology computer-aided design (TCAD) offers both device and process simulation which can be used to model semiconductor device operation and fabrication, respectively. Using device simulation one can simulate the charge carrier transport and its related electrical behavior of semiconductor devices while using process simulation one can simulate physical processes such as material growth, oxidation, ion implantation, dopant diffusion, etching and metal deposition in device fabrication.

The important goal of using device simulation tools is to capture the necessary physics needed to evaluate accurate device operation and at the same time minimize the computational time and cost. Semiconductor device simulation can be done by solving self-consistently the transport equations that govern charge flow and the equations of the fields that drive charge flow. These equations are coupled, hence simultaneous solution is required [2]. From the solution of Maxwell's equations, the fields arising from external sources, as well as charge and current densities can be obtained. In the absence of a changing magnetic field, only the electric fields arising from the solution of the Poisson's equation are required. At larger scales (devices down to 0.5um) the electrical characteristics of semiconductor devices can be estimated solving the drift-diffusion (DD) equations numerically. Scharfetter and Gummel proposed a very robust discretization of the DD equations for numerical simulation of carrier transport in semiconductor devices which is still used [3].

However, shrinking of semiconductor devices to the submicron regime required the refinement and extension of transport models to capture the physical phenomena that occur in small-dimensions. The supply voltages cannot be scaled accordingly due to loss of circuit performance. As a result, the electric field inside these devices has increased, generating hot-carrier and non-local effects. These effects can dominate device performance of small-scale devices. To overcome the limitations of the DD model, many extensions have been proposed. These extensions consider an additional balance equation for the average carrier energy and add a driving term to the current expression. This additional term is proportional to the gradient of the carrier temperature [4]. Many of these models exist and hydrodynamic and energybalance models are two of the most famous ones. However, these models do not have the capability to accurately simulate ultra-small devices. For these devices, the quantum simulation of carrier transport becomes necessary since the charge-carrier DeBroglie wavelength is comparable to scaled device features. Some of these quantum models are as follows. The quantum hydrodynamic model keeps all classical hydrodynamic features but adds some quantum corrections. The quantumkinetic equation (Wigner-Boltzmann) is accurate up to a single particle description. The Green's functions include correlations in both space and time domain and can accommodate many-body effects. Finally, one could attempt the direct solution of the Schrödinger equation which can be performed only for small number of particles. Indeed, the simulation of ultra-scaled devices suffers from several computational challenges such as the necessity to solve both the carrier transport and Poisson's equations for the full 3D domain. Very efficient algorithms, multi-processor platforms, and the appropriate level of approximation are essential to capture the necessary transport physics for the description of future technologies.

#### 2.2. Semi-classical transport

#### 2.2.1 Drift-Diffusion simulations

The Boltzmann transport equation has been widely used to describe the transport properties of materials semi-classically [5]. However, combining the direct solution of the Boltzmann equation with field solvers for device simulation is computationally expensive. Therefore, another model based on the solution of the

so-called drift-diffusion equations is dominant for traditional semiconductor simulations. The drift-diffusion equations are local in terms of the driving forces. The DD model is based on the following set of equations [2]:

Current equations:

$$J_n = qn\mu_n E + qD_n \nabla n 2.1$$

$$J_p = qn\mu_p E - qD_p \nabla p 2.2$$

$D_n$  and  $D_p$  are the diffusion constants.

Continuity equations (which are the conservation laws for the carriers):

$$\frac{dn}{dt} = \frac{1}{q} \nabla J_n + U_n \tag{2.3}$$

$$\frac{dp}{dt} = -\frac{1}{q}\nabla J_p + U_p$$

2.4

$U_n$  and  $U_p$  are the net generation-recombination rates.

Poisson's equation:

$$\nabla \varepsilon. \, \nabla V = -q(p - n + N_D - N_A) \tag{2.5}$$

where p, n are the electron and hole concentration and  $N_D$ ,  $N_A$  are the donor and acceptor impurity concentrations. For the drift-diffusion equations, it is not possible to obtain a solution in one step and a non-linear iteration method is necessary. The two widely used methods are Gummel's iteration [6] and Newton's method [7].

#### 2.2.2 Hydrodynamic simulations

In deeply-scaled semiconductor MOSFETs velocity overshoot can occur which makes the drift-diffusion model invalid. In the HD model the information about average carrier energies is in the form of carrier temperatures. The electron gas is assumed to be in thermal equilibrium with the lattice temperature in the DD model. However, the presence of a strong electric field drives electrons to gain energy and

increase the temperature of the electron gas  $(T_n)$  [2]. The pressure of the electron gas is proportional to  $nK_bT_n$  and the driving force becomes a pressure gradient instead of only the density gradient. As a result, a temperature gradient is added as an additional driving force. We can rewrite the current equation as follows:

$$J_n = qn\mu_n E + qD_n \nabla n + qnD_T \nabla T_n$$

2.6

where  $D_T$  is the thermal diffusivity and  $T_n$  represents the electronic temperature.

#### 2.2.3 Energy-Balance simulations

The energy balance model is another approach with higher order solutions to the general Boltzmann transport equation. It is suitable for simulations of deeply-scaled semiconductor MOSFETs and provides a more accurate description of device physics, especially effects such as velocity overshoot and non-local impact ionization which cannot be captured by the classical DD model. Energy balance models consider coupling of the current density to the carrier temperature, or energy. The current density equations from the DD model are modified to include this additional physical relationship [8].

#### 2.3. Quantum transport

#### 2.3.1 Introduction

Ultra-scaled semiconductor devices have approached the quantum transport regime. To model the quantum transport phenomena one can use the non-equilibrium Green's function (NEGF) formalism. NEGF is a very powerful and useful technique which was introduced at the beginning of the 1960's [9-12]. Using NEGF one can study the time evolution of a many-particle quantum system. NEGF formalism and its mathematical derivation has been discussed extensively and can be easily found in the literature [13-15]; therefore here we do not present the many-body discussion of the NEGF formalism.

The NEGF formalism has become a very popular approach in the development of quantum-mechanical simulators for CMOS nanoscale devices [16-23]. Even within the effective-mass approximation, it allows for the treatment of sophisticated

bandstructure models derived from the atomic level [14, 24-27]. The NEGF formalism has been widely used to simulate quantum ballistic transport (i.e., disregarding energy relaxation processes of charge carriers) in semiconductor devices [28-33] but different types of scattering processes can be treated with various degrees of approximation through the NEGF formalism [23, 25, 30, 34-36].

Also, different numerical methods can be used to simulate 3D quantum transport in the conduction band of semiconductor MOSFETs within the effective mass approximation. Real-space and mode-space approaches are two different methods which can be used [37, 38]. Both real-space and mode-space approaches are able to model electron transport in arbitrary device structures with different shapes. These approaches discretize the Hamiltonian in spatial coordinates. The real-space approach is very general and accurate but it requires huge computational time and resources which is a drawback of this method [28, 38]. On the other hand, the mode-space approach is capable of handling most of the problems of interest as the real-space approach but with reasonable computational efficiency [37, 39, 40].