| Title                | Electrochemical materials for integrated magnetics                                                              |

|----------------------|-----------------------------------------------------------------------------------------------------------------|

| Authors              | Smallwood, Daniel C.                                                                                            |

| Publication date     | 2021-06-23                                                                                                      |

| Original Citation    | Smallwood, D. C. 2021. Electrochemical materials for integrated magnetics. PhD Thesis, University College Cork. |

| Type of publication  | Doctoral thesis                                                                                                 |

| Rights               | © 2021, Daniel C. Smallwood https://creativecommons.org/<br>licenses/by-nc-nd/4.0/                              |

| Download date        | 2024-04-19 03:55:44                                                                                             |

| Item downloaded from | https://hdl.handle.net/10468/11937                                                                              |

# **Electrochemical Materials for Integrated Magnetics**

A thesis submitted for the degree of Doctor of Philosophy (Ph.D.) in Engineering Science by

Daniel C. Smallwood, B.A., B.Sc.

Tyndall National Institute, University College Cork – National University of Ireland, 2021

College of Science, Engineering and Food Science

Department of Engineering Science

Micro & Nano Systems Centre

Electrochemical Materials and Energy & Integrated Magnetics Groups

Head of Department: Dr. Fatima Gunning

Supervisors: Dr. James F. Rohan & Dr. Paul McCloskey

Research supported by Science Foundation Ireland under the ADEPT Project No. 15/IA/3180 "Advanced Integrated Power Magnetics Technology - From Atoms to Systems" for which Prof. Cian O'Mathuna is the Principal Investigator.

Copyright © Daniel C. Smallwood 2021

| To my amazing parents, | loving wife and everyone who has supported me along the way. |

|------------------------|--------------------------------------------------------------|

|                        |                                                              |

|                        |                                                              |

|                        |                                                              |

|                        |                                                              |

|                        |                                                              |

## **Table of Contents**

| Declaration                                                                                                            | i          |

|------------------------------------------------------------------------------------------------------------------------|------------|

| Acknowledgements                                                                                                       | ii         |

| List of Acronyms                                                                                                       | iii        |

| List of Symbols                                                                                                        | vii        |

| List of Figures                                                                                                        | xiii       |

| Chapter 1                                                                                                              | xiii       |

| Chapter 2                                                                                                              | xiii       |

| Chapter 3                                                                                                              | xiv        |

| Chapter 4                                                                                                              | xiv        |

| Chapter 5                                                                                                              | xiv        |

| Chapter 6                                                                                                              | xv         |

| List of Tables                                                                                                         | xvi        |

| Chapter 2                                                                                                              | xvi        |

| Chapter 3                                                                                                              | xvi        |

| Chapter 4                                                                                                              | xvi        |

| Chapter 5                                                                                                              | xvi        |

| Abstract                                                                                                               | xvii       |

| Chapter 1 - Introduction                                                                                               | 1          |

| 1.1. Integrated magnetics for efficient DC-DC conversion with a buck converter                                         | 1          |

| 1.2. Research goals and challenges                                                                                     | 5          |

| 1.3. Thesis scope                                                                                                      | 6          |

| 1.4. References                                                                                                        | 7          |

| Chapter 2 – State-of-the-art: VIAs in 2.5D and 3D advanced packaging architectures, and emerging microinductor devices | MEMS<br>10 |

| 2.1. Introduction                                                                                                      | 10         |

| 2.2. VIA fabrication methods                                                                                           | 16         |

| 2.2.1. Deep reactive ion etching                                                                                       | 16         |

| 2.2.2. Laser ablation                                                                                                  | 20         |

| 2.2.3. Photolithography                                                                                                | 21         |

| 2.2.4. Conclusion                                                                                                      | 28         |

| 2.3. Thick photoresists                                                                                                | 30         |

| 2.4. 3D microinductors with VIAs                                                                                       | 33         |

| 2.5. References                                                                                                        | 36         |

| Chapter 3 – Photoresist VIA Relief Mold Formation                                                                      | 71         |

| 2.1. Abotes of                                                                                                         | 71         |

| 3.2. Introduction                                                                                                                                         | 71  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.3. Results                                                                                                                                              | 76  |

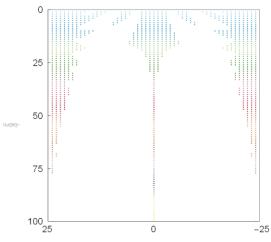

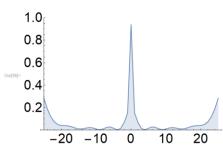

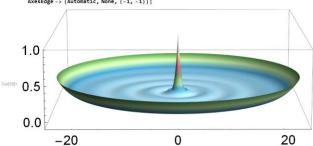

| 3.3.1. Polychromatic light attenuation with a simple new equation                                                                                         | 76  |

| 3.3.2. Advancing methods in photolithography: Depth-selective exposure dose a exposure dose determination                                                 |     |

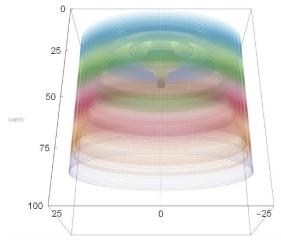

| 3.3.3. Exact, fast scalar diffraction equations for the ultra-near field                                                                                  | 79  |

| 3.3.4. Introducing fast scalar diffraction equations with refraction for aperture occulters in the near field                                             |     |

| 3.3.5. Rapid and accurate latent image calculation with polychromatic exposure diffraction, reflection, refraction and attenuation                        | _   |

| 3.3.6. Validity of near field scalar diffraction equations                                                                                                | 83  |

| 3.3.7. Equation validation: simulations and experiments                                                                                                   | 85  |

| 3.4. Discussion                                                                                                                                           | 89  |

| 3.4.1 Methods for latent image simulations in photolithography with a polychroattenuation equation for fabricating VIAs in 2.5D and 3D advanced packaging | 0   |

| architectures                                                                                                                                             |     |

| 3.4.2 Wet etching in photolithography: Development                                                                                                        |     |

| 3.4.3. Future work                                                                                                                                        |     |

| 3.5. Materials and methods                                                                                                                                |     |

| 3.6. References                                                                                                                                           |     |

| Chapter 4 - VIA Electroplating: Metallization in 3D Photoresist Relief Structures                                                                         |     |

| 4.1. Introduction                                                                                                                                         |     |

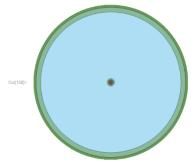

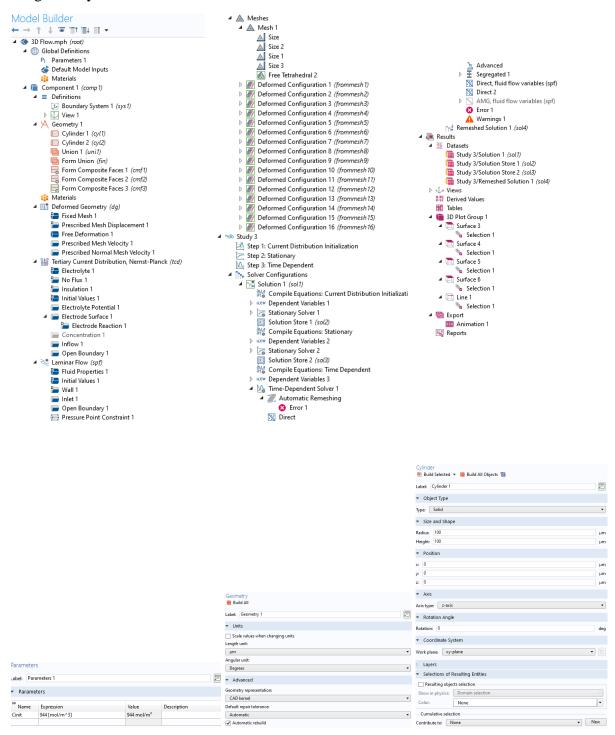

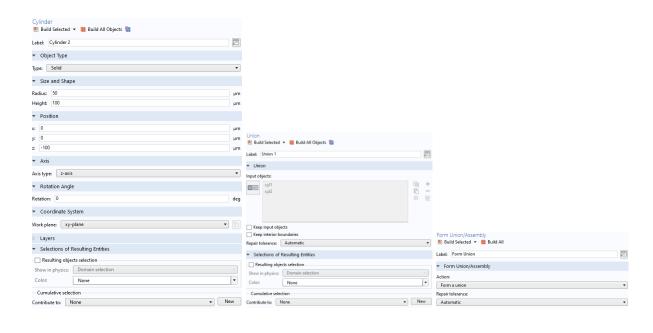

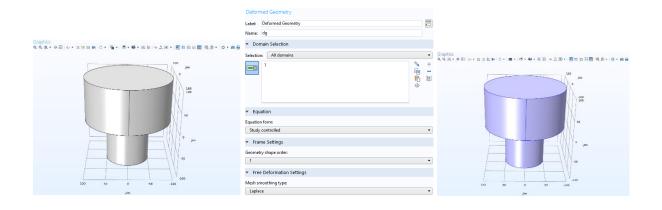

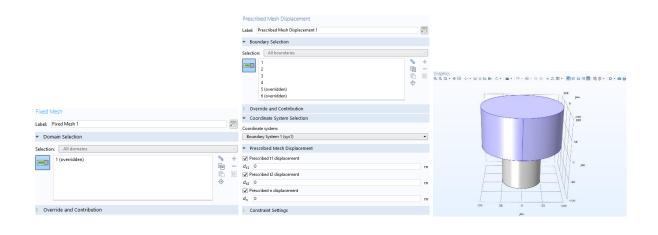

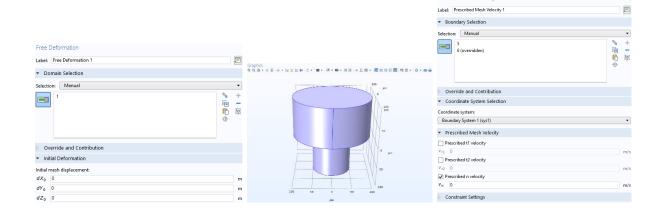

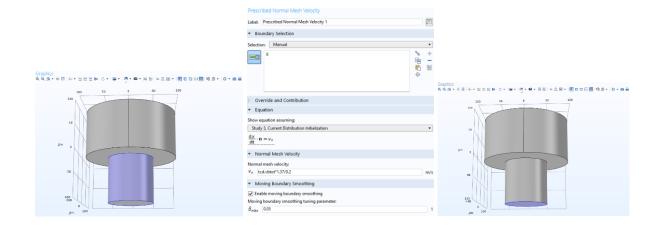

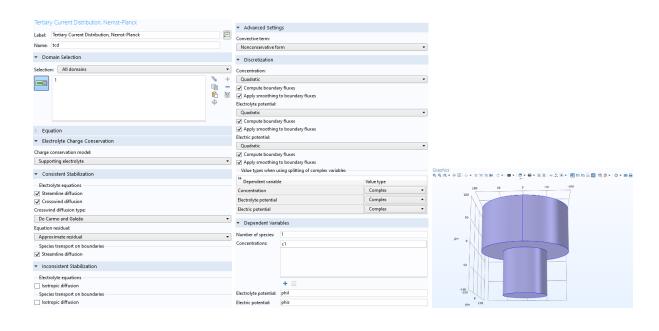

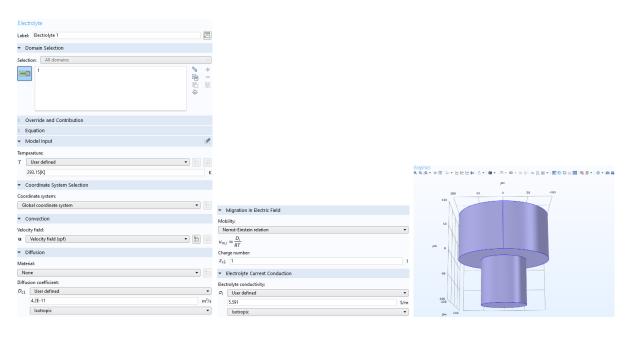

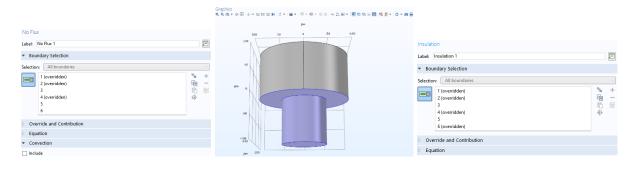

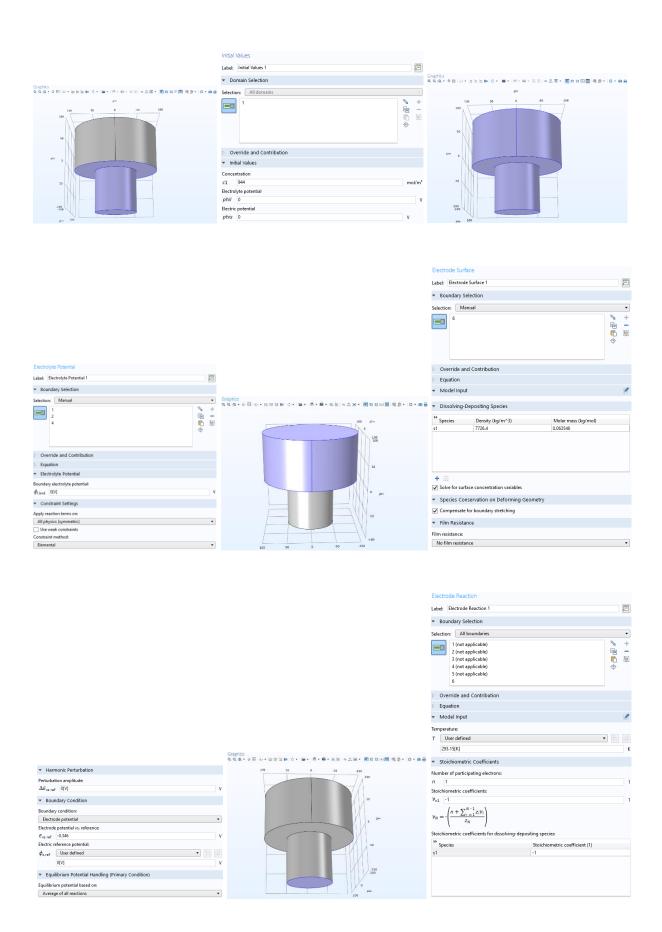

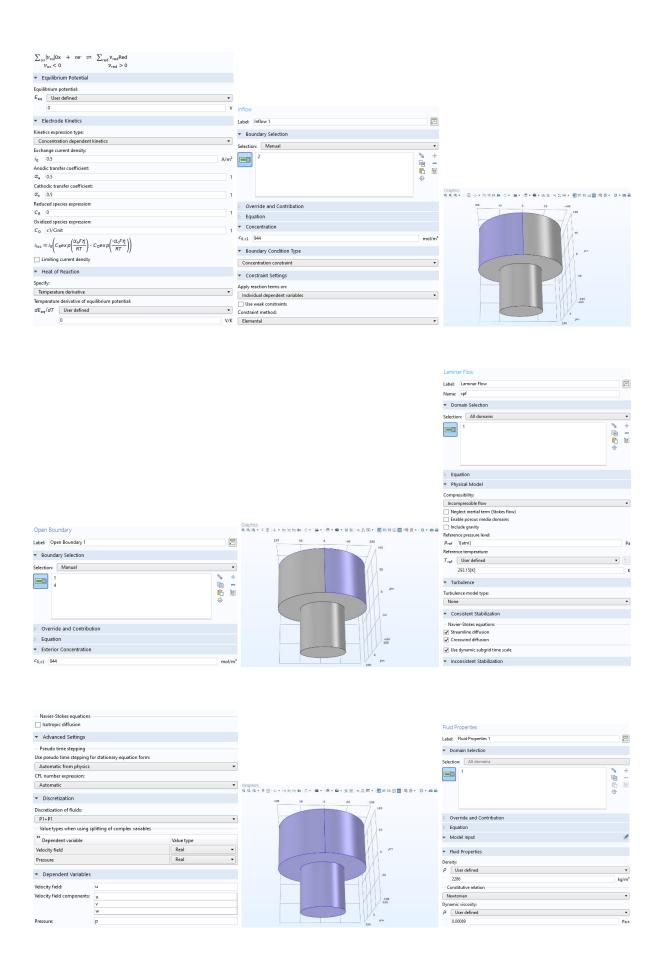

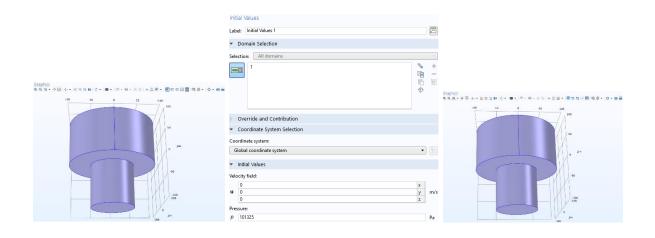

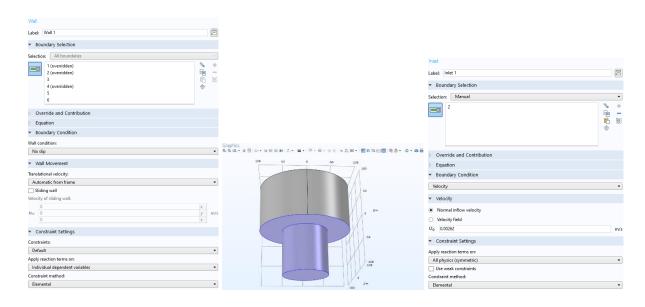

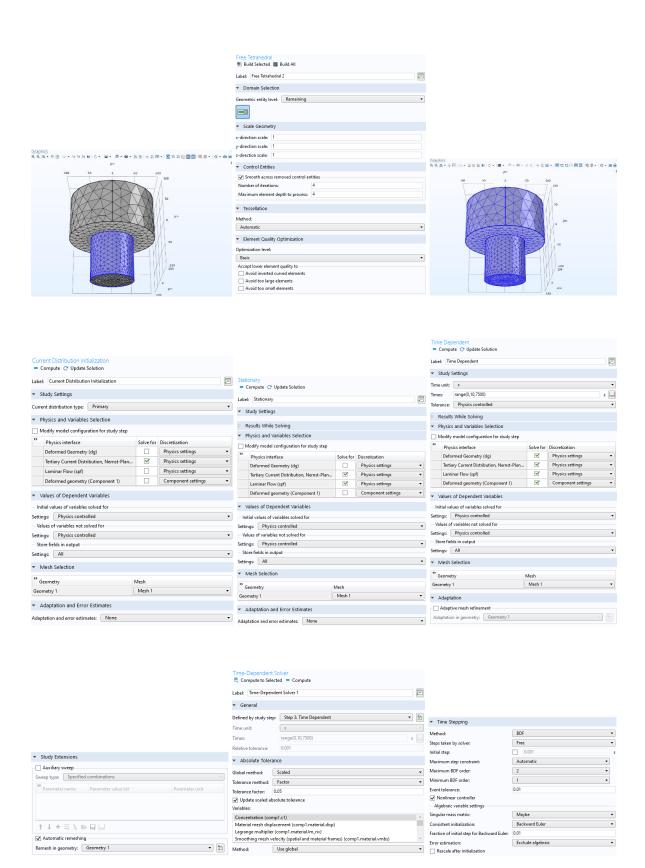

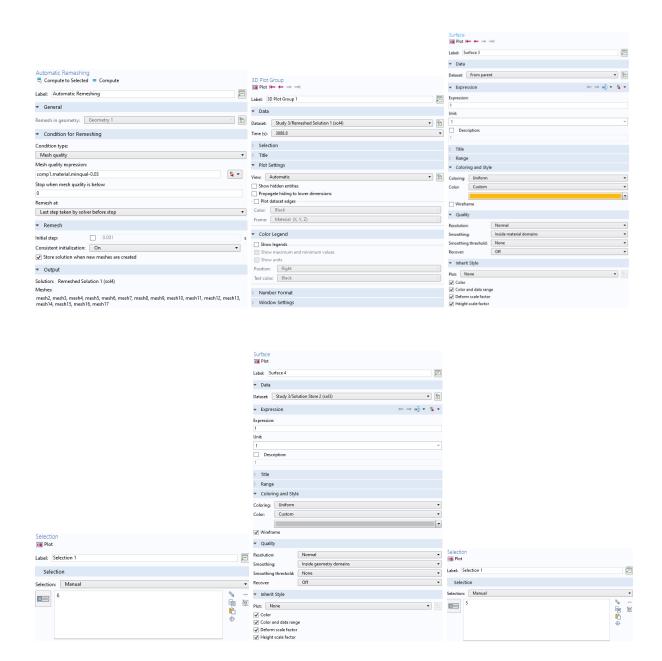

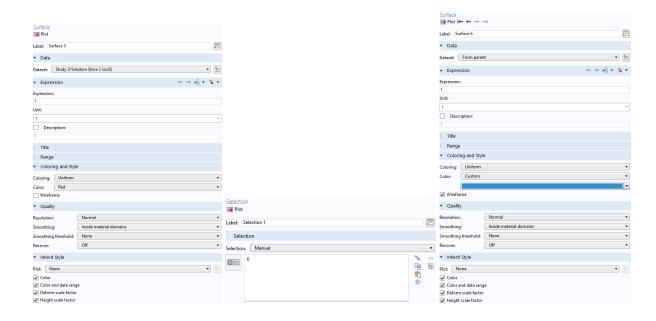

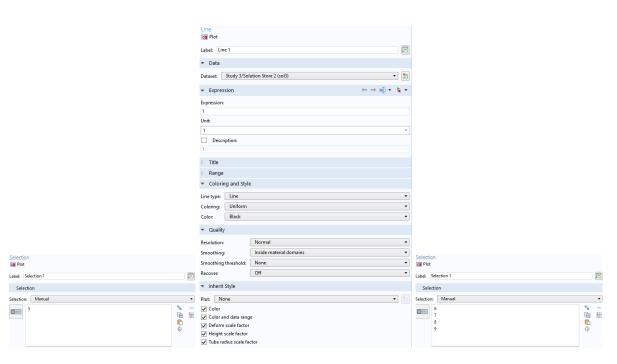

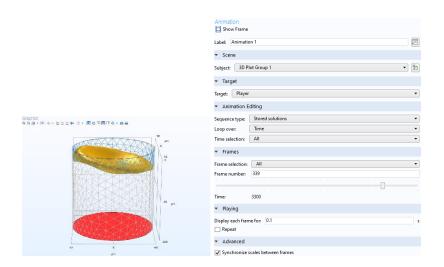

| 4.2. 3D simulations in COMSOL Multiphysics                                                                                                                |     |

| 4.2.1. Fundamental equations                                                                                                                              |     |

| 4.2.2. Solver settings                                                                                                                                    |     |

| 4.2.3. Validating 3D simulations with experimental work                                                                                                   |     |

| 4.3. Experimental results                                                                                                                                 |     |

| 4.3.1. Cu VIA electroplated thickness progression                                                                                                         |     |

| 4.3.2. Cu VIA electroplating technical challenges                                                                                                         |     |

| 4.4. Achievements and conclusions                                                                                                                         |     |

| 4.5. References                                                                                                                                           |     |

| Chapter 5 - Fabrication of Novel 3D Microinductors for Next Generation Integrated                                                                         |     |

| 5.1. Target device                                                                                                                                        |     |

| 5.2. Process design                                                                                                                                       | 130 |

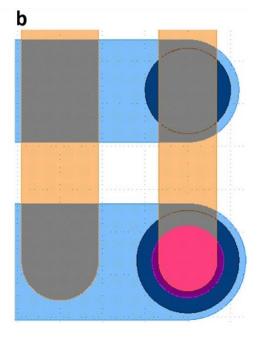

| 5.3. KLayout photomask designs                                                                                                                            | 135 |

| 5.3.1. Plating density normalization                                                                                                                      | 135 |

| 5.3.2. Mask 1                                               | 136 |

|-------------------------------------------------------------|-----|

| 5.3.3. Mask 2                                               | 137 |

| 5.3.4. Mask 3                                               | 138 |

| 5.3.5. Mask 4                                               | 138 |

| 5.3.6. Mask 5                                               | 139 |

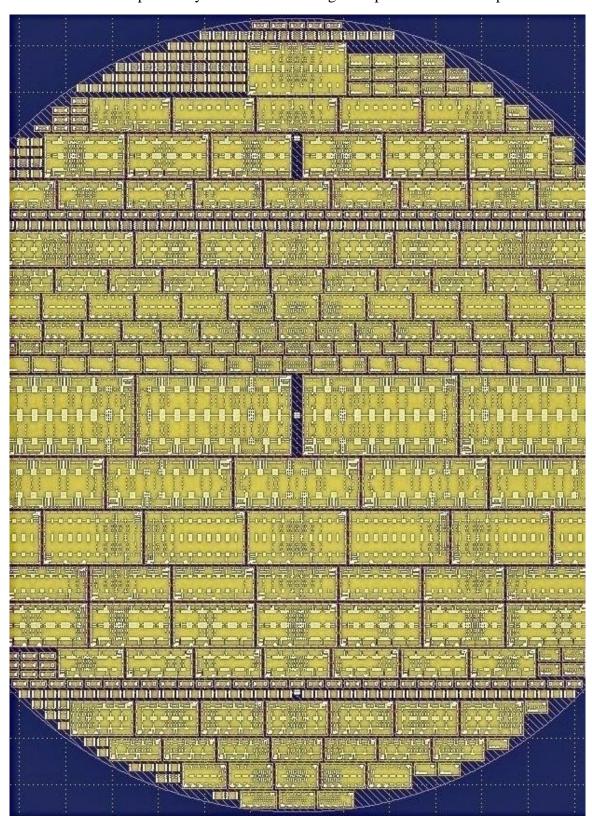

| 5.3.7. Full wafer layout                                    | 139 |

| 5.4. Standard operating procedures                          | 140 |

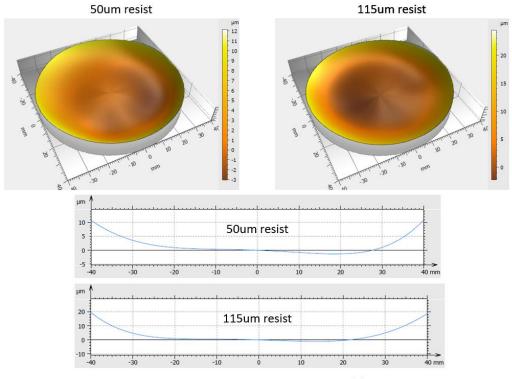

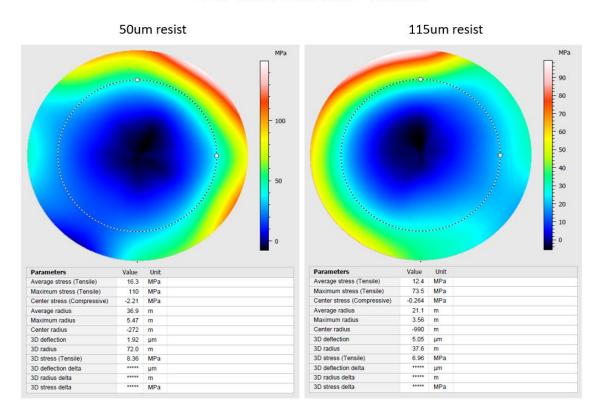

| 5.5. Chemical mechanical polishing                          | 140 |

| 5.6. Fabricated devices                                     | 142 |

| 5.6.1. High-resolution light microscope images              | 142 |

| 5.6.2. X-ray images                                         | 144 |

| 5.7. Device characterization: results and analysis          | 144 |

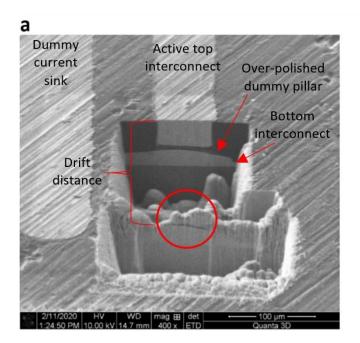

| 5.7.1. Focused ion beam SEM micrographs                     | 144 |

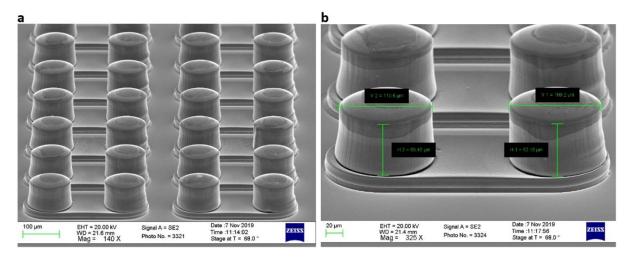

| 5.7.2. Photoresist stripping and SEM micrographs            | 145 |

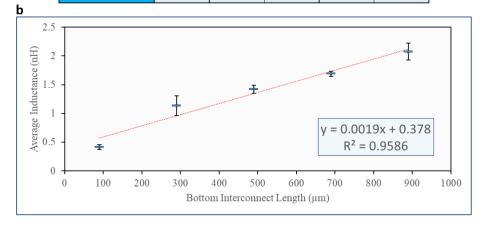

| 5.7.3. LCR meter electrical testing                         | 146 |

| 5.7.4. Magnetic anisotropy investigation                    | 147 |

| 5.7.5. Microinductor footprint reduction investigation      | 148 |

| 5.8. Achievements and conclusions                           | 150 |

| 5.9. References                                             | 150 |

| Chapter 6 – Summary and Future Work                         | 152 |

| 6.1. Summary                                                | 152 |

| 6.1.1. Main contributions of this work                      | 154 |

| 6.2. Future work                                            | 155 |

| 6.2.1. In-situ photomask                                    | 155 |

| 6.2.2. Polymer core VIAs                                    | 156 |

| 6.2.3. Electroplating soft magnetic laminations             | 157 |

| 6.3. References                                             | 158 |

| Appendix I: Patents, publications and awards                | 162 |

| Patents                                                     | 162 |

| Publications                                                | 162 |

| Awards                                                      | 162 |

| Appendix II: Wolfram Mathematica code                       | 163 |

| Appendix III: COMSOL simulations                            | 168 |

| Appendix IV: THB-151N profilometer metrology                | 180 |

| Appendix V: ADEPT patent application                        | 181 |

| Appendix VI: Enabling CMOS compatibility in the plating lab | 251 |

| Appendix VII: imec ASCENT work package       | 258 |

|----------------------------------------------|-----|

| Appendix VIII: Scientific image competitions | 261 |

| Appendix IX: SOPs for photomasks 1-5         | 266 |

| Photomask 1                                  | 266 |

| Photomask 2                                  | 267 |

| Blanket spin                                 | 268 |

| Photomask 3                                  | 268 |

| Photomask 4                                  | 269 |

| Photomask 5                                  | 269 |

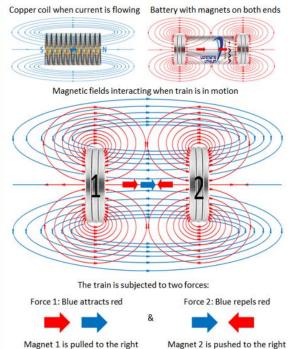

| Appendix X: Electromagnet outreach project   | 270 |

|                                              |     |

## **Declaration**

| This is to certify that the work I am submitting is my own and has not been submitted for   |

|---------------------------------------------------------------------------------------------|

| another degree, either at University College Cork or elsewhere. All external references and |

| sources are clearly acknowledged and identified within the contents. I have read and        |

| understood the regulations of University College Cork concerning plagiarism.                |

Daniel Smallwood

#### Acknowledgements

I wish to express my sincere gratitude to my supervisors, Dr. James Rohan and Dr. Paul McCloskey, for welcoming me into their research groups at Tyndall National Institute. Their scientific guidance, mentorship and vast knowledge of electrochemistry, physics and integrated magnetics greatly assisted in the momentum of this work. I wish to say a special thank you to the PI of our research project, Prof. Cian O'Mathuna, for his support, encouragement and inspirational leadership. I'd also like to express my gratitude to Prof. John Hayes for the engaging and insightful lessons in power electronics.

Thank you to all my friends and colleagues in both the Electrochemical Materials and Energy and the Integrated Magnetics groups. I especially wish to thank Declan Casey for his valued comradery and for assisting with many of the technical challenges of fabrication. Thank you to the amazing ADEPT project team: Darragh Cronin, Liang Ye, Daniel Lordan, Guannan Wei, Youssef Kandeel, Maeve Duffy and Chandra Shetty. I've really enjoyed being part of such a brilliant and motivated group of individuals.

There are so many people at Tyndall who have assisted me along the way. In particular, I wish to thank: Finbarr Waldron, Ann Foley, Richard Murphy, Joe O'Brien, Alan Hydes, Alan Blake, Lorraine Nagle, Paul Tassie, Krimo Khalfi, Dermot Houston, Vince Lodge, John Cashman, Ricky Anthony, Michael Schmidt and Tomás Clancy. Thank you to my thesis committee for their valuable advice and many discussions that shaped the path of my PhD. Thank you to Fatima Gunning, Willie Lawton and Ian Povey for their guidance and support throughout my postgraduate journey. Thank you to James O'Callaghan and Dara Fitzpatrick for giving me the opportunity to develop and share my passion and enthusiasm for teaching at the graduate and postgraduate level. Thank you to Alida Zauers for organizing so many great STEM outreach events, which I've enjoyed taking part in. Thank you to Prof. Eoin O'Reilly for reviewing and providing insightful commentary on our manuscript. Thanks to Julie Donnelly, John Slabbekoorn, Paul Roseingrave and Andy Miller for assisting with the imec ASCENT project. Thank you to Science Foundation Ireland for funding this research.

To my fellow colleagues, collaborators, PhD students and postdocs at Tyndall and UCC, thank you for the many engaging discussions, your friendship and for making this journey so enjoyable. A special thanks to Pranay Podder, Ansar Masood, Zoran Pavlović, Louise McGrath, Fiona Barry, Hasan Baghbaderani, Hugh Smiddy, Seamus O'Driscoll, Declan Jordan, Ruaidhrí Murphy, Zahra Ghaferi, Ehren Dixon, Mary Kent, Eilís Mulcahy, Sinead O'Sullivan, Orla Slattery and Jim Greer.

I'm deeply grateful to my family, friends and in-laws for all the fun times in between long hours of research, which included discovering the wild beauty of Ireland and fossil hunting on England's Jurassic coast. I especially wish to thank my mom and dad, Kristin and Chuck, for their endless love, support and advice. Finally, I am eternally grateful to my amazing and loving wife, Catherine. Thank you for always encouraging me to follow my dreams.

### **List of Acronyms**

24/7 24 hours per day, 7 days per week

AC Alternating Current

AI Artificial Intelligence

ALD Atomic Layer Deposition

AR Aspect Ratio

ASIC Application Specific Integrated Circuit

BIC Bottom Interconnect

BTA 1,2,3-Benzotriazole

CAD Computer Aided Design

CAGR Compound Annual Growth Rate

CCM Continuous Conduction Mode

CED Critical Exposure Dose

CMOS Complementary Metal-Oxide-Semiconductor

CMP Chemical Mechanical Polishing

CPU Central Processing Unit

CTE Coefficient of Thermal Expansion

CVD Chemical Vapor Deposition

DC Direct Current

DG Deformed Geometry

DI Deionized

DM Digital Matrix

DMSO Dimethyl Sulfoxide

DRAM Dynamic Random Access Memory

DRIE Deep Reactive Ion Etching

D:SS Diameter to Step Size Ratio

DUV Deep Ultraviolet

e.g. Exempli Gratia

EBR Edge Bead Removal

ED Exposure Dose

EDX Energy Dispersive X-Ray

EHT Electron High Tension

EM Electromagnetic

EMF Electromotive Force

EMI Electromagnetic Interference

ESW EBR Stream Width

FAR Floor Area Ratio

FC Flip-Chip

FEM Finite Element Method

FEPA Federation of European Producers of Abrasives

FIB Focused Ion Beam

GPU Graphics Processing Unit

GSGSG Ground Source Ground Source Ground

HAR High Aspect Ratio

HBM High Bandwidth Memory

HDD Hard Disk Drive

HF High Frequency

HTC Heat Transfer Coefficient

I/O Input/Output

IC Integrated Circuit

ID Identifier

IoT Internet of Things

IRDS International Roadmap for Devices and Systems

ISO International Standards Organization

ITRS International Technology Roadmap for Semiconductors

IVR Integrated Voltage Regulator

JGB Janus Green B

KMC kinetic Monte Carlo

1/s Line to Space

LCR Inductance, Capacitance and Resistance

LF Laminar Flow

LIGA Lithography Electroplating and Molding

LP Long Pass

MEMS Microelectromechanical Systems

MM More Moore or Moving Mesh

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MPS 3-Mercapto-1-Propanesulfonic Acid

MtM More than Moore

N/A Not Applicable

NA Numerical Aperture

NEMS Nanoelectromechanical Systems

OB Open Boundary

PC Personal Computer

PEB Post Exposure Bake

PECVD Plasma Enhanced Chemical Vapor Deposition

PEG Polyethylene Glycol

PGMEA Propylene Glycol Monomethyl Ether Acetate

PMIC Power Management Integrated Circuit

PMMA Poly(Methyl Methacrylate)

PoL Point-of-Load

PoS Point-of-Source

PPG Polypropylene Glycol

PPR Periodic Pulse Reverse

PR Photoresist

psi Pounds Per Square Inch

PVD Physical Vapor Deposition

PwrSiP Power Supply in Package

PwrSoC Power Supply on Chip

R&D Research and Development

RDL Redistribution Layer

RF Radio Frequency

rpm Rotations Per Minute

RT Room Temperature

SEM Scanning Electron Microscope

SFI Science Foundation Ireland

SiP System in Package

SMPS Switch-Mode Power Supply

SoC System on Chip

SOP Standard Operating Procedure

SPS Bis-(3-Sulfopropyl) Disulfide

SQUID Superconducting Quantum Interference Device

SSD Solid State Drive

STP Standard Temperature & Pressure

TCD Tertiary Current Distribution

TDS Technical Data Sheet

TIC Top Interconnect

TMAOH Tetramethylammoniumhydroxide

TPV Through Polymer Via

TSV Through Substrate/Silicon Via

UV Ultraviolet

VIA Vertical Interconnect Access

WD Working Distance

WLVP Wafer Level Vacuum Packaging

### **List of Symbols**

Null field

\$ Dollars

% Percent

$\Delta I_{L(p-p)}$  Inductor ripple current magnitude

$A_1$  Transmitted attenuating path length

$A_2$  Internally reflected attenuating path length

$C_0$  Oxidized species concentration

$C_F$  Fixed costs

$C_R$  Reduced species concentration

$C_V$  Variable costs

$ED_{spec}$  Specified aerial exposure dose

$E_a$  Activation energy

$E_{eq}$  Equilibrium voltage

$I_{\lambda_i}$  Aerial relative intensity fraction of the ith species

*I*<sub>0</sub> Bulb irradiance

$I_D$  Diode current

$I_{HV}$  High voltage current

$I_{L(max)}$  Maximum inductor current

$I_{L(min)}$  Minimum inductor current

$I_{LV}$  Low voltage current

$I_Q$  Transistor current

*I<sub>max</sub>* Maximum current

*I<sub>sat</sub>* Saturation current

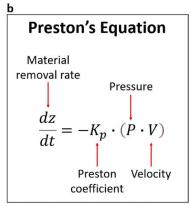

$K_p$  Preston coefficient

$R_{p_{i_{1,2}}}$  P-polarized reflection coefficient at interfaces 1 and 2

$R_{S_{i_1}}$  S-polarized reflection coefficient at interfaces 1 and 2

$R_{AC}$  Alternating current resistance

$R_{DC}$  Direct current resistance

$R_{i1}$  Reflection coefficient at interface 1

$R_{i2}$  Reflection coefficient at interface 2

$T_S$  Switching period

$U_0$  Unattenuated light amplitude

$V_{HV}$  High voltage value

$V_{LV}$  Low voltage value

Z' Impedance real part

Z" Impedance imaginary part

e<sup>-</sup> Electron

$f_S$ ,  $\omega$  Switching frequency

$g_1$  Non-attenuating path length

$g_2$  Refraction-adjusted non-attenuating path length

*i*<sub>0</sub> Exchange current density

$i_{loc}$  Local current density

*i*<sub>p</sub> Pulse current

$i_{rev}$  Reverse current

*k<sub>B</sub>* Boltzmann's constant

$t_{off}$  Off time

$t_{on}$  On time

$t_{rev}$  Reverse time

$\vec{u}$  Velocity vector

$u_0$  Aperture plane light amplitude

$v_P$  Pole voltage

$\Phi_B$  Magnetic flux

$\alpha_a$  Anodic transfer coefficient

$\alpha_c$  Cathodic transfer coefficient

$\mu_0$  Vacuum permeability

$\mu_r$  Relative permeability/Large relative permeability value

$\mu_r'$  Small relative permeability value

$\epsilon_0$  Vacuum permittivity

$\epsilon_r$  Relative permittivity

$\Delta T$  Temperature difference

Degrees

$\sim$  or  $\approx$  Approximately equal to

°C Degree Celsius

μ*m* Micrometer

Å Angstrom

Electromotive force

h Heat transfer coefficient/Hour

h-line 405 nanometer wavelength

N, W, S, E The cardinal directions

κ Dielectric constant

A Ampere/Aperture/Area

A, B, C, D, E, F Cauchy coefficients

Ag Silver

Al Aluminum

Au Gold

B Magnetic field strength/Boron

C Coulomb

Co Cobalt

Cu Copper

Diameter/Diffusion coefficient/Diode/Duty cycle/Dimensional

E Applied voltage

Faraday's constant/Fresnel number/Fluorine

Fe Iron

G Gate

Henries/Auxiliary magnetic field/Hydrogen

I Current

I(z) Luminous intensity

Joule/Diffusive flux

K Degree Kelvin/Extinction coefficient

L Inductor/Inductance/Characteristic length/Large inductance value

L' Small inductance value

MHz Megahertz

MX Metal pitch of X

MY Man years

N Complex refractive index/Winding or turn number/Mass transport

vector/Nitrogen

*N* + Negatively doped

P + Positively doped

Nd Neodymium

Ni Nickel

Occulter/Oxygen

Oe Oersted

*P* Power/Pressure

Pa Pascal

Pt Platinum

Q Transistor/Switch/Quality/Rate of heat transfer

R Ideal gas constant/Electrical resistance

Re Reynolds number

Siemens/Spacing/Sulfur

Si Silicon

Tesla/Thickness

*Ta* Tantalum

*Ti* Titanium

U Attenuated light amplitude

V Velocity/Volt

W Watts/Tungsten

*Y* Yttrium

Zr Zirconium

b Bulb relative intensity spectrum

*c* Concentration

*cP* Centipoise

cm Centimeter

d Edge-broadening magnitude

d, g Air gap length

dm Decimeter

*e* The constant e

g Gram

g-line 436 nanometer wavelength

*i* The ith species/The imaginary unit

i-line 365 nanometer wavelength

k Wavenumber

*kHz* Kilohertz

keV Kiloelectron volt

kg Kilogram

l Path length/Cell length

m Meter

*mA* Milliamp

*mL* Milliliter

min Minute

mm Millimeter

mol 6.022x10<sup>23</sup> units

*n* The nth number/Refractive index

*nH* Nanohenry

*nm* Nanometer

ns Nanosecond

*pH* Picohenry

ppm Parts per million

r Radius/Electrical resistances Second/Solid

t Time

*u* Flow velocity

wt Weight

x Radial point/Horizontal direction

y Direction orthogonal to screen/page

z Distance from photomask/Vertical direction/Ionic charge

$\Omega$  Electrical resistance

∇Ø Electric field potential gradient

$\nabla c$  Concentration gradient

$\alpha$  Absorption coefficient

$\delta$  Angle of incidence/Partial derivative

$\eta$  Dynamic viscosity/Overpotential

$\theta$  Angle to the vertical line

$\lambda$  Wavelength

μ Kinematic viscosity

$\pi$  The constant Pi

*ρ* Density/Resistivity

$\varphi$  Substrate refraction angle

## **List of Figures**

## Chapter 1

| Figure 1.1. Buck converter inductor charging and discharging modes                                                    | 1       |

|-----------------------------------------------------------------------------------------------------------------------|---------|

| Figure 1.2. Buck converter operation in continuous conduction mode (CCM).                                             | 2       |

| Figure 1.3. Magnetic core microinductor schematic and cross-section.                                                  | 3       |

| Figure 1.4. Inductor footprint vs. frequency.                                                                         | 4       |

| Figure 1.5. 3D microinductor schematics with Cu pillars laminated in a magnetic material                              | 4       |

|                                                                                                                       |         |

| Chapter 2                                                                                                             |         |

| Figure 2.1. CMOS dimensional scaling projection from 2020-2034.                                                       | 10      |

| Figure 2.2. Semiconductor units shipped per year from 1978-2020.                                                      | 11      |

| Figure 2.3. Schematic of a TSV cross-section.                                                                         | 12      |

| Figure 2.4. Schematic cross-section of a 3D package                                                                   | 12      |

| Figure 2.5. The benefits of 3D integration.                                                                           | 13      |

| Figure 2.6. Schematic of a 2.5D package.                                                                              | 14      |

| Figure 2.7. MEMS WLVP with TSVs for I/O                                                                               | 15      |

| Figure 2.8. 3D microinductor with hyperfunctional VIAs coated in a laminated soft magnetic material.                  | 15      |

| Figure 2.9. 2.5D and 3D packaging with heterogeneous component integration demonstrating high device packing density. | :<br>16 |

| Figure 2.10. TSV scalloping as a result of a time-multiplexed etch (the Bosch process)                                | 17      |

| Figure 2.11. Plating voids in TSVs.                                                                                   | 18      |

| Figure 2.12. Superconformal electroplating.                                                                           | 19      |

| Figure 2.13. Bottom-up electroplating.                                                                                | 20      |

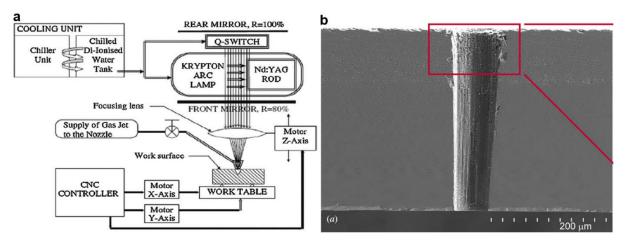

| Figure 2.14. Laser ablation.                                                                                          | 21      |

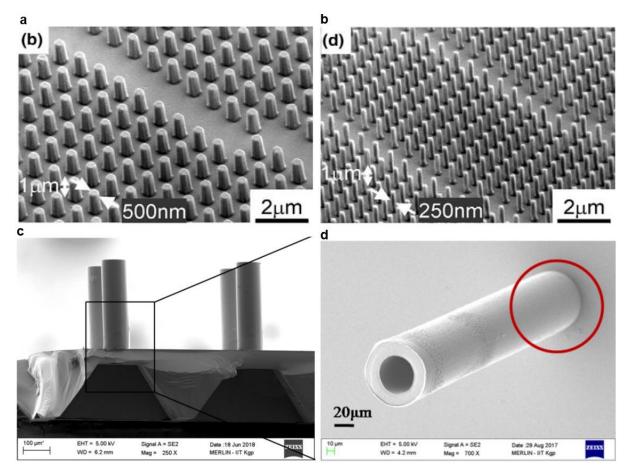

| Figure 2.15. Example lithography applications.                                                                        | 22      |

| Figure 2.16. Example lithography structures.                                                                          | 23      |

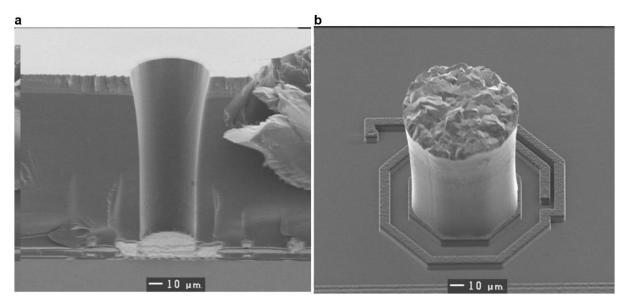

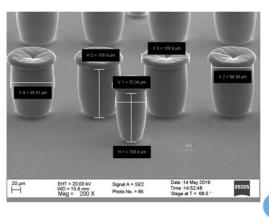

| Figure 2.17. Photolithography VIA mold and electroplated micropillar.                                                 | 24      |

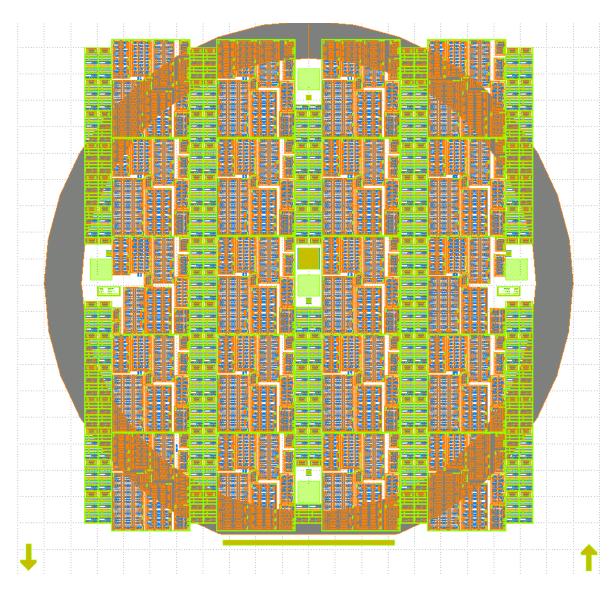

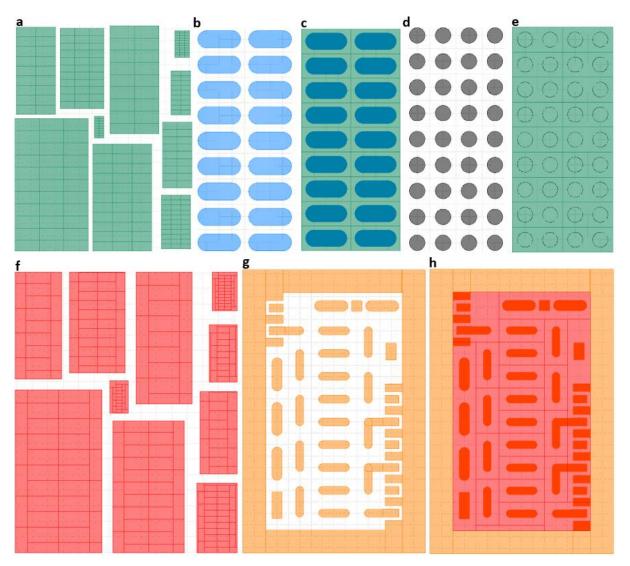

| Figure 2.18. Five-tier bright field photomask created in KLayout for making TSV microinductors                        | 25      |

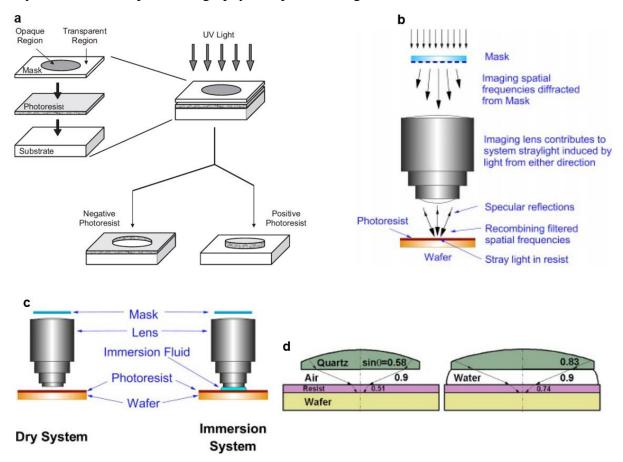

| Figure 2.19. Photolithography exposure process.                                                                       | 26      |

| Figure 2.20. Two key challenges in photolithography                                                                   | 27      |

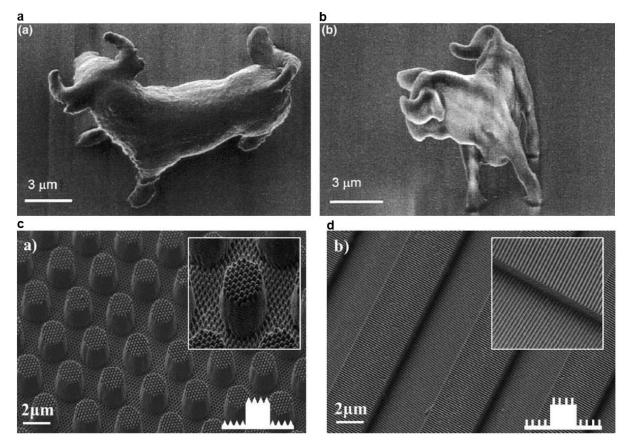

| Figure 2.21. Example techniques in photolithography.                                                                  | 28      |

| Figure 2.22. Cost analysis of photolithography (UV LIGA), DRIE and laser ablation                                     | 29      |

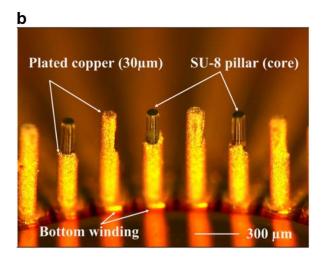

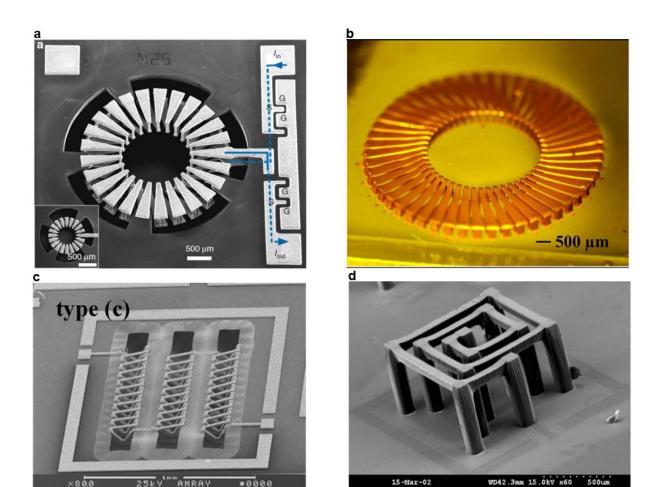

| Figure 2.23. 3D microinductors using VIAs.                                                                              | 34           |

|-------------------------------------------------------------------------------------------------------------------------|--------------|

| Chapter 3                                                                                                               |              |

| Figure 3.1. VIAs in 2.5D and 3D advanced packaging architectures.                                                       | 73           |

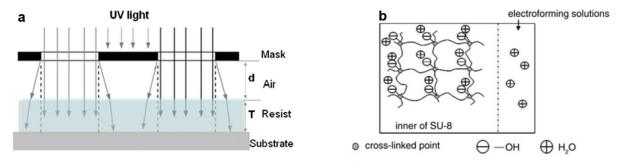

| Figure 3.2. Schematic depicting Huygens-Fresnel diffraction of a planar wave front at a photomask occuboundary          | lter<br>74   |

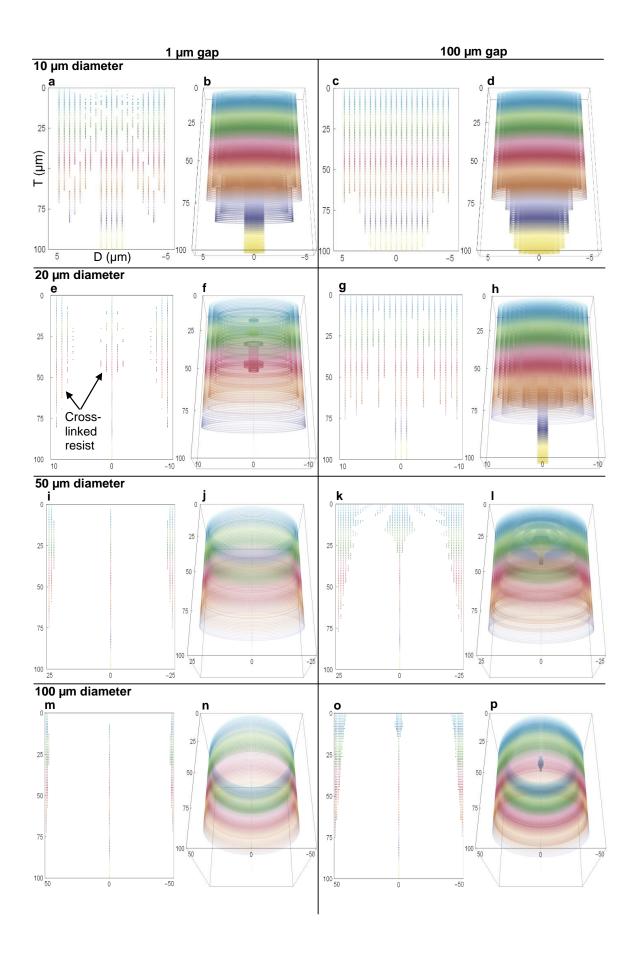

| Figure 3.3. Latent image simulations of varying photomask occulter diameters and air gaps                               | 86           |

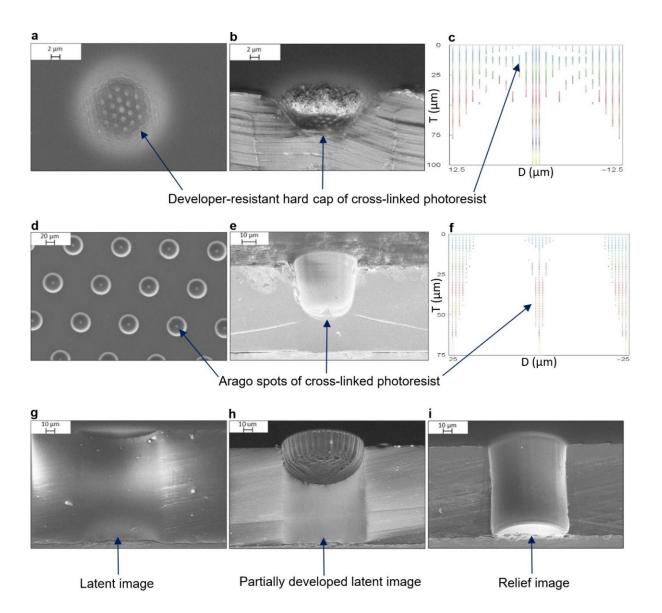

| Figure 3.4. Comparison between experimental and simulation work                                                         | 88           |

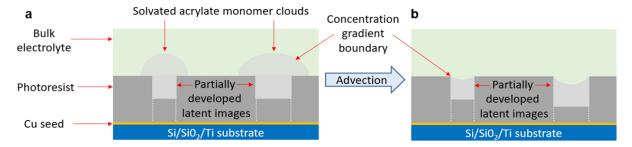

| Figure 3.5. The role of advection in increasing diffusive flux.                                                         | 92           |

| Figure 3.6. Developer temperature efficacy.                                                                             | 93           |

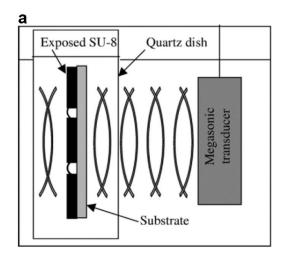

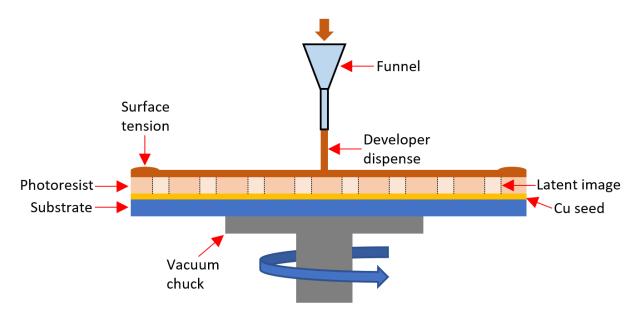

| Figure 3.7. Spin development schematic.                                                                                 | 94           |

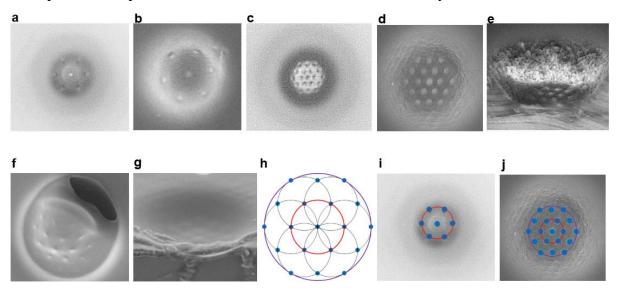

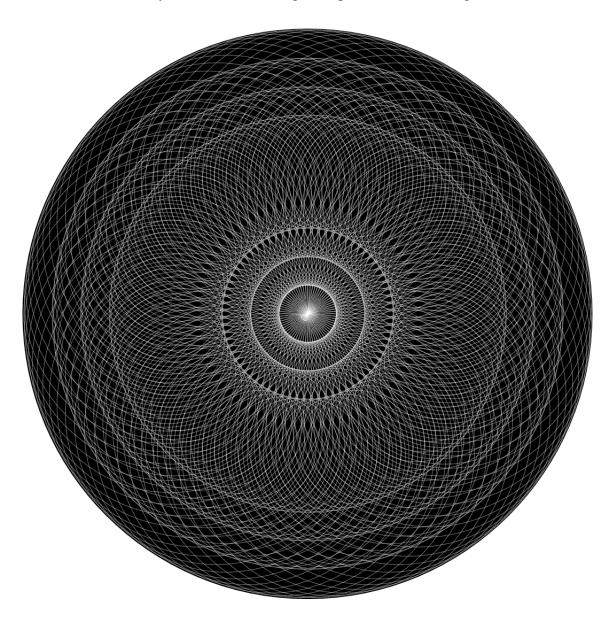

| Figure 3.8. Patterned phenomenon in photoresist, observed with different machinery, process parameters different dates. | and on<br>95 |

| Chapter 4                                                                                                               |              |

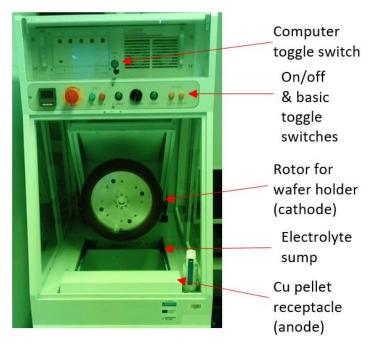

| Figure 4.1. Image of our dedicated Cu electroplating setup.                                                             | 104          |

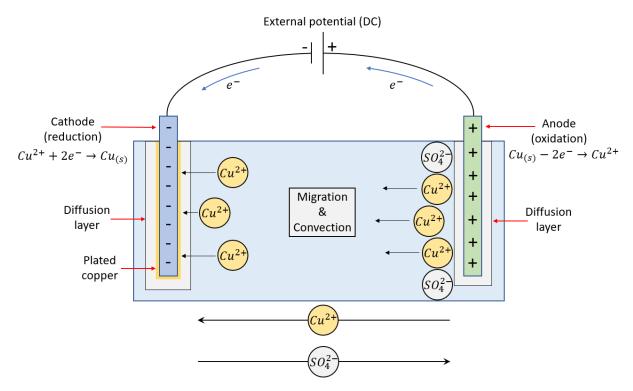

| Figure 4.2. Copper sulfate electrolytic cell.                                                                           | 107          |

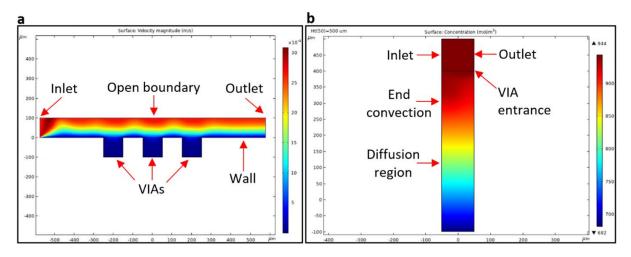

| Figure 4.3. VIA flow dynamics.                                                                                          | 108          |

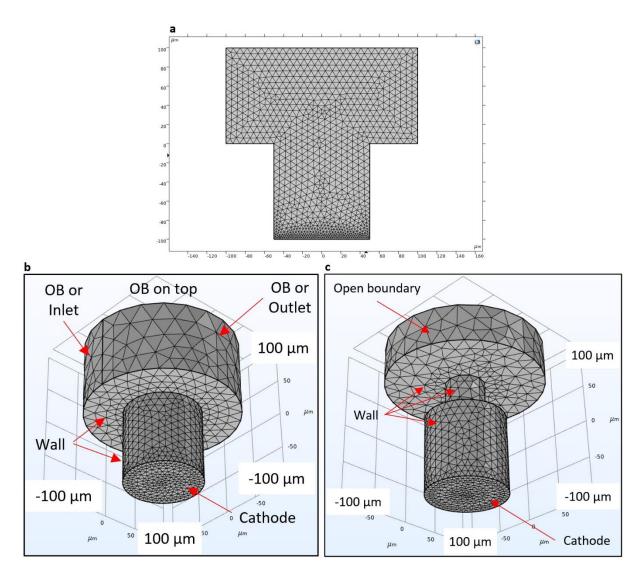

| Figure 4.4. Solver geometries and FEM meshes.                                                                           | 110          |

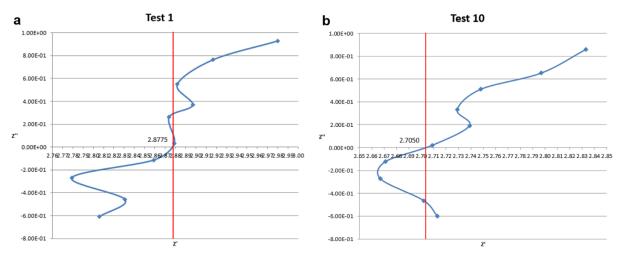

| Figure 4.5. Example impedance plots for electrolyte resistance determination.                                           | 111          |

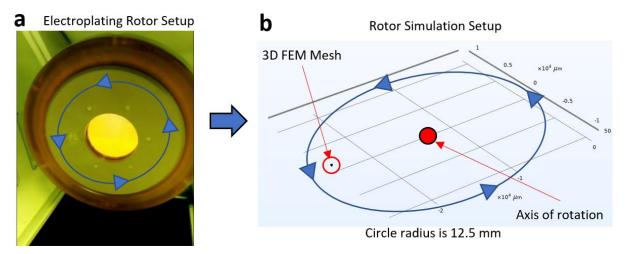

| Figure 4.6. Lab and COMSOL rotor setup.                                                                                 | 114          |

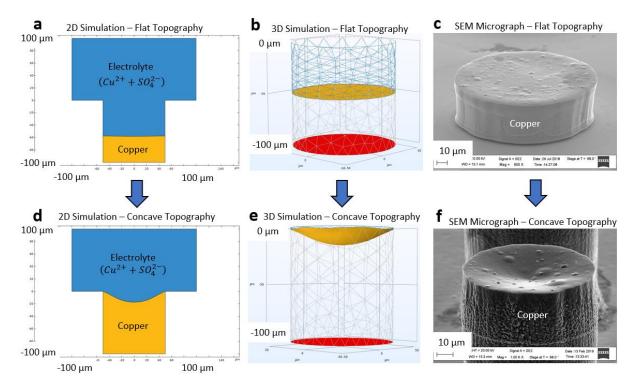

| Figure 4.7. 2D and 3D simulations with corresponding experimental work for concave topographies                         | 116          |

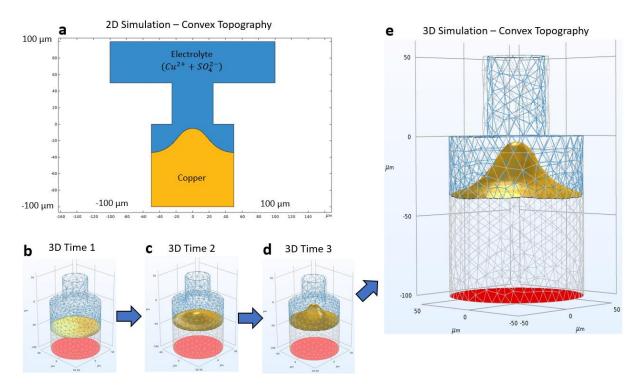

| Figure 4.8. 2D and 3D simulations for convex topographies.                                                              | 117          |

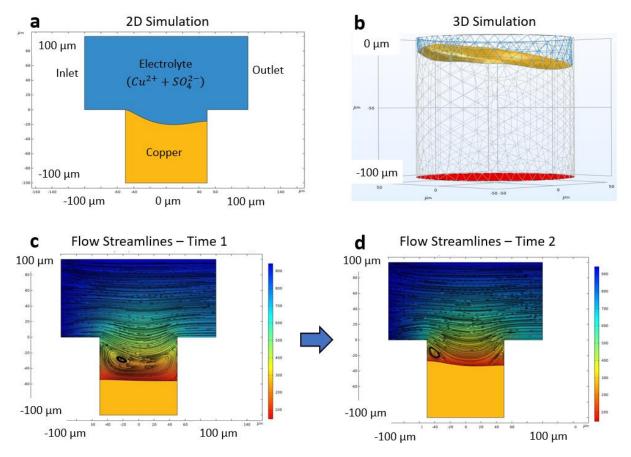

| Figure 4.9. 2D and 3D simulations with convection.                                                                      | 118          |

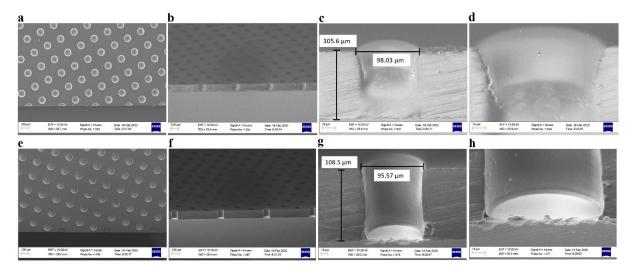

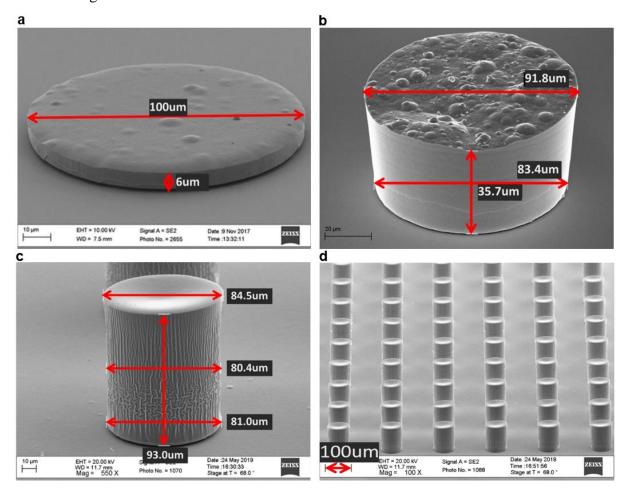

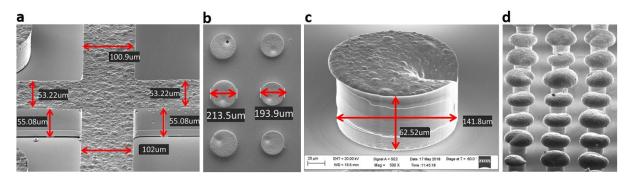

| Figure 4.10. Cu VIA electroplating thickness progression.                                                               | 119          |

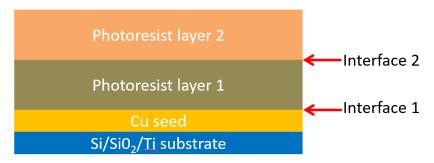

| Figure 4.11. Internal interfaces inside a double-spun photoresist.                                                      | 120          |

| Figure 4.12. Cu VIA electroplating technical challenges.                                                                | 121          |

| Chapter 5                                                                                                               |              |

| Figure 5.1. 3D schematic of the target microinductor device.                                                            | 129          |

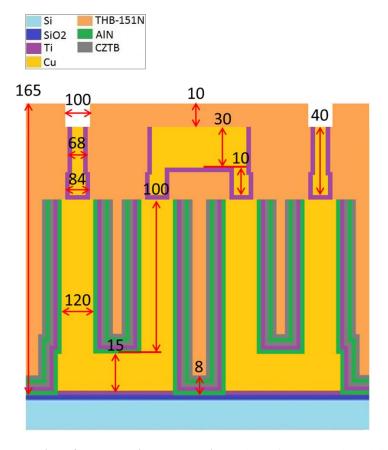

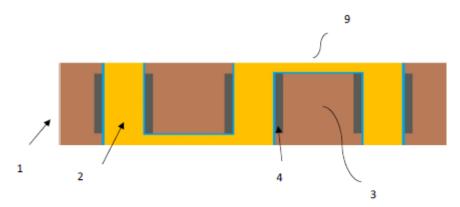

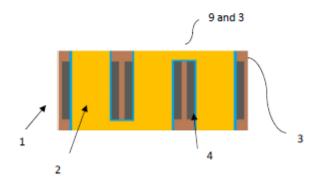

| Figure 5.2. 2D x-z cross section of the target inductor device                                                          | 130          |

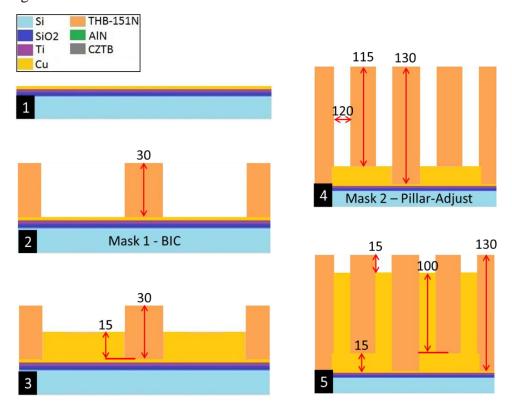

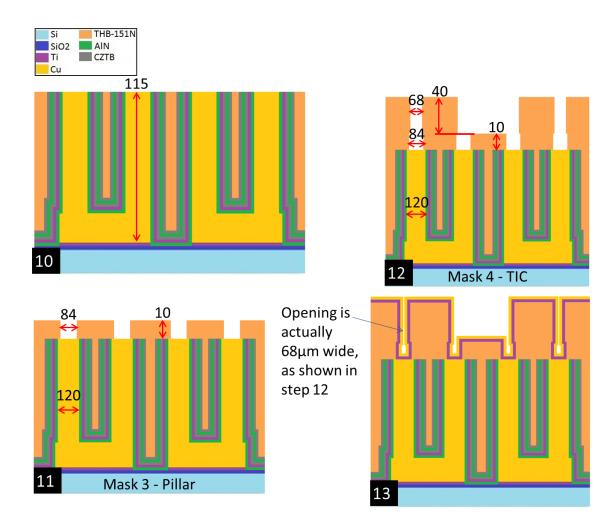

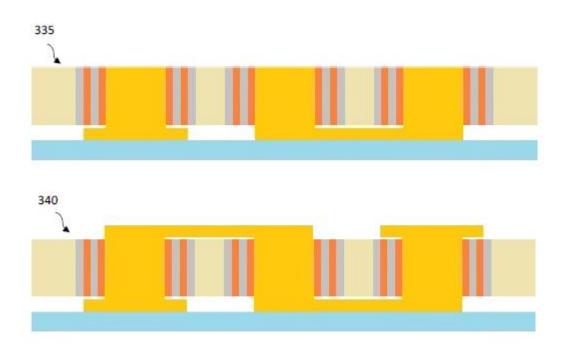

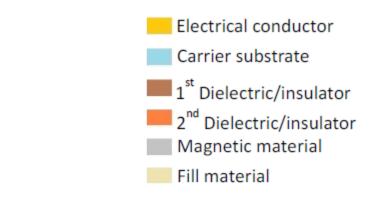

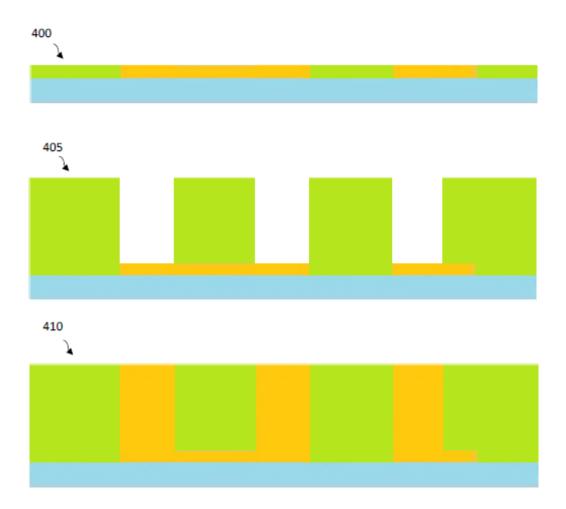

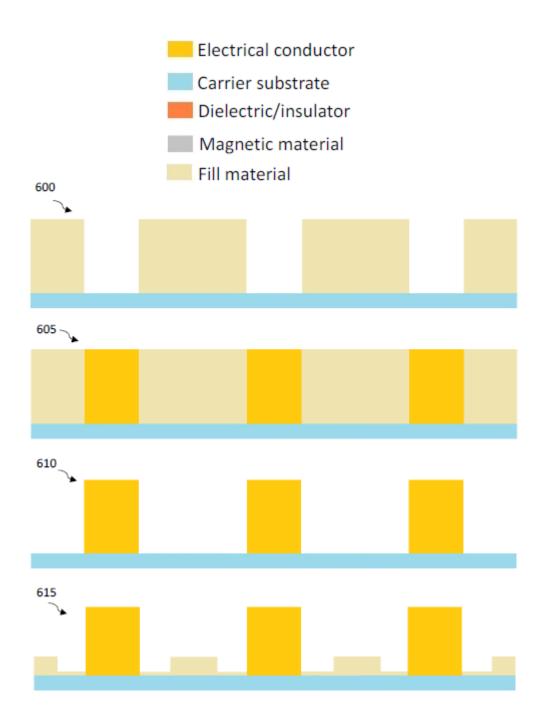

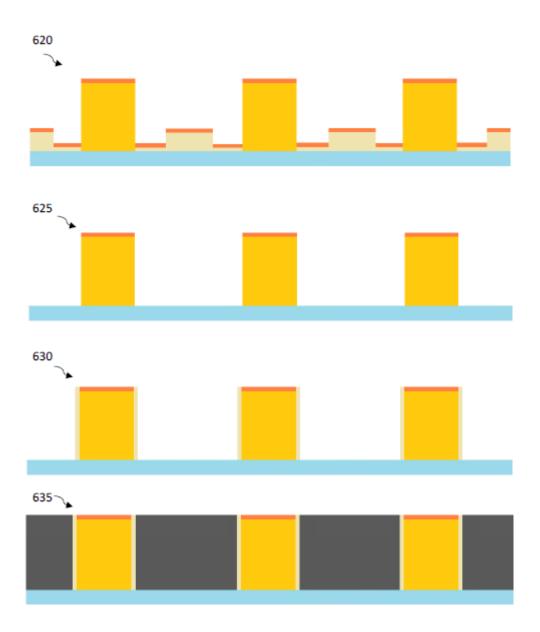

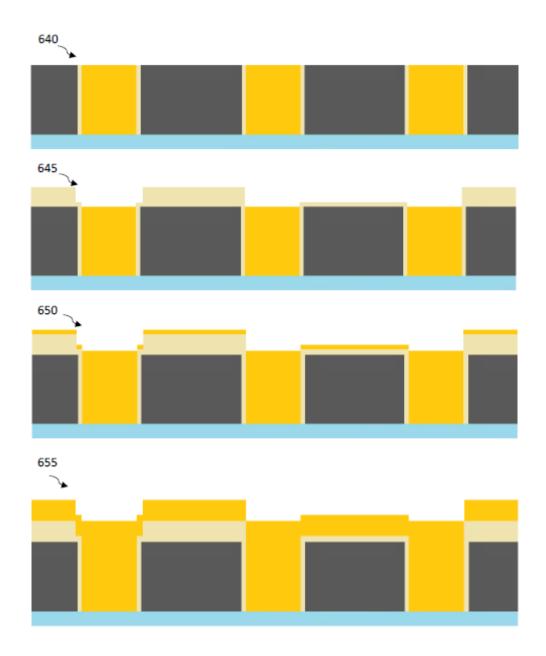

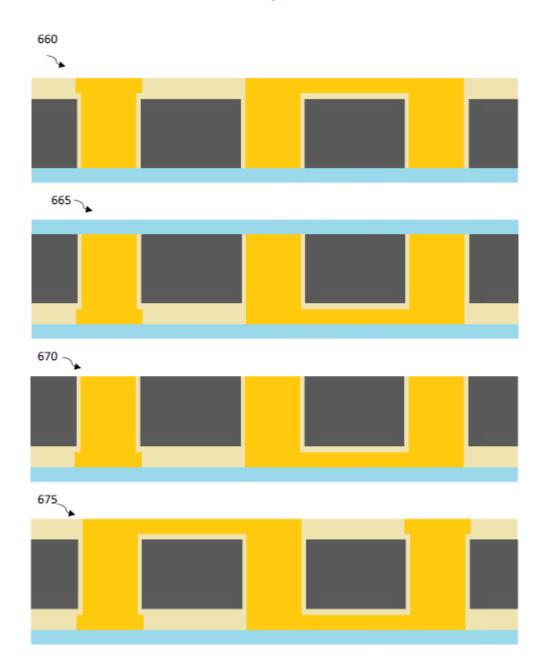

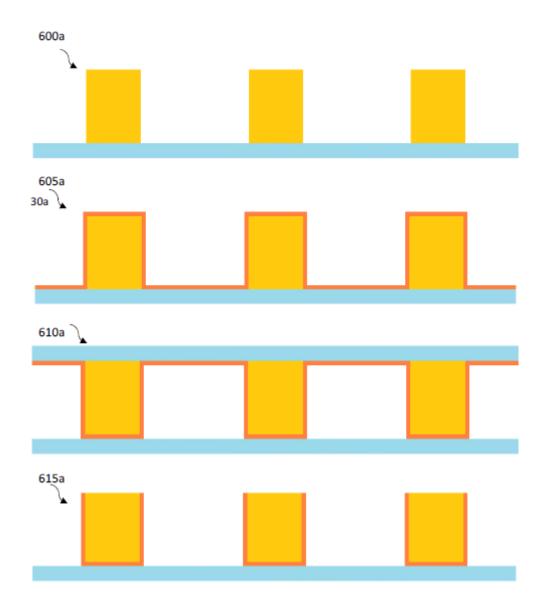

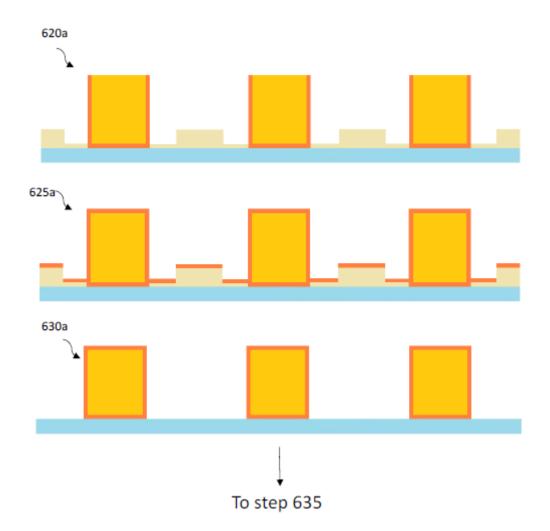

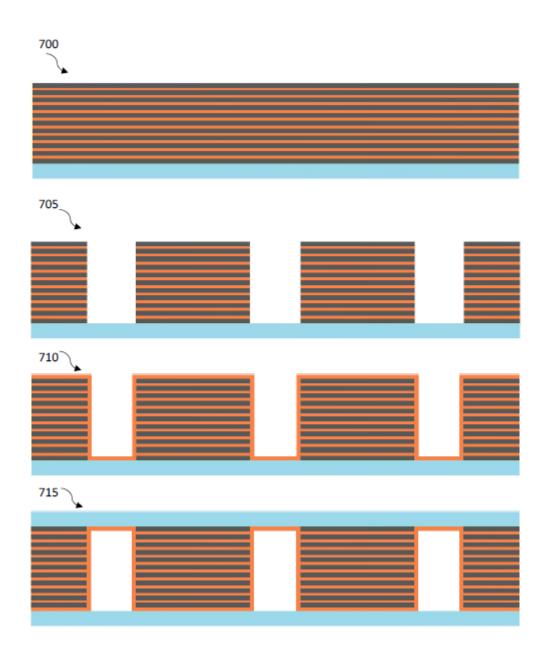

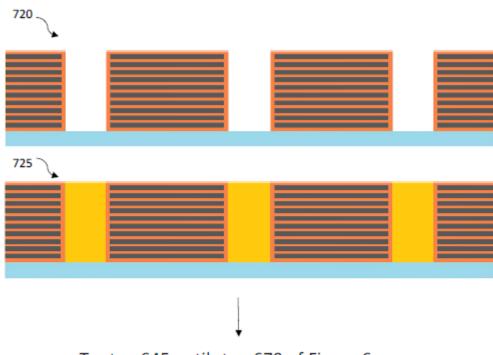

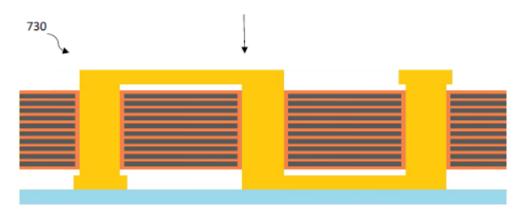

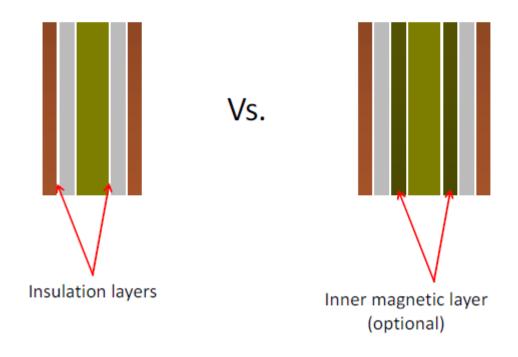

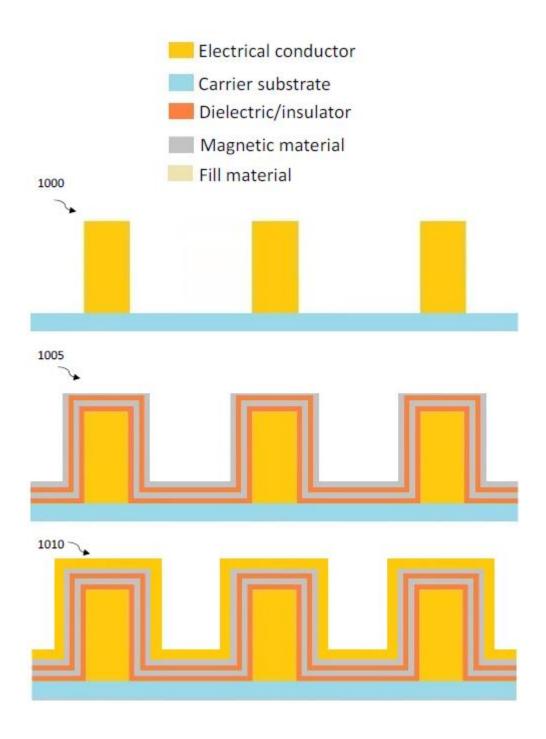

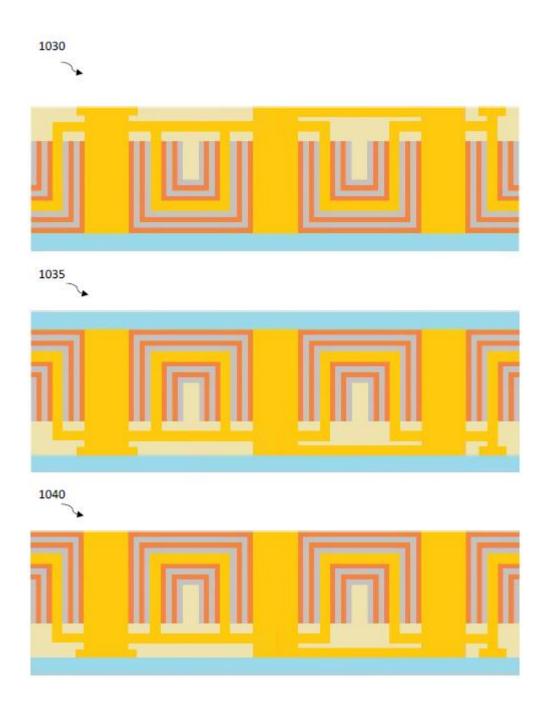

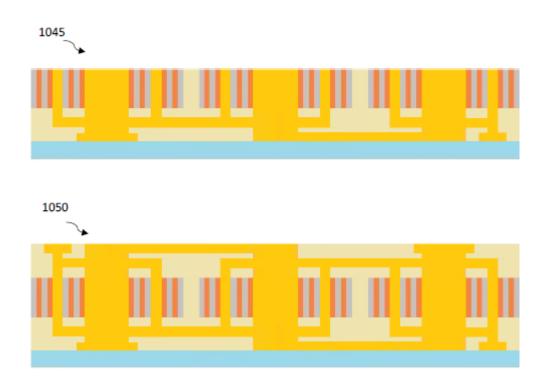

| Figure 5.3. Steps 1-5 of the fabrication process flow.                                                                  | 131          |

| Figure 5.4. Steps 6-9 of the fabrication process flow.                                                                                           | 132               |

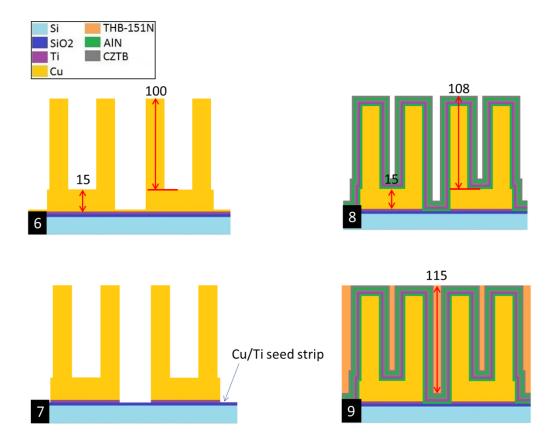

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

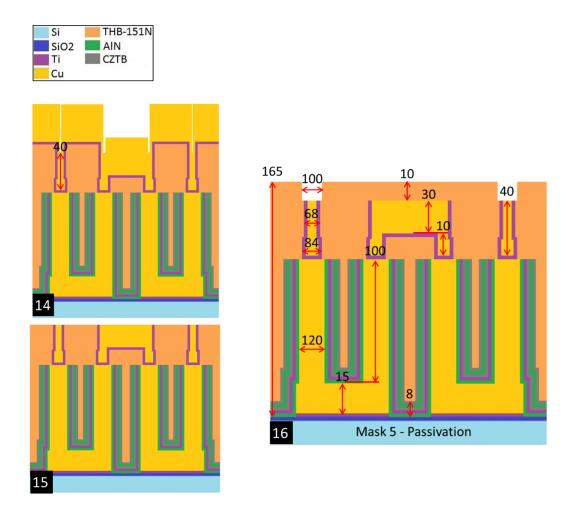

| Figure 5.5. Steps 10-13 of the fabrication process flow.                                                                                         | 133               |

| Figure 5.6. Steps 14-16 of the fabrication process flow.                                                                                         | 134               |

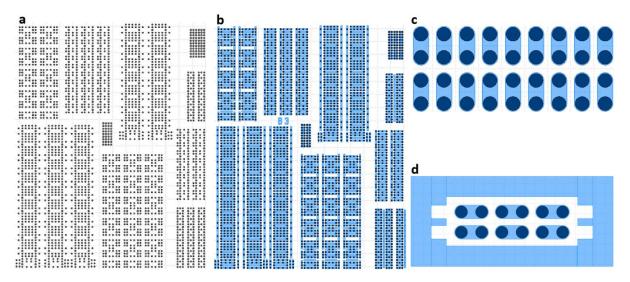

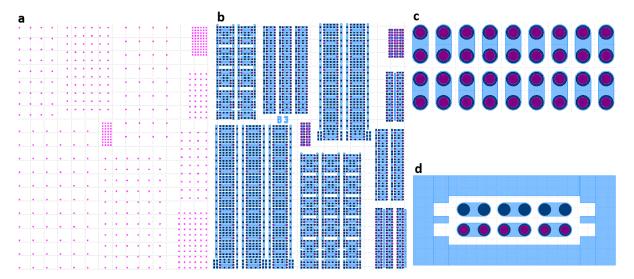

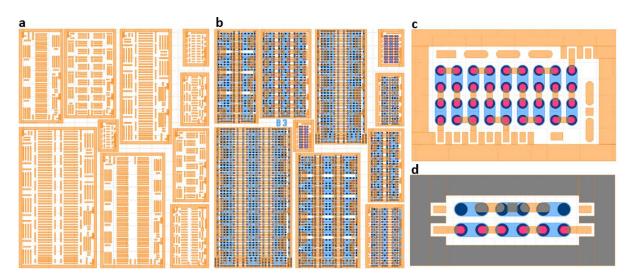

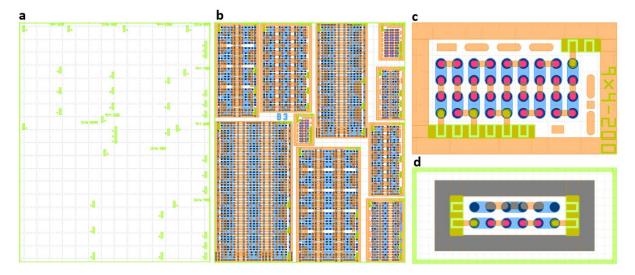

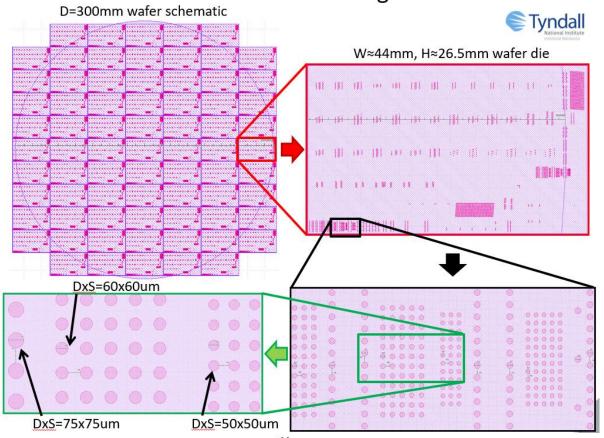

| Figure 5.7. Current density normalization scheme for controlling the electroplated thickness across the end ADEPT die.                           | ntire<br>136      |

| Figure 5.8. The bottom interconnect photomask.                                                                                                   | 137               |

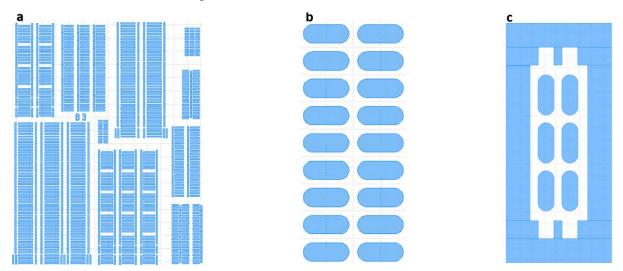

| Figure 5.9. The Cu pillar photomask.                                                                                                             | 137               |

| Figure 5.10 The Cu pillar selective activation photomask                                                                                         | 138               |

| Figure 5.11. The top interconnect photomask.                                                                                                     | 138               |

| Figure 5.12. The GSGSG probe point and solder ball mold photomask.                                                                               | 139               |

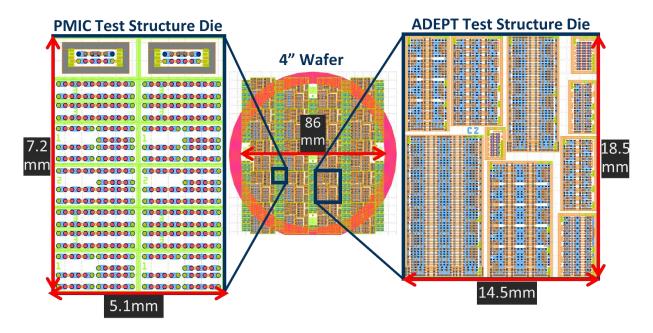

| Figure 5.13. Full wafer layout of the five-tiered photomask stack.                                                                               | 140               |

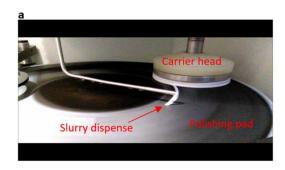

| Figure 5.14. CMP setup and rate equation.                                                                                                        | 141               |

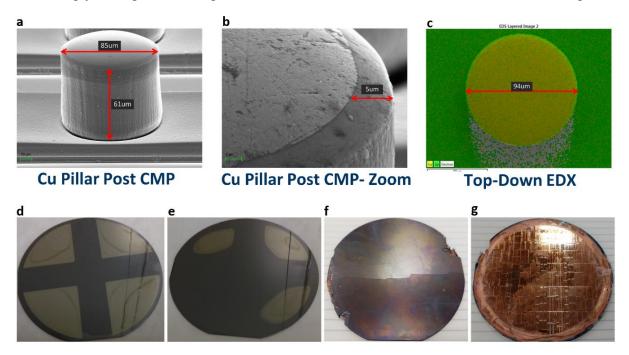

| Figure 5.15. CMP results.                                                                                                                        | 142               |

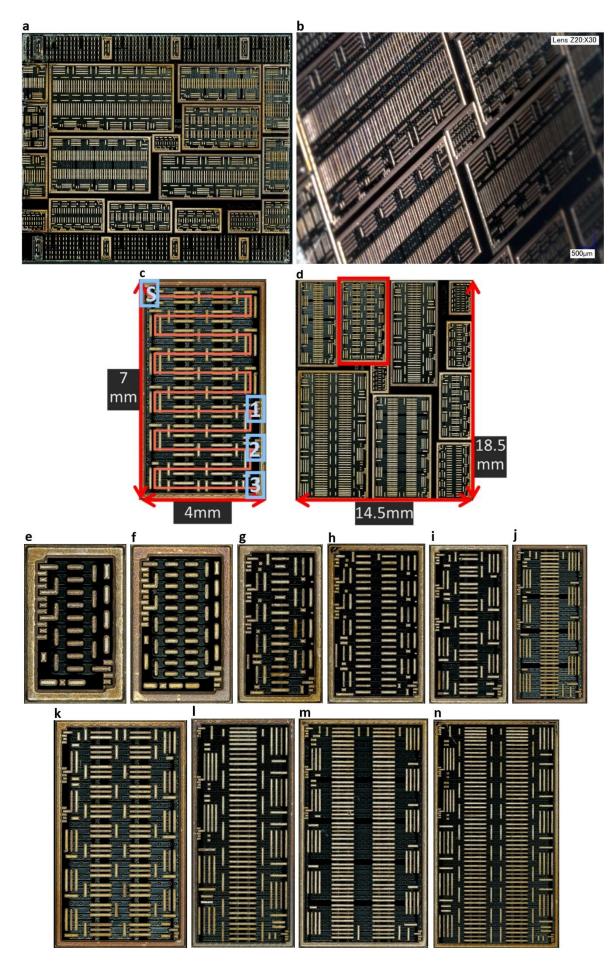

| Figure 5.16. High-resolution images of the ADEPT and PMIC dies with all ten unique ADEPT microind devices.                                       | luctor<br>143     |

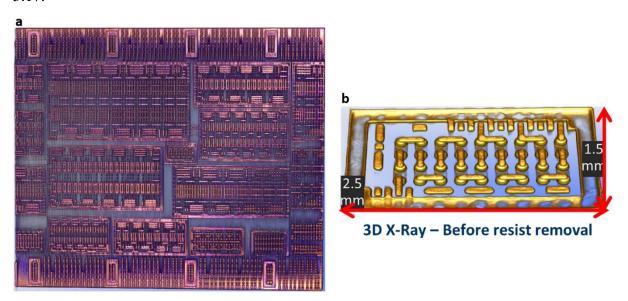

| Figure 5.17. X-ray images.                                                                                                                       | 144               |

|                                                                                                                                                  |                   |

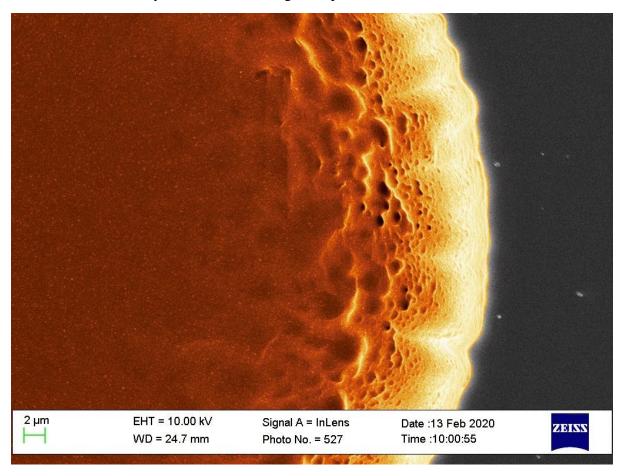

| Figure 5.18. FIB cut of the Cu pillar to top interconnect interface.                                                                             | 145               |

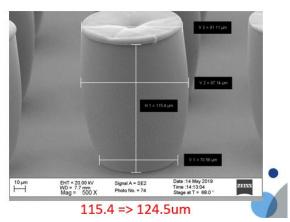

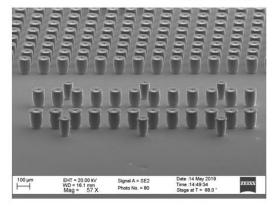

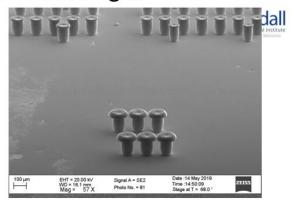

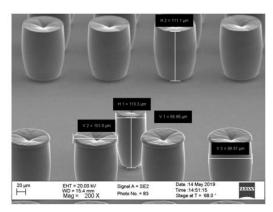

| Figure 5.18. FIB cut of the Cu pillar to top interconnect interface.  Figure 5.19. SEM micrographs of the Cu pillars and the bottom interconnect | 145<br>146        |

|                                                                                                                                                  |                   |

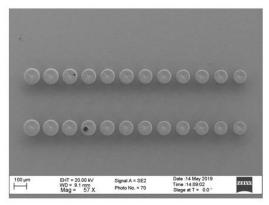

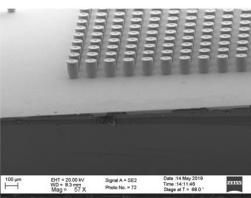

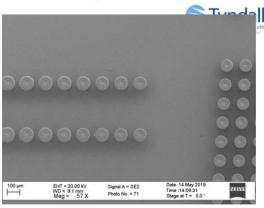

| Figure 5.19. SEM micrographs of the Cu pillars and the bottom interconnect                                                                       | 146               |

| Figure 5.19. SEM micrographs of the Cu pillars and the bottom interconnect                                                                       | 146<br>146        |

| Figure 5.19. SEM micrographs of the Cu pillars and the bottom interconnect                                                                       | 146<br>146        |

| Figure 5.19. SEM micrographs of the Cu pillars and the bottom interconnect                                                                       | 146<br>146<br>147 |

## **List of Tables**

## Chapter 2

| Table 2.1. Thick photoresist datasheet                                                                                   | 30           |

|--------------------------------------------------------------------------------------------------------------------------|--------------|

| Table 2.2. Reported 3D microinductors                                                                                    | 34           |

| Table 2.3. Relevant patents for 3D microinductors and VIAs with a clad soft magnetic core                                | 36           |

|                                                                                                                          |              |

| Chapter 3                                                                                                                |              |

| Table 3.1. Spin development procedure.                                                                                   | 95           |

|                                                                                                                          | ,,,          |

| Chapter 4                                                                                                                |              |

|                                                                                                                          |              |

| Table 4.1. Simulation parameters for physics modules 1-4.                                                                | 114          |

|                                                                                                                          |              |

| Chapter 5                                                                                                                |              |

| Table 5.1. Ansys Maxwell simulation data and 3D microinductor device metrics                                             | 148          |

| Table 5.2. Example comparison between reported state-of-the-art 2D microinductors and simulated/proto 3D microinductors. | typed<br>149 |

#### **Abstract**

Next generation microinductors with magnetically enhanced VIA technology hold great promise for power converter applications in broad technology domains such as automotive, space, high-end computing, mobile devices, radio frequency (RF), artificial intelligence (AI) and the internet of things (IoT). Microinductor VIAs enable monolithic 3D device topologies with reduced footprint, increased inductance density and minimal parasitics. These qualities are essential for emerging 2.5/3D packaging architectures that require granular point-of-load (PoL) power delivery to efficiently supply a multitude of heterogeneously integrated devices.

This thesis addresses the challenges of 3D monolithic microinductor design and fabrication, inclusive of magnetically enhanced VIAs comprising a clad laminated soft magnetic core. The current state-of-the-art utilizes 2D microinductor topologies and 2D fabrication methods, therefore significant advancement is required to enable fabrication of a novel 3D monolithic microinductor device comprising vertically oriented integrated magnetics. The major challenges addressed in this thesis fall into two main categories: 1) predictive modeling with computational lithography and computational electrochemistry to enable optimization of the VIA formation process and 2) the design and fabrication of a novel magnetically enhanced monolithic 3D microinductor device.

A major contribution from the computational lithography is the derivation of a novel polychromatic light attenuation equation that is used to produce a succinct formula comprising a complete coupling between resist photochemistry and light diffraction effects. Additionally, new photoresist exposure dose determination methods are presented that negate the need for time consuming and costly in-situ metrology. These equations and methods enable fast and accurate predictive modeling of 3D photoresist VIA latent images, which are verified by comparison to directly corresponding experimental work, with highly positive correlation. These formulas converge quickly on the average modern computer and can be readily integrated into lithography simulators. Photoresist development is then investigated, wherein spin development is identified as the optimal method for wet etching VIA latent images. With computational electrochemistry, the electroforming process of Cu VIAs is explored using the FEM in COMSOL Multiphysics to perform 2D and 3D time-dependent simulation studies. Simulations are then verified by comparison to experimental results, with highly positive correlation. Special attention is given to electroformed surface topographies, which is valuable for sensor and flip chip applications.

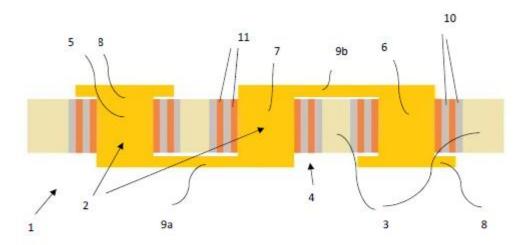

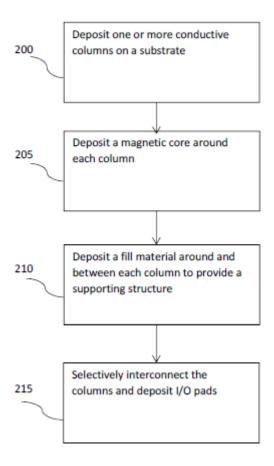

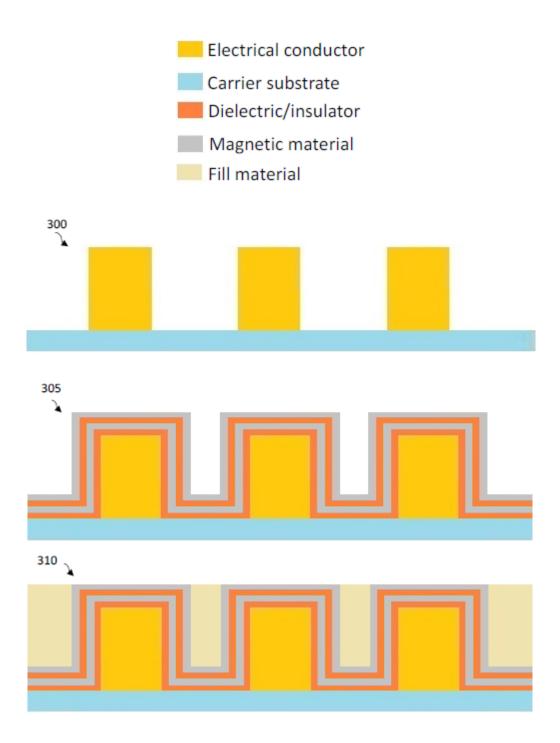

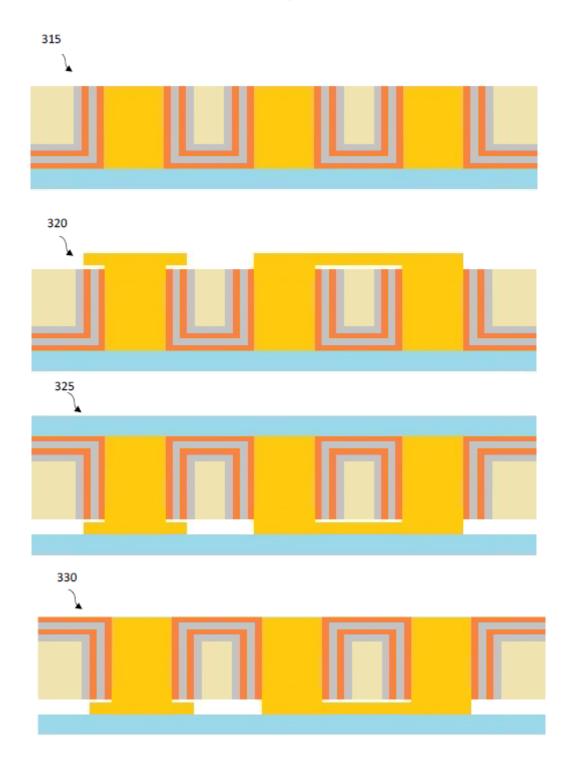

The major contributions from the microinductor device design and fabrication first include designing a unique device that meets target specifications for reduced footprint, increased inductance density and minimized parasitics. A novel fabrication process flow is next engineered to enable a vertically meandering current path with a repeating unit cell comprising a bottom interconnect, a first Cu VIA, a top interconnect and a second Cu VIA. This process flow is compatible with conformal deposition of a soft magnetic laminate (e.g., CoZrTa) for formation of a vertically oriented magnetic core clad on the Cu VIAs. Next, a 5-tiered photomask stack is designed and the corresponding SOPs are engineered. This enables fully in-house microinductor device fabrication, after which vital metrology and characterization is performed. The measured inductance density of our prototype magnetically enhanced monolithic 3D microinductor devices is 10.36 nH/mm², which is comparable to previously

reported metrics for fabricated 3D microinductors. This metric could be significantly improved in future devices by increasing the magnetic core thickness and/or optimizing the magnetic anisotropy characteristic of the integrated magnetic material and/or reducing the pillar diameter, wherein the VIA fabrication research presented in this thesis will be essential. Therefore, this novel microinductor research holds great promise for applications in next generation power converters.

## **Chapter 1 - Introduction**

A microinductor is a magnetic device that stores electrical energy in the form of a magnetic field. It is an essential component of modern integrated voltage regulators (IVRs), which use a radio frequency (RF) switch such as a metal-oxide-semiconductor field-effect transistor (MOSFET) to enable direct current (DC) voltage source modulation. This thesis investigates the design and fabrication of magnetically enhanced 3D microinductors with reduced footprint for point-of-load (PoL) power conversion in integrated circuits (ICs) and increased compatibility with emerging 2.5D and 3D advanced packaging architectures. These next generation microinductors hold great promise for power converter applications in technology domains such as automotive, space, high-end computing, mobile devices, radio frequency (RF), artificial intelligence (AI) and the internet of things (IoT). To understand the role of the microinductor in a power converter, a buck converter is first presented below.

#### 1.1. Integrated magnetics for efficient DC-DC conversion with a buck converter

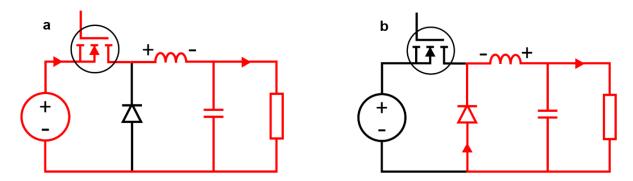

By alternating between on and off states, the MOSFET cyclically charges and discharges a microinductor, which powers a load during the MOSFET off state, as shown in Fig. 1.1.

**Figure 1.1. Buck converter inductor charging and discharging modes. a** On-state. Current flows through the MOSFET and the inductor is charging. **b** Off-state. Current flows through the diode and the inductor is discharging.

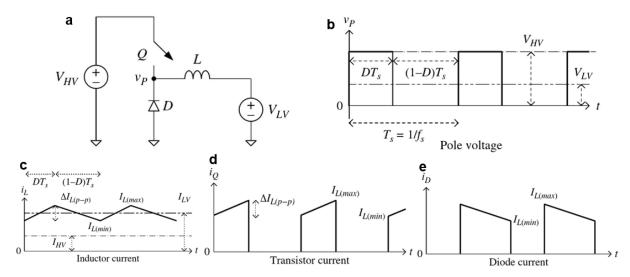

The detailed operation of a buck converter is shown in Fig. 1.2, which depicts voltage and current waveforms during the MOSFET on/off states.

Figure 1.2. Buck converter operation in continuous conduction mode (CCM)<sup>1</sup>. a Buck converter schematic, where  $v_P$  is the pole voltage. b Pole voltage vs. time, where D, the duty cycle defined as  $D = V_{LV}/V_{HV}$ , sets the output voltage.  $DT_s + (1-D)T_s = T_s$  is the switching period in s, which is the inverse of the switching frequency,  $f_s = 1/T_s$  in s<sup>-1</sup>. During  $DT_s$ , the switch is closed (MOSFET conducting),  $v_P = V_{HV}$  and the inductor is charging. During  $(1-D)T_s$ , the switch is open (MOSFET not conducting),  $v_P = 0$  and the inductor is discharging. c Inductor current vs. time. The inductor charges during  $DT_s$  and discharges during  $(1-D)T_s$ , where  $I_{L(max)} - I_{L(min)} = \Delta I_{L(p-p)}$  is the current ripple magnitude. d MOSFET current vs. time. e Diode current vs. time. (a-e reprinted from ref. 1 with kind permission from John Wiley & Sons. Copyright 2018 John Wiley & Sons Ltd.)

As opposed to a linear power converter, the buck converter enables high efficiency step down of the supply voltage with minimal Joule heating, which is essential for modern electronic devices<sup>2</sup>. This is made possible by the energy storage capability of the microinductor, which operates by the principle of Faraday's Law of Induction, equation (1.1), where  $\mathcal{E}$  is the electromotive force (EMF) in V, N is the number of inductor windings/turns and  $\Phi_B$  is the magnetic flux in V·s<sup>3</sup>.

$$\mathcal{E} = -N \frac{\partial \Phi_B}{\partial t} \tag{1.1}$$

Consequently, a time variant magnetic field induces an EMF with proportion to the number of inductor windings/turns. The magnetic field strength, B in tesla (T) or kg·s<sup>-2</sup>·A<sup>-1</sup>, as described by equation (1.2), is a function of  $\mu_r$ , the relative permeability of a material,  $\mu_0$ , vacuum permeability in H·m<sup>-1</sup> or kg·m·s<sup>-2</sup>·A<sup>-2</sup> and H, the auxiliary magnetic field in A·m<sup>-1</sup>  $\frac{4}{2}$ .

$$B = \mu_r \mu_0 H \tag{1.2}$$

The magnetic field strength can be increased by using a material with a relative permeability greater than unity, which in-turn, boosts the induced EMF. As an example, some soft magnetic materials such as Metglas have a relative permeability of  $1,000,000^{5}$ .

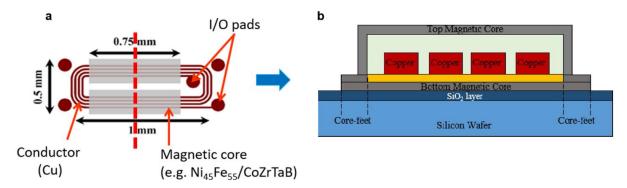

**Figure 1.3. Magnetic core microinductor schematic and cross-section. a** Top-down schematic of a magnetic core racetrack microinductor with four turns<sup>6</sup>. (Reprinted from ref. 6 with kind permission from IOP Publishing, Ltd. Copyright 2016 IOP Publishing, Ltd.; permission conveyed through Copyright Clearance Center, Inc.) **b** Cross-section of  $\mathbf{a}^{7}$ . (Reprinted from ref. 7 under the Creative Commons Attribution 4.0 International License.)

Therefore, in addition to the conductor cross-section and device topology, the energy storage capability of a microinductor is proportional to its size (e.g., the number of windings/turns) and is a function of its material properties. These parameters contribute to inductance (L), as described by equation (1.3), where L in units of henries (H) or  $kg \cdot m^2 \cdot s^{-2} \cdot A^{-2}$  is equal to the ratio of the magnetic flux,  $\Phi_B$ , to the current, I in  $A^8$ .

$$L = \frac{\Phi_B(I)}{I} \tag{1.3}$$

Consequently, the inductance is a measure of the energy storage capability of an inductor. An alternative formulation for the induced EMF is equation (1.4), where L is the inductance and I is the current<sup>8</sup>.

$$\mathcal{E} = -L \frac{\partial I}{\partial t} \tag{1.4}$$

Since  $\mathcal{E} \propto L$ , the required inductance value is proportional to the amount of electrical energy that must be stored in the form of a magnetic field. Therefore, a high MOSFET switching frequency can be used with a low transient energy storage requirement, thereby enabling a small inductor footprint for granular PoL power conversion. Equation (1.5) demonstrates the inverse relationship between inductance and switching frequency and Fig. 1.4. depicts a reduction in the inductor footprint as frequency is increased  $\frac{9.10}{2}$ .

$$\Delta I_{L(p-p)} = \frac{V_{LV}D}{f_SL} \tag{1.5}$$

|                        | Footprint (mm <sup>2</sup> ) | Volume<br>(mm³) | Frequency<br>MHz |

|------------------------|------------------------------|-----------------|------------------|

| Power<br>Management IC |                              |                 |                  |

| Magnetic Inductors     | 50                           | 150             | 1                |

|                        | 30                           | 25              | 5                |

| Capacitors             | 7.0                          | 3.5             | 20               |

|                        | 2.0                          | 1.0             | 50-100           |

**Figure 1.4. Inductor footprint vs. frequency**<sup>9,10</sup>. (Reprinted from ref. 10 with kind permission from IEEE. Copyright 2010 IEEE.)

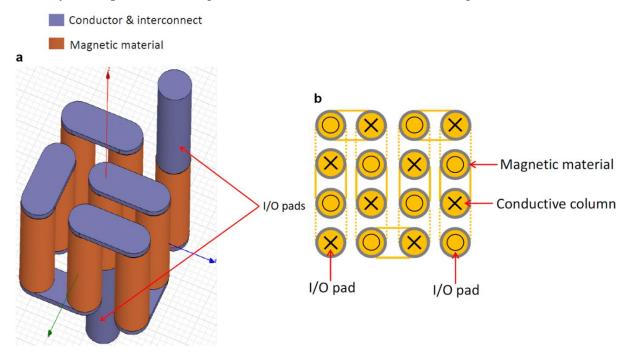

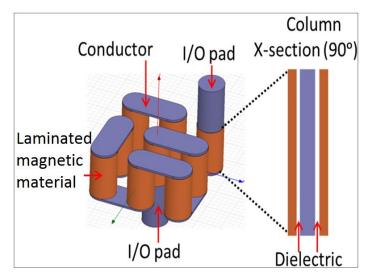

In addition to frequency related size reduction, the microinductor footprint can be further reduced by transitioning from a 2D to a 3D winding topology 11,12,13,14,15,16,17,18. Using an architectural analogy, transitioning from a 2D to a 3D winding topology is equivalent to modifying the microinductor floor area ratio (FAR), whereby the gross floor area (microinductor volume) to plot area (substrate surface area) ratio is significantly increased, which is a core concept behind vertical architecture (e.g., skyscrapers) 19,20. In 3D microinductors, a vertically meandering current path is enabled by selectively interconnecting an array of Cu pillars or through substrate vias (TSVs), as shown in Fig. 1.5.

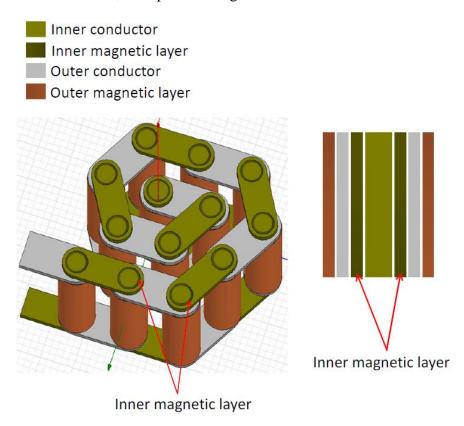

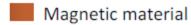

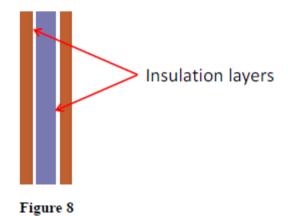

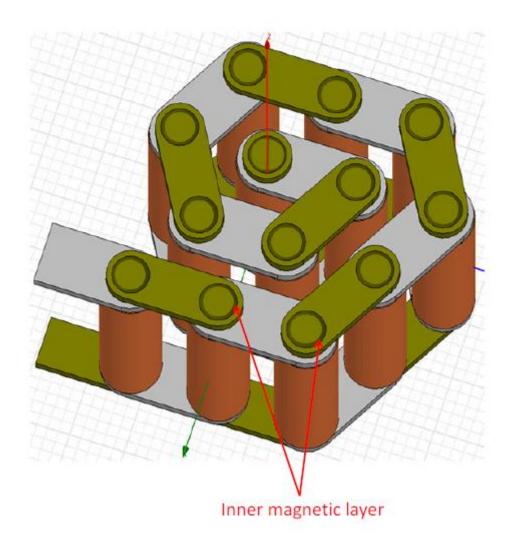

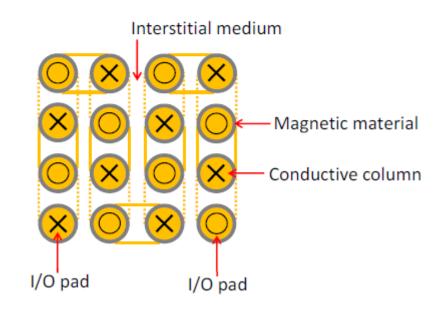

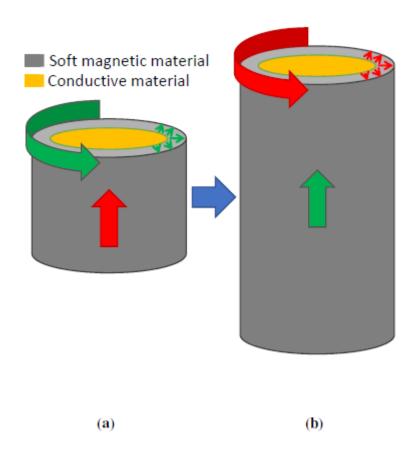

**Figure 1.5. 3D microinductor schematics with Cu pillars laminated in a magnetic material**<sup>21</sup>. **a** Angled view. **b** Top-down view. Downward traveling current is marked with an "X" and upward traveling current is marked with an "O".

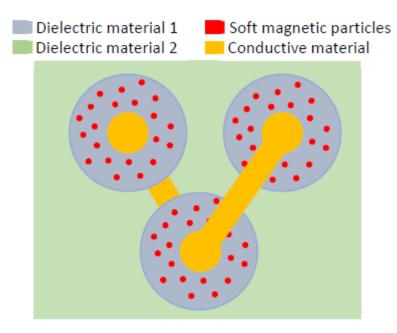

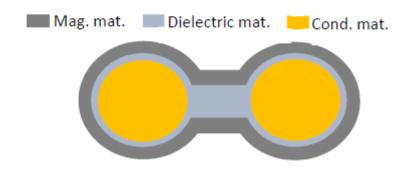

For example, the four turn 2D microinductor depicted in Fig. 1.3a has a footprint of 0.5 mm<sup>2</sup>, whereas an equivalent four turn 3D microinductor with 4x100 µm diameter square packed TSVs and a pitch of 200 µm would have a footprint of 0.09 mm<sup>2</sup>, which is a size reduction of 5.6x (assuming equivalent device parameters (e.g., inductance, dc resistance, saturation current and operating frequency) and magnetic material parameters (e.g., resistivity, coercivity, saturation magnetization, relative permeability and anisotropy field)). Furthermore, laminating

the Cu pillars in a magnetic material significantly boosts inductance by equation (1.2), while simultaneously functioning as an in-situ shield against electromagnetic interference (EMI)<sup>22,23</sup>. Together, these design options offer a promising solution for next-generation microinductors with reduced footprint, in-situ EMI shielding, high inductance density and enhanced compatibility with emerging 2.5/3D packaging architectures.

#### 1.2. Research goals and challenges

#### Goals:

- Conduct a literature review on high-throughput (fast) and cost-effective (inexpensive) vertical interconnect access (VIA) fabrication techniques and reported 3D microinductors, wherein these qualities are essential for modern semiconductor manufacturing process flows.

- 2. Develop complementary metal-oxide-semiconductor (CMOS) compatible fabrication methods for next generation 3D integrated magnetic devices by incorporating novel magnetic lamination methods into the full device fabrication process flow. Herein, CMOS compatible refers to low-temperature (e.g., <200 °C) cleanroom processing (e.g., silicon wafers that are not contaminated with trace metals such as Ni, Fe, Ag, Au, etc.)<sup>12,13</sup>.

- 3. Demonstrate high-throughput and low-cost scalable processing options for novel 3D micro-magnetic inductor structures, wherein scalability enables integration of small-scale, research laboratory process flows into high-volume industrial manufacturing.

Research challenges related to the achievement of Goals 2 and 3:

- 1. Diffraction effects degrade VIA mold resolution in photolithography. To address this, computational lithography is required to enable predictive modeling of diffraction effects during photoresist exposure. This entails:

- Deriving a new polychromatic light attenuation equation for compatibility with broad-spectrum exposure, as is typical in mask aligner photolithography (e.g., with Hg bulbs),

- o Developing novel methods for photoresist cross-link determination, and

- o Using an exact scalar diffraction equation for a circular diffractor.

- 2. Electroplating is a complex process, wherein tailoring the topography of the electroplated surface (e.g., flat for flip-chip applications) requires knowledge of electroactive species mass transport dynamics and electrode reaction kinetics. To enable this, the finite element method (FEM) in COMSOL Multiphysics is needed to perform computational electrochemistry for predictive modeling of the Cu electroplating process.

- 3. Feasible 3D microinductor device design topologies that comprise Cu pillars clad in a vertically oriented magnetic material and arranged in a selectively interconnected array have not yet been explored. This design space needs to be investigated to identify promising prototypes, which must be enabled by utilizing wafer level layout for stacked photomask alignment through to tapeout.

- 4. Wafer transfer from the plating lab to the MEMS fabrication lab at Tyndall requires CMOS compatible Si wafers to enable sputtering of vertically oriented magnetic material on Cu pillars. A CMOS compatible process flow for fabricating Cu interconnects is thus required to enable monolithic microinductors comprising Cu VIAs clad in a laminated soft magnetic material.

- 5. Standard operating procedures (SOPs) for the novel fabrication process flow do not yet exist and must be engineered.

- 6. These novel magnetically enhanced 3D microinductors have never before been prototyped and must be fabricated with in-house equipment and processing.

#### 1.3. Thesis scope

This thesis addresses the goals and challenges outlined in section 1.2, wherein the research was conducted at the interface between lithography, electrochemistry and integrated magnetics. The key research focus was to advance the state-of-the-art by transitioning from 2D microinductors to 3D magnetically enhanced monolithic microinductor device topologies for scalable applications in power supply in/on package/chip (PwrSiP/PwrSoC) and 2.5/3D advanced packaging architectures. Fundamental to this goal was the development of a high-throughput and cost-effective VIA fabrication method for use in a novel 3D magnetically enhanced microinductor device design. Notable research requirements included computational lithography, computational electrochemistry, device design, process design, establishing SOPs and performing continuous validation with metrology and characterization. Furthermore, my research culminated in spearheading a full microinductor device fabrication effort, which resulted in fabricated prototypes of novel 3D magnetically enhanced microinductors.

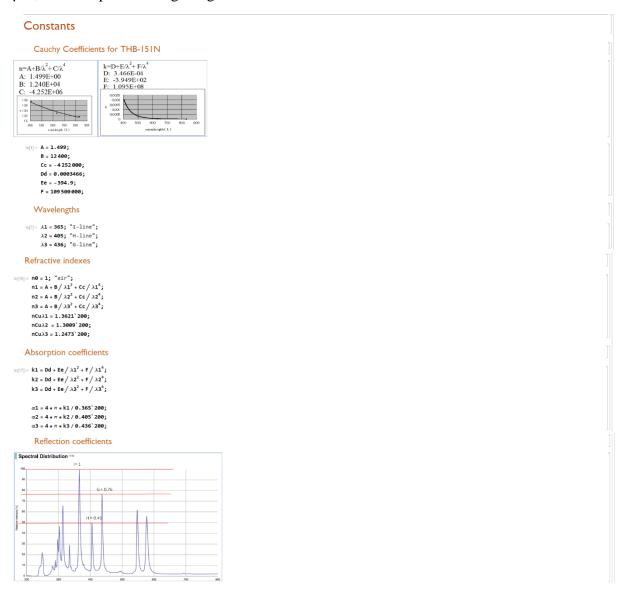

Chapter 2 (Goal 1) first establishes the context of cutting-edge VIA applications in 2.5D and 3D advanced packaging architectures, microelectromechanical systems (MEMS) and emerging microinductor devices. Following this, VIA fabrication methods are discussed, wherein photolithography is identified as a promising fabrication option. A detailed review of thick photoresists is then presented and THB-151N is selected as a suitable photoresist. Finally, reported 3D microinductors with VIAs are reviewed and a microinductor device comprising VIAs clad in magnetic laminations is proposed as a novel design option.

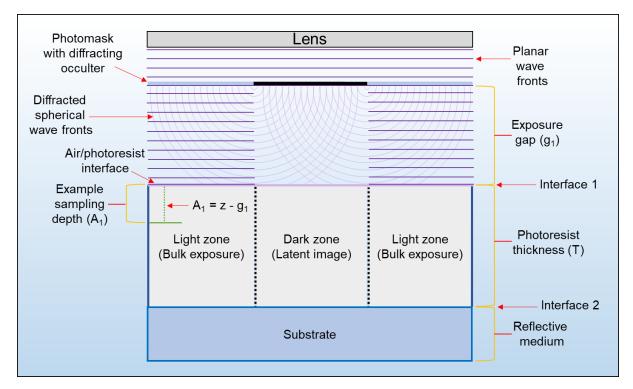

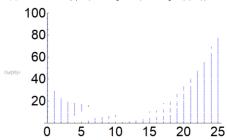

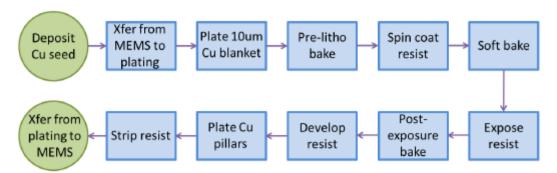

Chapter 3 (Challenge 1) addresses the role of light diffraction effects in photolithography, which can significantly affect the target photoresist relief mold geometry. A new polychromatic light attenuation equation is derived, presented and applied along with an exact scalar diffraction formula to enable predictive modeling of VIA latent image profiles in Wolfram Mathematica. VIA latent image simulations are then compared to directly corresponding experimental work, with highly positive correlation. The mechanism of photoresist development, wherein a latent image is etched into a relief mold, is next investigated and spin development is suggested as a suitable development methodology.

Chapter 4 (Challenge 2) uses the FEM in COMSOL Multiphysics to simulate 3D electrode growth during Cu VIA electroplating. The fundamental mass-transport and reaction kinetics equations are discussed and implemented in four distinct physics modules, which are then combined into a multiphysics time-dependent simulation. Consistency checks are performed between 2D and 3D electrode geometry growth simulations, which are then compared to

directly corresponding experimental work, with highly positive correlation. This study provides insight into the electroforming process of Cu VIAs with special attention to pillar topography.

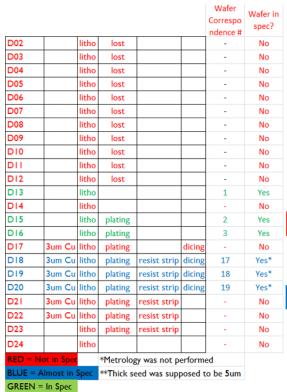

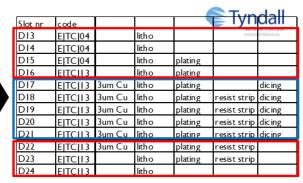

Chapter 5 (Goals 2-3, Challenges 3-6) describes the target 3D microinductor device design, process design, photomask layout/design, key aspects of the generated SOPs, key fabrication steps and the corresponding characterization and metrology. The target device design is presented in a detailed 2D x-z cross-sectional schematic, which is achieved by a 16-step process flow. The layout designs entail a 5-tiered photomask stack for fabricating 14 discrete 3D microinductor devices on a single 4" wafer. Key aspects of the corresponding SOPs and challenging fabrication steps are then discussed with a special focus on chemical mechanical polishing (CMP). Finally, light microscope, scanning electron microscope (SEM) and X-ray images of the fabricated 3D microinductor devices are presented along with the corresponding metrology and characterization results.

Chapter 6 provides a summary of the thesis and discusses potential future work. A promising future option for high aspect ratio (HAR) VIA fabrication with photolithography is to use an in-situ photomask. This technique eliminates the photomask air gap while simultaneously introducing a long pass (LP) filter, which could prove highly effective for reducing diffraction effects. This fabrication option could first be simulated in Wolfram Mathematica with my VIA latent image model, which would greatly assist in HAR VIA fabrication. Additionally, and for high frequency (HF) applications, a thick dry film could be utilized for thickness uniformity and to enable hollow VIA fabrication with minimal electroplating duration. Both of these VIA fabrication options are promising for realizing advanced 3D microinductors with maximum efficiency, minimum footprint and enhanced compatibility with emerging 2.5/3D packaging architectures. Furthermore, and due to its high-throughput capability, my latent image model could be developed into an on-the-go app for ease of use during experimentation in the laboratory. Finally, and as an alternative to sputtering, Cu pillars clad in a vertically oriented laminated soft magnetic core could be realized by selectively etching Cu in an electroplated [Ni45Fe55/Cu]n stack and back filling with a low viscosity photoresist for mechanical stability.

Click to skip to next chapter.

#### 1.4. References

- Hayes, J. G. & Goodarzi, G. A. Electric Powertrain: Energy Systems, Power Electronics and Drives for Hybrid, Electric and Fuel Cell Vehicles. *Wiley*, 306-312 (2018).

- 2. Rao, D. P. Design of DC-DC buck converter for airborne radar application.

International Journal & Magazine of Engineering, Technology, Management and Research, 28-33 (2015).

- 3. Hayt, W. H. Engineering electromagnetics. *McGraw-Hill Inc.*, **5**, 313 (1989).

- 4. Jiles, D. Introduction to magnetism and magnetic materials. *CRC Press, Taylor & Francis Group*, **3**, 11 (2016).

- 5. Lamichhane, T. N. *et al.* Additive manufacturing of soft magnets for electrical machines—a review. *Materials Today Physics* **15**, 100255 (2020).

- 6. Anthony, R., Laforge, E., Casey, D. P., Rohan, J. F. & O'Mathuna, C. High-aspect-ratio photoresist processing for fabrication of high resolution and thick micro-windings. *J. Micromech. Microeng.* **26**, 105012 (2016).

- Anthony, R., Mathúna, C. Ó. & Rohan, J. F. Palladium Activated Self-Assembled Monolayer for Magnetics on Silicon Applications. *Physics Procedia* 75, 1207–1213 (2015).

- 8. Purcell, E. M. & Morin, D. J. Electricity and Magnetism. *Cambridge University Press*, 364 (2013).

- 9. O'Mathúna, C. Power Supply on Chip (PwrSoC). PwrSoC Conference, 14 (2011).

- 10. Wang, N. et al. Integrated magnetics on silicon for power supply in package (PSiP) and power supply on chip (PwrSoC). *IEEE*, (2010).

- Heterogeneous Integration Roadmap. Chapter 10: Integrated Power Electronics. (IEEE EPS, 2019).

- 12. Le, H. T. *et al.* Fabrication of 3D air-core MEMS inductors for very-high-frequency power conversions. *Microsyst Nanoeng* **4**, 17082 (2018).

- Mathúna, C. O., Ningning Wang, Kulkarni, S. & Roy, S. Review of Integrated Magnetics for Power Supply on Chip (PwrSoC). *IEEE Trans. Power Electron.* 27, 4799–4816 (2012).

- 14. Su, Y. High Frequency, High Current 3D Integrated Point-of-Load Module. *Virginia Polytechnic Institute and State University*, (2014).

- 15. VanAckern, G. Design Guide for CMOS Process On-Chip 3D Inductor using Thru-

- Wafer Vias. Boise State University Theses and Dissertations, (2011).

- Wang, N. et al. High frequency DC-DC converter with co-packaged planar inductor and power IC. in 2013 IEEE 63rd Electronic Components and Technology Conference 1946–1952 (IEEE, 2013). doi:10.1109/ECTC.2013.6575844.

- 17. Zia, M., Oh, H. & Bakir, M. S. Post-CMOS Fabrication Technology Enabling

Simultaneous Fabrication of 3-D Solenoidal Micro-Inductors and Flexible I/Os. *IEEE Trans. Compon., Packag. Manufact. Technol.* **8**, 2039–2044 (2018).

- Jun Zou et al. Development of three-dimensional inductors using plastic deformation magnetic assembly (PDMA). IEEE Trans. Microwave Theory Techn. 51, 1067–1075 (2003).

- 19. McNeill, D. The volumetric city. *Progress in Human Geography* **44**, 815–831 (2020).

- 20. Gottmann, J. Why the Skyscraper? Geographical Review 56, 190 (1966).

- 21. O'Mathuna, C. et. al. A Vertical Magnetic Structure for Integrated Power Conversion.

Patent Application PCT/EP2019/077978, (2020).

- 22. Dijith, K. S., Aiswarya, R., Praveen, M., Pillai, S. & Surendran, K. P. Polyol derived Ni and NiFe alloys for effective shielding of electromagnetic interference. *Mater. Chem. Front.* **2**, 1829–1841 (2018).

- 23. Sun, X., Van der Plas, G. & Beyne, E. Improved Staggered Through Silicon Via Inductors for RF and Power Applications. in 2018 IEEE 68th Electronic Components and Technology Conference (ECTC) 1692–1697 (IEEE, 2018).

## Chapter 2 – State-of-the-art: VIAs in 2.5D and 3D advanced packaging architectures, MEMS and emerging microinductor devices

#### 2.1. Introduction

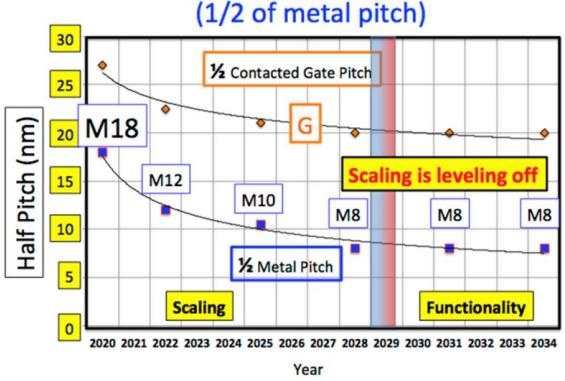

Omnipresent in the semiconductor industry, Moore's law states that the number of metal-oxide-semiconductor field-effect transistors (MOSFETs) in a microchip doubles every 1.5-2 years<sup>1</sup>. The predictive power of Moore's law held firm throughout the 1970s and well into the 21<sup>st</sup> century<sup>1</sup>. However due to fundamental limits such as the quantum tunnelling property of electrons causing off-state leakage currents, as required by Heisenberg's uncertainty principle<sup>1</sup>, transistor scaling is predicted to slow pace so significantly that in 2015 even Moore himself stated that, "I see Moore's law dying here in the next decade or so"<sup>2</sup>. Correspondingly, the International Roadmap for Devices and Systems (IRDS) More Moore (MM) focus team reported in 2020 that MOSFET scaling is expected to saturate by around 2028 with a half-pitch of 7-8 nm, as shown in Fig. 2.1<sup>3</sup>.

## Reconnecting with NTRS/ITRS Technology Nodes

**Figure 2.1. CMOS dimensional scaling projection from 2020-2034**<sup>4</sup>. (Reprinted from ref. 4 with kind permission from IEEE. Copyright 2020 IEEE.)

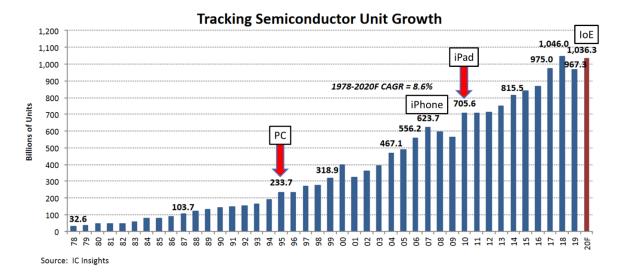

With the end of MOSFET scaling on the horizon, demand is nevertheless accelerating for enhanced mobile devices, advanced sensors and high-end computers with increased functionality, minimal power loss and maximum power density. As an example, the semiconductor unit growth from 1978-2020 is shown in Fig 2.2.

**Figure 2.2. Semiconductor units shipped per year from 1978-2020**<sup>5</sup>. The CAGR is 8.6%. (Reprinted from ref. 5 with kind permission from IC Insights.)

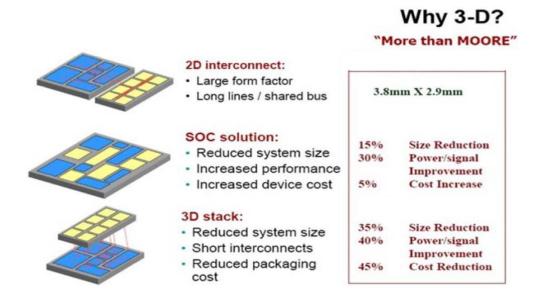

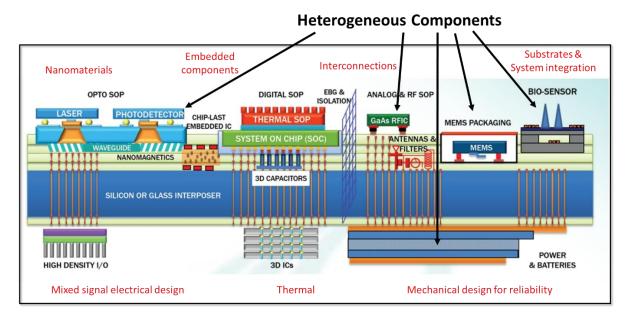

Accordingly, the number of devices connected to the internet of things (IoT) is expected to increase by a factor of 200 over the next several years. To prepare for this, the International Technology Roadmap for Semiconductors (ITRS) designated the More than Moore (MtM) concept as one of the key focus areas for the semiconductor industry in their 2015 executive report. MtM refers to the system in package (SiP) and system on chip (SoC) integration of non-digital (non-complementary metal oxide semiconductor (CMOS)) devices such as sensors, voltage regulators and energy harvesters that do not scale according to Moore's law. The unique scaling metric of SiP and SoC however, as denoted by compacting increasingly more devices into a constant substrate area, is nonetheless expected to progress at a pace according to Moore's law with a compound annual growth rate (CAGR) of 41% for the next two decades. Due to this, MtM is a promising new technology domain with great potential to fulfil the performance, functionality and power density requirements of cutting-edge semiconductor devices for many years to come.

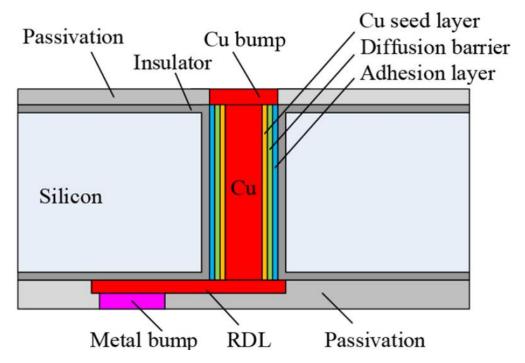

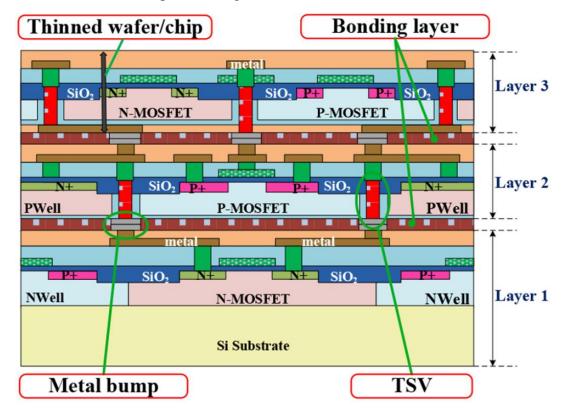

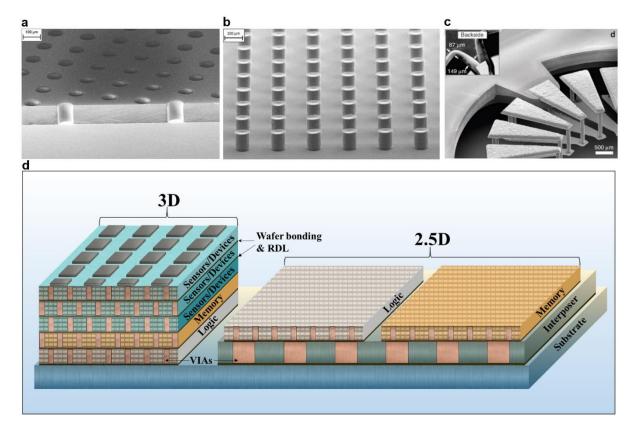

Enabling MtM requires transitioning from planar devices and planar device arrays to vertical device structures and vertically stacked device architectures. This has been defined as the 3<sup>rd</sup> age of semiconductor scaling<sup>4</sup>. Densely packed skyscrapers in the metropolis of today are analogue to the 3D microchip packages of the future. Like steel beams that connect successive levels, through substrate vias (TSVs) connect successive chips in a 3D package. A TSV comprises a vertical interconnect access (VIA) conductive material, such as Cu, that interconnects the top and bottom surfaces of a substrate or chip, as depicted in Fig. 2.3.

**Figure 2.3. Schematic of a TSV cross-section**<sup>8</sup>. (Reprinted from ref. 8 with kind permission from Elsevier. Copyright 2019 Elsevier B.V.)

Additionally, VIAs can also be used to create monolithic devices with stacked conductor layers (e.g., meander microinductors  $^{9,10}$ ) for integration with 3D packaging architectures, an x-z cross-section of which is depicted in Fig. 2.4.

**Figure 2.4. Schematic cross-section of a 3D package**<sup>§</sup>. VIAs are colored red. (Reprinted from ref. 8 with kind permission from Elsevier. Copyright 2019 Elsevier B.V.)

By using VIAs, heterogeneous chips can be stacked like floors in a building with benefits such as: increased functionality, enhanced design versatility, high efficiency due to minimal interconnect parasitics (e.g., inductance, capacitance and resistance) and increased power density<sup>8,11,12,13,14,15,16,17,18,19,20,21,22,23,24</sup>. Due to this, TSVs are considered as, "the heart of 3D integration"<sup>20</sup>. The benefits of 3D integration are demonstrated in Fig 2.5.

**Figure 2.5. The benefits of 3D integration**<sup>2</sup>. (Reprinted from ref. 7 with kind permission from the Semiconductor Industry Association.)

Future 3D microchip architectures offer the potential for highly integrated packages that comprise from the top-downwards multiple heterogeneous device and sensor layers, a high bandwidth memory (HBM) stack, a CMOS logic/processor layer, a voltage source and finally a heat sink, where each stacked layer uses VIAs as vertical interconnects. Regarding VIA size, a cutting-edge HBM dynamic random access memory (DRAM) die uses an array of  $\approx 5,000$  TSVs with a thickness of 50  $\mu$ m and a pitch of 50  $\mu$ m, which corresponds to an aspect ratio (AR) of two with an equal line to space (l/s) ratio<sup>25</sup>. Example VIA dimensions in the device and sensor layers for 3D integration include thickness (T,  $\mu$ m) =  $5^{26,27}$ ,  $100^{8,28}$ ,  $200^{29,30}$ ,  $230^{31}$ ,  $300^{32}$  and diameter (D,  $\mu$ m) =  $15^{30}$ ,  $20^{26,27}$ ,  $50^{32}$ ,  $80^{29}$ ,  $90^{31}$ ,  $100^{28}$  with ARs ranging from 0.25-13.3.

Whilst 3D microchip packaging offers significant benefits, it can be expensive and technically difficult to realize due to for example, warping during multilayer wafer bonding with heterogeneous materials, excess heat generation and a mismatch of the coefficient of thermal expansion (CTE) between packaged layers/materials that causes stress during operation 8,33,34,35. To circumvent these difficulties, a simpler and more cost-effective advanced packaging technique has emerged that uses interposer substrates with chips bonded to the surface and VIAs embedded inside for enhanced input/output (I/O) redistribution 8,36,37. Since this technique uses VIAs but decouples their fabrication from the sensors, devices and CMOS integrated circuits (ICs) on the interposer surface, it acts as a bridge between 2D and 3D technology and is therefore known as 2.5D packaging, as depicted in Fig. 2.6.

**Figure 2.6. Schematic of a 2.5D package**<sup>37</sup>. VIAs are colored blue and extend through the Si interposer. (Reprinted from ref. 37 with kind permission from Springer Nature. Copyright Springer-Verlag Berlin Heidelberg 2013.)

In addition to enabling reduced interconnect lengths and reduced form factors, 2.5D packaging has the potential to eliminate CTE mismatch induced stress between adjacent heterogeneous chips by using an interposer material with a low Young's modulus, such as an acrylic polymer, which has already been demonstrated as a stress mitigating dielectric liner in TSVs<sup>38,39,40,41,42</sup>. For a sense of scale, interposers are usually around 100-150 µm thick and comprise thousands of VIAs that typically range from 50-200 µm in diameter (AR=0.75-3)<sup>8,25</sup>.

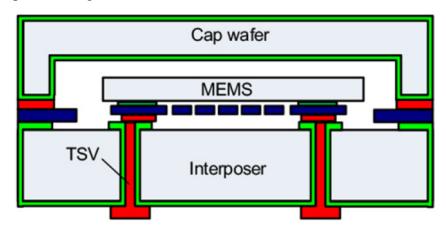

In addition to providing vertical interconnect access, multifunctional TSVs are increasingly being used in emerging devices such as 3D microinductors and enhanced microelectromechanical systems (MEMS) sensors and actuators. For example, in MEMS, it is often necessary to vacuum seal device components (e.g., the electrical wiring) from the surrounding environment to prevent detrimental chemical reactions such as corrosion and erosion from degrading device sensitivity. Wafer level vacuum packaging (WLVP) products have been commercialized that use TSVs as I/O interconnects for vacuum sealed MEMS devices, as depicted in Fig. 2.7, such as inertial sensors 43,44 and RF transceivers 45.

**Figure 2.7. MEMS WLVP with TSVs for I/O**<sup>8</sup>. (Reprinted from ref. 8 with kind permission from Elsevier. Copyright 2019 Elsevier B.V.)

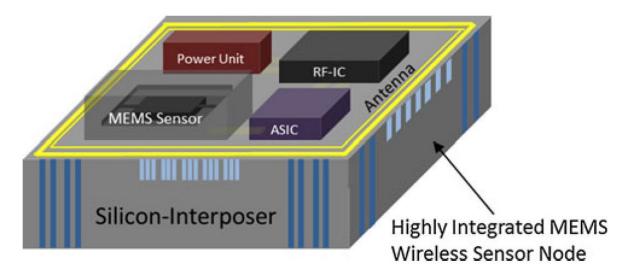

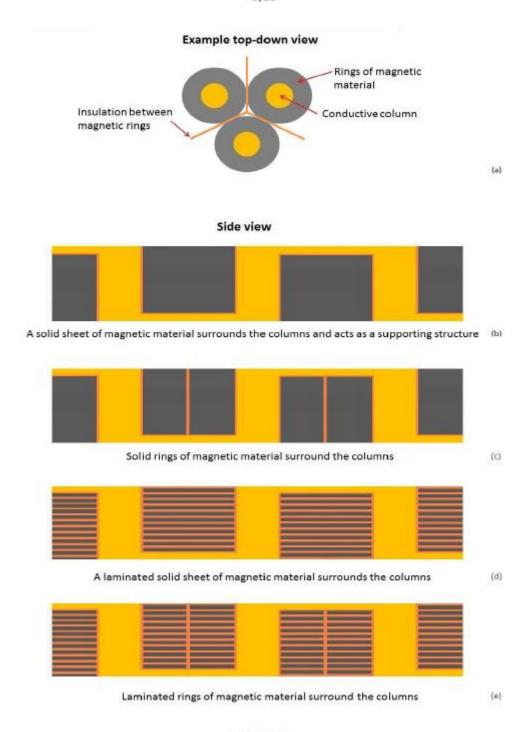

Using VIAs in WLVP hugely reduces the packaging cost and footprint by about 5-10x when compared to traditional topologies, which has been an essential facilitator of MEMS integration into consumer electronics and mobile devices over the last decade<sup>8</sup>. In 3D microinductors, TSVs enable a vertically meandering current path with a high volume and small footprint while simultaneously providing structural support<sup>46</sup>. Furthermore, microinductor TSVs can be made hyperfunctional by using VIAs with a clad soft magnetic core that significantly boosts inductance and reduces EMI, as depicted in Fig. 2.8<sup>46</sup>.

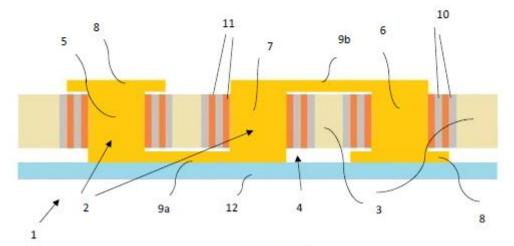

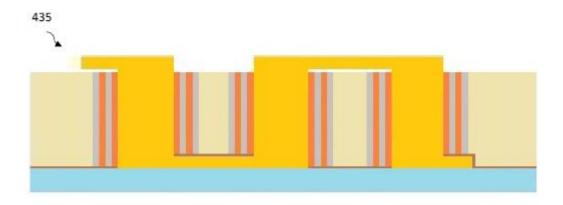

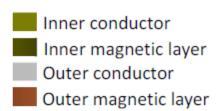

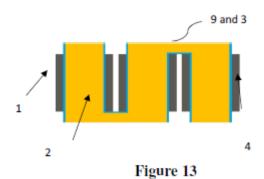

Figure 2.8. Coupled 3D microinductor with hyperfunctional VIAs coated in a laminated soft magnetic material. This schematic is from the Tyndall ADEPT group patent (PCT/EP2019/077978) entitled, "A vertical magnetic structure for integrated power conversion".

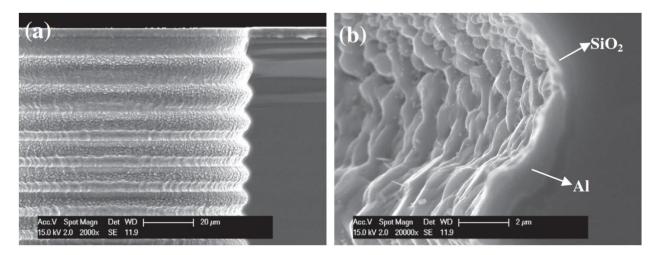

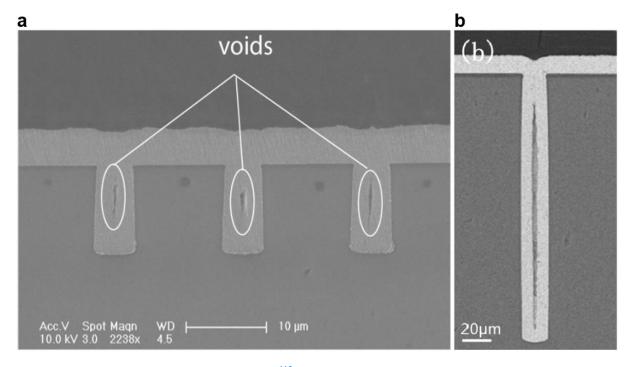

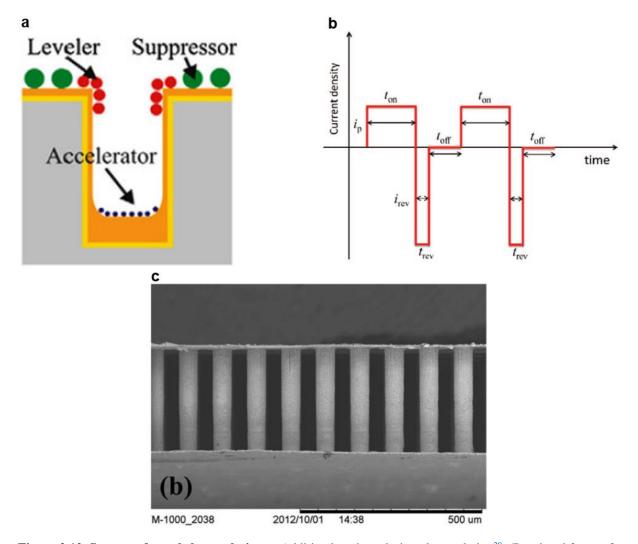

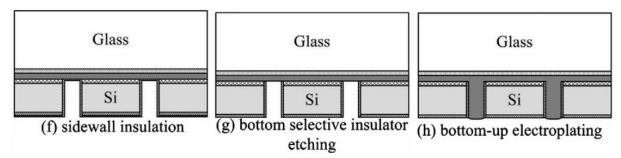

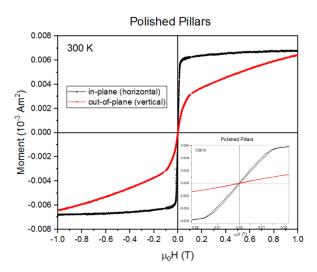

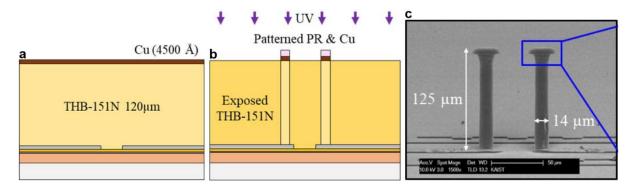

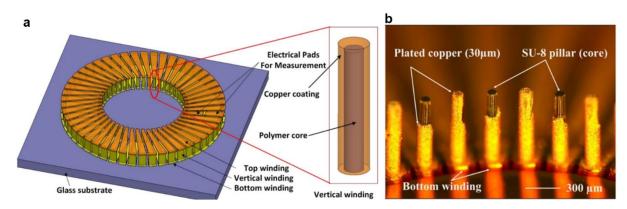

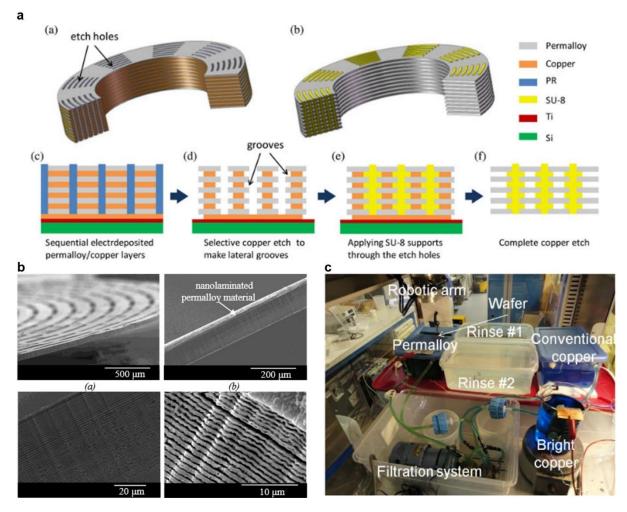

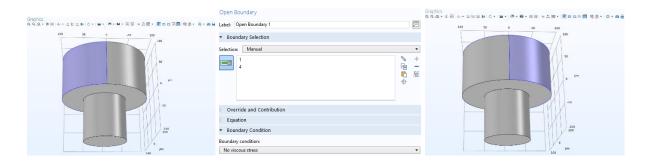

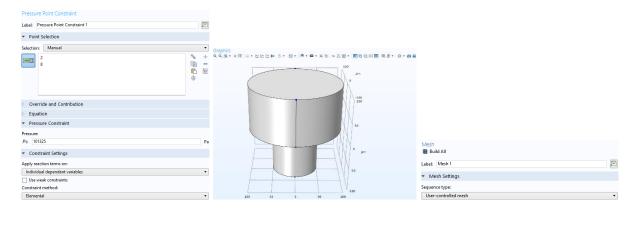

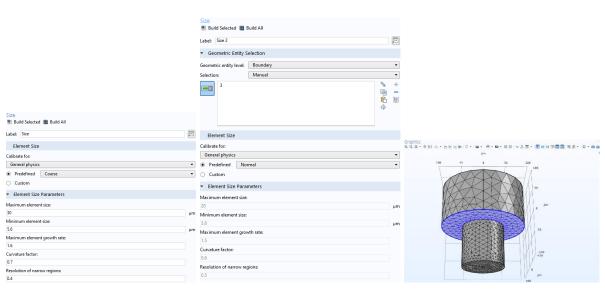

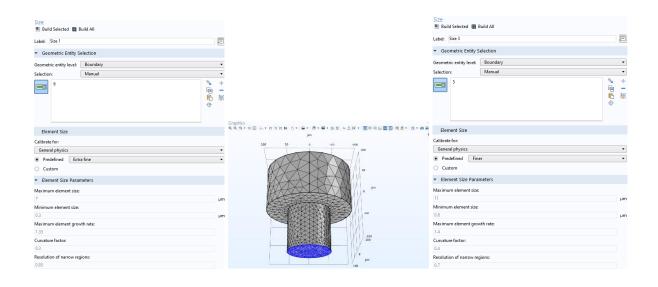

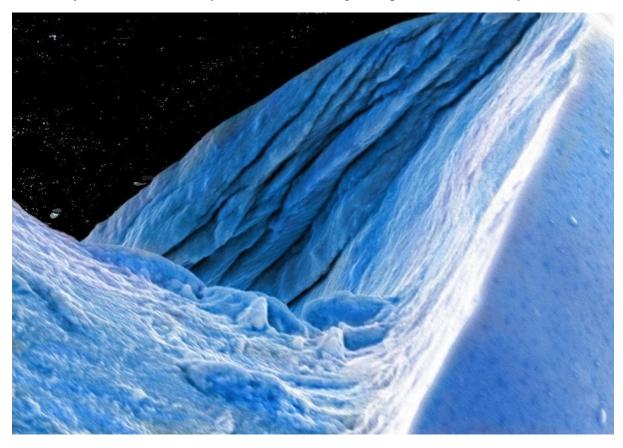

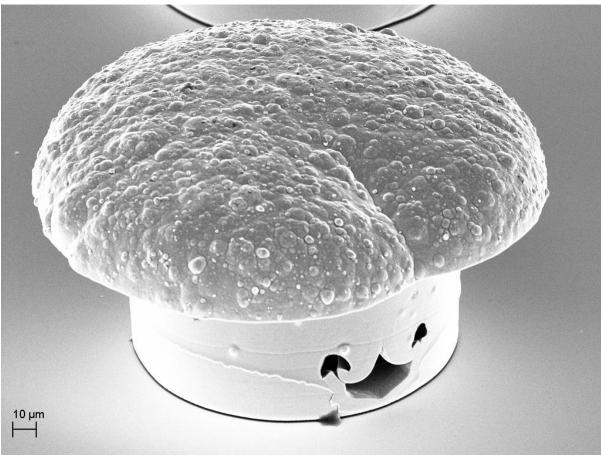

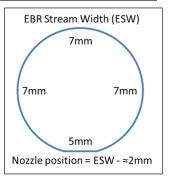

Hyperfunctional VIA microinductors directly address the main challenges of power management integrated circuits (PMICs), which are miniaturizing the micro-magnetic components, reducing electromagnetic (EM) leakage and minimizing power consumption<sup>6</sup>. Due to this, TSV enhanced microinductors in next-generation IVRs will be essential for autonomous MEMS and IoT devices<sup>6</sup>. Paving the way for this newly emerging 3D microinductor technology, Tyndall National Institute is a key facilitator of magnetic materials and microinductor research with an abundance of design/process<sup>7,47,48,49,50,51,52,53,54,55,56,57,58,59,60,61,62,63,64,65,66,67,68,69,70,71,72,73,74,75</sup> and review papers<sup>76,77,78,79,80,81</sup> available in the literature.