| Title                       | Pseudocapacitive charge storage at nanoscale silicon electrodes                                                                                                                                             |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | McSweeney, William;Geaney, Hugh;Glynn, Colm;McNulty,<br>David;O'Dwyer, Colm                                                                                                                                 |

| Publication date            | 2015-05                                                                                                                                                                                                     |

| Original Citation           | McSweeney, W., Geaney, H., Glynn, C., McNulty, D. and O'Dwyer, C. (2015) 'Pseudocapacitive Charge Storage at Nanoscale Silicon Electrodes', ECS Transactions, 66(6), pp. 39-48. doi: 10.1149/06606.0039ecst |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                     |

| Link to publisher's version | http://ecst.ecsdl.org/content/66/6/39.abstract -<br>10.1149/06606.0039ecst                                                                                                                                  |

| Rights                      | © 2015 ECS - The Electrochemical Society                                                                                                                                                                    |

| Download date               | 2024-05-01 16:29:45                                                                                                                                                                                         |

| Item downloaded from        | https://hdl.handle.net/10468/6461                                                                                                                                                                           |

### Pseudocapacitive charge storage at nanoscale silicon electrodes

W. McSweeney, H. Geaney, C. Glynn, D. McNulty, and C. O'Dwyer

Department of Chemistry, University College Cork, Cork, Ireland Micro and Nanoelectronics Centre, Tyndall National Institute, Lee Maltings, Cork, Ireland

Pseudocapacitive behaviour can be accessed when Si nanowire (NW) electrodes are scanned at relatively fast potential scan rates in Li-ion battery electrolytes. Measurements using cyclic voltammetry supported by electron microscopy confirm that Si NWs formed on silicon substrates, as opposed to metallic current collectors, do not solely undergo alloying reactions. The influence of doping type, carrier concentration and bias condition during voltammetric polarization significantly alters the mechanism of electrochemical energy storage. The formation of a carrier depleted (electrically dead) layer of n-type NWs on silicon current collector electrodes limits insertion or alloying processes and rates that ordinarily form Li-Si phases, and charge is also stored within the electric double layer via pseudocapacitive processes. P-type NWs with solid crystalline cores also exhibit pseudocapacitive charge storage without structural modification of the NWs.

#### Introduction

Porous semiconductors continue to receive considerable attention because of functionality afforded by random or ordered structuring on the nano or mesoscale. For instance, a wide range of mono- and compound semiconductors can be rendered porous through electroless or electrochemical etching (1-26), and such top down approaches allow a high degree of control over porosity formation. Additionally, the resulting skeleton formed through these means allows the possibility for arrays or arrangements of nanostructured materials such as nanowires (NWs), mesoporous materials, nanorods, photonic crystals and many other structural forms. When the sizes of the remaining semiconductors is reduced, photonic and phononic confinement effects can alter (electro)chemical, mechanical, and other physical characteristics. Porous materials can often prevent material break up caused by stress-strain changes during large structural volume changes during reversible lithiation. Changes in unit cell volume caused by swelling and contraction during charging and discharging is minimized with porous materials that provide room for expansion within the structure. Silicon has maintained a strong fundamental and applied research value, and recently has become one of the most significant materials when structured on the nanoscale, for Li-ion battery anodes (27-29).

Rechargeable batteries have been critical for enabling portable consumer electronics and are beginning to be used in electric vehicles. They are also becoming an attractive option for large-scale stationary energy storage (30-35). For mobile applications, high energy (per weight and volume) is the most important parameter since it determines the usage time per charge. For stationary applications, cost is the

most important design parameter, and high energy batteries could help reduce the cost per unit of stored energy (36,37).

Current lithium-ion battery anode research involves significant investigations of semiconducting and metalloid materials, particularly Si as its theoretical specific capacity is >4000 mAh/g (38) under deep cycling conditions. Previous theoretical studies showed that porous Si with a large pore size and high porosity can maintain its structure after Li ion induced alloying and swelling. Metal-assisted chemical (MAC) etching is known to form internally mesoporous nanowires in the form of a layer, etched from highly doped Si (39-42). Some porous materials are well known to exhibit pseudocapacitive behaviour in aqueous or typical organic battery electrolytes (43,44).

Here, we demonstrate that pseudocapacitive behaviour can be harnessed when Si nanowires are etched to maximum mesoporosity, forming an electrically dead layer on silicon current collector electrodes. An appropriate choice of conduction type can also be used to effect control over insertion or alloying processes that form Li-Si phases (45-47) as the dominant charge compensation process. By reducing silicon to nanoscale dimensions, a switch from Faradaic to non-Faradaic charge storage is possible for semiconducting electrodes in Li-ion containing electrolytes.

# **Experimental**

### Metal-assisted electroless etching of Si NW layers

Layers of p-type and n-type Si NWs, were fabricated by metal-assisted chemical (MAC) etching of 200 mm diameter lightly p-doped silicon (100) wafers (680 μm thickness) and highly doped n-type wafers, both with a native oxide layer (~2-5 nm thick). Substrates were immersed for two hours in a heated solution of 10% HF containing 0.04 M AgNO<sub>3</sub> and maintained at 50 °C using a thermostated water bath. Upon removal from the etching bath, samples were washed copiously with deionised water and then treated with concentrated nitric acid to remove unwanted silver deposition. The length of the NWs was controlled by the etching time and etchant concentration leaving a uniform layer of vertically aligned NWs. The remaining skeleton formed a vertical array of NWs ranging from 80 – 200 nm in diameter.

### Structural, compositional and morphological characterization

All materials and samples were analysed using scanning and transmission electron microscopy (SEM/TEM). SEM was performed using both Hitachi S4800 and SU70 instruments equipped with an Oxford-50 mm<sup>2</sup> X-Max detector for energy dispersive X-ray analysis. TEM analysis was conducted with a JEOL JEM-2100F field emission microscope operating at 200 kV, equipped with a Gatan Ultrascan CCD camera and EDAX Genesis EDS detector for atomic resolution crystal structure and composition examination. For ultra-high resolution morphology, STEM and high angle annular dark field (HAADF) couple with electron diffraction was performed.

## Electrochemical analysis in Li-ion battery cells

Cyclic voltammetry and galvanostatic measurements were carried out using either 3-electrode cells or 2-electrode coin cells using a Multi Autolab 101 potentiostat and a BioLogic VSP potentio/galvanostat. All potentials, unless otherwise stated, are relative to Li<sup>+</sup>/Li. Split coin cells were used with counter and active material electrodes separated by a polypropylene or glass wool separators soaked in 1 mol dm<sup>-3</sup>

solution of LiPF<sub>6</sub> in EC:DMC at a 50:50 v/v ratio. The electrodes were cycled at a range of potential scan rates in cyclic voltammetric measurements. Afterwards, electrodes were carefully washed in acetonitrile and a  $10^{-4}$  mol dm<sup>-3</sup> solution of acetic acid to remove the electrolyte residue.

#### **Results and Discussion**

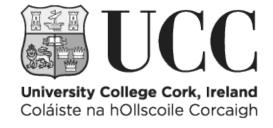

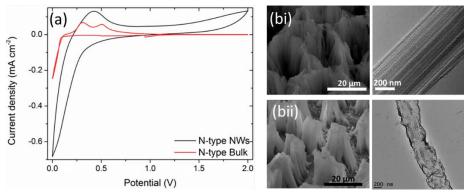

Si NWs were fabricated from low doped p-type Si and highly doped n-type Si via a MAC etching process, reported elsewhere (39,40). When formed from Si(100) wafers the Si NWs tend to form perpendicular to the substrate owing to preferred <100> etching direction of the Ag particles used in the etching process. Figures 1(a-c) shows the structure of the low doped p-type Si NWs via SEM (a) and TEM (b+c), and Figs 1(d-f) show the structure of the highly doped n-type NWs via SEM (d) and TEM (e+f). The p-type Si forms solid NWs with roughened edges (Figs 1(b+c)), whereas the n-type Si forms internally porous NWs as shown in Figs 1(e+f), which is characteristic of highly doped Si. The NWs clump at their tips due to van der Waals and capillary forces as shown in the SEM images in Figs 1(a+d).

**Figure 1.** SEM(a) and TEM(b+c) images of Si NWs formed from low doped p-type Si and SEM(d) and TEM(e+f) images of Si NWs formed from highly doped n-type Si exhibiting the different structure of the two sets of Si NWs.

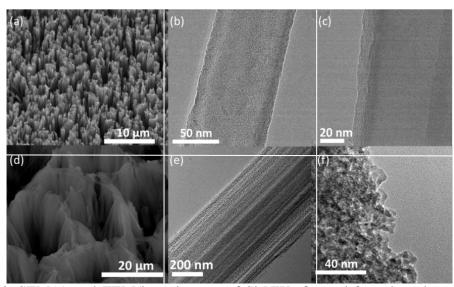

Figure 2(a) shows the CV response of p-type NWs together with the corresponding p-type bulk electrode response for comparison. By etching the Si wafer up to ~100 μm in depth in the form of a NW layer, the CV profile of the p-type Si NWs differs greatly to that of the p-type bulk Si(100) electrode. The characteristic difference compared to Si NWs on metallic current collectors is the observation of significant current and cumulative charge over the entire potential range (particularly where no alloying reactions occur), and the development of voltammetric symmetry at very high scan rates. Figure 2(b) shows the CV response of n-type NWs (etched for 3 h) compared to their monocrystalline bulk Si(100) equivalent and again it can be seen that the profile shape of the NW CV has changed dramatically when compared to the voltammetric response of a planar Si(100) electrode. It is interesting to note that nearly all of the CV responses in Fig. 2 have anodic peak(s) at ~0.5 V corresponding to Li<sup>+</sup> extraction from each type of Si anodes. For the p-type NW anode, definitive Li<sup>+</sup> insertion or extraction peaks are not observed. The profile of the voltammograms in

Fig. 2 are not characteristic of Li<sup>+</sup> insertion or extraction within the p-type NWs. It is well established that the Si lattice structure changes upon Li<sup>+</sup> insertion, and the reversible alloying processes that form Li-Si phases have characteristic cathodic and anodic peaks (see Fig. 2).

Figure 2(c) is a schematic of the cross section of p-type and n-type Si NWs, low doped p-type Si has a wider depletion region (at an equivalent biasing condition) than high doped Si as a function of the difference in relative doping densities. The doping density of the n-type Si is  $(N_{\rm D}=1.2\times10^{19}~{\rm cm^{-3}}-7.4\times10^{19}~{\rm cm^{-3}})$  compared to the doping density of the p-type Si  $(N_{\rm A}=1.6\times10^{14}~{\rm cm^{-3}}-7.0\times10^{15}~{\rm cm^{-3}})$ . The majority carriers in the n-type Si are electrons, which enable the reduction of Li<sup>+</sup> ions during the alloying process insertion. This schematic is useful for understanding the CV responses of the p-type and n-type Si NWs shown in Figs 2(a) and (b) respectively.

**Figure 2.** CVs of (a) p-type Si NWs and p-type bulk Si(100) and (b) n-type Si NWs and n-type bulk Si(100) acquired in the potential range 2–0 V at a scan rate of 1 mV s<sup>-1</sup>. (c) Schematic of the cross section of the p-type and n-type Si NWs showing the variation in depletion region thicknesses.

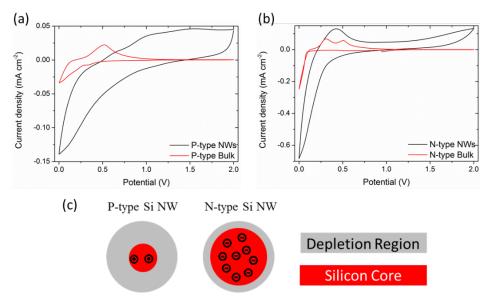

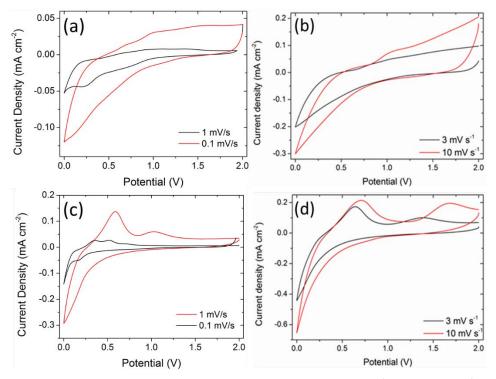

When the scan rate of the CV was varied, the CV profile of the p-type Si NWs changed considerably. At a low scan rate of 0.1 mV s<sup>-1</sup>, a cathodic Li<sup>+</sup> insertion peak can be observed as shown in Fig. 3(a), consistent with Li insertion potentials observed for bulk Si wafers. The CV at 0.1 mV s<sup>-1</sup> scan rate is shown with a voltammetric scan of a similar electrode acquired at 1 mV s<sup>-1</sup> for comparison. At lower scan rates, Li insertion into the NWs occurs rather than purely capacitive charge storage, and characteristically and smaller integrated charge is found at potentials > 0.5 V, where no Li-Si reactions occur. Wide current ranges over this potential range are more indicative of pseudocapacitive storage. SEM images of the p-type Si NWs after the 1 mV s<sup>-1</sup> scan and the 0.1 mV s<sup>-1</sup> scan are shown in Figs 3(bi) and b(ii), respectively. The Si NWs after the 1 mV s<sup>-1</sup> scan appear unaffected by the cyclic potential sweep, while the Si NWs cycled at 0.1 mV s<sup>-1</sup> scan appear roughened. This confirms reversible alloying and associated phase and structural changes from slow, diffusion limited Li-Si reactions.

**Figure 3.** (a) CVs of p-type Si NWs at scan rates of 1 mV s<sup>-1</sup> and 0.1 mV s<sup>-1</sup>, the current was normalised to highlight the relative peak potentials and overall difference in profile. SEM images of the p-type NWs after a scan rate of 1 mV s<sup>-1</sup> (bi) and 0.1 mV s<sup>-1</sup> (bii). The far right TEM images are from p-type Si NWs in a 'lithiated' charge condition.

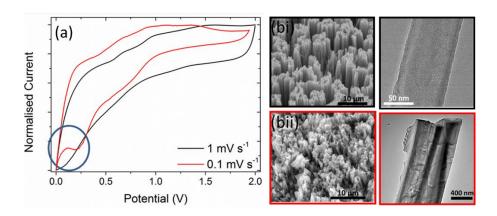

A TEM image of p-type Si NWs cycled at 0.1 mV s<sup>-1</sup> is shown in Fig. 3(bii). The Si NW appears distorted, especially when compared to TEM images of pristine Si NWs shown in Figs 1(b-c). The cycled NW appears to have a solid, crystalline core with an amorphous shell, which would indicate that limited lithiation at slow scan rates occurred at the outer regions of the Si NW but not at the core of the Si NW. It should be noted that MAC etching produces Si NWs that vary greatly in diameter due to random deposition of Ag NPs on the Si surface during the etching process, and very large diameter NWs typically retain a pristine region at the center. Typically, the morphology of p-type NWs cycled at 0.1 mV s<sup>-1</sup> is irreversibly altered. Figure 4(a) shows the corresponding CVs of n-type Si NWs and bulk n-type Si(100) planar electrode. An SEM image of the n-type Si NWs post cycling confirm significant roughening due to Li<sup>+</sup> insertion and extraction processes indicated by the large cathodic current peak in Fig. 4(a). The corresponding TEM image of the n-type Si NWs post cycling demonstrates that the n-type Si NWs show negligible morphological changes after polarization at faster scan rates. Significant internal porosity development is found scan rates an order of magnitude slower. This is a marked structural change when compared to a TEM image of a pristine n-type Si NW that was shown in Fig. 1(e). Thus, for p-type and n-type NWs, the different CV response to reversible lithiation is scan rate dependent, and at slow scan rate where alloying processes dominate, the NWs undergo irreversible changes in structure.

**Figure 4.** CVs of n-type Si NWs and n-type bulk Si(100) acquired in the potential range 2–0 V at a scan rate of 1 mV s<sup>-1</sup>. SEM images of the n-type NWs after a scan rate of 1 mV s<sup>-1</sup> (bi) and 0.1 mV s<sup>-1</sup> (bii). The far right TEM images are from n-type Si NWs following cycling at the scan rates for (bi) and (bii) respectively.

Increasing the potential scan rate of a CV for porous semiconducting materials such as MAC etched Si NWs has thus a considerable influence on the type of electrochemical reaction. One characteristic is that the current peaks associated with SEI formation, alloying or intercalation, are convoluted within the total integrated charge on the initial cathodic sweep. As demonstrated in Figs 3 and 4, the rate of applied potential influences the current profile such that pseudocapacitive charge storage occurs, including significant cumulative charge at high potentials where Li-Si reactions do not proceed. In materials that exhibit hybrid electrochemical energy storage mechanism, Conway established that  $i(V) \propto v$  (pseudocapacitance) and  $i(V) \propto v^{1/2}$  (reversible alloying). Since no Li-Si reactions occur > 0.7 V (see Fig. 2), cumulative charge at high potentials (and less well-defined cathodic and anodic current peaks) is characteristic of double layer capacitive charging. For p-type and ntype Si NW electrodes, cyclic voltammograms acquired with scan rates in the range 0.1 – 10 mV s<sup>-1</sup> and the voltammetric response compared to planar Si(100) electrodes where Li-Si reactions occur. Fig. 5(a,b) shows the CV profiles obtained from a cyclic potential sweeps of rough surfaced p-type Si NW electrodes ranging from 0.1 - 10 mV s<sup>-1</sup>. An enhancement of the current at potentials where primary Li-Si reactions occur, while the voltammogram develops symmetry in the cathodic and anodic chargedischarge sweep at successively higher scan rates. No Li insertion peak is evident for p-type Si NWs at scan rates of 1 mV s<sup>-1</sup> or greater.

The shape of the CV has some characteristics similar to an asymmetric supercapacitor. The current response from both p-type and n-type NW electrodes in Fig. 5a,c (compared to planar Si(100) electrodes) is typically larger at potentials < 1 V than at faster scan rates, suggesting that there is an additional charge storage mechanism at larger potentials. The total stored charge includes the faradaic contribution from the Li<sup>+</sup> ion insertion processes (when allowed), the faradaic contribution from the charge transfer process with the surface atoms/species (i.e. pseudocapacitance), and the non-faradaic contribution from the double layer charging.

**Figure 5.** (a) CVs of p-type Si NWs at scan rates of 0.1 mV s<sup>-1</sup> and 1 mV s<sup>-1</sup> and (b) at scan rates of 3 mV s<sup>-1</sup> and 10 mV s<sup>-1</sup>. (c) CVs of n-type Si NWs at scan rates of 0.1 mV s<sup>-1</sup> and 1 mV s<sup>-1</sup> and (d) at scan rates of 3 mV s<sup>-1</sup> and 10 mV s<sup>-1</sup>.

For a high degree of porosity, both types of capacitive contributions can be significant, and kinetic processes (as opposed to diffusion-limited processes) may dominate at faster scan rates. For n-type Si NWs (Figs 5(c,d)), the response includes reversible alloying as indicated by characteristic cathodic and anodic current peaks, and at faster rates, an additional capacitive contribution to the overall charge.

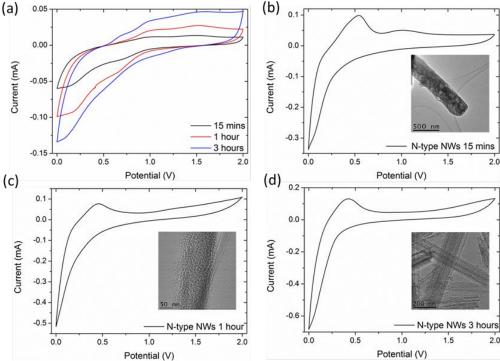

P-type electrodes with NW length defined by etching time were also prepared using etching times in the range 15 mins – 3 h. CVs were also acquired at a scan rate of 1 mV s<sup>-1</sup> and from Fig. 6(a), it was observed that with increasing NW length, a significantly modified cumulative charge is noted in the CV response, which we attribute to the greater effective surface area of carrier depleted Si interfaced with low viscosity electrolyte. It should be noted that although the area of the CV profiles increased that the CV profile remained similar for p-type NWs of different length. N-type NWs that were etched for different lengths of time and the corresponding CV profiles are shown in Fig. 6(b-d). The CV profiles of the n-type NWs not only increase in cathodic (charging) current for NWs etched for longer durations (longer NWs) but the profile of the CV also changes due to changing development of internal porosity within the n-type Si NWs, as confirmed by TEM analysis of the NW morphology.

N-type NWs etched for 15 mins (Fig. 6(b)) responded with a different CV profile at the same scan rate as n-type NWs etched for 3 h (Fig. 6(d)). Longer n-type NWs are produced after 3 h etching time and develop internal porosity thus increasing the effective surface area. It has been shown that the galvanostatic profile of porous Si electrodes varies from that of their non-porous equivalent (48) and a similar effect can be observed under slow rate potentiodynamic conditions here – at slow rates, n-type Si NWs permit lithiation at low potentials. P-type Si NWs do not become internally porous with etching time and after 3 h of etching the p-type NWs have an average length of 110  $\mu$ m, whereas after a 3 h etching duration, the n-type NWs are 50  $\mu$ m in length. The reduced length is due to lateral and internal etching of material from within the highly doped NW.

**Figure 6.** (a) Cyclic voltammograms acquired 1 mV s<sup>-1</sup> of p-type Si NWs that were etched for 15 mins – 3 h. (b) Cyclic voltammograms at 1 mV s<sup>-1</sup> of n-type Si NWs etched for (b) 15 mins, (c) 1 h, and (d) 3 h.

In the CV profile of n-type NWs etched for 15 mins, two anodic peaks can be seen at ~0.5 V and at ~1 V associated with dealloying from high mole fraction  $\text{Li}_x\text{Si}$  (29,38,45). The current values for n-type Si NWs are noticeably higher than for p-type Si NWs under similar conditions due to the difference in doping density and free majority carrier (electron) concentration of the Si NWs – the forward biased condition and high doping density ensures a greater surface electron density for a faster initial  $\text{Li}^+$  reduction rate. Figure 6(c) shows the CV response of n-type NWs etched for 1 h. There is a noticeable change in the profile shape of Fig. 6(c) when compared to Fig. 6(b), primarily the absence of the anodic (discharge) peak at ~1 V. This peak is also absent in the CV profile for the n-type Si NWs etched for 3 h as shown in Fig. 6(d).

We surmise that several effects are particular to electrodes composed of semiconducting NWs, in the absence of a metallic current collector. Contributions to the accumulated stored charge can arise from effective interpenetration of electrode and electrolyte species and phases, so that double layers formed at the semiconductorsolution interface extend entirely throughout the NW region, similar to a (pseudo)capacitor configuration. Second, the doped semiconductor electron concentration influences the degree and direction of band-bending relative to the redox potential in solution, and can be controlled by the applied bias. In the p-type NWs, reverse bias at anodic potentials limits the charge transfer of already minority carrier electrons to reduce Li to cause alloying, thereby allowing the capacitive surface area effect to dominate instead. Analogously, the n-type NWs would ordinarily be in forward bias in the accumulation regime, with a high surface free carrier electron density. Nominally, this would result in a high current and alloying reaction rate, but the internal mesoporosity of the NWs (comprising 3-10 nm crystallites of Si) is less than the narrow depletion region width, limiting but not preventing the alloying reaction. Here, the large surface area pseudocapacitive effects are found in addition to some alloying reactions at the faster scan rates.

For the NWs, considerable space charge capacitance contributed to the measured charge, and further work is underway to define the conditions under which a potential or time-dependent transition from intercalation to pseudocapacitance for these materials occurs.

#### **Conclusions**

MAC etched Si NWs were produced were produced from highly doped n-type Si and low doped p-type Si. A CV study showed that the response of the NWs was different from that of the bulk Si from which they were etched. It was shown that at a scan rate of 1 mV s<sup>-1</sup> that no Li<sup>+</sup> insertion occurs into the p-type NWs, but when the scan rate was reduced Li<sup>+</sup> insertion can occur. Electron microscopy analysis also demonstrated that the p-type and n-type Si NWs are structurally modified upon Li<sup>+</sup> insertion, with the p-type NWs retaining a crystalline core, and n-type wires developing irreversible porosity at slower scan rates. The integrated voltammetric charge from CVs of the NWs increased with longer NWs with higher (internal) porosity due to the electrolyte having larger surface area with which to react. Fundamentally, the response is evidence of pseudocapacitive charge storage in the double layer at the high surface area Si NW electrode due to charge carrier depletion under forward bias that severely limits the degree of alloying reactions that can occur. As p-type NWs are also reverse biased under similar conditions, and have electrons and minority carriers with lesser concentration and mobility, the voltammetric response is largely (pseudo)capacitive in nature, except at very slow scan rate where some intercalation reactions can occur. For n-type mesoporous Si NWs, a combination of alloying and capacitive contributions are found at scan rates where pseudocapacitive effects are dominant in p-type NWs.

### Acknowledgements

WMS acknowledges support under the framework of the INSPIRE programme, funded by the Irish Government's Programme for Research in Third Level Institutions, Cycle 4, National Development Plan 2007-2013. CG acknowledges financial support from the Irish Research council under Award No. RS/2011/797. The authors also acknowledge support from the European Union 7th Framework Programme FP7/2007-2013 (Project STABLE) under grant agreement no. 314508. Support from Science Foundation Ireland under Award No. 13/TIDA/E2761 is also acknowledged.

#### References

- [1] H. Föll, S. Langa, J. Carstensen, M. Christophersen and I.M. Tiginyanu, *Adv. Mater.* **15**, 183 (2003).

- [2] E. Spiecker, M. Rudel, W. Jäger, M. Leisner and H. Föll, *phys. stat. sol.* (a) **202**, 2950 (2005).

- [3] S. Langa, J. Carstensen, I.M. Tiginyanu, M. Christophersen and H. Föll. *Electrochem. Solid-State Lett.* **5**, C14 (2002).

- [4] M. Christophersen, S. Langa, J. Carstensen, I.M. Tiginyanu and H. Föll, *phys. stat. sol.* (a) **197**, 197 (2003).

- [5] S. Lölkes, M. Christophersen, S. Langa, J. Carstensen and H. Föll, *Mater. Sci. Eng. B*, **101**, 159 (2003).

- [6] S. Langa, J. Carstensen, M. Christophersen, K. Steen, S. Frey, I.M. Tiginyanu and H. Föll, *J. Electrochem. Soc.* **152**, C525 (2005).

- [7] F.M. Ross, G. Oskam, P.C. Searson, J.M. Macaulay and J.A. Liddle, *Philos. Mag. A* **75**, 525 (1997).

- [8] M. Osiak, W. Khunsin, E. Armstrong, T. Kennedy, C. M. Sotomayor Torres, K. M. Ryan, and C. O'Dwyer, *Nanotechnology*, **24**, 065401 (2013)

- [9] H. Tsuchiya, M. Hueppe, T. Djenizian, P. Schmuki and S. Fujimoto, *Sci. Tech. Adv. Mater.* **5**, 119 (2004).

- [10] C. O'Dwyer, M. Szachowicz, G. V. Visimberga, V. Lavayen, S. B. Newcomb, C. M. Sotomayor Torres, *Nat. Nanotech.* 4, 239 (2009).

- [11] S. Langa, M. Christophersen, J. Carstensen, I.M. Tiginyanu and H. Föll, *phys. stat. sol.* (a) **197**, 77 (2003).

- [12] A.-M. Gonçalves, L. Santinacci, A. Eb, C. David, C. Mathieu, M. Herlem and A. Etcheberry, *phys. stat. sol.* (a) **204**, 1286 (2007).

- [13] A.-M. Gonçalves, L. Santinacci, A. Eb, I. Gerard, C. Mathieu and A. Etcheberry, *Electrochem. Solid-State Lett.* **10**, D35 (2007).

- [14] M.M. Faktor, D.G. Fiddyment and M.R. Taylor, *J. Electrochem. Soc.*, **122**, 1566 (1975).

- [15] E. Harvey, C. Heffernan, and D. N. Buckley and C. O'Raifeartaigh, *Appl. Phys Lett.*, **81**, 3191 (2002).

- [16] L. Macht, J.J. Kelly, J.L. Weyher, A. Grzegorczyk and P.K. Larsen, *J. Crystal Growth* **273**, 347 (2005).

- [17] J. J. Kelly, L. Macht, D.H. van Dorp, M.R. Kooijman and J.L, Weyher, *in Processes at the Compound-Semiconductor/Solution Interface*, Editors: P.C. Chang, K. Shiojima, R.E. Kopf, X. Chen, D. Noel Buckley, A. Etcheberry, and B.

- Marsan, State-of-the-Art Program on Compound Semiconductors XLII, **PV 2005-04**, p. 138 (2005).

- [18] R. Lynch, C. O'Dwyer, D.N. Buckley, D. Sutton and S.B. Newcomb, *ECS Trans* **2**, 131 (2006).

- [19] R. Lynch, M. Dornhege, P. Sánchez Bodega, H.H. Rotermund and D.N. Buckley, *ECS Trans* **6**, 331 (2007).

- [20] R. Lynch, C. O'Dwyer, D. Sutton, S. Newcomb, and D.N. Buckley, *ECS Trans* 6, 355 (2007).

- [21] R. Lynch, C. O'Dwyer, N. Quill, S. Nakahara, S.B. Newcomb, and D.N. Buckley, *ECS Trans* **16**, 393 (2008).

- [22] N. Quill, C. O'Dwyer, R. Lynch, C. Heffernan, and D. N. Buckley, *ECS Trans* **19**, 295 (2009).

- [23] C. O'Dwyer, D.N. Buckley, D. Sutton, and S.B. Newcomb, *J. Electrochem. Soc.*, **153**, G1039 (2006).

- [24] C. O'Dwyer, D.N. Buckley, and S. B. Newcomb, *Langmuir*, **21**, 8090 (2005)

- [25] C. O'Dwyer, D.N. Buckley, D. Sutton, M. Serantoni, and S.B. Newcomb, *J. Electrochem. Soc.*, **154**, H78 (2007).

- [26] O. V. Bilousov, J. J. Carvajal, D. Drouin, X. Mateos, F. Díaz, M. Aguiló and C. O'Dwyer, *ACS Appl. Mater. Interfaces*, **4**, 6927 (2012).

- [27] C. K. Chan, H. L. Peng, G. Liu, K. McIlwrath, X. F. Zhang, R. A. Huggins, Y. Cui, *Nat. Nanotechnol.* **3** (2008) 31 (2008).

- [28] M. T. McDowell, S.W. Lee, C. Wang, Y. Cui, *Nano Energy* 1, 401 (2012).

- [29] M. T. McDowell, Y. Cui, Adv. Energy Mater. 1, 894 (2011).

- [30] J.M. Tarascon, M. Armand, *Nature* **414**, 359 (2001).

- [31] M.S. Whittingham, Chem. Rev. 104, 4271 (2004).

- [32] M. Armand, J.M. Tarascon, *Nature* **451**, 652 (2008).

- [33] D. Linden, T. Reddy, Handbook of Batteries, McGraw-Hill, New York, 2002.

- [34] J. B. Goodenough, H. Abruna, M. Buchanan, US Department of Energy, Washington, DC, 2007.

- [35] C. Liu, F. Li, L.P. Ma, H.M. Cheng, *Adv. Mater.* **22**, E28 (2010).

- [36] Y. J. Lee, H. Yi, W.J. Kim, K. Kang, D. S. Yun, M. S. Strano, G. Ceder, A. M. Belcher, *Science* **324**, 1051 (2009).

- [37] B. Scrosati, J. Garche, J. Power Sources 195, 2419 (2010).

- [38] W. McSweeney, H. Geaney and C. O'Dwyer, *Nano Res.* doi:10.1007/s12274-014-0659-9 (2015).

- [39] W. McSweeney, O. Lotty, N. Mogili, C. Glynn, H. Geaney, D. Tanner, J. Holmes and C. O'Dwyer, *J. Appl. Phys.* **114**, 034309 (2013).

- [40] W. McSweeney, O. Lotty, J. D. Holmes, C. O'Dwyer, *ECS Trans.* **35**, 25 (2011).

- [41] C. Glynn, O. Lotty, W. McSweeney, J. D. Holmes, C. O'Dwyer, *ECS Trans.* **8**, 73 (2011).

- [42] A. I. Hochbaum, D. Gargas, Y. J. Hwang, P. Yang, Nano Lett. 9, 3550 (2009).

- [43] P. Simon and Y. Gogotsi, Nat. Mater. 7, 845 (2008).

- [44] T. Brezesinski, J. Wang, S. H. Tolbert and B. Dunn, Nat. Mater. 9, 146 (2010).

- [45] W. McSweeney, O. Lotty, C. Glynn, H. Geaney, J. D. Holmes and C. O'Dwyer, *Electrochim. Acta*, **135**, 356 (2014).

- [46] M. Osiak, H. Geaney, E. Armstrong and C. O'Dwyer, *J. Mater. Chem. A*, **2**, 9433 (2014).

- [47] M. J. Armstrong, C. O'Dwyer, W. J. Macklin and J. D. Holmes, *Nano Res.*, 7, 1 (2014).

- [48] B. M. Bang, H. Kim, J.-P. Lee, J. Cho and S. Park, *Energy Environ. Sci.* **4** 3395 (2011).