| Title                       | Investigation of high-κ/InxGa1-xAs interfaces                                                                                                                                                                                                    |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Cherkaoui, Karim;O'Connor, Éamon;Monaghan, Scott;Long,<br>Rathnait D.;Djara, Vladimir;O'Mahony, A.;Nagle, R.;Pemble,<br>Martyn E.;Hurley, Paul K.                                                                                                |

| Publication date            | 2010-01                                                                                                                                                                                                                                          |

| Original Citation           | Cherkaoui, K., O'Connor, É., Monaghan, S., Long, R. D., Djara, V., O'Mahony, A., Nagle, R., Pemble, M. E. and Hurley, P. K. (2010) 'Investigation of high-κ/InxGa1-xAs interfaces', ECS Transactions, 28(2), pp. 181-190. doi: 10.1149/1.3372574 |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                          |

| Link to publisher's version | 10.1149/1.3372574                                                                                                                                                                                                                                |

| Rights                      | © 2010, The Electrochemical Society.                                                                                                                                                                                                             |

| Download date               | 2024-05-20 01:45:44                                                                                                                                                                                                                              |

| Item downloaded from        | https://hdl.handle.net/10468/13320                                                                                                                                                                                                               |

### Investigation of High-k/In<sub>x</sub>Ga<sub>1-x</sub>As Interfaces

K. Cherkaoui, É. O'Connor, S. Monaghan, R. D. Long, V. Djara, A. O'Mahony, R. Nagle, I. M. Povey, M. E. Pemble, P. K. Hurley

Tyndall National Institute, University College Cork, <u>Lee Maltings</u>, <u>Prospect Row</u>, <u>Cork</u>, <u>Ireland</u>

The quality of the high- $k/In_xGa_{1-x}As$  interface is a crucial factor in achieving high electron mobility compound semiconductor field effect transistors. Capacitance and conductance characterisation methods were employed to evaluate different high-k/InGaAs interfaces. This paper will first discuss the specificity of capacitance voltage characteristics of compound semiconductor MOS structures, and then the recent progress in the study of high- $k/In_xGa_{1-x}As$  interfaces will be presented. The capacitance and conductance measurements are combined to provide a picture of the interface state density. We have also investigated the merit of using intermediate k value dielectrics such as  $Al_2O_3$  and MgO as interface control layers between the semiconductor and the main high k layer.

#### Introduction

The recent introduction of HfO<sub>2</sub> in the gate stack of Si CMOS devices has led to significant transistor performance enhancement [1]. However, the incorporation of a high dielectric constant (high-k) material into the gate stack combined with future device scaling indicates that the near ideal Si/SiO<sub>2</sub> interface will no longer be at the heart of future MOSFETs. This has opened new opportunities for high electron mobility compound semiconductors to replace Si as an n-channel material for future MOSFETs. The low quality native oxides of III-V semiconductors and the absence of dielectrics exhibiting excellent III-V semiconductor/dielectric interfaces have always been a major obstacle to the advance of large scale III-V ICs. In recent years there have been breakthroughs in the field of deposited dielectrics on III-V materials, such as a very low interface state density being achieved using *in situ* MBE grown Ga<sub>2</sub>O<sub>3</sub> on GaAs [2] or by using a silicon passivation layer between the GaAs surface and the oxide layer providing a significant improvement in the capacitance interface state response [3].

## **Capacitance Characteristics of Compound Semiconductor MOS Structures**

Several electrical characterisation techniques to investigate the oxide/semiconductor interface have been successfully employed for many years [4]. All these methods were established and developed to study the Si/SiO<sub>2</sub> system which has been at the heart of MOSFET devices for more than four decades. With the introduction of new high-*k* dielectrics in the gate stack and the search for alternative high mobility channel materials to replace Si, a need has emerged to understand, adapt and appropriately interpret the specific features of conventional electrical measurement techniques when applied to compound semiconductor MOS structures. In this section, we will briefly describe the capacitance voltage techniques and the specific considerations when applying these to compound semiconductors devices.

# The contribution of interface states to the measured capacitance

The capacitance voltage characteristic of a MOS capacitor consists of three main components: the oxide  $(C_{ox})$ , the semiconductor  $(C_s)$  and the interface states  $(C_{it})$  capacitance contributions. Each capacitance component exhibits different dependence upon applied bias, temperature, and measurement frequency. Assuming a constant capacitance contribution for the oxide, both the semiconductor and interface state capacitance responses vary with bias and frequency [4]. The semiconductor capacitance is strongly voltage dependent in the entire voltage range and also shows frequency dependence in the inversion region depending on the ability of the minority carriers to follow the measurement frequency. The interface states capacitance contribution varies also with voltage and frequency. This dependence is related to the Fermi level position at the interface which defines the portion of the band gap which is probed, as well as defining the response time associated with the capture and emission of free carriers at the interface.

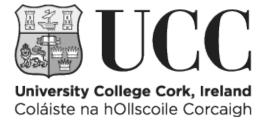

Figure 1. Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As CV characteristics measured at high frequency and liquid Nitrogen temperature compared to room temperature CV measured at lower frequency to demonstrate the interface states response.

When all the interface states are able to respond to the measurement frequency, their associated capacitance is added to the semiconductor differential capacitance which in turn is in series with the oxide capacitance. The total measured capacitance can then be expressed as:

$$\mathbf{C}_{\mathrm{m}} = \left(\frac{1}{\mathbf{C}_{\mathrm{ox}}} + \frac{1}{\mathbf{C}_{\mathrm{s}} + \mathbf{C}_{\mathrm{it}}}\right)^{-1}$$

[1]

When the interface states are not able to follow the measurement frequency, they do not contribute to the differential capacitance. In this case the interface states cause a

stretch out of the CV characteristics induced by their charging when the Fermi level is swept across the band gap. The frequency and temperature measurement parameters can be used to either maximise or eliminate the C<sub>it</sub> component. Figure 1 illustrates this method.

The density of interface states for each gate voltage condition is then extracted using the following equation [4]:

$$C_{it} = \left(\frac{1}{C_{LF}} - \frac{1}{C_{ox}}\right)^{-1} - \left(\frac{1}{C_{HF}} - \frac{1}{C_{ox}}\right)^{-1}$$

[2]

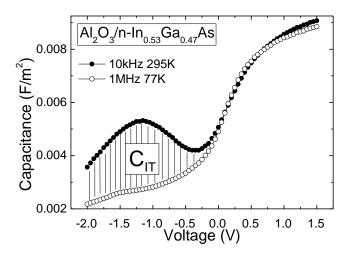

where  $C_{LF}$  and  $C_{HF}$  are the measured capacitance characteristics at low frequency (room temperature ~ 295K) and high frequency (LN<sub>2</sub> temperature ~ 77K) respectively. The temperature dependence of other parameters could affect the results obtained using this method, for instance if the oxide presents border traps or if the semiconductor exhibits carrier freeze out (usually observed in wider band gap materials or lower temperature) the  $C_{LF}$  and  $C_{HF}$  difference can be then caused by other sources than interface states. In the case presented in figure 1, the comparison is justified since both CVs are identical in accumulation and part of the depletion region. By comparing the low temperature CV with a simulated ideal CV curve without an interface state component (figure 2) the Fermi level position at the interface for a given gate voltage can be extracted. This allows the density of interface states as a function of the band gap energy to be constructed. The noticeable asymmetry in the simulated CV will be discussed later.

Figure 2. Comparison of the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  CV response measured at 77K and 1MHz with a simulated CV curve to show the stretch out originating from the charging of interface states as the Fermi level is swept towards the conduction band.

Capacitance voltage characteristic in the presence of a very large interface state density

When measuring the CV characteristics of a silicon MOS capacitor, rarely is the magnitude of  $D_{it}$  so high that it prevents clear observation of the inversion, depletion, and

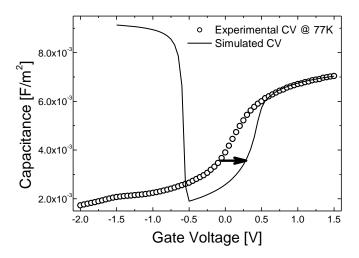

accumulation regimes. However, certain processing conditions could generate very high  $D_{it}$  levels in Si MOS capacitors. Figure 3a presents the CV response of a Ni(100)/HfO<sub>2</sub>(3.5nm)/SiO<sub>x</sub>(3nm)/n-Si MOS capacitor. The 3.5nm HfO<sub>2</sub> film was formed by electron beam evaporation from a solid source of HfO<sub>2</sub> under a film densifying Ar plasma. These processing conditions not only generate a thick SiO<sub>x</sub> (3nm) interlayer but also cause significant lattice damage at the interface [5]. It is clear from figure 3a that the CV characteristics must be measured over a large frequency range in order to get an idea of the level of the interface state contribution. This example illustrates the case that is very often encountered when investigating oxide/compound semiconductor interfaces. Figure 3b presents the CV characteristics of a Pd(100nm)/HfO<sub>2</sub>(11.4nm)/n-GaAs MOS structure measured at different frequencies. Despite a three stage chemical passivation step [6] and the ALD growth of HfO<sub>2</sub> as opposed to the harsher electron beam evaporation technique, the frequency dispersion is still very large. The GaAs interface does not reach true accumulation as might be inferred if one analyses the low frequency (1 kHz) CV characteristic alone.

Figure 3. a) Multi frequency CV characteristics of Ni(100)/HfO<sub>2</sub>(3.5nm)/SiO<sub>x</sub>(3nm)/n-Si. The HfO<sub>2</sub> film was formed using electron beam evaporation under Ar ion assist. b) Multi frequency CV characteristics of Pd(100nm)/HfO<sub>2</sub>(11.4nm)/n-GaAs. The HfO<sub>2</sub> film was formed by ALD.

## Compound semiconductor capacitance voltage characteristics

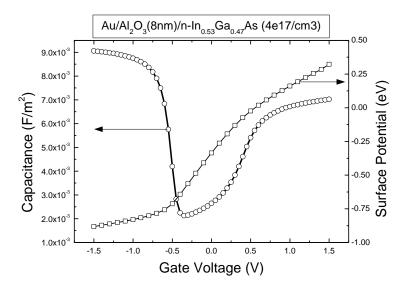

The investigation of oxide/compound semiconductor interfaces using CV techniques often requires the simulation of the ideal CV of the studied structure. The In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS theoretical CV curves obtained using 1D Schrodinger-Poisson solvers present a very significant difference when compared to conventional CVs on Si MOS structures. Figure 4 shows the simulated CV for an Au/Al<sub>2</sub>O<sub>3</sub>(8nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As structure [7]. The large asymmetry in the CV is the most remarkable feature as compared to a conventional CV on a Si MOS device. This difference is due to the lower effective density of states in the conduction band (Nc~2x10<sup>17</sup>cm<sup>-3</sup>) than in the valence band (Nv~5x10<sup>18</sup>cm<sup>-3</sup>) for In<sub>0.53</sub>Ga<sub>0.47</sub>As. In order to visualise the origin of this asymmetry we

have plotted the surface potential as a function of gate voltage. Figure 4 shows that the surface potential increases at higher rate with voltage in accumulation than it does in inversion. This means the Fermi level at the surface moves well into the conduction band. The semiconductor capacitance  $C_s$ , which is the surface charge differential with respect to the surface potential, is therefore considerably reduced in accumulation relative to  $C_s$  in inversion (for n-type  $In_{0.53}Ga_{0.47}As$ ). Similar effects have been described for MOS structures fabricated on narrow band gap II-VI compounds [8].

Figure 4. Simulated CV curve for a Au/Al<sub>2</sub>O<sub>3</sub>(8nm)/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As structure. The surface potential dependence upon gate voltage is also presented. No quantum confinement effects were included in the simulation.

In the case of Si,  $C_s$  in accumulation or inversion is much greater than  $C_{ox}$  due to the large Nc and Nv values for Si  $(Nc(Si)\sim3x10^{19}cm^{-3})$  and  $Nv(Si)\sim2x10^{19}cm^{-3}$ . Considering equation (3),  $C_{max}\sim C_{ox}$  for Si whereas the correction factor is significant for  $In_{0.53}Ga_{0.47}As$  and different from accumulation to inversion.

$$\mathbf{C}_{\text{max}} = \mathbf{C}_{\text{ox}} \left( 1 + \frac{\mathbf{C}_{\text{ox}}}{\mathbf{C}_{\text{s}}} \right)^{-1}$$

[3]

It is interesting to note that the asymmetry and the large capacitance correction are present in the theoretical CV curve (figure 4) while the quantum effects are not included in the simulation. The confinement of free carriers at the interface further increases the divergence of  $C_{max}$  from  $C_{ox}$ .

## High-k/InGaAs Interfaces

In this section we will present a study carried out on three different oxides stacks on In<sub>0.53</sub>Ga<sub>0.47</sub>As interfaces where the characterisation methods described in the previous section were employed. The sample set consisted of one HfO<sub>2</sub> control sample and two bilayer samples: HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>/MgO. Both Al<sub>2</sub>O<sub>3</sub> and MgO interlayers are selected

for their wide band gap compared to HfO<sub>2</sub>. The aim of this study is to investigate the electrical properties of the oxide/In<sub>0.53</sub>Ga<sub>0.47</sub>As with and without interlayers.

## Experimental Details

The sample set used in this study consisted of:  $Pd/HfO_2(5nm)/In_{0.53}Ga_{0.47}As$ ,  $Pd/HfO_2(5nm)/Al_2O_3(1nm)/In_{0.53}Ga_{0.47}As$  and  $Pd/HfO_2(5nm)/MgO(1nm)/In_{0.53}Ga_{0.47}As$ . The  $2\mu m$  thick  $In_{0.53}Ga_{0.47}As$  epilayer was grown by MOVPE lattice matched on n+InP. The Si n type doping in the  $In_{0.53}Ga_{0.47}As$  epilayer was  $3.5 \times 10^{17} cm^{-3}$ . The samples were preserved under  $N_2$  ambient prior to loading in an ALD reactor for oxide deposition, in order to minimise the ambient exposure time pre-ALD. The InGaAs surface was untreated prior to ALD. The precursors used for the  $HfO_2$ , MgO, and  $Al_2O_3$  films were  $Hf[N(C_2H_5)(CH_3)]_4$ ,  $(C_5H_5)_2Mg$ , and  $Al(CH_3)_3$  respectively in combination with  $H_2O$ . The growth temperature was  $250^{\circ}C$ . The 200nm Pd gate electrodes were formed by electron beam evaporation and lift off lithography process.

#### Results and discussion

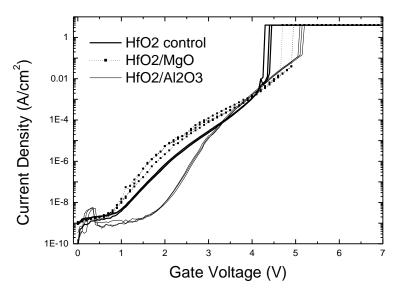

The current density measured at positive gate bias shows uniform leakage properties across all three samples (figure 5). As expected the HfO<sub>2</sub> control sample (smallest physical thickness) presents the lowest breakdown voltage. The HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack shows the highest breakdown voltage. In the 1V to 4V bias range the control sample exhibits a lower leakage current density than the MgO/HfO<sub>2</sub> despite the extra ~ 1 nm MgO layer. This could be explained by the presence of a trap assisted tunnelling current mechanism, as is the subject of further investigations.

Figure 5. Leakage current densities measured on several 50x50 μm<sup>2</sup> sites on each sample.

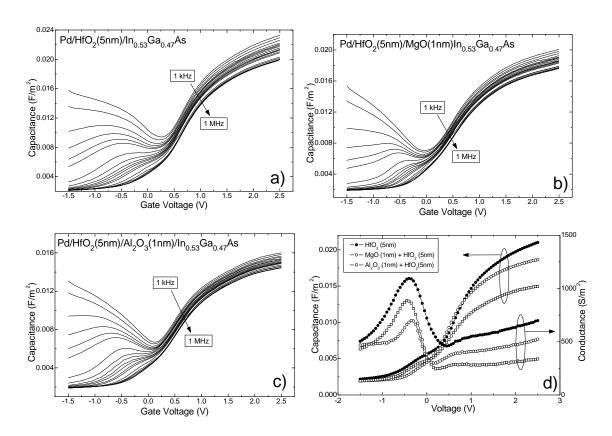

Figure 6 (a, b and c) presents the CV characteristics of the three samples measured over a wide range of frequencies. The capacitance equivalent oxide thickness is highest for the control sample and lowest for the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bi-layer. This result correlates with the breakdown trend for this set of samples. Assuming the interlayer and HfO<sub>2</sub> physical

thickness to be identical for both bi-layer samples this indicates that the MgO film has a higher dielectric constant than the  $Al_2O_3$ . The frequency dispersion in the accumulation region for the three samples could be induced by oxide border traps which are able to respond to the measurement frequency [9]. This effect should be less prominent in MOS structures with thicker oxides as the oxide traps contribution to the capacitance could be dominant regardless of its fluctuation with frequency and as a result the measured capacitance will tend to  $C_{max}$  with less dispersion.

All three samples also display significant frequency dependence in the depletion/inversion region of the CV. In the case of an interface defect with a discrete energy level in the band gap, the CV curve is expected to go through a peak (observed at intermediate frequencies in figures 6a, 6b and 6c). The continuous increase of capacitance in inversion at low measurement frequency could be attributed either to the minority carriers being able to respond to the low frequency or to the presence of more interface states deeper in the band gap.

Figure 6. Capacitance voltage characteristics measured over a range of frequencies (1kHz to 1MHz) for a) HfO<sub>2</sub> control sample, b) MgO/HfO<sub>2</sub> bi-layer and c) Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>. d) is a CV and GV comparison of all three samples at 100 kHz.

Figure 6d compares the Capacitance and Conductance voltage characteristics measured at 100 kHz on the three samples. The peak conductance (from -1V to 0V) falls in the same bias range as the frequency dependent shoulder in the CV characteristics confirming the conductance loss originates from the interface states. The fact that the interface states behaviour is very similar on all three samples indicates that the dominant interface defect originates from the  $In_{0.53}Ga_{0.47}As$  surface as opposed to the oxide. It must

be emphasised that these electrical characteristics are similar to already published results on  $In_{0.53}Ga_{0.47}As$  MOS structures with unpassivated [10], sulphur passivated [11], and (NH<sub>4</sub>)OH passivated surfaces [12]. The  $In_{0.53}Ga_{0.47}As$  surface in the current study received no chemical passivation treatment, no post deposition anneal, and no forming gas (N<sub>2</sub>/H<sub>2</sub>) annealing. The fact that the results are comparable with those obtained for chemically passivated surfaces is due to careful preparation of the MOVPE  $In_{0.53}Ga_{0.47}As$  epilayers and the fast transfer to the ALD reactor for oxide deposition where exposure to ambient air is kept to minimum.

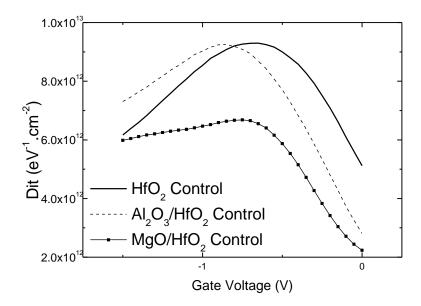

Figure 7. Estimated interface state densities extracted using equation (2) and the relation  $D_{it} = C_{it}/q$ . The low and high frequency CVs were measured at 6 kHz and 1MHz respectively (room temperature).

The high-low frequency method described in the first section was applied to these samples. Figure 7 shows the extracted density of states profiles as a function of gate bias for the three samples using equation (2) and the relation  $D_{it} = C_{it}/q$ . In this study the lowest frequency measurement available couldn't be exploited for this analysis. As the measurement frequency is reduced in order to maximise the interface states response other contributions are also brought into play. In the depletion region, minority carriers will produce a capacitance which will affect the D<sub>it</sub> curve [13]. The data presented in figure 7 was extracted using the capacitance measured at 6 kHz and at 1 MHz. It must be emphasised that the profiles generated using intermediate frequencies could lead to a slightly underestimated density of interface states. However, these profiles are useful for a comparative evaluation of the interface state densities present in the different samples since they are obtained under the same conditions. In addition the densities extracted using this CV method confirm the conductance results of figure 6d for which the HfO<sub>2</sub>/MgO sample presents the lowest D<sub>it</sub>. The peak D<sub>it</sub> position was found to be located ~ 0.4eV above the In<sub>0.53</sub>Ga<sub>0.47</sub>As valence band using the simulated surface potential dependence upon gate voltage (not shown).

#### Conclusion

We have described capacitance voltage characterisation techniques when applied to compound semiconductors. Some of the significant differences as compared with common Si MOS characteristics were discussed. In the second part, the efficacy of three high- $k/In_{0.53}Ga_{0.47}As$  MOS structures in terms of device electrical behaviour was compared. The benefit of using an  $Al_2O_3$  or an MgO interlayer between the HfO<sub>2</sub> film and the  $In_{0.53}Ga_{0.47}As$  surface was compared in terms of leakage current and interface state density. The MgO material presented the lowest interface state density ( $\sim 6x10^{12} \text{ eV}^{-1}.\text{cm}^{-2}$ ) of all three samples examined.

# Acknowledgments

The authors would like to acknowledge Science Foundation Ireland (Grant No 07/SRC/I1172 FORME) and Enterprise Ireland (Grant No IR-2008-0006 ENGAGE) for financial support of this work. The authors would also like to thank John MacHale and Aidan Quinn for the electrical measurements at cryogenic temperature.

#### References

- K. Mistry, C. Allen, C. Auth, B. Beattie, D. Bergstrom, M. Bost, M. Brazier, M. Buehler, A. Cappellani, R. Chau, C.-H. Choi, G. Ding, K. Fischer, T. Ghani, R. Grover, W. Han, D. Hanken, M. Hattendorf, J. He, J. Hicks, R. Huessner, D. Ingerly, P. Jain, R. James, L. Jong, S. Joshi, C. Kenyon, K. Kuhn, K. Lee, H. Liu, J. Maiz, B. McIntyre, P. Moon, J. Neirynck, S. Pae, C. Parker, D. Parsons, C. Prasad, L. Pipes, M. Prince, P. Ranade, T. Reynolds, J. Sandford, L. Shifren, J. Sebastian, J. Seiple, D. Simon, S. Sivakumar, P. Smith, C. Thomas, T. Troeger, P. Vandervoorn, S. Williams, K. Zawadzki, *IEEE International Electron Devices Meeting*, p. 247(2007).

- 2. M. Passlack, M. Hong, J. P. Mannaerts, R. L. Opila, S. N. G. Chu, N. Moriya, F. Ren, J. R. Kwo, *IEEE T. Electron Dev.*, **44**, (2) 214 (1997).

- 3. C. L. Hinkle, M. Milojevic, B. Brennan, A. M. Sonnet, F. S. Aguirre-Tostado, G. J. Hughes, E. M. Vogel, R. M. Wallace, *Appl. Phys. Lett.*, **94**, 162101 (2009).

- 4. E. H. Nicollian and J. R. Brews, *MOS Physics and Technology* Wiley Interscience, New York (1982).

- 5. K Cherkaoui, S. Monaghan, M. A. Negara, M. Modreanu, P. K. Hurley, D. O'Connell, S. McDonnell, G. Hughes, S. Wright, R. C. Barklie, P. Bailey, T. C. Q. Noakes, *J. Appl. Phys.*, **104**, 064113 (2008).

- 6. É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev, P. K. Hurley, *Appl. Phys. Lett.*, **94**, 102902 (2009).

- 7. http://www.nd.edu/~gsnider/

- 8. V. Mosser, R. Sizmann, F. Koch, J. Ziegler, H. Maier, *Semicond. Sci. Technol.*, 3, 808 (1988).

- 9. E. J. Kim, L. Wang, P. M. Asbeck, K. C. Saraswat, P. C. McIntyre, *Appl. Phys. Lett.*, **96**, 012906 (2010).

- 10. Y. C. Chang, M. L. Huang, K. Y. Lee, Y. J. Lee, T. D. Lin, M. Hong, J. Kwo, T. S. Lay, C. C. Liao, and K. Y. Cheng, *Appl. Phys. Lett.*, **92**, 072901 (2008).

- 11. H.-C. Lin, W.-E. Wang, G. Brammertz, M. Meuris, M. Heyns, *Microelectronic Engineering*, **86**, 1554 (2009).

- 12. B. Shin, J. Cagnon, R. D. Long, P. K. Hurley, S. Stemmer, P. C. McIntyre *Electrochem. Solid St. Lett.*, **12**, G40 (2009).

- 13. K. Martens IEEE K. Martens, C. O. Chui, G. Brammertz, B. De Jaeger, D. Kuzum, M. Meuris, M. M. Heyns, T. Krishnamohan, K. Saraswat, H. E. Maes, and G. Groeseneken, *IEEE T. Electron Dev.*, **55**, 547 (2008).