| Title                | Analysis and design of low phase noise CMOS oscillator circuit topologies                                                       |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Authors              | Chlis, Ilias                                                                                                                    |

| Publication date     | 2016                                                                                                                            |

| Original Citation    | Chlis, I. 2016. Analysis and design of low phase noise CMOS oscillator circuit topologies. PhD Thesis, University College Cork. |

| Type of publication  | Doctoral thesis                                                                                                                 |

| Rights               | © 2016, Ilias Chlis http://creativecommons.org/licenses/by-nc-nd/3.0/                                                           |

| Download date        | 2024-04-27 12:28:34                                                                                                             |

| Item downloaded from | https://hdl.handle.net/10468/4146                                                                                               |

# Analysis and Design of Low Phase Noise CMOS Oscillator Circuit Topologies

### Ilias Chlis

# National University of Ireland, Cork

A thesis submitted for the degree of

### DOCTOR OF PHILOSOPHY

Department of Electrical and Electronics Engineering

University College Cork

Marconi Lab, Tyndall National Institute

Research Supervisor: Dr. Domenico Zito

Co-Supervisor: Dr. Domenico Pepe

Head of Department: Prof. Nabeel Riza

January 2016

# **Examining Commission**

Prof. Andrea Bevilacqua University of Padova, Italy

Prof. Michael Peter Kennedy University College Cork, Ireland

Dr. Domenico Zito University College Cork & Marconi Lab, Tyndall National Institute, Ireland

Dr. Domenico Pepe Marconi Lab, Tyndall National Institute, Ireland

# **Declaration**

The submitted thesis is the candidate's own work and has not been submitted for another degree, either at University College Cork or elsewhere.

Ilias Chlis

### Acknowledgements

First of all, I owe many thanks to professor Domenico Zito, who structured the research programme behind this manuscript thesis and provided guidance all levels, and to Dr. Domenico Pepe for his contribution, during all the stages of the research programme.

I am also grateful to the thesis committee, professor Michael Peter Kennedy and Dr. Alan Mathewson for their precious support.

Moreover, I wish to express my gratitude to professor Andrea Bevilacqua for accepting to be the external examiner for this thesis.

Furthermore, I would like to thank the colleagues, fellow members of the Marconi Lab, in particular Dr. Luca Aluigi, Michele Spasaro and Valentina Palazzi.

Last, I am thankful to Zuzanna Łojek, as well as to my family, for their patience and support.

#### **Abstract**

The research activity carried out during the PhD is focused on the study, analysis and design of millimeter-wave integrated oscillator circuits for high-speed wireless communications.

In Chapter 1 comparative analyses of phase noise (PN) in Hartley, Colpitts and common-source cross-coupled differential pair LC oscillator topologies are carried out under common conditions in 28 nm CMOS technology. The impulse sensitivity function (ISF) is used to carry out both qualitative and quantitative analyses of the phase noise exhibited by each circuit component in each circuit topology with oscillation frequency ranging from 1 to 100 GHz. The comparative analyses show the existence of four distinct frequency regions in which the three oscillator topologies rank unevenly in terms of best phase noise performance, due to the combined effects of device noise and circuit node sensitivity. Moreover, the analyses show that there is no superior oscillator topology in the absolute sense, but that the identification of the best circuit topology with respect to phase noise is strictly related to the operating frequency range.

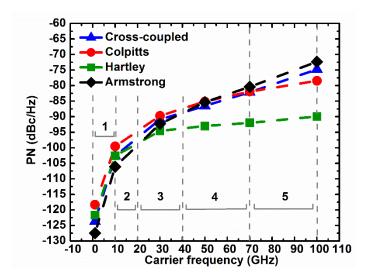

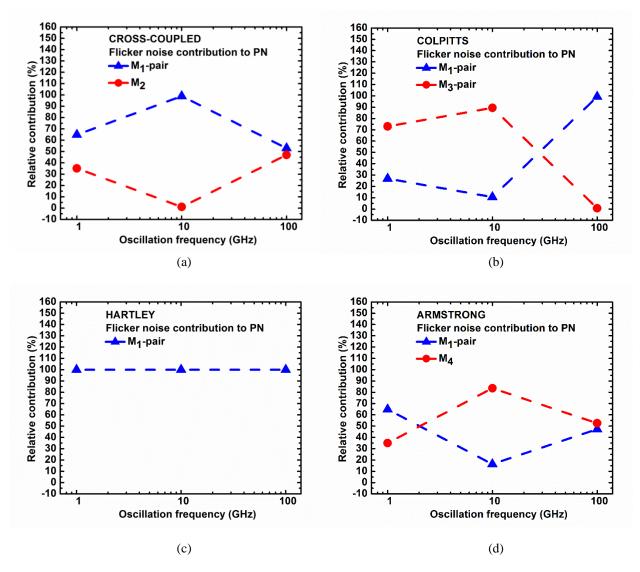

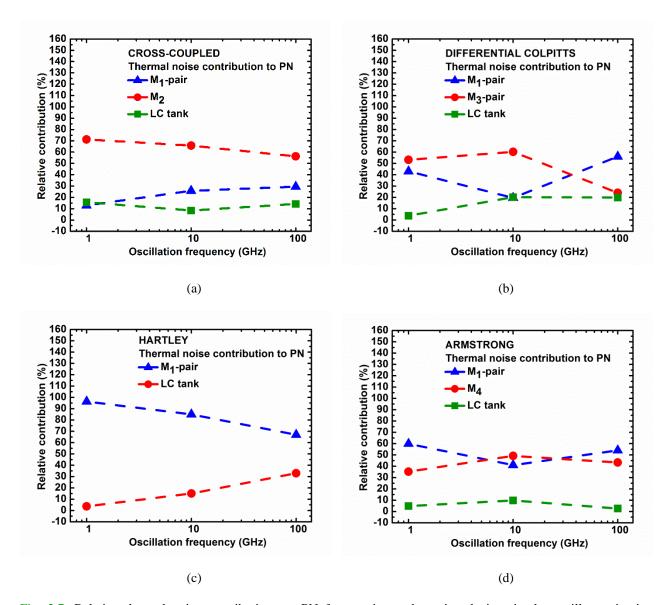

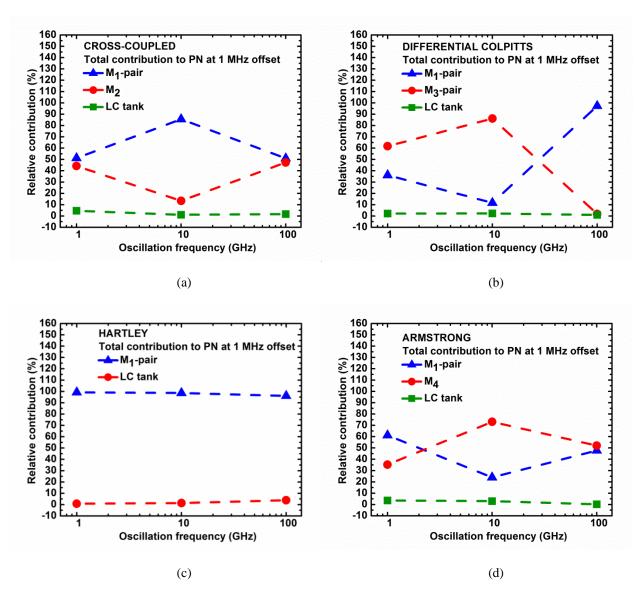

In Chapter 2 comparative phase noise analyses of common-source cross-coupled pair, Colpitts, Hartley and Armstrong differential oscillator circuit topologies, designed in 28 nm bulk CMOS technology in a set of common conditions for operating frequencies in the range from 1 to 100 GHz, are carried out in order to identify their relative performance. The impulse sensitivity function is used to carry out qualitative and quantitative analyses of the noise contributions exhibited by each circuit component in each topology, allowing an understanding of their impact on phase noise. The comparative analyses show the existence of five distinct frequency regions in which the four topologies rank unevenly in terms of best phase noise performance. Moreover, the results obtained from the impulse sensitivity function show the impact of flicker noise contribution as the major effect leading to phase noise degradation in nano-scale CMOS LC oscillators.

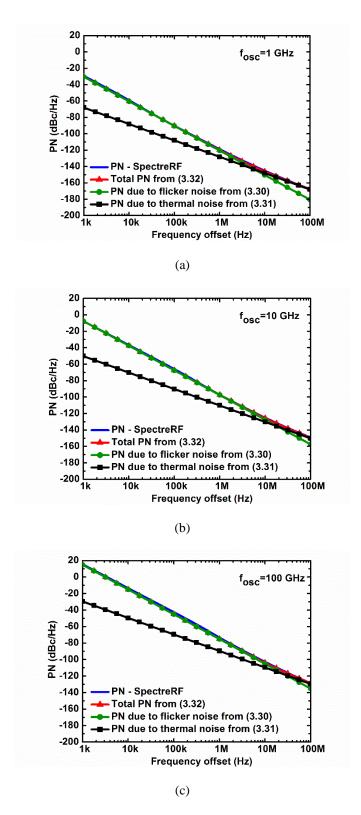

Chapter 3 reports a phase noise analysis in a differential Armstrong oscillator circuit topology in CMOS technology. The analytical expressions of phase noise due to flicker and thermal noise sources are derived and validated by the results obtained through SpectreRF simulations for oscillation frequencies of 1, 10 and 100 GHz. The analysis captures well the phase noise of the oscillator topology and shows the impact of flicker noise contribution as the major effect leading to phase noise degradation in nano-scale CMOS LC oscillators.

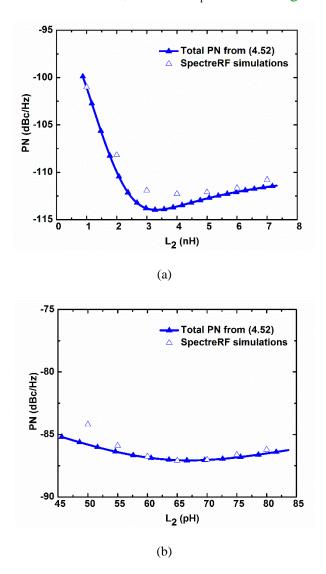

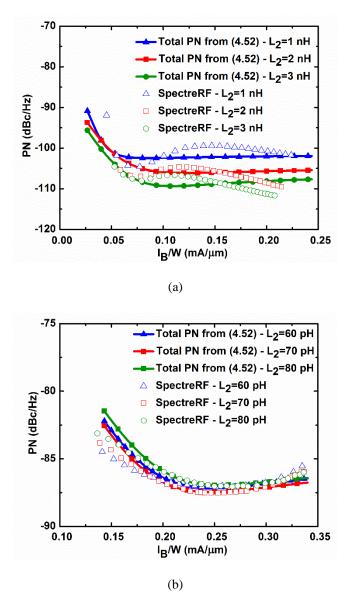

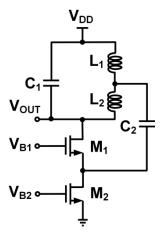

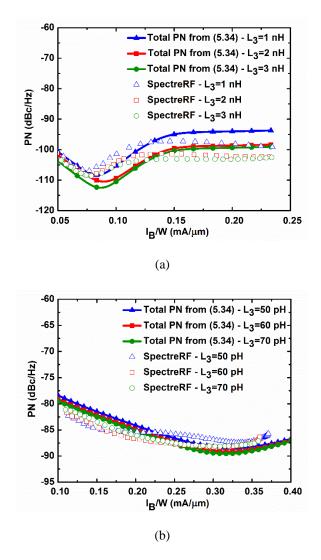

Chapter 4 reports the analyses of three techniques for phase noise reduction in the CMOS Colpitts oscillator circuit topology. Namely, the three techniques are: inductive degeneration, noise filter, and optimum current density. The design of the circuit topology is carried out in 28 nm bulk CMOS technology. The analytical expression of the oscillation frequency is derived and validated through circuit simulations. Moreover, the theoretical analyses of the three techniques are carried out and verified by means of circuit simulations within a commercial design environment. The results obtained for the inductive degeneration and noise filter show the

existence of an optimum inductance for minimum phase noise. The results obtained for the optimum bias current density technique applied to a Colpitts oscillator circuit topology incorporating either inductive degeneration or noise filter, show the existence of an optimum bias current density for minimum phase noise. Overall, the analyses show that, with respect to the reference values obtained in Chapter 2, the adoption of these techniques may lead to a potential phase noise reduction up to 19 dB and 17 dB at a 1 MHz frequency offset for the oscillation frequencies of 10 GHz and 100 GHz respectively.

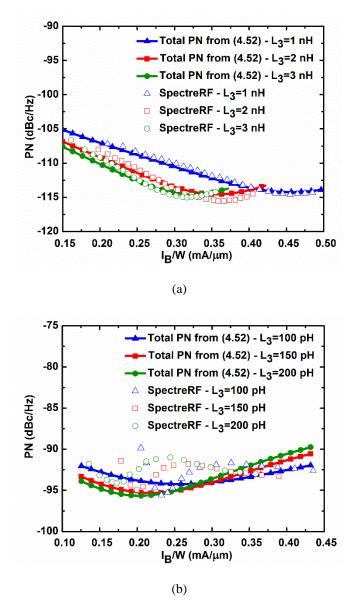

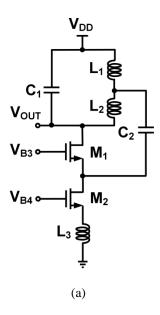

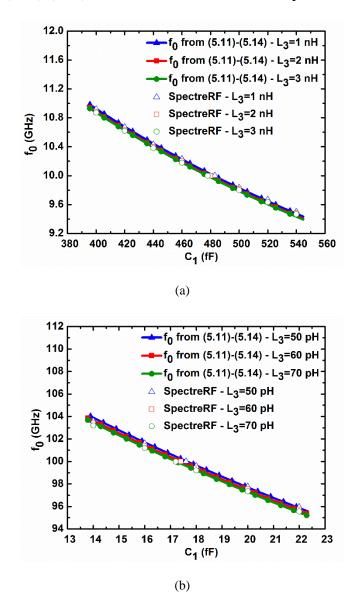

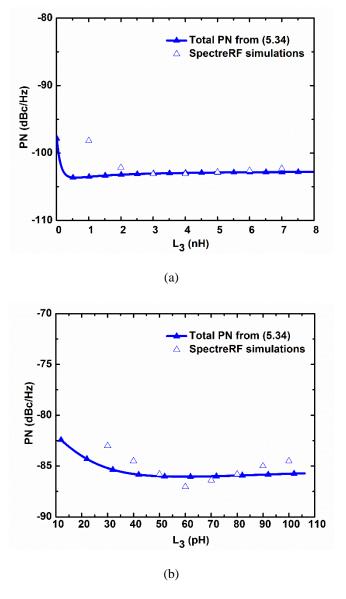

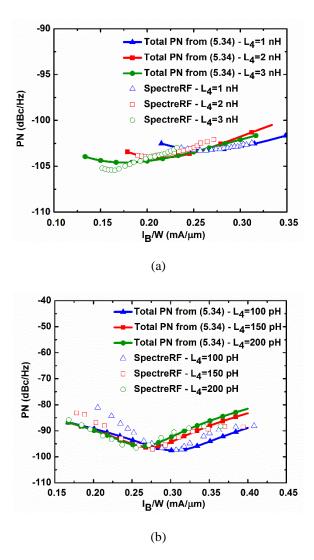

Chapter 5 reports the analyses of the three techniques discussed in Chapter 4, applied to the CMOS Hartley oscillator circuit topology. The design of the circuit topology is carried out in 28 nm bulk CMOS technology. The analytical expression of the oscillation frequency is derived and validated through circuit simulations. Moreover, the theoretical analyses of the three techniques are carried out and verified by means of circuit simulations. As in the case of the Colpitts topology, the results obtained for the inductive degeneration and noise filter show the existence of an optimum inductance for minimum phase noise. The results obtained for the optimum bias current density technique applied to a Hartley oscillator circuit topology incorporating either inductive degeneration or noise filter, show the existence of an optimum bias current density for minimum phase noise. Overall, wih respect to the reference values obtained in Chapter 2, the analyses show that the adoption of these techniques may lead to a potential phase noise reduction up to 17 dB and 16 dB at a 1 MHz frequency offset for the oscillation frequencies of 10 GHz and 100 GHz respectively, with respect to the traditional Hartley topology.

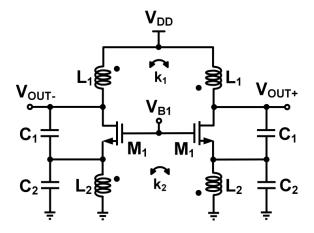

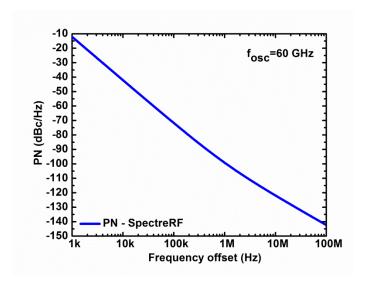

Finally, Chapter 6 reports the design of an advanced solution, adopting the techniques discussed in Chapters 4 and 5. The voltage-controlled oscillator (VCO) topology can be tuned from 58.1 GHz to 63.3 GHz. From periodic steady state (PSS) and periodic noise (Pnoise) SpectreRF simulations the best phase noise performance is observed for  $f_0$ =63.3 GHz, and amounts to -100.2 dBc/Hz at a 1 MHz frequency offset from the oscillation frequency, for a power consumption of 13.6 mW. This corresponds to a figure of merit (FOM) of 185 dB.

#### **Preface**

The recent advances in silicon technologies allow us to implement integrated transceivers operating at the millimeter-waves, enabling the realization of a new class of mass-market devices for very high data rate wireless communications, such as 60 GHz uncompressed wireless video communications. In spite of some encouraging results in transceiver integration, system-level studies reported in the literature have emphasized the need of building-blocks with superior performance in order to overcome the main limitations for an efficient system-on-chip implementation of the overall transceivers.

In particular, oscillator phase noise (PN) is one of the main bottlenecks for the information capacity of communication systems, leading to severe challenges in the design of local oscillators, especially at very high frequencies. However, no complete comparative studies have been carried out on how to choose the oscillator circuit topology that could potentially offer the best performance in terms of phase noise for the range of operating frequencies of modern telecommunication systems. Usually, thanks to its reliable start-up, the common-source cross-coupled differential pair topology is chosen a priori without any further considerations.

On the basis of the above motivations, the research activity carried out during the PhD dealt with this open question not addressed by the literature. The investigations could allow us to extend the range of possibilities beyond the common practice of choosing the common-source cross-coupled differential pair topology, traditionally selected for its reliable start-up, but without further topological considerations.

The PhD thesis is organized in six chapters. The presentation order follows the thesis schedule.

Chapter 1 reports a comparative analysis in terms of phase noise performance of the single-ended Colpitts, single-ended Hartley and common-source cross-coupled topogogies, under common conditions, for a discrete set of operating frequencies from 1 to 100 GHz.

Chapter 2 extends the comparative analysis of phase noise carried out in Chapter 1 to the Colpitts, Hartley and Armstrong differential oscillator topologies.

Chapter 3 addresses a complete analytical study of phase noise in the differential Armstrong topology, with the objective of providing a closed-form symbolic expression for the phase noise in both the  $1/f^3$  and  $1/f^2$  regions, by using the impulse sensitivity function (ISF).

Chapter 4 reports the analysis and design of three techniques for phase noise reduction in a single-ended Colpitts oscillator circuit topology. In particular, the techniques of inductive degeneration, noise filter and optimum current density.

In Chapter 5 the techniques discussed in Chapter 4 are applied and analysed for the design of a single-ended Hartley oscillator circuit topology.

Finally, Chapter 6 presents a novel differential Colpitts voltage-controlled oscillator (VCO) topology adopting the techniques of phase noise reduction discussed in Chapters 4 and 5.

The original contributions of this PhD thesis to the state of the art are referred with the label OP (e.g. [OP1]), and reported in the List of Publications.

# Contents

| De | eclaration                                                                | i    |

|----|---------------------------------------------------------------------------|------|

| A  | cknowledgements                                                           | ii   |

| Al | bstract                                                                   | iii  |

| Pr | reface                                                                    | vi   |

| Co | ontents                                                                   | viii |

| 1  | Colpitts, Hartley and Common-Source Cross-Coupled Topologies              | 1    |

|    | 1.1 Introduction                                                          | 1    |

|    | 1.2 Circuit Topologies                                                    | 2    |

|    | 1.3 Impulse Sensitivity Function                                          | 4    |

|    | 1.3.1 Simulation Steps and Settings                                       | 5    |

|    | 1.3.2 Results                                                             | 7    |

|    | 1.4 Analyses and Comparison versus Oscillation Frequency                  | 11   |

|    | 1.4.1 Comparative Analysis between Devices                                | 14   |

|    | 1.4.2 Comparative Analysis between Topologies                             | 17   |

|    | 1.5 Topology Performances versus Oscillation Frequency Regions            | 19   |

|    | 1.6 Conclusions                                                           | 21   |

| 2  | Colpitts, Hartley, Common-Source Cross-Coupled and Armstrong Differential |      |

|    | topologies                                                                | 23   |

|    | 2.1 Introduction                                                          | 23   |

|    | 2.2 Circuit Topologies                                                    | 25   |

|    | 2.3 Comparison of Phase Noise Performance                                 | 27   |

|    | 2.4 Contributions of the Device Noise to Phase Noise                      | 32   |

|    | 2.5 Conclusions                                                           | 39   |

| 3  | Phase Noise Analysis of a Differential Armstrong Topology                 | 40   |

|    | 3.1 Introduction                                                          | 40   |

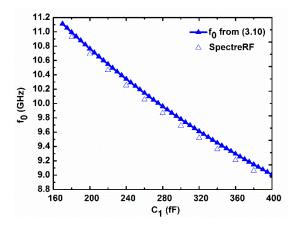

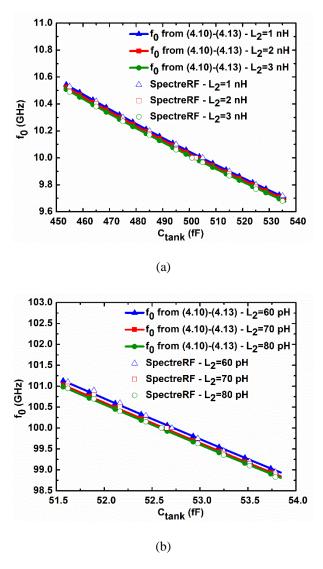

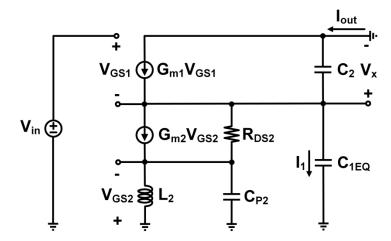

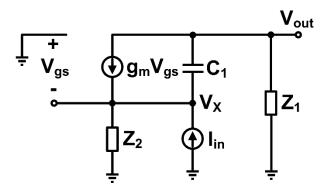

|    | 3.2 Oscillation Frequency                                                 | 41   |

|    | 3.3 Phase Noise Analysis                                                  | 45   |

|    | 3.4 Numerical Evaluations and Circuit Simulations                         | 49   |

|    | 3.5 Conclusions                                                           | 52   |

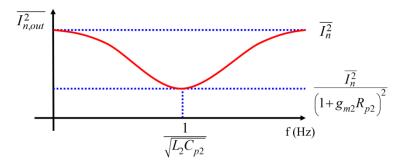

| 4  | Phase Noise Reduction Techniques in the Colpitts Topology                 | 53   |

|    | 4.1 Introduction                                               | 53  |

|----|----------------------------------------------------------------|-----|

|    | 4.2 Inductive Degeneration                                     | 55  |

|    | 4.2.1 Oscillation Frequency                                    | 56  |

|    | 4.2.2 Optimum Inductance for Minimum Phase Noise               | 59  |

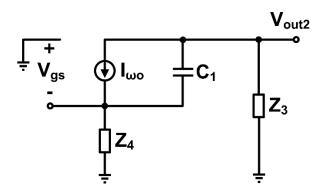

|    | 4.3 Noise Filter                                               | 67  |

|    | 4.3.1 Oscillation Frequency                                    | 68  |

|    | 4.3.2 Optimum Inductance for Minimum Phase Noise               | 71  |

|    | 4.4 Optimum Current Density                                    | 75  |

|    | 4.4.1 Inductive Degeneration                                   | 75  |

|    | 4.4.2 Noise Filter                                             | 78  |

|    | 4.5 Conclusions                                                | 80  |

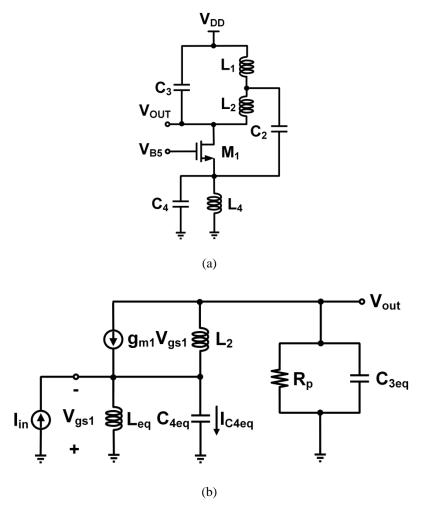

| 5  | Phase Noise Reduction Techniques in the Hartley Topology       | 82  |

|    | 5.1 Introduction                                               | 82  |

|    | 5.2 Inductive Degeneration                                     | 83  |

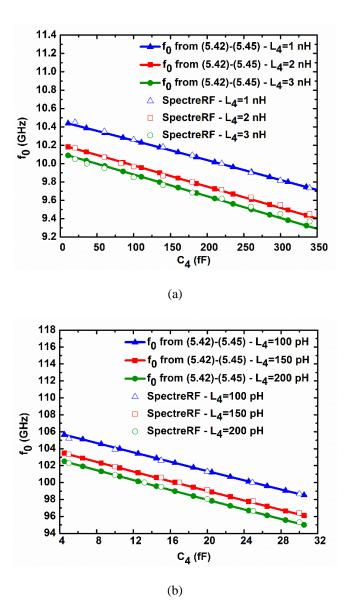

|    | 5.2.1 Oscillation Frequency                                    | 83  |

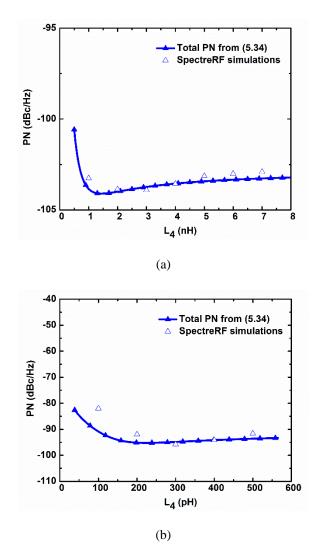

|    | 5.2.2 Optimum Inductance for Minimum Phase Noise               | 87  |

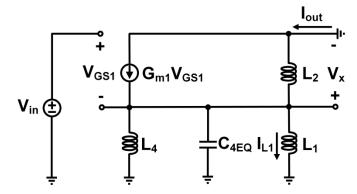

|    | 5.3 Noise Filter                                               | 92  |

|    | 5.3.1 Oscillation Frequency                                    | 93  |

|    | 5.3.2 Optimum Inductance for Minimum Phase Noise               | 95  |

|    | 5.4 Optimum Current Density                                    | 100 |

|    | 5.4.1 Inductive Degeneration                                   | 100 |

|    | 5.4.2 Noise Filter                                             | 102 |

|    | 5.5 Conclusions                                                | 104 |

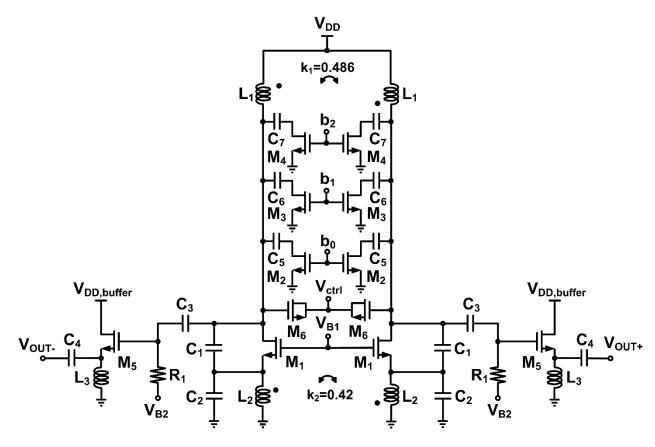

| 6  | Design of a Low Phase Noise Differential Colpitts VCO Topology | 106 |

|    | 6.1 Introduction                                               | 106 |

|    | 6.2 Oscillation Frequency and Output Voltage                   | 107 |

|    | 6.2.1 Oscillation Frequency                                    | 107 |

|    | 6.2.2 Output Voltage                                           | 109 |

|    | 6.3 Post-Layout Simulation Results                             | 110 |

|    | 6.4 Conclusions                                                |     |

| Co | onclusions                                                     | 114 |

| List of Publications              | 116 |

|-----------------------------------|-----|

| Bibliography                      | 118 |

| List of Symbols and Abbreviations | 126 |

| List of Figures                   |     |

| List of Tables                    | 130 |

| Index                             | 131 |

#### Chapter 1

### Colpitts, Hartley and Common-Source Cross-Coupled Topologies

#### 1.1 Introduction

Oscillator phase noise (PN) is one of the main bottlenecks for the information capacity of communication systems, leading to severe challenges in the design of local oscillators in silicon technologies, especially at very high frequency [1-5]. In particular, the main difficulties are to achieve a high quality factor LC tank [6-11] and consume a reasonable power [12-13].

Oscillator phase noise has been studied extensively over the last decades [14-17]. Most of these studies are based on linear time-invariant (LTI) oscillator models, which provide important qualitative design insights, but are limited in the quantitative prediction of the power spectral density levels [18], in some cases addressed by adopting nonlinear approaches [19].

The linear time-variant (LTV) oscillator model allows a quantitative understanding of oscillator phase noise through the Impulse Sensitivity Function (ISF), represented as  $\Gamma(x)$  [18]. Since the oscillator is assumed as a linear time-varying circuit, the phase sensitivity to noise perturbations can be described in terms of its (time-varying) impulse response.

The evaluation of the ISF involves a significant amount of transient simulations and data extractions, resulting in time consuming calculations, potentially prone to inaccuracy. Recently, new efficient frequency-domain methods operating directly in the steady-state were proposed [20, 21], allowing a consistent reduction of the simulation workload. Regardless of the methods, the analysis of the phase sensitivity can contribute significantly to a better understanding of the impact of noise sources to the oscillator phase noise in the most widespread circuit topologies.

A comparative analysis of common-source cross-coupled differential pair and differential Colpitts LC oscillators in 0.35 µm CMOS technology at 2.9 GHz was carried in [22], showing the superior performance of the cross-coupled differential topology. In this perspective, it could be interesting to extend the comparison also to other topologies, technology nodes and oscillation frequencies.

This chapter reports a comparative study of phase noise for the three oscillator topologies: Hartley, Colpitts and common-source cross-coupled differential pair circuit topologies in 28 nm CMOS technology. The results of the analyses show interesting aspects not addressed by the literature. In detail, all the steps for an accurate derivation of the ISF are summarized and the phase noise predictions for a wide set of amplitudes of the injected current pulse are compared with the results obtained by the direct plots obtained by means of SpectreRF-Cadence Periodic Steady State (PSS) analysis. The contributions from each noise source to the overall phase noise are evaluated qualitatively and quantitatively through the ISF for each topology operating in a discrete set of frequencies from 1 to 100 GHz.

The chapter is organized as follows. Section 1.2 reports the design of the three oscillator topologies in 28 nm CMOS technology. Section 1.3 summarizes the key analytical expressions for phase noise predictions through the ISF, the key steps and settings for accurate evaluations, and finally reports the results for the oscillation frequency of 10 GHz. In Section 1.4, qualitative and quantitative analyses of the phase noise contributed by each circuit component are carried out for each topology for a discrete set of oscillation frequencies ranging from 1 to 100 GHz. Section 1.5 reports the results that reveal the existence of four different frequency regions in which the best phase noise performance is given case by case by a different topology. In Section 1.6, the conclusions are drawn.

The key contents of this chapter have been reported in original contributions published in an international peer-reviewed journal and in conference proceedings [OP1, OP6].

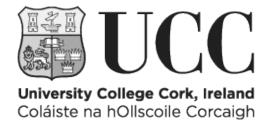

#### 1.2 Circuit Topologies

Three LC oscillator topologies have been analysed: single-ended Colpitts, single-ended Hartley and top-biased common-source cross-coupled differential pair oscillator topologies, as shown in Fig. 1.1. The three oscillator circuit topologies have been implemented in 28 nm bulk CMOS technology by ST-Microelectronics by adopting the same criteria for a fair comparison as follows. The frequency of operation is 10 GHz. The sizes of the transistors and the value of the inductors and capacitors used are reported in Table 1.1. Despite this work is addressed to the investigations of the circuit topologies as such, rather than the circuit design and implementation, i.e. regardless of the effects of parasitic components, we considered a reasonable quality factor for the LC tank in order to carry out the comparative study of the properties of each circuit topology under the same typical conditions. Thereby, a quality factor (Q) equal to 10 has been assumed for the inductors, considering a parasitic resistance in series with the inductor, whereas the capacitors have been considered as ideal devices. In all cases the power consumption is 6.3 mW.

A small signal noise analysis by SpectreRF was used for the derivation of the flicker noise corner of each transistor. Assuming that the power spectral density (PSD) of the thermal and flicker noise currents generated by the transistor in the saturation region are given by equations (1.1) and (1.2) respectively, the flicker noise corner is given by equation (1.3) [23].

$$S_{iw} = 4kT\gamma g_m \tag{1.1}$$

$$S_{if} = g_m^2 \frac{k_f}{WLC_{ox}} \frac{1}{f^c}$$

(1.2)

$$f_{1/f} = \sqrt[c]{\frac{k_f}{WLC_{ox}} \frac{g_m}{4kT\gamma}}$$

(1.3)

Fig. 1.1. Schematic of the oscillator circuit topologies: (a) single-ended Colpitts; (b) single-ended Hartley; (c) top-biased common-source cross-coupled differential pair.  $V_{B1}$ ,  $V_{B2}$  and  $V_{B3}$  are DC bias voltages.

Table 1.1. Device Sizing.

| Transistor Width [μm] |       |       | Capacitor value [pF] |       |       |       | Inductor value [pH] |       |       |

|-----------------------|-------|-------|----------------------|-------|-------|-------|---------------------|-------|-------|

| $M_1$                 | $M_2$ | $M_3$ | $M_4$                | $C_1$ | $C_2$ | $C_3$ | $C_4$               | $L_1$ | $L_2$ |

| 30                    | 30    | 30    | 15                   | 0.97  | 0.495 | 0.8   | 0.229               | 500   | 250   |

where  $k_f$  is a bias-dependent constant, c is a constant with typical values ranging from 0.7 to 1.2,  $C_{ox}$  is the oxide capacitance per unit area and  $\gamma$  is the excess noise coefficient. For the 28 nm bulk CMOS technology adopted, the thickness of the oxide  $t_{ox}$  is about 1.4 nm for the n-MOSFET and 1.7 nm for the p-MOSFET, from which we can derive that  $C_{ox}$  is about 0.026 and 0.02 F/m<sup>2</sup>, respectively. The values of  $k_f$ ,  $t_{1/f}$  and c have been derived by means of noise simulation of each single stand-alone transistor of Table 1.1. They are reported in Table 1.2.

Table 1.2. Impulse Sensitivity Function.

| Transistor     | $k_f(V^2F)$            | f <sub>1/f</sub> (MHz) | С    |

|----------------|------------------------|------------------------|------|

| $\mathbf{M}_1$ | 1.09×10 <sup>-22</sup> | 1390                   | 0.9  |

| $M_2$          | 2.26×10 <sup>-23</sup> | 870                    | 0.9  |

| $M_3$          | 1.88×10 <sup>-23</sup> | 1100                   | 0.93 |

| $M_4$          | 1.25×10 <sup>-22</sup> | 1430                   | 0.9  |

#### 1.3 Impulse Sensitivity Function

In order to get an insight of the noise contribution of each circuit component in each circuit topology, hereinafter we make use of the ISF as a predictive tool for quantitative and qualitative phase noise evaluations.

A detailed procedure for computation of the ISF and phase noise prediction in a linear time-varying system in the case of a source-coupled CMOS multi-vibrator with operating frequency up to 2 MHz was presented in [24]. All the results were achieved only for a single amplitude value of the injected pulse. However, the time-domain evaluation of the ISF involves a number of transient simulations, resulting potentially prone to inaccuracy. Thereby, it is worth consolidating all the steps in order to achieve accurate results.

The impulse response from each current noise source to the oscillator output phase can be written as [18]:

$$h_{\phi}(t,\tau) = \frac{\Gamma(\omega_0 \tau)}{q_{\text{max}}} u(t-\tau)$$

(1.4)

where  $q_{max}$  is the charge injected into a specific circuit node of the oscillator at time  $t=\tau$ , u(t) is the unity step function and  $\Gamma(\omega_0\tau)$  is a dimensionless periodic function that can be expressed as a Fourier series [18]:

$$\Gamma(\omega_0 \tau) = \frac{c_0}{2} + \sum_{n=1}^{\infty} c_n \cos(n\omega_0 \tau + \theta_n)$$

(1.5)

The DC and root mean square (rms) values of  $\Gamma(\omega_0\tau)$  are given by the following two equations [18]:

$$\Gamma_{DC} = \frac{c_0}{2} \tag{1.6}$$

$$\Gamma_{rms} = \sqrt{\frac{1}{2} \sum_{n=0}^{\infty} c_n^2} \tag{1.7}$$

The thermal noise contribution to the phase noise spectrum for any oscillator, this last traditionally indicated with  $\mathcal{Z}$ , from each given noise source with a white power spectral density, can be expressed as [18]

$$\left[ \left[ \Delta \omega \right] \right]_{flicker} = \frac{\Gamma_{rms}^2}{q_{max}^2} \frac{\left( \frac{\overline{i_n}^2}{\Delta f} \right)}{2\Delta \omega^2}$$

(1.8)

where  $q_{max}$  is the charge injected into a circuit node by the noise source insisting in that node and  $\Delta\omega$  is the offset from the oscillation angular frequency. Therein [18], it is tacitly assumed that c in equation (1.2) is equal to 1, regardless of the technology node. This assumption leads to the above relatively rough but simple equation (1.8).

The flicker noise contribution to the phase noise spectrum for any oscillator, from each given noise source with a 1/f spectrum can be expressed as follows [18], where  $\omega_{1/f}$  is the flicker noise corner of the device

$$\left[ \left[ \Delta \omega \right] \right]_{thermal} = \frac{c_0^2}{q_{max}^2} \frac{\left( \frac{\overline{i_n^2}}{\Delta f} \right)}{8\Delta \omega^2} \frac{\omega_{1/f}}{\Delta \omega}$$

(1.9)

#### 1.3.1 Simulation Steps and Settings

All the simulations have been carried out by using the SpectreRF simulator in the Cadence design environment. The ISF of the oscillator topologies has been evaluated for an oscillation frequency of 10 GHz, which will be considered hereinafter as a reference for all the other cases. First we run a transient simulation in order to observe and record when the amplitude of the oscillation waveform reaches the steady state regime. In our case, this occurs with large margins after 5 ns. Afterwards, we perform other transient simulations applying current impulsive sources acting in parallel with the actual inherent current noise sources of the LC tank and transistors, by

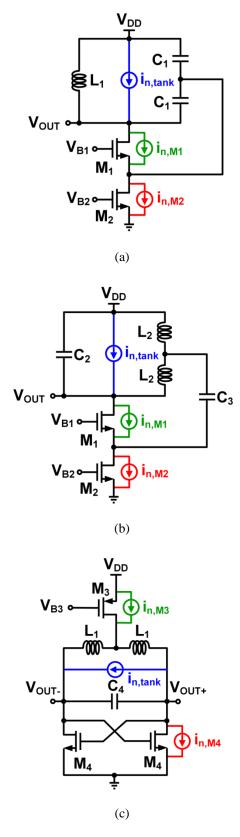

activating only one noise source at one time. The current impulses are set to occur in the steady state regime starting from a given time reference for the unperturbed solution. The pulse width of each current source has been chosen equal to 1 ps (i.e. one hundredth of the oscillation period) with 0.1 ps rise and fall time, as shown in Fig. 1.2.

Fig. 1.2. The injected current pulse.

The simulation has been repeated for amplitudes of the injected current of 1, 10, 100  $\mu$ A and 1, 10 mA. Each transient analysis is performed using the conservative mode and a maximum time step of 10 fs (i.e. one 10-thousandth of the oscillation period), in order to have a good accuracy even in the case of the smallest injected current pulse (i.e. 1  $\mu$ A). The charge  $q_{max}$  injected in each node corresponds to the area under each pulse, i.e. the area of the trapezoid, of Fig. 1.2.

$$q_{\text{max}} = I_{\text{pulse}} \times 1.1 \times 10^{-12} \text{ Coulombs}$$

(1.10)

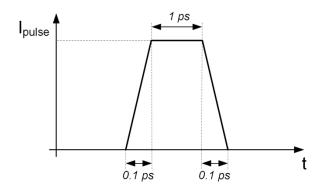

where  $I_{pulse}$  is the amplitude value of each source pulse. This is repeated for all the N noise sources connected in parallel, for all the M instants of time over one period of oscillation, where N=3 and M=40, in our case. The time instants have been chosen to be equally spaced in an oscillation period. The time shift caused by the impulse injection can be extracted by comparing the perturbed and unperturbed waveforms. This means that when the oscillation has reached the steady state regime, the time shift  $\Delta t_i$  of the zero-crossing instant of the perturbed oscillation with respect to the unperturbed one, i.e. when no impulse is applied, is calculated as shown in Fig. 1.3.

Fig. 1.3. Time shift  $\Delta t$  caused by the impulse injection occurring at the time  $\tau$ .

Then, these time shifts are converted into phase shifts by using the following relation

$$\Gamma(x = \omega_0 t) = 2\pi \frac{\Delta t_i(t)}{T} \tag{1.11}$$

In order to take into account the cyclostationary nature of the active device noise sources,  $\Gamma(x)$  is multiplied with  $\alpha(x)$ , where  $\alpha(x)$  is the absolute value of the unperturbed current flowing in the respective node in which the impulses are injected, and at the same time instant in which they are injected, normalized to its maximum value in the period. Then, the DC and root mean square (rms) components of the product  $\Gamma(x) \times \alpha(x)$  can be calculated as follows

$$\Gamma_{DC} = \frac{\sum_{i=1}^{40} \left[ \Gamma(x) \alpha(x) \right]}{40} \tag{1.12}$$

$$\Gamma_{rms} = \sqrt{\frac{\sum_{i=1}^{40} \left\{ \left[ \Gamma(x) \alpha(x) \right]^2 \right\}}{40}}$$

(1.13)

Finally, the total phase noise of the oscillator is computed by adding the contributions from all the noise sources acting in the circuit, according to (1.8) and (1.9). In particular, the active devices inject noise to the terms responsible for both flicker and thermal noise contributions to the oscillator phase noise, whereas the LC tank participates only to the thermal noise contribution to phase noise. Equation (1.14) gives the total phase noise for each of the three oscillators, where m is the number of transistors of the oscillator circuit. The first sum in (1.14) describes the phase noise contribution from the thermal noise. As a result, it contains an additional term (m+1), due to thermal noise coming from the LC tank.

$$\left[ \left[ \left[ \Delta \omega \right] \right]_{total} = 10 \log \left\{ \sum_{i=1}^{m+1} \left[ \frac{\Gamma_{ms}^{2}}{q_{max}^{2}} \frac{\left( \overline{i_{n}^{2}} \right)}{2 \Delta \omega^{2}} \right] + \sum_{i=1}^{m} \left[ \frac{\Gamma_{DC}^{2}}{q_{max}^{2}} \frac{\left( \overline{i_{n}^{2}} \right)}{\Delta f}_{i} \left( \omega_{1/f} \right)_{i}}{8 \Delta \omega^{2}} \right] \right\}$$

(14)

#### 1.3.2 Results

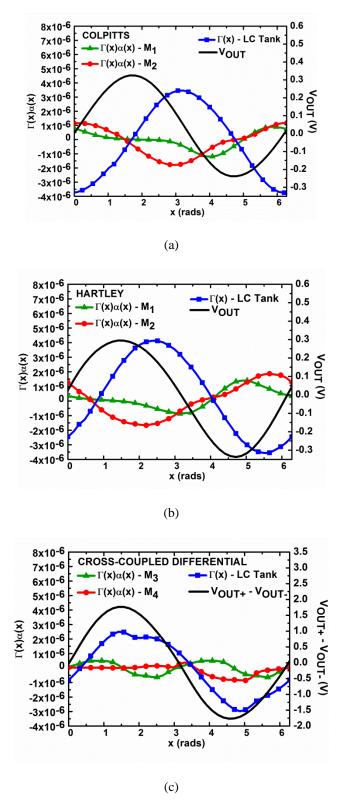

Fig. 1.4 reports  $\Gamma(x) \times \alpha(x)$  for an injected current pulse amplitude of 1  $\mu$ A versus the phase for the injected noise sources, during one oscillation period, for the three oscillator circuit topologies.

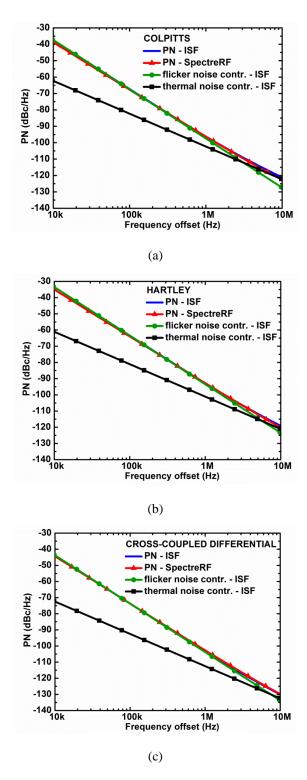

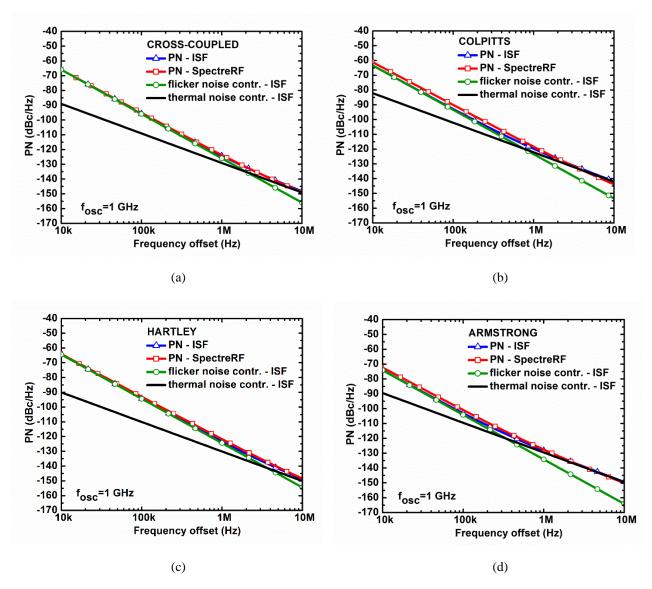

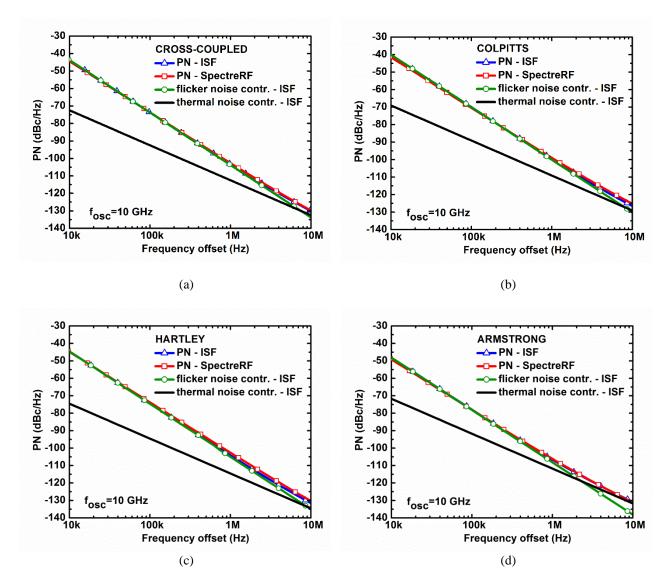

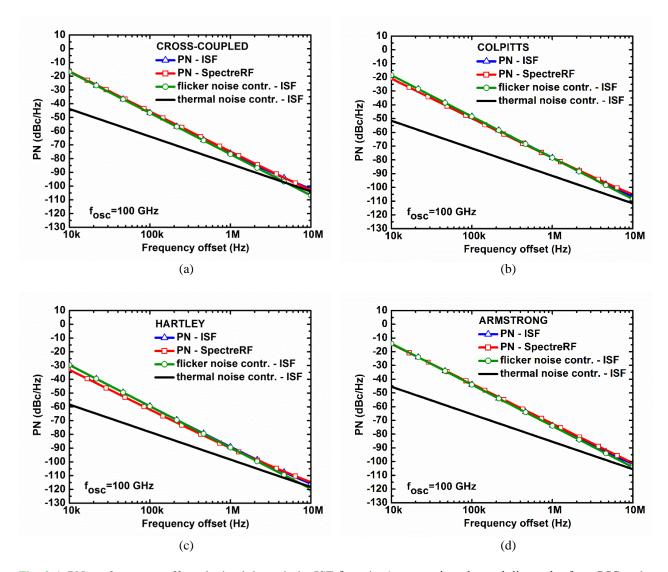

Fig. 1.5 reports the comparison between the phase noise obtained through the ISF and the phase noise obtained by direct plots from PSS and periodic noise simulations, for the three

oscillator circuit topologies. Note that the phase noise predicted by the ISF is very close to the values obtained by means of SpectreRF simulations. Table 1.3 provides the phase noise results for all the current impulse amplitude values, for a 1 MHz frequency offset from the carrier.

PN [dBc/Hz] @ 1 MHz frequency offset Topology SpectreRF **ISF**  $10 \mu A$ 100 µA 1 mA 10 mA Colpitts -96.25 -96.20 -98.33 -98.49 -98.50 -98.45 -92.75 -92.79 -95.18 -94.85 -95.29 Hartley -94.36 Cross-coupled -102.69 -102.84 -102.84 -102.94 -102.66 -102.83

Table 1.3. Summary of the PN results obtained by SpectreRF and ISF.

Note that for this oscillation frequency (10 GHz) the phase noise of the common-source cross-coupled differential pair topology is lower to the phase noise of the Colpitts topology, in agreement with [22], and that the phase noise of Colpitts is lower to the phase noise exhibited by the Hartley topology. Moreover, note that the agreement degrades for higher pulse amplitudes, when the current-to-phase transfer function starts becoming nonlinear. The amplitude in which this occurs is slightly different for each oscillator topology, but for the injected current impulse of 1  $\mu$ A, the difference between the phase noise predicted by the ISF method and the one given by PSS and periodic noise (Pnoise) analysis is lower than 1 % at a 1 MHz frequency offset.

Fig. 1.4.  $\Gamma(x) \times \alpha(x)$  of the MOSFETs and  $\Gamma(x)$  of the LC tank vs. phase for a 1  $\mu$ A amplitude current impulse, for the oscillation frequency of 10 GHz: (a) Colpitts topology; (b) Hartley topology; (c) Common-source cross-coupled differential pair topology.

Fig. 1.5. PN vs. frequency offset for the three oscillator circuit topologies, obtained through the ISF for a 1  $\mu$ A current impulse and direct plot from PSS and periodic noise (PN) SpectreRF simulations, for the oscillation frequency of 10 GHz. The flicker and thermal noise contributions to the overall PN are also plotted in order to identify the  $1/f^3$  PN frequency corner. (a) Colpitts. The  $1/f^3$  PN corner is at the frequency offset of 3.1 MHz. (b) Hartley. The  $1/f^3$  PN corner is at the frequency offset of 5.7 MHz. (c) Common-source cross-coupled differential pair. The  $1/f^3$  PN corner is at the frequency offset of 7.5 MHz.

#### 1.4 Analyses and Comparison versus Oscillation Frequency

The investigations through the ISF can provide a better understanding of the phase noise in each oscillator topology. In order to be able to extract further useful considerations about the devices and topologies, the previous analyses have been reiterated also for other oscillation frequencies. In detail, the three oscillator topologies have been implemented also for 1 and 100 GHz operations, by keeping the quality factor of 10 for the LC tank and preserving the same power consumption of 6.3~mW as in the case of the 10 GHz oscillation frequency. The transistor sizes were also kept the same as in the previous case. As a consequence of the results reported in the previous section, we injected noise current impulses with amplitude of 1  $\mu$ A.

Table 1.4 reports the values of the individual circuit components for the topologies of Fig. 1.1, used for the oscillation frequencies of 1 and 100 GHz.

Transistor Width [µm] Capacitor value [pF] Inductor value [pH] Frequency [GHz]  $M_1$  $M_2$  $M_3$  $M_4$  $C_1$  $C_2$  $C_3$  $C_4$  $C_5$  $L_1$ L 10  $10^{5}$ 5 2.5  $5 \times 10^{3}$  $2.5 \times 10^{3}$ 1 30 30 30 15 10 100 0.0515 0.023 30 30 15 0.1 0.0057 25

Table 1.4. Device Sizing for Oscillation Frequencies of 1 and 100 GHz.

Table 1.5 reports the phase noise values at a 1 MHz offset predicted by the ISF along with the values obtained by means of SpectreRF simulations for the oscillation frequencies of 1 and 100 GHz.

| PN [dBc/Hz] @ 1 MHz frequency offset |            |            |            |            |  |  |  |  |  |

|--------------------------------------|------------|------------|------------|------------|--|--|--|--|--|

| Topology                             | 16         | Hz         | 100 GHz    |            |  |  |  |  |  |

|                                      | Spectre RF | ISF (1 μA) | Spectre RF | ISF (1 μA) |  |  |  |  |  |

| Colpitts                             | -115.31    | -116       | -77.06     | -77.69     |  |  |  |  |  |

| Hartley                              | -114.52    | -114.85    | -81.18     | -81.38     |  |  |  |  |  |

| Cross-coupled                        | -123.7     | -124.06    | -74.78     | -75.59     |  |  |  |  |  |

Table 1.5. Summary of the PN Results Obtained by SpectreRF and ISF.

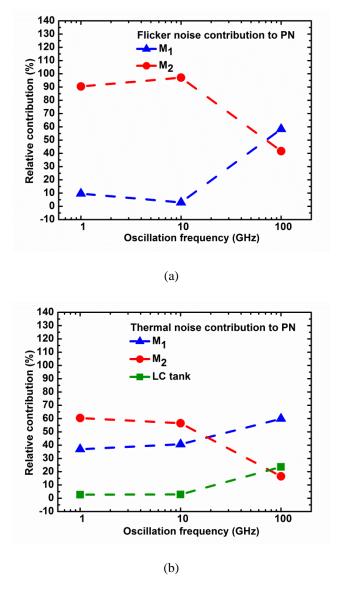

Fig. 1.6 reports the relative contributions of  $M_1$ ,  $M_2$  and LC tank to the overall phase noise versus the oscillation frequency for the Colpitts topology, in both the flicker and thermal noise contributions to phase noise.

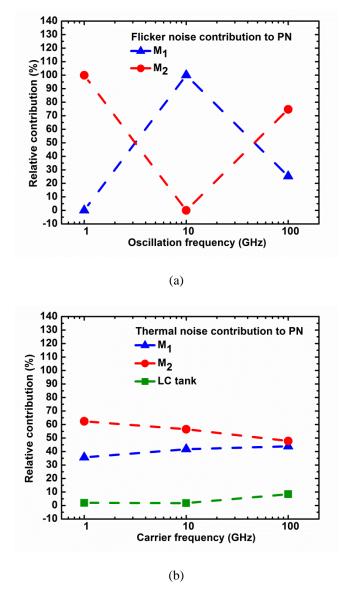

Figs. 1.7 and 1.8 report the results for the Hartley and common-source cross-coupled differential pair topologies, respectively.

Fig. 1.6. Relative contributions of  $M_1$ ,  $M_2$  and the LC tank for the Colpitts topology vs. oscillation frequency @ 1 MHz offset. (a) flicker noise contribution to PN. (b) thermal noise contribution to PN.

Fig. 1.7. Relative contributions of  $M_1$ ,  $M_2$  and the LC tank for the Hartley topology vs. oscillation frequency @ 1 MHz offset. (a) flicker noise contribution to PN. (b) thermal noise contribution to PN.

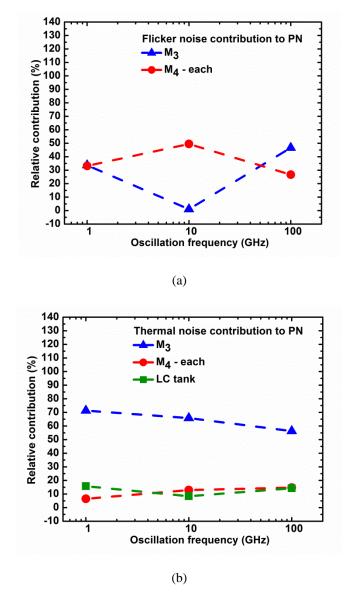

Fig. 1.8. Relative contributions of  $M_3$ ,  $M_4$  and the LC tank for the common-source cross-coupled differential pair topology vs. frequency of oscillation @ 1 MHz offset. (a) flicker noise contribution to PN. (b) thermal noise contribution to PN.

#### 1.4.1 Comparative Analysis between Devices

The relative contributions to the overall current flicker and thermal noise from MOSFETs and LC tank of the three oscillator topologies are summarized in Table 1.6, as well as the values of  $\Gamma_{DC}$  and  $\Gamma_{rms}$  calculated for the 1  $\mu$ A injected noise source.

|                  | C . 1 .: .          | C                   |                       |                       |                       |                      |                      |                      |

|------------------|---------------------|---------------------|-----------------------|-----------------------|-----------------------|----------------------|----------------------|----------------------|

|                  | Contribution to     | Contribution to     |                       | _                     |                       |                      | _                    |                      |

| Colpitts         | total flicker noise | total thermal noise |                       | $\Gamma_{ m DC}$      |                       |                      | $\Gamma_{ m rms}$    |                      |

|                  | (%)                 | (%)                 |                       |                       |                       |                      |                      |                      |

| Oscillation      |                     |                     | 1 CHa                 | 10 GHz                | 100 GHz               | 1 CHa                | 10 GHz               | 100CHz               |

| freq.            |                     |                     | 1 GHz                 | 10 GHZ                | 100 GHZ               | 1 GHz                | 10 GHZ               | 100GHz               |

| $M_1$            | 76.88               | 67.18               | 3.8×10 <sup>-8</sup>  | $-2.0\times10^{-8}$   | $5.4 \times 10^{-7}$  | 5.9×10 <sup>-7</sup> | 5.9×10 <sup>-7</sup> | 1.1×10 <sup>-6</sup> |

| $M_2$            | 23.1                | 32.27               | -2.0×10 <sup>-7</sup> | -2.0×10 <sup>-7</sup> | 9.9×10 <sup>-8</sup>  | 1.1×10 <sup>-6</sup> | 1.0×10 <sup>-6</sup> | 7.9×10 <sup>-7</sup> |

| LC tank          |                     | 0.55                |                       |                       |                       | 2.6×10 <sup>-6</sup> | 1.8×10 <sup>-6</sup> | 6.9×10 <sup>-6</sup> |

|                  | Contribution to     | Contribution to     |                       |                       |                       |                      |                      |                      |

| Hartley          | total flicker noise | total thermal noise |                       | $\Gamma_{ m DC}$      |                       |                      | $\Gamma_{ m rms}$    |                      |

|                  | (%)                 | (%)                 |                       | 20                    |                       |                      | 11115                |                      |

| Oscillation      |                     |                     | 1.011                 | 10.611                | 100 CH                | 1.011                | 10 CH                | 100011               |

| freq.            |                     |                     | 1 GHz                 | 10 GHz                | 100 GHz               | 1 GHz                | 10 GHz               | 100GHz               |

| $M_1$            | 76.88               | 67.18               | -4.3×10 <sup>-9</sup> | 1.9×10 <sup>-7</sup>  | 1.5×10 <sup>-7</sup>  | 6.1×10 <sup>-7</sup> | 7.0×10 <sup>-7</sup> | 5.4×10 <sup>-7</sup> |

| $M_2$            | 23.1                | 32.27               | -3.0×10 <sup>-7</sup> | -4.1×10 <sup>-9</sup> | -3.0×10 <sup>-7</sup> | 1.1×10 <sup>-6</sup> | 1.2×10 <sup>-6</sup> | 6.4×10 <sup>-7</sup> |

| LC tank          |                     | 0.55                |                       |                       |                       | 2.5×10 <sup>-6</sup> | 2.7×10 <sup>-6</sup> | 2.0×10 <sup>-6</sup> |

|                  | Contribution to     | Contribution to     |                       |                       |                       |                      |                      |                      |

| Cross-           | total flicker noise | total thermal noise |                       | $\Gamma_{ m DC}$      |                       |                      | $\Gamma_{ m rms}$    |                      |

| coupled          | (%)                 | (%)                 |                       | ЪС                    |                       |                      | IIIIS                |                      |

| Oscillation      |                     | , ,                 | 1 CH                  | 10 CH                 | 100 GH                | 1.011                | 10 CH                | 100 CH               |

| freq.            |                     |                     | 1 GHz                 | 10 GHz                | 100 GHz               | 1 GHz                | 10 GHz               | 100 GHz              |

| $\overline{M_3}$ | 20.60               | 26.47               | -3.3×10 <sup>-8</sup> | -1.5×10 <sup>-8</sup> | 3.3×10 <sup>-7</sup>  | 4.5×10 <sup>-7</sup> | 4.1×10 <sup>-7</sup> | 6.7×10 <sup>-7</sup> |

| $\overline{M_4}$ | 39.7 - each         | 30.70 - each        | 4.6×10 <sup>-8</sup>  | -1.5×10 <sup>-7</sup> | 2.0×10 <sup>-7</sup>  | 2.7×10 <sup>-7</sup> | 3.7×10 <sup>-7</sup> | 6.7×10 <sup>-7</sup> |

| LC tank          |                     | 12.13               |                       |                       |                       | 1.8×10 <sup>-6</sup> | 1.8×10 <sup>-6</sup> | 2.9×10 <sup>-6</sup> |

Table 1.6.  $\Gamma_{DC}$ ,  $\Gamma_{rms}$  and Relative Noise Contributions for a 1  $\mu$ A Injected Noise Source @ 1 MHz offset.

These results stimulate some careful evaluations about the noise contributions of each device in each oscillator topology at different oscillation frequencies.

To do this, we could refer again to equations (1.8), (1.9) and (1.14) and consider preliminarily that the amount of flicker or thermal noise of the transistor in a certain region of operation does not determine exclusively the flicker or thermal noise contribution to the oscillator phase noise, as reported in [18]. In particular, we can observe that for a given  $q_{max}$  (1.10) and a given frequency offset  $\Delta\omega=2\pi\times10^6$ , the amount of flicker noise contribution to phase noise is proportional to the product of the transistor flicker noise and  $\Gamma_{DC}^2$

$$\mathcal{Z}\{\Delta\omega\}\Big|_{flicker} \propto \sum_{i=1}^{m} \left\{ \Gamma_{DC}^{2} \left[ \left( \frac{\overline{i_{n}^{2}}}{\Delta f} \right) \frac{\omega_{1/f}}{\Delta\omega} \right] \right\}$$

(1.15)

whereas, the amount of thermal noise contribution to phase noise is proportional to the product of the thermal noise of the transistor and LC tank, and their respective  $\Gamma_{rms}^2$

$$\left. Z\{\Delta\omega\} \right|_{thermal} \propto \sum_{i=1}^{m+1} \left\{ \Gamma_{rms}^2 \left( \frac{\overline{i_n^2}}{\Delta f} \right) \right\}$$

(1.16)

In other words, the flicker noise is weighted by  $\Gamma_{DC}^2$  whereas the thermal noise is weighted by  $\Gamma_{rms}^2$ , as mentioned in [18]. On the other hand,  $\Gamma_{DC}$  and  $\Gamma_{rms}$  do not depend on the device noise sources, but on the node in which the noise current is injected in a circuit topology.

Considering these aspects it is worth highlighting the following observations on the above results.

In the Colpitts topology, we observe from Fig. 1.6 (a) and Table 1.6 that for oscillation frequencies higher than about 70 GHz, transistor  $M_1$  dominates the flicker noise contribution to PN. However,  $M_2$  dominates at frequencies lower than 70 GHz, despite  $M_2$  generates a lower flicker noise than  $M_1$ . This is due to the fact that, according to Table 1.6, the absolute value of  $\Gamma_{DC}$  for  $M_2$  is larger than  $\Gamma_{DC}$  for  $M_1$  at low frequencies of oscillation. In other terms, this means that the oscillation waveform at the node (drain node of  $M_2$ ) into which the noise current is injected is less symmetrical with respect to the rise and fall times [18]. Regarding the thermal noise contribution to phase noise, shown in Fig. 1.6 (b), at oscillation frequencies above 20 GHz,  $M_1$  has the major phase noise contribution. However, below 20 GHz,  $M_2$  has a higher  $\Gamma_{rms}$  than  $M_1$ , as shown in Table 1.6. As a result, despite according to Table 1.6 the thermal noise contribution of  $M_2$  is half that of  $M_1$ , it takes a larger portion of the thermal noise contribution to PN at oscillation frequencies below 20 GHz.

As for the Hartley oscillator topology, we observe from Fig. 1.7 (a) that at oscillation frequencies between 3 and 50 GHz, transistor  $M_1$  dominates the flicker noise contribution to phase noise. Nonetheless, in lower and higher oscillation frequencies,  $M_2$  dominates, despite its lower flicker noise with respect to  $M_1$  as shown in Table 1.6, since its contribution is characterized by a higher absolute value of  $\Gamma_{DC}$ , as again shown in Table 1.6. In the thermal noise contribution to phase noise reported in Fig. 1.7 (b),  $M_2$  presents the major contribution, because, from Table 1.6  $M_2$  has a higher  $\Gamma_{rms}$  than  $M_1$ . As a result, despite according to Table 1.6 the thermal noise contribution of  $M_2$  is half that of  $M_1$ , it takes a larger portion of the thermal noise contribution to phase noise.

As for the common-source cross-coupled differential pair oscillator topology, we see in Fig. 1.8 (a), that the pair of n-MOSFETs  $M_4$ , at frequencies lower than 50 GHz, is responsible for most of the flicker noise contribution to phase noise, as not only generates more flicker noise, but also has a higher absolute value of  $\Gamma_{DC}$  than  $M_3$  (see Table 1.6). After 50 GHz, the contribution of  $M_3$  increases due to its higher  $\Gamma_{DC}$  value and surpasses that of  $M_4$ , even though  $M_4$  generates a higher flicker noise. With respect to the behavior of the thermal noise contribution to phase noise seen in Fig. 1.8 (b), the relative contribution from the current source  $M_3$  gradually drops with increasing oscillation frequencies, whereas  $M_4$  follows an opposite trend.

Moreover, from Figs. 1.6 (b) and 1.7 (b), we note that in the Colpitts and Hartley topologies, the LC tank occupies at lower oscillation frequencies a small portion of the contribution of thermal noise to phase noise graph, because, as Table 1.6 indicates, the thermal noise generated

by the LC tank is at least one order of magnitude below the thermal noise generated by the transistors in each case. However, both in Colpitts and Hartley, the contribution of the LC tank increases at higher oscillation frequencies where Table 1.6 indicates that  $\Gamma_{rms}$  of the tank is notably larger than  $\Gamma_{rms}$  of both devices.

On the other hand, from Figs. 1.6 (b), 1.7 (b) and 1.8 (b) we note that in all three oscillator topologies, the relative contribution of the current sources  $M_2$  and  $M_3$  to the thermal noise contribution to phase noise drops at higher oscillation frequencies. According to Table 1.6, this is due to the reduction of the  $\Gamma_{rms}$  for the current sources relative to the  $\Gamma_{rms}$  values for the other oscillator components.

#### 1.4.2 Comparative Analysis between Topologies

1.0×10<sup>-32</sup>

Total  $(\Sigma)$

By using the values in Table 1.6 along with the equations (1.15) and (1.16), we can determine the flicker and thermal noise contributions obtained by the ISF for a 1  $\mu$ A injected current source, as reported in Table 1.7.

| Colpitts          |                       | $\Gamma_{DC}^{2} \left[ \left( \frac{\overline{i_{n}^{2}}}{\Delta f} \right) \frac{\omega_{1/f}}{\Delta \omega} \right]$ |                       |                       | $\Gamma_{ms}^{2} \left( \frac{\overline{i_{n}^{2}}}{\Delta f} \right)$  |                       |

|-------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-------------------------------------------------------------------------|-----------------------|

| Oscillation freq. | 1 GHz                 | 10 GHz                                                                                                                   | 100 GHz               | 1 GHz                 | 10 GHz                                                                  | 100 GHz               |

| $M_1$             | 6.8×10 <sup>-33</sup> | 2.0×10 <sup>-33</sup>                                                                                                    | 4.2×10 <sup>-32</sup> | 2.2×10 <sup>-33</sup> | 2.3×10 <sup>-33</sup>                                                   | 3.3×10 <sup>-33</sup> |

| $M_2$             | 6.4×10 <sup>-32</sup> | 6.7×10 <sup>-32</sup>                                                                                                    | 3.0×10 <sup>-32</sup> | 3.6×10 <sup>-33</sup> | 3.2×10 <sup>-33</sup>                                                   | 9.1×10 <sup>-34</sup> |

| LC tank           |                       |                                                                                                                          |                       | 1.6×10 <sup>-34</sup> | 1.6×10 <sup>-34</sup>                                                   | 1.3×10 <sup>-33</sup> |

| Total $(\Sigma)$  | 7.1×10 <sup>-32</sup> | 6.9×10 <sup>-32</sup>                                                                                                    | 7.2×10 <sup>-32</sup> | 6.0×10 <sup>-33</sup> | 5.6×10 <sup>-33</sup>                                                   | 5.5×10 <sup>-33</sup> |

| Hartley           | ]                     | $\Gamma_{DC}^{2} \left[ \left( \frac{\overline{i_{n}^{2}}}{\Delta f} \right) \frac{\omega_{1/f}}{\Delta \alpha} \right]$ | 5                     |                       | $\Gamma_{rms}^{2} \left( \frac{\overline{i_{n}^{2}}}{\Delta f} \right)$ |                       |

| Oscillation freq. | 1 GHz                 | 10 GHz                                                                                                                   | 100 GHz               | 1 GHz                 | 10 GHz                                                                  | 100 GHz               |

| $M_1$             | 6.2×10 <sup>-35</sup> | 1.7×10 <sup>-31</sup>                                                                                                    | 4.4×10 <sup>-33</sup> | 2.4×10 <sup>-33</sup> | 3.1×10 <sup>-33</sup>                                                   | 1.1×10 <sup>-33</sup> |

| $M_2$             | 9.8×10 <sup>-32</sup> | 2.7×10 <sup>-35</sup>                                                                                                    | 1.3×10 <sup>-32</sup> | 4.2×10 <sup>-33</sup> | 4.2×10 <sup>-33</sup>                                                   | 1.2×10 <sup>-33</sup> |

| LC tank           |                       |                                                                                                                          |                       | 1.3×10 <sup>-34</sup> | 1.3×10 <sup>-34</sup>                                                   | $2.1 \times 10^{-34}$ |

| Total $(\Sigma)$  | 9.8×10 <sup>-32</sup> | 1.7×10 <sup>-31</sup>                                                                                                    | 1.8×10 <sup>-32</sup> | 6.8×10 <sup>-33</sup> | 7.4×10 <sup>-33</sup>                                                   | 2.5×10 <sup>-33</sup> |

| Cross-coupled     | ]                     | $\Gamma_{DC}^{2} \left[ \left( \frac{\overline{i_{n}^{2}}}{\Delta f} \right) \frac{\omega_{1/f}}{\Delta \alpha} \right]$ |                       |                       | $\Gamma_{rms}^{2} \left( \frac{\overline{i_{n}^{2}}}{\Delta f} \right)$ |                       |

| Oscillation freq. | 1 GHz                 | 10 GHz                                                                                                                   | 100 GHz               | 1 GHz                 | 10 GHz                                                                  | 100 GHz               |

| $M_3$             | $3.4 \times 10^{-33}$ | 1.3×10 <sup>-34</sup>                                                                                                    | 4.2×10 <sup>-32</sup> | 7.7×10 <sup>-34</sup> | 5.1×10 <sup>-34</sup>                                                   | 1.7×10 <sup>-33</sup> |

| $M_4$             | 6.7×10 <sup>-33</sup> | 1.3×10 <sup>-32</sup>                                                                                                    | 4.8×10 <sup>-32</sup> | 1.4×10 <sup>-34</sup> | 2.0×10 <sup>-34</sup>                                                   | 8.9×10 <sup>-34</sup> |

| LC tank           |                       |                                                                                                                          |                       | 1.7×10 <sup>-34</sup> | 6.5×10 <sup>-35</sup>                                                   | 4.3×10 <sup>-34</sup> |

Table 1.7. Noise Contributions @ 1 MHz Frequency Offset for a 1 μA Injected Noise Current.

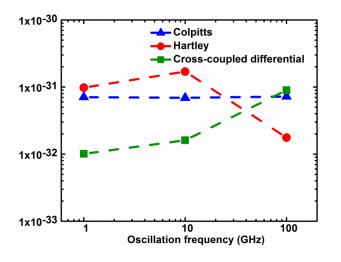

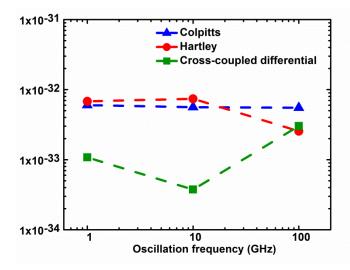

In order to provide them in a more intuitive form, the results in Table 1.7 are plotted in Figs. 1.9 and 1.10.

As in the previous subsection, by considering a given  $q_{max}$  (1.10) and a given frequency offset  $\Delta\omega=2\pi\times10^6$ , equations (1.15) and (1.16) can be used in order to compare the flicker and

thermal noise contributions respectively, to the phase noise of various oscillator topologies. In this perspective, Figs. 1.9 and 1.10 show the variation of the flicker and thermal noise contributions to phase noise respectively, for the three oscillator topologies under investigation with respect to changes in the oscillation frequency, at a frequency offset of 1 MHz.

Fig. 1.9. Sum of  $\Gamma_{DC}^2 \left[ \left( \frac{\overline{i_n^2}}{\Delta f} \right) \frac{\omega_{l/f}}{\Delta \omega} \right]$  for all flicker noise sources in each oscillator topology @ 1 MHz offset vs. oscillation frequency for Colpitts, Hartley and common-source cross-coupled differential pair topologies.

Fig. 1.10. Sum of  $\Gamma_{mns}^2 \left( \frac{i_n^2}{\Delta f} \right)$  for all thermal noise sources in each oscillator topology @ 1 MHz offset vs. oscillation frequency for Colpitts, Hartley and common-source cross-coupled differential pair topologies.

#### 1.5 Topology Performances versus Oscillation Frequency Regions

In the previous section we reported the results of the effective ISF for every active device of the three oscillator topologies according to equations (1.12) and (1.13). Here we try to explain the different phase noise behavior achieved for the three oscillator topologies over the frequency range from 1 to 100 GHz. The results of the previous section suggest considering additional oscillation frequencies. For this reason, the three topologies have been designed also for the additional oscillation frequencies of 30, 50 and 70 GHz, according to the same criteria of Sections 1.2 and 1.4.

Table 1.8 reports the values of the circuit components for each topology for the oscillation frequencies of 30, 50 and 70 GHz.

|                 | Transistor Width [μm] |       |       |       | Capacitor value [pF] |                 |                |       | Inductor value [pH] |       |       |

|-----------------|-----------------------|-------|-------|-------|----------------------|-----------------|----------------|-------|---------------------|-------|-------|

| frequency [GHz] | $M_1$                 | $M_2$ | $M_3$ | $M_4$ | $C_1$                | $C_2$           | C <sub>3</sub> | $C_4$ | $C_5$               | $L_1$ | $L_2$ |

| 30              | 30                    | 30    | 30    | 15    | 0.286                | $10^{5}$        | 0.1385         | 0.4   | 0.0627              | 166.7 | 83.35 |

| 50              | 30                    | 30    | 30    | 15    | 0.15                 | $10^{5}$        | 0.071          | 0.25  | 0.0297              | 100   | 50    |

| 70              | 30                    | 30    | 30    | 15    | 0.0928               | 10 <sup>5</sup> | 0.0439         | 0.15  | 0.0158              | 71.4  | 35.7  |

Table 1.8. Device sizing for oscillation frequencies of 30, 50 and 70 GHz.

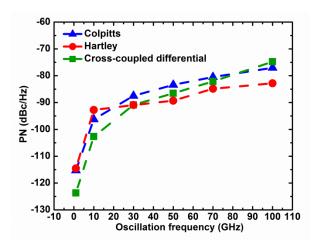

Fig. 1.11 reports the phase noise results obtained by SpectreRF for 1, 10, 30, 50, 70 and 100 GHz at a 1 MHz frequency offset from the carrier.

Fig. 1.11. PN at a 1 MHz frequency offset from carrier vs. oscillation frequency for Colpitts, Hartley and common-source cross-coupled differential pair topologies by SpectreRF.

These results allow us to identify the following four main frequency regions: 1-20, 20-30, 30-80 and 80-100 GHz. They offer the opportunity to carry out further comparative analyses and derive a number of observations.

Comparing the total (i.e. sum) contributions of the flicker and thermal noise sources in Table 1.7 and Figs. 1.9 and 1.10, we can note that the flicker noise contribution dominates at the frequency offset of 1 MHz at the oscillation frequencies of 1, 10 and 100 GHz. We can also note

that the term (1.15) determining the flicker noise contribution derived from ISF, as in Fig. 1.9, shows an agreement with the phase noise derived by SpectreRF-Cadence, as in Fig. 1.11.

This is because, as already mentioned in Section 1.4, from equations (1.8), (1.9) and (1.14), it can be concluded that the flicker noise contribution to phase noise is defined by the product of the transistor flicker noise with  $\Gamma_{DC}^2$ , as expressed in (1.15) and quantified in Table 1.7.

**Region 1 (1-20 GHz):** According to Fig. 1.11, the common-source cross-coupled differential pair topology exhibits the lowest phase noise with respect to the other two topologies. The highest phase noise is exhibited by the Hartley topology. This is in agreement with the trend reported in Fig. 1.9. Delving into the separate noise sources as addressed in Section 1.4 and shown in Figs. 1.6 (a), 1.7 (a) and 1.8 (a), the nodes mostly prone to the current noise injection are: the drain of  $M_2$  in the Colpitts topology; the drain of  $M_2$  from 1 to 3 GHz and the drain of  $M_1$  from 3 to 20 GHz in the Hartley topology; and the drain of both  $M_3$  and  $M_4$  in the common-source cross-coupled differential pair topology.

**Region 2 (20-30 GHz):** In this region, we note from Fig. 1.11 that the common-source cross-coupled differential pair topology still maintains the best phase noise performance, but unlike the above case, we can observe an inversion between the Hartley and Colpitts topologies. The latter exhibits the worst phase noise at 30 GHz. Fig. 1.9 follows approximately the same results. From Figs. 1.6 (a), 1.7 (a) and 1.8 (a) we can see that the nodes mostly sensitive to noise injections are: the drain of  $M_2$  in the Colpitts topology; the drain of  $M_1$  in the Hartley topology; and the drain of  $M_4$  in the common-source cross-coupled differential pair topology.

**Region 3 (30-80 GHz):** In Fig. 1.11, we register an inversion for the best phase noise performance, given now by the Hartley topology, whereas the Colpitts topology still exhibits the worst phase noise as in the previous case. A similar behavior is exhibited in Fig. 1.9. In this region the nodes mostly sensitive to noise injection according to Figs. 1.6 (a), 1.7 (a) and 1.8 (a) are: the drain of  $M_2$  in the Colpitts topology; the drain of  $M_1$  up to 50 GHz and the drain of  $M_2$  at higher frequencies in the Hartley topology; the drain of both  $M_3$  and  $M_4$  until 50 GHz and of  $M_3$  above 50 GHz in the common-source cross-coupled differential pair topology.

**Region 4 (80-100 GHz):** Fig. 1.11 indicates that Hartley continues to exhibiting the lowest phase noise. However, with respect to the previous case, here we can observe an inversion of performance between the Colpitts topology and the common-source cross-coupled differential pair topology, which now exhibits the highest phase noise. We can also derive the same conclusions from Fig. 1.9. The operation in the triode region for some part of the oscillation period is the main reason for this noise performance degradation at the highest frequencies in the common-source cross-coupled differential pair topology according to the notes in [25]. Indeed, our design operates in the voltage-limited regime, thus causing the active devices to enter in the triode region at the peaks of the differential output node voltage. We notice from Figs. 1.6 (a), 1.7 (a) and 1.8 (a) that the most sensitive nodes in this frequency range are: the drain of  $M_1$  in the

Colpitts topology; the drain of  $M_2$  in the Hartley topology; the drain of  $M_3$  in the common-source cross-coupled differential pair topology.

At least up to a 1 MHz frequency offset from the carrier, the flicker noise contribution is dominant according to Figs. 1.5 (a) - (c) and Table 1.7. Therefore, the proportional increase of the flicker noise contribution to phase noise due to  $M_3$  at the highest oscillation frequencies in the common-source cross-coupled differential pair topology, as observed in Table 1.6 and Fig. 1.8 (a), is the main cause of the overall phase noise increase. Actually, this is an effect of the losses through the p-MOSFET tail current source that become part of the tank circuit, thus impairing its Q [26, 27]. Note that the superior phase noise performance of the Hartley topology at high frequencies noted in Regions 3 and 4 is in agreement with the observations in [25, 28].

#### 1.6 Conclusions

Phase noise comparative analyses have been carried out for Colpitts, Hartley and common-source cross-coupled differential pair LC oscillator topologies in the frequency range from 1 to 100 GHz. The circuit topologies have been implemented in 28 nm bulk CMOS technology for operation at 1, 10, 30, 50, 70 and 100 GHz, maintaining equal power consumption, quality factor and transistor sizes for a fair comparison among all the circuit topologies. All the steps and settings for accurate evaluations of the impulse sensitivity function have been discussed and clarified in depth. Phase noise performances have also been evaluated directly through periodic steady-state simulations in the SpectreRF-Cadence environment. These last results have been compared with the results obtained through the ISF for a wide set of amplitudes of injected current pulses. The phase noise predicted by the ISF is in a good agreement with the results obtained by SpectreRF under the given simulation settings, especially for the pulse amplitude of 1  $\mu$ A.

Moreover, the investigations on the phase noise contributions from each component of the investigated oscillator circuit topologies have been reported and discussed in detail. The results show that, under the adopted design conditions, the three oscillator topologies rank unevenly in terms of the best phase noise performance rating scale for oscillation frequencies from 1 to 100 GHz. This comes as a result of the frequency dependence of both contributions from each circuit component and the sensitivity to noise injections in the circuit nodes. Recent studies refer to the common-source cross-coupled differential pair topology as the one with the best phase noise as a consequence of the circuit designs carried out at lower frequencies. Our comparative analyses reported here show that there is no superior topology in the absolute sense, but that the identification of the best circuit topology with respect to phase noise is strictly related to the operating frequency range. Nowadays, the most popular topology used is the common-source cross-coupled differential mainly due to its reliable start-up. However, the results presented here, suggest the opportunity to invest additional studies and efforts in exploring the circuit design implementations also of other topologies, whose potential may have been perhaps underestimated up to date, especially at very high frequencies for which, thanks to the recent

advances in the nano-scale technology process, MOSFETs with cut-off and max frequencies in excess of 280 and 350 GHz [29], respectively, are available nowadays for a potential use in a number of emerging wireless applications in the millimeter-wave frequency range.

# Chapter 2

# Colpitts, Hartley, Common-Source Cross-Coupled and Armstrong Differential topologies

### 2.1 Introduction

Advances in wireless communications have a great impact on our societal and economic challenges [30-34]. One of the most critical circuits of modern radiofrequency transceivers is the local oscillator, i.e. an autonomous circuit operating as the "pulsing heart" of such systems, in an analogy with the human body. As any other solid-state circuits, oscillators are affected by the inherent noise of the electronic devices. One of the major negative effects of noise in oscillators is given by the induced variations on the instantaneous oscillation frequency, leading to the degradation of the spectral purity of the output voltage, referred as phase noise (PN) [5, 8]. Oscillator phase noise performance directly affects the bit-error rate (BER) of the overall communication system [2].

Understanding the generation mechanisms of phase noise has been a very intriguing challenge and consequently most of the efforts have been made in this direction for a number of circuit topologies [35]. However, no complete comparative studies have been carried out on how to choose the oscillator circuit topology that could potentially offer the best performance in terms of phase noise for the range of operating frequencies of modern telecommunication systems. Usually, thanks to its reliable start-up, the common-source cross-coupled differential pair topology is chosen a priori without any further considerations. Thereby, from a designer perspective, such a comparative analysis could be very helpful in focusing the design efforts toward specific directions.

On the basis of the above motivations, in Chapter 1 and in our recent works [OP1, OP6] we dealt with this open question not addressed by the literature. In particular, we carried out a comparative analysis of phase noise of the common-source cross-coupled differential pair topology with Colpitts and Hartley single-ended topologies in 28 nm bulk CMOS technology for oscillation frequencies ranging from 1 to 100 GHz. In that study we made use of the impulse sensitivity function (ISF),  $\Gamma(x)$  [36], which allowed us to quantify the noise contributions to the overall phase noise for each device in each oscillator circuit topology and identify the dominant noise sources and their impact versus the operating frequency [OP1]. Interestingly, the results showed that there is not a superior topology in the absolute sense, but that the identification of the best circuit topology is related to the operating frequency range. In particular, the Hartley topology exhibited the best performance at higher frequency [OP1].

Despite these results provide a first interesting perspective, this is limited by the comparison between a differential topology, i.e. cross-coupled common-source differential pair, and two single-ended topologies, Colpitts and Hartley. In fact, assuming a perfect symmetry, common-

mode noise sources (e.g. noise coming from the common bias circuitry) do not produce effects in a differential topology; thereby, in principle, this aspect may play a significant role in determining the phase noise performance, then leading to a less effective comparison. Moreover, despite Colpitts and Hartley single-ended topologies have long been used in discrete circuit design, the advances in silicon integration have led to the implementation of differential versions as well [37], which have shown the potential for superior performance, typically at the expenses of larger area occupancy on silicon.

Consequently, extending the comparative analyses of phase noise carried out in Chapter 1 and therein [OP1, OP6] to the Colpitts and Hartley differential topologies is in order for a comparison under common conditions. Moreover, on the basis of the advances in integration and intrigued by the interesting results revealed by our previous analyses reported in Chapter 1 and therein [OP1, OP6], it would be useful to extend the study to other oscillator topologies which may deserve our attention, such as the Armstrong topology. A recent implementation of this circuit topology shows potential for very low power operation, while achieving high spectral purity [38]. This solution exploits integrated transformers [6, 39] in order to implement magnetic coupling between gate and drain terminals, as well as source and drain terminals of the transistor pair in the oscillator.

Driven by the above motivations, in this chapter we report a comparative investigation of phase noise in the common-source cross-coupled pair, Colpitts, Hartley and Armstrong differential oscillator topologies, with the main objective of bringing to the light the contributions of the inherent noise sources in the most widespread oscillator topologies reported in the literature. This comparative analysis extends and complements the previous analysis reported in Chapter 1 and therein [OP1, OP6], which was limited to Colpitts and Hartley singleended topologies and common-source cross-coupled differential pair. Here, the comparative analysis is extended to differential topologies for a fair comparison with the common-source cross-coupled differential pair and extended also to the Armstrong topology (in addition to Colpitts and Hartley). The oscillator circuit topologies are investigated under the common design conditions, such as (a) power consumption, (b) supply voltage, (c) transistor current density and (d) sizing (area, aspect ratio, finger width), (e) inductance and (f) quality factor of the integrated spiral inductors, (g) coupling factor of the integrated transformers, and (h) considering the full models of the transistors available within the process design kit, including all their parasitic components related to their actual size, but excluding the layout interconnections, since the additional parasitic components introduced by the layout implementation could mask the results of the topological investigations which are the objective of our study. The common conditions adopted in this comparative analysis are the same as those adopted for the comparative analysis between Colpitts and Hartley single-ended topologies and common-source cross-coupled differential pair reported in Chapter 1 and published therein [OP1, OP6], thereby they represent the natural sequel from the previous results, which assures the continuity with them. As in the previous work [OP1, OP6], the ISF is used to quantify the impact of each noise source on the overall phase noise in each oscillator circuit topology, allowing the identification of the major contributions to the phase noise degradation versus the oscillation frequency. The results could drive the designer through the choice of the oscillator circuit topology that could potentially offer the best phase noise.

The chapter is organized as follows. Section 2.2 describes the oscillator circuit topologies and their common design conditions. Section 2.3 reports the comparative analyses of phase noise. Section 2.4 reports the investigation on the contributions of each noise source to the overall phase noise. Finally, in Section 2.5 the conclusions are drawn.

The key contents of this chapter have been reported in original contributions published in an international peer-reviewed journal and in conference proceedings [OP2, OP7, OP8].

## 2.2 Circuit Topologies

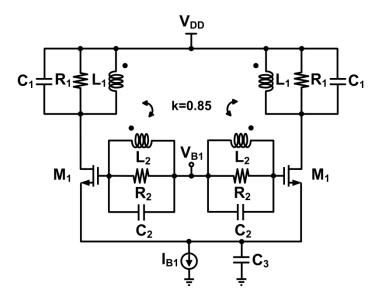

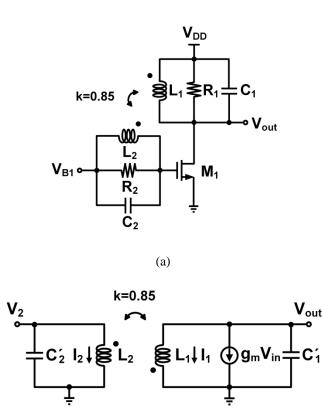

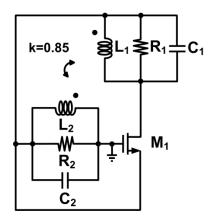

Fig. 2.1 shows the oscillator circuit topologies designed in 28 nm bulk CMOS technology, operating from a 1 V supply voltage. All the circuit topologies operate in the voltage-limited regime. The same figure shows the current impulsive sources acting in parallel to the inherent current noise sources and used for the evaluation of the ISF. Based on the findings reported in Chapter 1 and therein [OP1, OP6], transient simulations were performed for an injected current amplitude of 1 μA. The workload for the circuit simulations was significantly reduced by using OCEAN scripts [21].

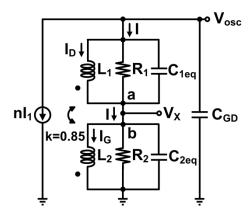

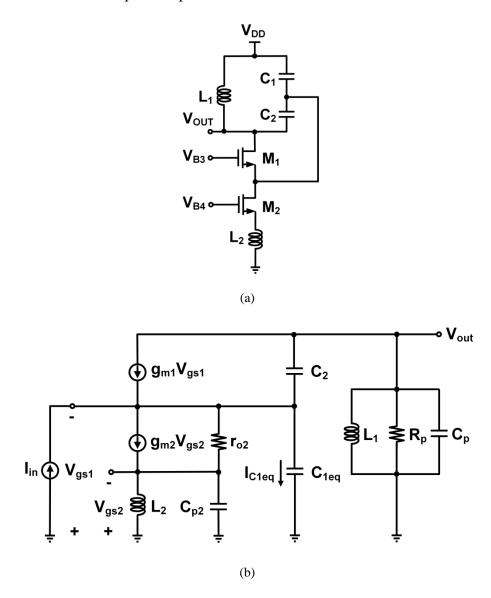

The sizes of the active and passive devices are reported in Table 2.1. Capacitors are considered ideal, whereas a quality factor (Q) of 10 is assumed for the spiral inductors, i.e. a feasible value for the oscillation frequencies in the range of interest from 1 to 100 GHz [7, 40]. A coupling factor k of 0.85 is assumed for the transformers [37]. For all the investigated differential circuit topologies the total power consumption is 6.3 mW, as in Chapter 1 and therein [OP1, OP6].

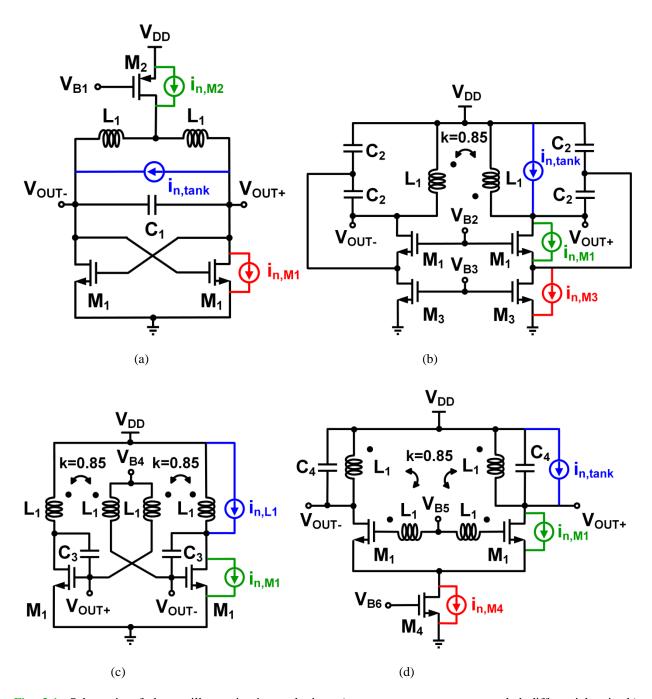

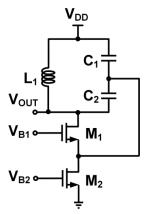

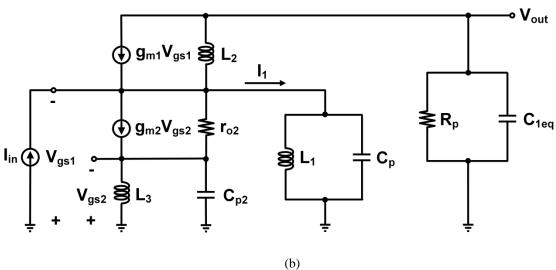

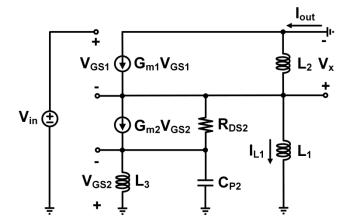

In particular, the comparative analysis takes into account the common-source cross-coupled differential pair, Colpitts, Hartley and Armstrong differential circuit topologies shown in Figs. 2.1 (a)-(d), which have shown the best phase noise performances with respect to other design variations. Thereby, these topologies allow an effective comparison based on the actual needs and opportunities, rather than a comparison between basic topologies and their variations which are known from the literature to provide worse phase noise performance with respect to those considered in this comparative analysis. In other words, the investigated topologies are the most promising in their category. The common-source cross-coupled pair in Fig. 2.1 (a) provides the negative resistance needed for the oscillation start-up. A p-MOSFET is chosen as a current source since it exhibits lower flicker noise. The transformer coupling in the Colpitts topology of Fig. 2.1 (b) contributes to the suppression of common-mode oscillations [22]. Moreover, for lower phase noise, two separate tail current transistors are used for biasing, as in [41]. As for the Hartley topology in Fig. 2.1 (c), the transformer coupling is used in order to reduce the area

occupied by the inductors [42]. Finally, in the Armstrong topology of Fig. 2.1 (d), the transformer coupling between gate and drain is considered for the same reasons. Also, in the latter topology, the inductor of the LC tank is given by the overall equivalent inductance offered by the self-inductance of the spiral inductors of the transformer and the mutual inductance between the two spirals on the gate and drain terminals of  $M_1$ .

Fig. 2.1. Schematic of the oscillator circuit topologies: a) common-source cross-coupled differential pair; b) differential Colpitts; c) differential Hartley; d) differential Armstrong.  $V_{B1}$ ,  $V_{B2}$ ,  $V_{B3}$ ,  $V_{B4}$ ,  $V_{B5}$ , and  $V_{B6}$  are DC bias voltages.

Table 2.1. Device Sizing

| Osc.<br>freq. | Transistor Width<br>[μm] |       |       |       | Capacitor value [fF] |       |       |       | Inductor<br>value [pH] |

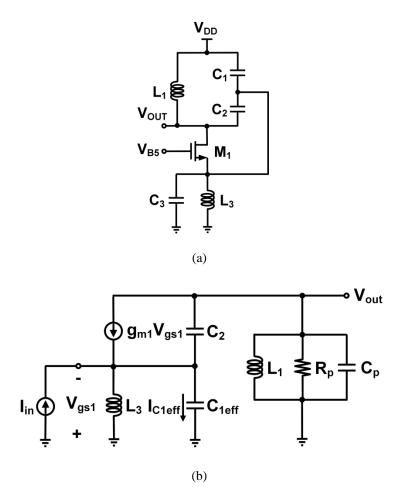

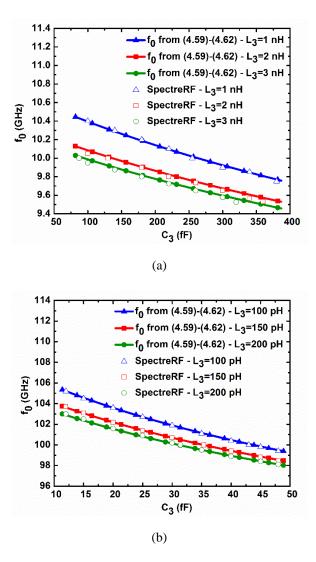

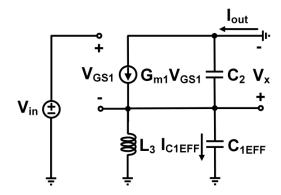

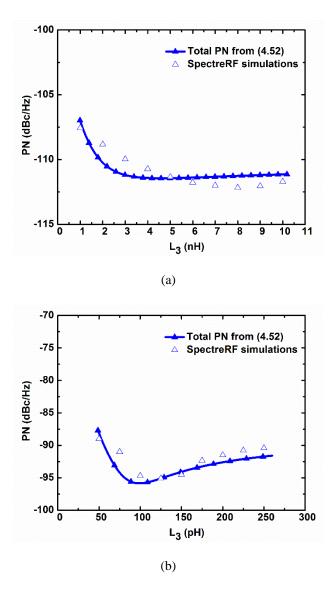

|---------------|--------------------------|-------|-------|-------|----------------------|-------|-------|-------|------------------------|