## UNIVERSITY COLLEGE CORK

College of Science, Engineering and Food Science

TYNDALL NATIONAL INSTITUTE

## Heterogeneous integration of InP etched facet lasers to silicon photonics by micro transfer printing

Thesis presented by: **Ruggero Loi**

FOR THE DEGREE OF: Doctor of Philosophy

*Supervisor:* Brian Corbett *Co-Supervisor:* Brendan Roycroft

## Contents

| A | Aknowledgements v |                                                                |                                                            |    |  |  |  |  |  |

|---|-------------------|----------------------------------------------------------------|------------------------------------------------------------|----|--|--|--|--|--|

| A | Abstract          |                                                                |                                                            |    |  |  |  |  |  |

| 1 | Introduction      |                                                                |                                                            |    |  |  |  |  |  |

|   | 1.1               | Data d                                                         | centres and the internet of the future                     | 5  |  |  |  |  |  |

|   | 1.2               | Photo                                                          | nic integrated circuits for telecom and datacom            | 7  |  |  |  |  |  |

|   |                   | 1.2.1                                                          | Packaging of PICs                                          | 9  |  |  |  |  |  |

|   | 1.3               | Silicon                                                        | n photonics integrated circuits                            | 10 |  |  |  |  |  |

|   | 1.4               | III-V r                                                        | materials and silicon photonics                            | 12 |  |  |  |  |  |

|   | 1.5               | Thesis                                                         | s structure                                                | 15 |  |  |  |  |  |

| 2 | III-V             | V lasers                                                       | s for Si photonics and integration                         | 21 |  |  |  |  |  |

|   | 2.1               | III-V I                                                        | Laser sources for silicon photonics                        | 21 |  |  |  |  |  |

|   |                   | 2.1.1                                                          | Light coupling between waveguides                          | 22 |  |  |  |  |  |

|   |                   |                                                                | Light coupling through gratings                            | 23 |  |  |  |  |  |

|   |                   |                                                                | Light evanescent-coupling                                  | 24 |  |  |  |  |  |

|   |                   |                                                                | Light edge-coupling                                        | 25 |  |  |  |  |  |

|   |                   | 2.1.2                                                          | External laser source                                      | 26 |  |  |  |  |  |

|   |                   | 2.1.3                                                          | Monolithically grown III-V laser on silicon photonics .    | 27 |  |  |  |  |  |

|   |                   | 2.1.4                                                          | Heterogeneously integrated laser                           | 28 |  |  |  |  |  |

|   |                   |                                                                | Evanescent lasers                                          | 29 |  |  |  |  |  |

|   |                   |                                                                | Edge-coupled laser                                         | 31 |  |  |  |  |  |

|   |                   |                                                                | Other heterogeneous lasers                                 | 33 |  |  |  |  |  |

|   | 2.2               | Techn                                                          | ologies for heterogeneous integration of III-V to SOI $$ . | 33 |  |  |  |  |  |

|   |                   | 2.2.1                                                          | Wafer and die to wafer bonding                             | 33 |  |  |  |  |  |

|   |                   | 2.2.2                                                          | Micro Transfer Printing                                    | 35 |  |  |  |  |  |

|   | 2.3               | Choice of the strategy for the heterogenous integration of InP |                                                            |    |  |  |  |  |  |

|   |                   | etcheo                                                         | l facet lasers to the SOI                                  | 38 |  |  |  |  |  |

|   | 2.4               | Concl                                                          | usion                                                      | 41 |  |  |  |  |  |

| 3 | Transfer printing of InP lasers                     |        |                                                                             | 51  |  |

|---|-----------------------------------------------------|--------|-----------------------------------------------------------------------------|-----|--|

|   | 3.1                                                 | Transf | fer printable InP Lasers                                                    | 51  |  |

|   |                                                     | 3.1.1  | Epitaxial structure                                                         | 54  |  |

|   | 3.2                                                 | Desig  | n and fabrication of the lasers                                             | 55  |  |

|   |                                                     | 3.2.1  | Laser fabrication process                                                   | 57  |  |

|   |                                                     | 3.2.2  | Different geometries of the devices                                         | 58  |  |

|   |                                                     | 3.2.3  | Stress management                                                           | 60  |  |

|   |                                                     | 3.2.4  | Etched facets                                                               | 61  |  |

|   |                                                     |        | Multi mode interferometer back reflector (MIR)                              | 65  |  |

|   |                                                     | 3.2.5  | Anchor system                                                               | 67  |  |

|   | 3.3                                                 | InGaA  | As and InAlAs release technologies                                          | 71  |  |

|   |                                                     | 3.3.1  | InGaAs/InP release structure                                                | 72  |  |

|   |                                                     | 3.3.2  | InAlAs/InP - InGaAs/InP comparison                                          | 74  |  |

|   | 3.4                                                 | Transf | fer printing of the lasers                                                  | 80  |  |

|   |                                                     | 3.4.1  | Adhesive-less printing                                                      | 82  |  |

|   |                                                     | 3.4.2  | Print with adhesives                                                        | 85  |  |

|   |                                                     | 3.4.3  | Post printing treatments                                                    | 88  |  |

|   |                                                     |        | Anchors removal by acetone gas-vapour                                       | 89  |  |

|   |                                                     |        | Adhesion enhancement                                                        | 91  |  |

|   | 3.5                                                 | Concl  | usion                                                                       | 91  |  |

| 4 | Characterization of the transfer printable lasers 9 |        |                                                                             |     |  |

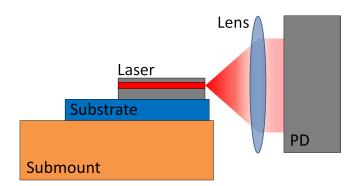

|   | 4.1                                                 | Meası  | arement setup                                                               | 97  |  |

|   | 4.2                                                 | Laser  | characterization                                                            | 100 |  |

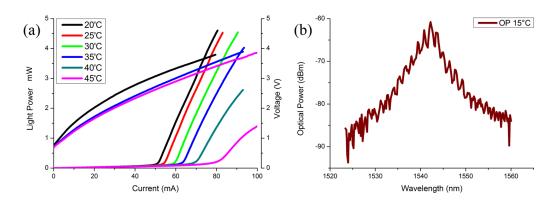

|   |                                                     | 4.2.1  | Initial run of fabricated lasers                                            | 102 |  |

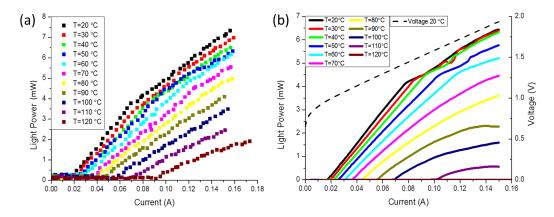

|   |                                                     | 4.2.2  | Final run of fabricated lasers                                              | 104 |  |

|   | 4.3                                                 | Therm  | nal characterization                                                        | 106 |  |

|   |                                                     | 4.3.1  | Simulated heat transfer                                                     | 108 |  |

|   | 4.4                                                 | Influe | nce of $\mu$ TP on the devices $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 115 |  |

|   | 4.5                                                 | Concl  | usion                                                                       | 116 |  |

| 5 | Laser to waveguide light edge-coupling              |        |                                                                             |     |  |

|   | 5.1                                                 | Desig  | n of the Light edge-coupling                                                | 120 |  |

|   | 5.2                                                 | Integr | ation strategies                                                            | 123 |  |

|   |                                                     | 5.2.1  | Formation of recesses in the SOI                                            | 123 |  |

|   | 5.3                                                 | Edge-  | coupling of InP lasers to polymer waveguides on sili-                       |     |  |

|   |                                                     | con pł | notonics                                                                    | 129 |  |

|   |                                                     | 5.3.1  | Laser devices                                                               | 131 |  |

|   |                                                     | 5.3.2  | Recesses on the SOI                                                         | 132 |  |

|   |                                                           | 5.3.3                    | $\mu$ TP of the lasers to the SOI      | 132               |  |

|---|-----------------------------------------------------------|--------------------------|----------------------------------------|-------------------|--|

|   |                                                           | 5.3.4                    | Edge-coupling to the polymer waveguide | 133               |  |

|   | 5.4 Characterization of the lasers integrated             |                          |                                        | 135               |  |

|   | 5.5                                                       | Conclu                   | usion                                  | 136               |  |

| 6 |                                                           | <b>clusior</b><br>Future | <b>is</b><br>e development             | <b>139</b><br>141 |  |

| 7 | List of publications                                      |                          |                                        |                   |  |

| A | Epitaxial structures for transfer printable lasers        |                          |                                        | 148               |  |

| B | Etched facets ridge lasers for $\mu$ TP to PICs           |                          |                                        |                   |  |

| C | Ledge-less etched facets ridge lasers for $\mu$ TP to PIC |                          |                                        |                   |  |

| D | Recesses on the SOI for laser edge-coupling               |                          |                                        |                   |  |

"I declare, this thesis resumes the research activities I was involved in the achievement of a transfer printable InP laser for silicon photonics.

This is to certify that the work I am submitting is my own and has not been submitted for another degree, either at University College Cork or elsewhere. All external references and sources are clearly acknowledged and identified within the contents. I have read and understood the regulations of University College Cork concerning plagiarism."

Ruggero Loi

## Acknowledgements

I thank *Brian Corbett*, the supervisor of this project, for the careful guidance provided during this thesis and for proposing to me a very interesting and challenging topic.

I am grateful to the people in the III-V group at Tyndall National Institute, in particular to *James O'Callaghan*, *Brendan Roycroft* and *John Justice*, they introduced me to the fabrication and the characterization of InP lasers and supported me during my activities; I thank *Cedric Robert*, *Lei Liu*, *Prasanna Ramaswamy*, *David Quinn*, *Umar Khan*, *Pleun Maskant*, *Mahbub Akter*, *Nan Ye*, for the support given to me in the understanding of photonics and the interesting and useful discussions we had during my studies.

I thank the people of the *Epitaxy and Physics of Nanostructures* group for providing high-spec-custom-made laser materials and accurate surface measurements. In particular, I thank *Emanuele Pelucchi*, *Agnieszka Gocalinska* and *Enrica Mura*.

I thank the whole *X*-*Celeprint* crew for the vital support provided in the understanding of  $\mu$ TP and during the transfer printing experiments. In particular *Chris Bower*, *Antonio Jose Trindade*, *Alin Fecioru*, *Alexander Farrell*, *Steven Kelleher*, *Raja Fazan Gul* and *David Gomez*.

I am grateful to *Simone Iadanza* and *William Whelan Curtin* from *Cork Institute of Technology* for the contribution given at the e-beam on the fabrication of the SOI-chip for the edge-coupling of the InP laser by  $\mu$ TP.

I am grateful to *Francesco Floris* and *Marco Passoni* for the contribution given with the simulations of the determination of the reflectivity of the facet of the laser and for the determination of the light coupling efficiency while misaligning the laser to the waveguide.

I thank the staff of the clean room at Tyndall National Institute for the support provided during the fabrication of the devices. In particular, I thank *Carmel Murphy* and *Dan O'Connell* for the metal evaporations and the initial guidance on the procedures used in the cleanroom, *Richard Davis* and *Patrick Connolly* for providing always a prompt maintenance of the tools, *Colin Lyons* for the advisory on the lithographies.

I thank my colleagues and friends at Tyndall National Institute, in particular *Matthiew Duperron* for the mentorship provided during the first three years of this work; *Domenico Pepe, Nicola Brandonisio, Andrea Pescaglini, Francesco Floris, Marco Dalla Santa, Jan Kegel, Stefano Moroni, Marc Rensing, Luca Zagaglia, Simone Iadanza, Meysam Khangah, Natalia Canas Estrada, Jacek Gosciniak* for the interesting and useful chats and for creating a pleasant workplace around me.

I thank my wife *Enrica Mura*, she always supported me, especially while I was under pressure.

I thank my parents, *Giovanni Paolo Loi* and *Lisetta Fiori* for always supporting me and for the chances they provided to me in life. I thank my parents in law, *Giuseppe Mura* and *Elisa Caocci* for their generosity and support.

I thank all my relatives and friends for always supporting me and in particular those that came to visit me and Enrica during our stay in Ireland, making us feel closer home.

A special aknowledgement goes to Science Foundation Ireland (12/RC/2276 (IPIC) and 15/IA/2864) and the European Union's Horizon 2020 Research and Innovation Programme (45314 (TOP-HIT)), for the financial support provided to this research.

## Abstract

Photonics Integrated Circuits allow optical functionalities and interconnects with small footprint, large band -width and -density, low heat generation. The silicon photonics platform (SOI) offers excellent waveguiding properties, large-area wafers and a highly developed CMOS infrastructure matured with electronics. Nevertheless, the key function of light amplification is missing due to the indirect band-gap of silicon. The light has to be provided to the SOI from a separate direct band-gap III-V material. InP based devices work in the infrared optical window of the electromagnetic spectrum and can be heterogeneously integrated to the SOI.

This research deals with the development of the first stand-alone InP Fabry-Perot lasers heterogeneously integrated to SOI by Micro Transfer Printing ( $\mu$ TP). The lasers are pre-fabricated and tested before transfer and are optimized to reach excellent optical, electrical and thermal performance. Lasers printed on Si substrates emit over 20 mW optical power, have threshold current of 16 mA and series resistance of 6  $\Omega$ ; the thermal impedance of 38 K/W is half of that for the same laser printed directly on the SOI. The transfer printable InP ridge lasers have been designed as rectangular coupons with both contacts at the top and etched facets at the sidewalls. Two main release technologies based on the FeCl<sub>3</sub>:H<sub>2</sub>O (1:2) solution and a InGaAs or a InAlAs sacrificial layer were developed for releasing the devices from the original InP substrate with selectivity to InP greater than 4000 at 1 °C. The working principle of a polymer anchor system which restrains the devices to the substrate during the undercut were determined. The devices were printed on different silicon photonic substrates with excellent adhesion, with and without adhesive layers. A process for creating recesses into the SOI was developed to allow edge coupling the laser waveguide to the SOI or a polymer waveguide. High alignment accuracy along the three spatial directions can be achieved with alignment markers, reference walls and the interposition of a metal layer beneath the devices.

This work shows a possible path for the achievement of a laser source for silicon photonics and it has been the basis for the integration of others InP devices to PICs by micro transfer printing.

## Glossary

- 2D: Bi-dimensional.

- **3D**: Three-dimensional.

- 3*σ*: Three sigma, 99.7 %.

- 5G: Fifth generation cellular broadband network technology.

- *µ***TP**: Micro transfer printing.

- AFM: Atomic force microscope.

- AlN: Aluminium Nitride compound (ceramic).

- **ART**: Aspect ratio trapping.

- ASIC: Application specific integrated circuit.

- BCB: Benzocyclobutene.

- BOE: Buffered oxide etch.

- BOX: Buried oxide.

- CMOS: Complementary metal oxide semiconductor.

- **CPB**: Copper pillar bump.

- **CW**: Continuous wave.

- **DBR**: Distributed bragg reflector.

- **DFB**: Distributed feedback reflector.

- **DI**: De-ionized water.

- DWDM: Dense wavelength-division multiplexer.

- **DUV**: deep ultraviolet.

- EAM: Electro-absorption modulator.

- e-beam: Electron beam.

- EIC: Electronic integrated circuit.

- **FeCl**<sub>3</sub>: Iron chloride compound.

- **FDM**: Finite difference model.

- **FEM**: Finite elements model.

- **FIB**: Focused Ion Beam.

- **FP**: Fabry-Perot.

- FWHM: Full width half maximum.

- **GaN**: Gallium nitride compound.

- **HF**: Hydrofluoric acid.

- HMDS: Hexamethyldisilazane.

- **HR**: Highly reflective.

- **IC**: Electrical integrated circuit.

- **ICP**: Inductively coupled plasma.

- **III-V**: Semiconductor alloys made by group III and V of the periodic table.

- InAlAs: Indium aluminium arsenide ternary III-V compound.

- InGaAs: Indium gallium arsenide ternary III-V compound.

- InP: Indium phosphide III-V compound.

- **IoT**: Internet of things.

- **IPA**: Isopropyl alcohol.

- **IR**: Infrared.

- LD: Laser diode.

- LED: Light emitting diode.

- L-I: Light-current characteristic.

- LO: Lift-off.

- LSS: Large spot size.

- MBE: Molecular beam epitaxy.

- MEMS: Micro electro mechanical systems.

- MFD: Mode field diameter.

- MMI: Multi mode interferometer.

- **MOVPE**: Metal-organic vapour phase epitaxy.

- MOCVD: Metal-organic chemical vapour deposition.

- MQW: Multi quantum well.

- MRI: MMI back reflector.

- MSC: Mode size converter.

- NA: Numerical aperture.

- **QD**: Quantum dot.

- **SBB**: Solder ball bump.

- SOI: Silicon on insulators.

- SOI-PIC: Silicon on insulators photonic integrated circuit.

- **PCB**: Printed circuit board.

- **PD**: Photo diode or photo detector.

- **PDMS**: Polydimethylsiloxane.

- PECVD: Plasma-enhanced chemical vapor deposition.

- **PIC**: Photonic integrated circuit.

- **PSM4**: Parallel single mode 4-channel signal transmission format.

- PW: Pulsed wave.

- **RMS**: Root Mean Square value.

- RSOA: Reflective silicon optical amplifier.

- **RTA**: Rapid thermal annealing.

- SEM: Scanning electron microscope.

- SiN: Silicon nitride.

- **SiN***<sub>x</sub>*: Silicon nitride compound.

- **SiO**<sub>2</sub>: Silicon dioxide.

- **SOA**: Silicon optical amplifier.

- **SOI**: Silicon on insulator.

- **TEC**: Thermoelectric controller.

- TLM: Transmission line measurements

- USA: United States of America.

- UV: Ultraviolet.

- VCSEL: Vertical cavity surface emitting laser.

- V-I: Voltage-current characteristic.

- WDM: Wave division multiplexing.

- **WDM4**: Wave division multiplexing 4 channels signal transmission format.

### Chapter 1

## Introduction

The internet of the future has the purpose of making the world more energy efficient through the interconnection and management of systems and objects of the real world. This is the so called internet of things (IoT). In order to enable such a system, an infrastructure able to exchange continuously the enormous amount of data produced by the IoT has to be set in place. The internet is organized in a way that the data centres work as hubs for the data traffic management and storage. In turn, the performance of the data centres have to be improved in the first instance to enable faster and more energy efficient datacom. Use of photonics inside servers could be the solution for a real paradigm shift in the field of datacom and telecommunication.

This chapter introduces the reader to the motivations behind this thesis work. The data centre architecture and its main requirements are briefly discussed. Photonic integrated circuits (PICs) for datacom are discussed with particular reference to the silicon photonics platform. The lack of a light source in silicon photonics and the demand for integration of a III-V laser able to operate in the O- and C-optical bands of the electromagnetic spectrum are introduced. The chapter ends with an outline of the thesis to provide the reader indications on the structure of this work.

#### **1.1** Data centres and the internet of the future

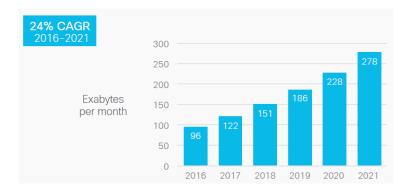

The advent of the Internet of Things (IoT) and the 5G telecommunication format requires an advanced internet infrastructure able to handle Zettabytes of data transmission. As reported in one of the last white papers from Cisco [1] the data traffic on the internet is expected to grow up to  $\sim 280 \cdot 10^{18}$  B/month by 2021 [Fig. 1.1], corresponding to an average  $\sim 8 \cdot 10^2$  Tbps rate.

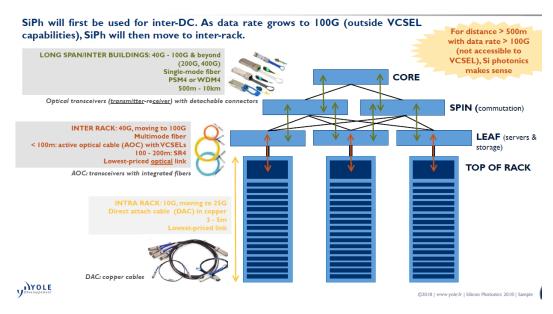

Nowadays optical interconnects are widely deployed in the internet and in data centres down to the ultra-short-reach <10 m interconnects between server racks. The architecture of a data centre with the interconnections types is reported in Fig. 1.2. The data centre is a hub of the internet where many optical links converge in order to access the data stored in servers. The external links access the core of the data centre from which an intricate amount of optical and copper interconnects, networking switches, routers and firewalls allow the access to particular servers and storage subsystems where the information required is stored. The long span inter-building interconnects (500 m to 10 km long links) are usually single mode fibers that allow parallel signal transmission formats as PSM4 and wavelength division multiplexing as WDM4. These interconnects can be operated at 40 to 100 Gbps and beyond (up to 400 Gbps). Optical inter-rack interconnects up to 200 m long are usually multi-mode optical fibers or active optical cables operated by vertical cavity surface emitting lasers (VCSELs) in SR4 format at 40 to 100 Gbps. Intra-rack interconnects up to 5 m long are direct attach cables made by copper that are still cheaper than optical interconnects and can operate up to 10 Gbps and beyond (moving to 25 Gbps). Use of optical interconnects for intra-rack communication would not introduce a great advantage in data rate transmission as the communication inside the servers is based on electronics [2]. The next step in enabling higher speed data flow consists in integrating photonics inside the servers for inter- and intrachip interconnects [3], [4]. Photonics will allow one order of magnitude higher bandwidth of >100 Gbps, spatial density of about Tb/s/mm<sup>2</sup> and reduced 10-100 fJ/bit energy-efficiency compared to the actual electronic servers operating at <10 Gbps, Gb/s/mm<sup>2</sup>, 1-10 pJ/bit while drastically reducing cross-talk, heating and then power-cooling issues [5], [6].

Figure 1.1: Cisco VNI forecasts 278 EB per month of IP traffic by 2021 [1].

**Figure 1.2**: Data centre architecture and data rate allowed by the different interconnects [2].

## 1.2 Photonic integrated circuits for telecom and datacom

A photonic integrated circuit (PIC) is a platform that combines optical devices by connecting them through optical waveguides. Suitable platforms for PICs operating in the telecommunication wavelength range are InP and GaAs which offer integrated monolithic light sources, detectors and modulators; Another important candidate is silicon photonics, which can include SiGe and III-V hybrid integrated active elements; Dielectrics such as SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> offer low loss waveguides and passive elements over a wide wavelength range. PICs are a valuable way to achieve small optical interconnects and functionalities inside servers; PICs have reduced footprint, can be arranged in 3D stacks and can be easily interfaced with the driving or receiving electronics; most importantly PICs provide more bandwidth, low latency and low mutual interference between waveguides while keeping heat generation at minimum. This results in lower power consumption and cooling costs in data centers. High reliability is another aspect benefited by photonic integration [7]. Research in photonic integrated circuits will open new directions for novel optical functions.

PICs for telecom and datacom are modules which transmit or receive signals, the optical transmitters and receivers or a combination of the two, the so called transceivers. These modules are made by combining lasers, modulators, photodiodes and passive optical waveguides to the driving receiving electronics. The laser allows generation of monochromatic light that can be modulated to transmit the information in a digital fashion. The higher the speed of signal transmission the more data that can be exchanged between two or more elements of a circuit per unit time. A laser can be modulated directly, or it can be powered in continuous wave while a modulator arranged in series with it modulates the light intensity or the phase. Photodiodes convert the light signals into current signals and are the core element of receivers.

The first  $10 \times 10$  Gb/s wavelength division multiplexing (WDM) transcei ver was demonstrated in 2004 and since then most of the high-end PICs have been demonstrated on expensive III–V substrates [8], [9]. On the other hand silicon photonics transceivers have been demonstrated up to 25 Gbps [10], [11], and are gaining consent thanks to the reduced cost and the possibility to be fabricated with complementary metal oxide semiconductor (CMOS) technology [12]. The transceivers can be exploited at their best working on the wavelength, the modulation format (by acting on the phase or the amplitude) and by using WDM modulation format which allows multiple bidirectional communications over different waveguides and then parallel multiplication of datacom capacity.

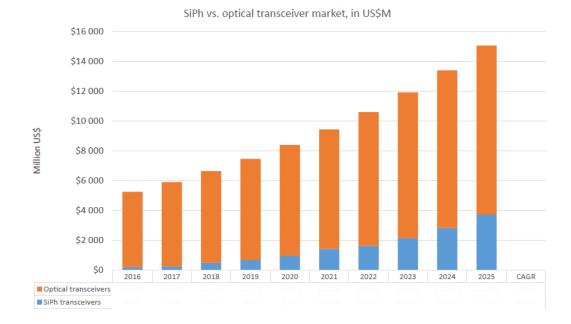

PICs can be created with two main approaches, monolithically, as in the case of InP photonics, and heterogeneously as for Si photonics. The monolithic approach offers integrated, compact, efficient devices. InP active devices like lasers and modulators performs better than silicon-based technologies due to lack of misalignments to the waveguides defined on the same platform. However, passive waveguiding regions of the III-V wafer account for a large waste of the expensive material. The heterogeneous approach offered by Si photonics is more scalable not only because of the larger wafers but also due to the possibility of outsourcing the production of single photonic functions and the integration to different specialized companies. A similar assembly approach has been applied profitably in other large scale production areas as electronics and automotive. Market analysis and forecast show quick growth of the market and high investments in photonics and in particular in silicon photonics [Fig. 1.3] indicating the trend of industry in moving towards the SOI platform and so towards the heterogeneous integration approach.

**Figure 1.3**: The Si photonics transceiver market is growing faster than the total optical transceiver market and is expected to reach more than 3500 M\$ by 2025 [2].

#### **1.2.1** Packaging of PICs

Packaging of PICs is perhaps the main challenge in creating optical transceivers, it requires tight micron alignment of the different optical and electronics elements, accurate temperature control and high spatial density integration of the different components. Telecom and datacom PICs are made by high bandwidth photonic devices connected by optical channels that can operate up to 25 Gbps and be multiplexed. Consequently, driving of the PIC components requires 25 Gbps electrical channels with low reflections and artifacts. Matching of photonics with electronics can be achieved with different layouts depending mainly on the final system. In some cases the PICs can be integrated with different layouts to an electronic integrated circuit (EIC), alternatively the PIC and the electrical integrated circuits (IC) can be integrated on a common EIC [10], [13], [14], [15]. In some cases, due to the large dimension of PICs it is convenient to integrate ICs along the PIC to drive the optical components [15]. The system is then connected to the electronics.

The electrical connection between a standard electronic printed circuit board (PCB) and the PIC can be achieved in different ways as there is not a standard layout for it. 50  $\Omega$  transmission lines able to deliver electrical signal to the photonic components connect a PCB to a PIC. A pitch-reducing multi-level ceramic interposer matches the pitch of the PCB electrical channels to that of the PIC which can be a factor of three smaller [15]. The Interposer is connected to the PCB by  $\sim 20 \ \mu m$  diameter and 100–500  $\mu m \log Au$ wire-bonds and to the PIC by bond pads [15]. The high-speed signals sent to the PIC must be then routed from the bond-pads to and from the relevant components on the PIC, tipically with a co-planar geometry. In small optical system such as transceivers, the vertical integration of a driver on the PIC is usually preferred over wire-bonds and interposers as it improves the high-speed electronic interface to the PIC with shorter and straight highly dense electrical connections that allow accurate sub-ns switching of multiple channels [15]. The vertical integration of an IC on a PIC can be achieved using  $\sim 10 \ \mu m$  short solder-ball-bump (SBB) or copper-pillar-bump (CPB) interconnects, which provide an electrical, mechanical, and thermal interface between the two chips and minimize parasitic induction effects [16], [17], [18], [19], [20], [15]. A  $<\pm 1 \mu$ m accuracy alignment of the IC to the PIC can be achieved with a flip-chip system.

The light signals to and from the optical transceivers are coupled to optical fibers mainly through a grating or a mode size converter (MSC) in a edge-coupling configuration (see next chapter for more details about different types of light coupling) [15].

#### **1.3** Silicon photonics integrated circuits

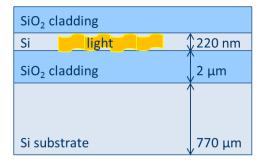

Silicon photonics is a large-area scalable platform offering up to 300 mm diameter wafers [21], this allows the integration of thousands of photonic components in waveguides above a buried silicon dioxide (BOX) cladding layer (Silicon on Insulator waveguides or SOI) [Fig. 1.4]. Silicon wafer are fabricated with the highest crystal lattice quality and are transparent in the wavelength range 1.1  $\mu$ m to 8  $\mu$ m allowing for light waveguiding in a broad range of wavelengths. This is of particular interest for the telecom wavelengths in the range 1.3  $\mu$ m - 1.6  $\mu$ m. Moreover, the SOI platform offers high index contrast between the Si waveguiding layer and the buried oxide allowing for high light confinement in tiny single mode waveguides of 220 nm × 450 nm cross section, with sharp bends of <5  $\mu$ m bending radius that help reducing the foot print of the PIC. Silicon photonics integrated circuits (SOI-PICs) are able to provide multiple optical functions on wafer such as ring and Mach-Zehnder modulators normal and in-plane couplers, multi channel dense wavelength-division multiplexers (DWDM)

and demultiplexers. Ge hetero-structures as electro-absorption modulators (Ge-EAM) and photo-detectors (Ge-PD) can be monolithically integrated in particular spots of the SOI wafer. Optically pumped Raman lasers have been demonstrated too [22].

**Figure 1.4**: Schematic cross section of a standard SOI wafer. The light propagates in the 220 nm thick Si waveguiding layer, the top SiO<sub>2</sub> cladding layer is optional.

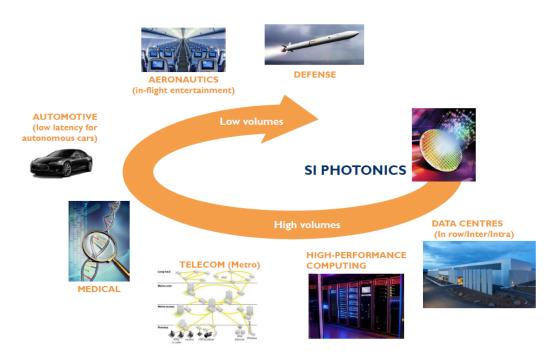

Silicon photonics, which is addressing many different opportunities and particularly optical interconnections for data centers, is an excellent platform for scaling photonics due to its similarity with the principles of the semiconductor electronics industry [23], [24], [25], [26], [12]. Silicon photonics exploits the fabrication experience, technology, and scalability already developed for complementary metal-oxide semiconductor (CMOS) electronics [4], [13], for the development of low-cost high-volume PICs with integrated electronics [3]. The functionalities of silicon photonics are revolutionizing the fields of telecommunication, datacom, high performance computing, medical devices, sensing automotive and military [27] [28], [23], [29], [Fig. 1.5]. Moreover SOI-PICs are applied in the creation of miniaturized spectrometers, bio-sensors, gas-sensors, lidar, optical coherence tomography etc. [15].

Contrary to III-V materials, Si is a naturally abundant material, it has high thermal conductivity of  $\sigma(Si) = 1.3 \text{ W} \cdot \text{cm}^{-1} \circ \text{C}^{-1}$ . Silicon photonics has the lowest cost per unit area with a 300 mm SOI wafer cheaper than a standard 50 mm diameter InP substrate. On the other hand the design and the development of new processes for silicon photonics accounts for most of the chip production costs, so the price per chip drops only when large scale fabrication can be achieved and only after that the processes have been optimized. Nevertheless, the key function of amplification (and lasing) is missing due to the indirect band-gap of silicon which makes it unlikely for electrons and holes to recombine radiatively when excited. Optical amplifiers in photonics are analogous of transistors in electronics, they are vital for creating lasers, switchers, for broadcast, wavelength conversion etc. Monolithic

Figure 1.5: Silicon photonics applications production. [2].

integration of optical amplifiers on Si still requires more development (see section 2.2.2), Ge can be heavily doped and strained to achieve a pseudo direct band-gap but the radiative recombination rate still remains low for creating an efficient laser light source. Another possibility is to hybrid integrate a III-V component onto silicon for light amplification. This strategy has been proven to be the most effective (see chapter 2), but usually comes with light coupling issues between the III-V element and the SOI waveguides which need to be carefully evaluated as they can have important consequences for optical power budgets and energy efficiency of the whole PIC.

#### **1.4 III-V materials and silicon photonics**

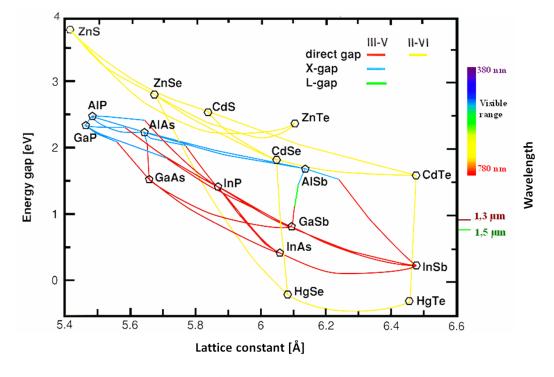

III-V compound semiconductors are alloys containing elements from groups III and V in the periodic table. III-V typically are zincblende crystal structures with superior electron mobilities and direct band-gap which makes them suitable for efficient light amplification by stimulated emission. Changes in the alloy influences the lattice constant and the characteristic band-gap of the material, thus the wavelength of emission [Fig. 1.6]. These alloys can be lattice matched with ternary or quaternary compound semiconductors (alloys of three, four elements of III-V). This allows the realization of epitaxial structures whose wavelength of emission can be finely tuned. For example the AlGaInAs active region of an InP telecom laser can be designed to emit at  $\sim$ 1550 nm wavelength.

**Figure 1.6**: Energy gap versus lattice distance and corresponding emission wavelengths of the alloy. [30].

Driven by increasing global IP traffic, there are growing opportunities for III-V based semiconductor photonics components to be used in a diverse range of applications. These components need to be provided at low cost and should ideally scale in similar manner to silicon electronics. Nevertheless, due to the specific nature of individual III-V photonic components (lasers, modulators, detectors), it is highly challenging to monolithically integrate all these functions on a single substrate without compromising the performance of the individual devices [8] [31]. Thus, in general, a heterogeneous integration approach can be an effective way to combine optimized components for different PICs [32]. This would lead to the photonics components not being stand-alone but being co-integrated with different electronic and wave-guiding platforms.

Due to the lack of optical gain in silicon, an amplifier component needs to be integrated with silicon photonics in order to provide a gain medium and enable the most functional PICs. The laser light for the silicon photonics has to be provided from a separate direct band-gap III-V material. InP or GaAs based devices can be heterogeneously integrated depending on the wavelength range it is desired to work at. GaAs based laser are used to operate in the optical band centered at 875 nm. As Si absorbs in the visible and near infrared (for wavelength  $\lambda$ <1200 nm), InP substrate based laser sources provide the most mature laser structures for data transmission in the optical C-band or in the O-band of the optical spectrum centered at 1550 nm and 1310 nm respectively. This wavelength range also offers easier interfacing of the PIC to the operational wavelength range of silica optical fibers. The heterogeneous integration of an InP-based devices to SOI has been demonstrated by using different integration techniques such as wafer bonding and micro transfer printing [33] [34] [35] [36] [37] (see section 2.2 for a more detailed discussion about these technologies).

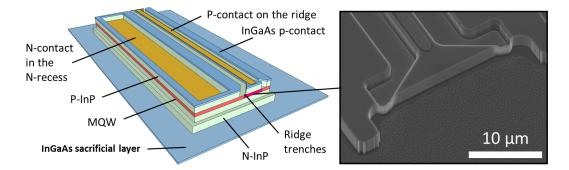

III-V laser sources for telecom SOI-PICs are made by an InP section that amplifies the light and two mirrors that create a resonating cavity for the light generated. The light emitted by the device has to be single spatial mode in order to efficiently couple to a standard single mode SOI waveguide. Single mode emission is achieved by laterally confining the light with a micron scale wide ridge on top of the active region. These devices are realized as p-i-n junctions with the intrinsic region grown epitaxially as a few hundred nm thick multi quantum well structure. Ohmic electrical contacts have to be defined to the p side (over the ridge) and to the n layer in order to inject the electric current that activates the diode.

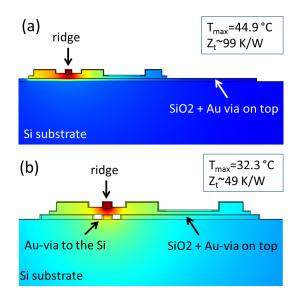

A crucial issue in the heterogeneous integration of InP active elements to SOI platforms is the thermal sinking of the heat produced by the device in operation [38], [39]. The heat generated by an integrated laser will increase the temperature of the active region shifting its wavelength and reducing its efficiency. The heat will also affect the platform on which the device operates through, for example, the resultant temperature distribution changing the properties of many devices (e.g. ring resonators, phase modulators) through the temperature dependence of the refractive index of silicon. In fact, while silicon is an excellent thermal conductor, the buried oxide in the SOI has poor thermal conductivity of  $\sigma_{SiO(2)} \sim 1.4 \text{ Wm}^{-1}\text{K}^{-1}$ . Since this represents an issue for the operation of the active devices on the SOI, the integration of III-V lasers requires careful attention of the system geometry and the materials involved to manage the heat produced [38], [40], [41], [42]. In the die bonding approach the heat should be dissipated through the buried oxide layer, so thermal shunts, metallic vias and trenches have been applied to sink the heat from the device to the Si substrate along preferential paths [42] [43], [34]. This approach involves a high level of complexity in fabrication, especially after the integration of the III-V to the SOI. Another possibility consists in bonding the III-V laser die upside down on a metal sub-mount in contact with the Si substrate while achieving light coupling to the SOI waveguide by gratings [44], [45]. A different approach is to sink the heat to the substrate by  $\mu$ TP of the devices inside a recess on the SOI directly on the silicon substrate and then edge coupling the light to a waveguide [46] [47], [48].

#### **1.5** Thesis structure

This work finds its main motivation in the development of a light source for silicon photonics; the structure of this work is summarized in 5 chapters which will guide the reader in a chronological description of the integration process of an InP transfer printable ridge laser with dry-etched facets to Si photonics by micro transfer printing.

- **Chapter 1**: As described at the beginning of this chapter, the first part focuses on the motivations behind this research. The data centre of the future requires photonic integrated circuits (PICs) for high speed intraservers datacom. Si photonics results the best candidate for telecom PICs, but requires a III-V laser source able to operate in the infrared region 1300-1600 nm of the electromagnetic spectrum.

- Chapter 2: This section of the thesis reports the state of the art in the heterogeneous integration of III-V lasers to silicon photonics. The main strategies for light coupling between waveguides are discussed as they determine the final geometry of the integrated laser. The principal approaches used for light sourcing silicon photonics are reported with particular focus on the heterogeneous integration approach. The wafer bonding technology used for the integration of III-V to silicon photonics and the new emerging approach of micro transfer printing are reviewed here. The strategy chosen in this work for integrating an InP laser to silicon photonics is described in the final section.

- **Chapter 3**: The laser epitaxial structures used for transfer printable InP devices are discussed in this chapter. The design and the technological issues related to the fabrication of the device and its elements (facets, contacts, coupon shape) are described. The wet-etching release technology developed for the two main release structures used, In-GaAs/InP and InAlAs/InP are described. The printing of the devices

with and without adhesives, the anchors removal and the adhesion enhancement methods are described too. Finally the recesses formation for laser integration and edge coupling to the SOI are described.

- **Chapter 4**: In this chapter are presented the electro-optical and the thermal characterization of the InP ridge lasers developed, before and after transfer printing to silicon photonics and other substrates. At the end of the chapter the effects of transfer printing on the device performance are discussed.

- Chapter 5: This chapter reports the simulations of the light edgecoupling of InP lasers to polymer and to SOI waveguides. The design and the sizing of the integrated system was determined by maximizing the light coupling efficiency. The demonstration of the first O-band laser heterogeneously integrated by μTP to recesses in the SOI and edge coupled to a multi-mode polymer waveguide is discussed together with the characterization steps performed.

- **Conclusions**: This section of the thesis summarizes the main results of this work focusing on the technological impact of this research. Future development and possible application of this technology are discussed at the end.

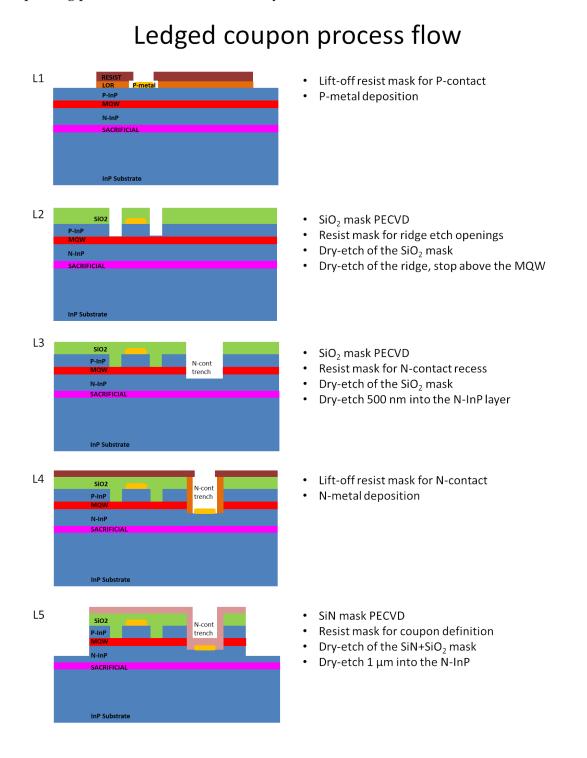

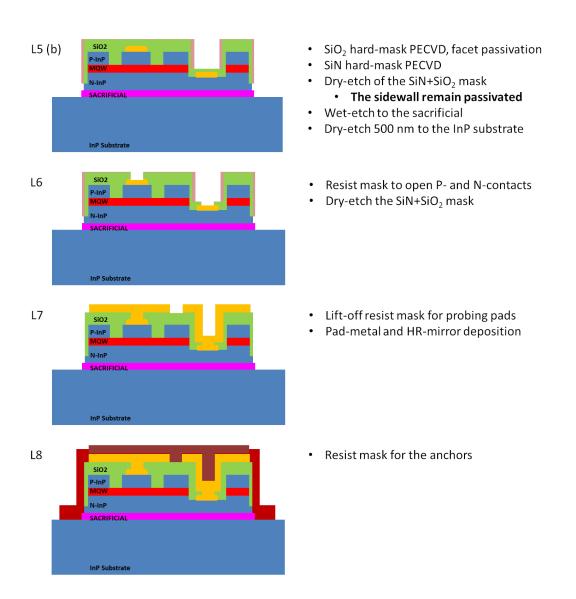

- Appendixes: Appendix A reports the main epitaxial structures used in this work for transfer printable InP lasers; Appendix B and C report the detailed fabrication processes for achieving a transfer printable InP Fabry-Perot laser coupon with and without encapsulation ledge. The ledge-less laser coupon is suitable for complete match of the emitting facet of the laser to a MSC on the SOI. Appendix D describes the fabrication process of recesses in the SOI, suitable for printing a laser coupon matched to the SOI.

## Bibliography

- [1] Cisco. The zettabyte era: trends and analysis. Updated (07/06/2017). 2017.

- [2] Yole Developpement. Silicon Photonics 2018: Yes, we've reached Si photonics' tipping point! 2018. URL: https://www.i-micronews.com/ report/product/silicon-photonics-2018.html (visited on 11/21/2018).

- [3] Roger Dangel et al. "Polymer waveguides for electro-optical integration in data centers and high-performance computers". In: *Optics express* 23.4 (2015), pp. 4736–4750.

- [4] Günther Roelkens et al. "III-V/silicon photonics for on-chip and intrachip optical interconnects". In: *Laser & Photonics Reviews* 4.6 (2010), pp. 751–779.

- [5] David A B Miller. "Physical reasons for optical interconnection". In: Intel J. Optoelectronics 11 (1997), pp. 155–168.

- [6] Sébastien Rumley et al. "Optical interconnects for extreme scale computing systems". In: *Parallel Computing* 64 (2017), pp. 65–80.

- [7] Sai Chu et al. "Advanced photonic integration and high-index-contrast circuit". In: *Proc. Optoelectron. Commun. Conf.(OECC)*. 2009, pp. 1–2.

- [8] Hyundai Park et al. "Device and integration technology for silicon photonic transmitters". In: *IEEE Journal of Selected Topics in Quantum Electronics* 17.3 (2011), pp. 671–688.

- [9] Radhakrishnan Nagarajan et al. "Large-scale photonic integrated circuits". In: *IEEE Journal of Selected Topics in Quantum Electronics* 11.1 (2005), pp. 50–65.

- [10] Akinori Hayakawa et al. "Silicon Photonics Optical Transceiver for High-speed, High-density and Low-power LSI Interconnect". In: FU-JITSU Sci. Tech. J 52.1 (2016), pp. 19–26.

- [11] Xuezhe Zheng and Ashok V Krishnamoorthy. "Si photonics technology for future optical interconnection". In: *Communications and Photonics Conference and Exhibition*, 2011. ACP. Asia. IEEE. 2011, pp. 1–11.

- [12] Christopher Richard Doerr. "Silicon photonic integration in telecommunications". In: *Frontiers in Physics* 3 (2015), p. 37.

- [13] Lockwood Tsybeskov, David J Lockwood, and Masakazu Ichikawa. "Silicon photonics: CMOS going optical [scanning the issue]". In: *Proceedings of the IEEE* 97.7 (2009), pp. 1161–1165.

- [14] Cyriel Minkenberg et al. "Reimagining datacenter topologies with integrated silicon photonics". In: *Journal of Optical Communications and Networking* 10.7 (2018), B126–B139.

- [15] Lee Carroll et al. "Photonic packaging: transforming silicon photonic integrated circuits into photonic devices". In: *Applied Sciences* 6.12 (2016), p. 426.

- [16] Kerstin Worhoff et al. "Flip-chip assembly for photonic circuits". In: *Micro-Optics: Fabrication, Packaging, and Integration*. Vol. 5454. International Society for Optics and Photonics. 2004, pp. 9–20.

- [17] XR Zhang et al. "Copper pillar bump structure optimization for flip chip packaging with Cu/Low-K stack". In: 2010 11th International Thermal, Mechanical & Multi-Physics Simulation, and Experiments in Microelectronics and Microsystems (EuroSimE). IEEE. 2010, pp. 1–7.

- [18] KM Chen and TS Lin. "Copper pillar bump design optimization for lead free flip-chip packaging". In: *Journal of Materials Science: Materials in Electronics* 21.3 (2010), pp. 278–284.

- [19] Philip Garrou, Christopher Bower, and Peter Ramm. Handbook of 3D Integration, Volume 1: Technology and Applications of 3D Integrated Circuits. John Wiley & Sons, 2011.

- [20] JM Fedeli et al. "Development of silicon photonics devices using microelectronic tools for the integration on top of a CMOS wafer". In: *Advances in Optical Technologies* 2008 (2008).

- [21] Shankar Kumar Selvaraja et al. "Highly uniform and low-loss passive silicon photonics devices using a 300mm CMOS platform". In: Optical Fiber Communication Conference. Optical Society of America. 2014, Th2A–33.

- [22] Haisheng Rong et al. "A continuous-wave Raman silicon laser". In: *Nature* 433.7027 (2005), p. 725.

- [23] Richard Soref. "The past, present, and future of silicon photonics". In: *IEEE Journal of selected topics in quantum electronics* 12.6 (2006), pp. 1678– 1687.

- [24] Michael Hochberg and Tom Baehr-Jones. "Towards fabless silicon photonics". In: *Nature Photonics* 4.8 (2010), p. 492.

- [25] Solomon Assefa et al. "CMOS-integrated optical receivers for on-chip interconnects". In: *IEEE Journal of Selected Topics in Quantum Electronics* 16.5 (2010), pp. 1376–1385.

- [26] Guoliang Li et al. "Ultralow-loss, high-density SOI optical waveguide routing for macrochip interconnects". In: *Optics express* 20.11 (2012), pp. 12035–12039.

- [27] Chen Sun et al. "Single-chip microprocessor that communicates directly using light". In: *Nature* 528.7583 (2015), p. 534.

- [28] Matthew Streshinsky et al. "The road to affordable, large-scale silicon photonics". In: *Optics and Photonics News* 24.9 (2013), pp. 32–39.

- [29] Yasuhiko Arakawa et al. "Silicon photonics for next generation system integration platform". In: *IEEE Communications Magazine* 51.3 (2013), pp. 72–77.

- [30] Prof. Dr. Helmut Foll. III-V Semiconductors and Optoelectronics. 2018. URL: https://www.tf.uni-kiel.de/matwis/amat/semitech\_en/ kap\_2/backbone/r2\_3\_1.html (visited on 11/21/2018).

- [31] Po Dong et al. "Silicon photonic devices and integrated circuits". In: *Nanophotonics* 3.4-5 (2014), pp. 215–228.

- [32] Guang-Hua Duan et al. "New advances on heterogeneous integration of III–V on silicon". In: *Journal of Lightwave Technology* 33.5 (2015), pp. 976–983.

- [33] Marco Lamponi et al. "Heterogeneously integrated InP/SOI laser using double tapered single-mode waveguides through adhesive die to wafer bonding". In: *Group IV Photonics (GFP), 2010 7th IEEE International Conference on*. IEEE. 2010, pp. 22–24.

- [34] Günther Roelkens et al. "III-V/Si photonics by die-to-wafer bonding". In: *Materials Today* 10.7-8 (2007), pp. 36–43.

- [35] Gunther Roelkens et al. "III-V-on-silicon photonic devices for optical communication and sensing". In: *Photonics*. Vol. 2. 3. Multidisciplinary Digital Publishing Institute. 2015, pp. 969–1004.

- [36] Ruggero Loi et al. "Transfer printing of AlGaInAs/InP etched facet lasers to Si substrates". In: *IEEE Photonics Journal* 8.6 (2016), pp. 1–10.

- [37] Andreas De Groote et al. "Transfer-printing-based integration of single-mode waveguide-coupled III-V-on-silicon broadband light emitters".

In: Optics Express 24.13 (2016), pp. 13754–13762.

- [38] Ruggero Loi et al. "Thermal Analysis of InP Lasers Transfer Printed to Silicon Photonics Substrates". In: *Journal of Lightwave Technology* 36.24 (2018), pp. 5935–5941.

- [39] Chao Chen et al. "Sharing and placement of on-chip laser sources in silicon-photonic NoCs". In: *Networks-on-Chip* (NoCS), 2014 Eighth IEEE/ACM International Symposium on. IEEE. 2014, pp. 88–95.

- [40] Zhi H Quan et al. "Thermal modelling of transfer-bonded thin-film gallium arsenide laser diode". In: *IET Optoelectronics* 10.2 (2016), pp. 51– 56.

- [41] Matthew N Sysak et al. "Experimental and theoretical thermal analysis of a hybrid silicon evanescent laser". In: *Optics Express* 15.23 (2007), pp. 15041–15046.

- [42] Matthew N Sysak et al. "Hybrid silicon laser technology: A thermal perspective". In: *IEEE Journal of Selected Topics in Quantum Electronics* 17.6 (2011), pp. 1490–1498.

- [43] Stanley Cheung et al. "Design optimization of energy-efficient hydrophobic wafer-bonded III-V/Si semiconductor optical amplifiers". In: Optical Interconnects Conference, 2013 IEEE. IEEE. 2013, pp. 108–109.

- [44] Bowen Song et al. "3D integrated hybrid silicon laser". In: *Optics express* 24.10 (2016), pp. 10435–10444.

- [45] Bowen Song et al. "High-Thermal Performance 3D Hybrid Silicon Lasers". In: *IEEE Photonics Technol. Lett* 29 (2017), pp. 1143–1146.

- [46] *Micro-transfer printing for advanced scalable hybrid photonic integration.* Vol. 5. Valencia, Spain, 2018.

- [47] Joan Juvert et al. "Integration of etched facet, electrically pumped, C-band Fabry-Pérot lasers on a silicon photonic integrated circuit by transfer printing". In: Optics express 26.17 (2018), pp. 21443–21454.

- [48] *Edge-coupling of O-band InP etched-facet lasers to polymer waveguides on SOI by micro-transfer-printing.* Ghent, Belgium, 2019.

#### Chapter 2

# III-V lasers for Si photonics and integration

The integration of III-V lasers to silicon photonics is an hot topic in recent research due to the possibility of joining the advantages of the III-V materials with those of the SOI platform for creating advanced photonic integrated circuits. The layout of a photonic circuit should depend mainly on the final packaging as the geometry and the layout of an integrated photonic device should be determined mainly by the way the light is coupled from the device to the waveguides. The engineering of the whole integration process should start with the analysis of these two main points. More often the integration goes the other way around with the devices to be integrated that determine the hosting platform layout. Still great efforts are needed in the standardization of the layouts of photonic integrated devices suitable for large scale production as the technology is at the early stage.

This chapter introduces the main approaches being used for coupling a III-V laser light source to silicon photonics with reference to the strategy used to couple the light between waveguides. The integration of III-V elements to silicon photonics has been successfully demonstrated through wafer bonding and it is discussed how it can be improved by micro transfer printing. The strategy chosen for the integration of a telecom InP laser to SOI is discussed at the end of the chapter.

#### 2.1 III-V Laser sources for silicon photonics

Due to the indirect band-gap of Si it is challenging to create a laser light source from Si as the rate of radiative recombination when the material is excited is too low. Direct band-gap materials such as the III-V alloys provide efficient radiative recombination by stimulated emission when an external bias pumps the electric carriers in the conduction band. As mentioned in the previous chapter it is possible to use strain and heavy doping to adjust the band-gap of Ge to being direct, but still the lasing performances of these materials are far from those of the III-V alloys. The advantages offered by the III-V compound semiconductors and their operation wavelengths make these materials suitable for creating efficient laser sources for silicon photonics. The light sourcing of silicon photonics with III-V must be achieved with a simple layout of integration and high light coupling efficiency in order to reduce powering budgets (as discussed in chapter 1). The III-V laser can be external to the PIC or integrated on it, then the light coupling can be achieved in different ways and with diverse layout of integration as outlined below:

- External laser

- Laser to fiber to PIC

- External cavity laser

- On-chip laser

- Monolithically grown III-V laser

- Heterogeneously integrated laser

Each of these configurations is classified as hybrid if the mirrors of the laser are positioned outside the III-V, i.e. on the SOI waveguide. Before discussing the different lasers for silicon photonics with their advantages and limitations, it is important to introduce the main light coupling strategies between waveguides as these determine the final layout of the device and of the PIC.

#### 2.1.1 Light coupling between waveguides

The light coupling between dissimilar waveguides is particularly challenging due to mode mismatch being the main source of losses in the light insertion into a waveguide. For example, the mode size of a beam emitted by a single mode InP ridge laser is approximately  $3.2 \times 1.7 \,\mu\text{m}^2$  while in a typical SOI single mode waveguide is  $0.5 \times 0.3 \,\mu\text{m}^2$  in size. Phase matching and polarization issues can sensibly affect the light coupling between the laser and the SOI waveguide depending on the light coupling configuration and by the modes supported by the waveguides coupled. Polarization is usually a big issue when coupling the light through gratings and is a second order loss in edge coupling. The light coming from an optical waveguide or fiber can be coupled to another waveguide in three main ways, by:

- Light coupling through gratings.

- Light evanescent-coupling.

- Light edge-coupling.

Each of these approaches has its own advantages and limitations, being more appropriate to a particular application. The principal aspects of these three different light coupling approaches applied to silicon photonics are discussed in the next sections.

#### Light coupling through gratings

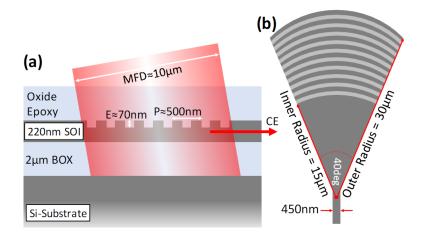

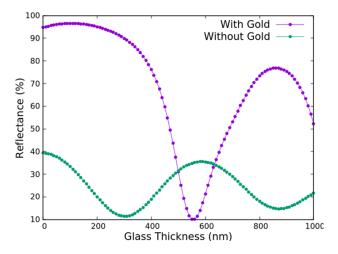

Light coupling through gratings at infrared wavelength exploit a sub-micron periodic structure to create a coherent interference condition that diffractively couples the injected beam into the adjacent SOI waveguide [1], [2]. The incoming light has to be directed to the grating at a designed angle (usually of  $\sim 10^{\circ}$ ) as to minimize the reflectance at the first order and maximize the injection according to the Bragg law. The etch depth of the grating changes the effective refractive index of the meta-material and has to maximize the transmittance while reducing the reflectance. The gratings are defined by immersion lithography or by electron beam (e-beam) lithography as shallow trenches etched into the SOI waveguiding layer [Fig 2.1(a)]; they can be shaped as mono dimensional or as bi-dimensional (2D) structures (more tolerant to misalignment) [Fig 2.1(b)]. Grating couplers do not need to be placed at the edge of the chip and can be wafer-scale tested before dicing and packaging. A typical 2D grating defined on a 220 nm thick SOI for matching the mode field diameter of a telecom optical fiber transmitting light at 1550 nm wavelength consists of a periodic array of 20 trenches about 70 nm deep and has a  $\sim 10 \times 10 \ \mu m^2$  area footprint [3]. Typical light coupling configurations consist of an optical fiber (or a waveguide) to grating or grating-to-grating and the insertion losses are typically -3 dB. Recent works on uniform and apodized grating-couplers on SOI report a 1.6 dB and 1.2 dB insertion-losses [4], [5]. Insertion losses as low as 0.6 dB can be achieved by incorporating a metallic back-reflector, however this process is not scalable at the moment [6]. Grating couplers result highly spectral and polarization dependent behaviour typically allowing only <100 nm spectral

band-width. The polarization sensitivity is strong for linear grating couplers, however a 2D grating-coupler can be designed to accept any incoming polarization of light [7]. 2D grating couplers have insertion losses of 1.0 dB and 2.0 dB for designs with and without back-reflectors respectively, the polarization dependent losses can be as low as 0.3 dB [8], [9]. Grating couplers offer relaxed  $\pm 2.5 \ \mu$ m in-plane alignment tolerances with an extra 1 dB penalty [10].

**Figure 2.1:** Fiber to SOI-PIC grating-coupling; (a) Side-view schematic of the grating-coupler defined on the SOI. The 10  $\mu$ m mode field diameter (MFD) shines on the grating with a  $\approx 10^{\circ}$  angle; (b) Top-view schematic of a 2D focusing grating-coupler. The footprint of the coupler matches the MFD of the optical fiber. [11].

#### Light evanescent-coupling

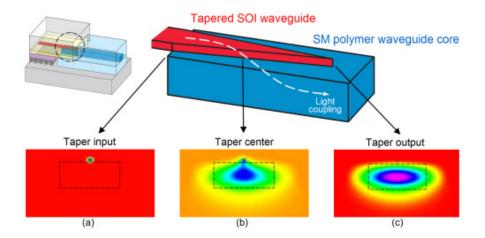

The evanescent coupling of the light between two adjacent waveguides is given by the interaction of the tail of the propagating modes. This strategy has been widely applied in the light coupling between III-V and SOI waveguides. Evanescent coupling between a III-V optical amplifier and an SOI waveguide were demonstrated at University of Santa Barbara (USA), IMEC (Belgium) and LETI (France), by using inverted taper structures [12], [13], [14] [15], [16], [17], [18], [19]. The light coupling efficiency was lower than 60 % as the light coupling between the III-V and the SOI waveguides was not completely adiabatic. The first truly adiabatic tapered structure for evanescent light coupling was demonstrated by IBM in 2015 [20]. In this case the light was completely evanescent coupled from an SOI waveguide to a single mode polymer waveguide with light coupling efficiency higher than 90 % [Fig. 2.2]. The same principles can be theoretically applied for the light coupling to glass-, SiN- or SiON-based waveguides coupled to the SOI. The evanescent coupling offers low insertion-loss of <1 dB, broadband

coupling, low sensitivity to polarization and relaxed alignment tolerances of  $\pm 2 \mu m$  between single mode waveguides [20]. The inverted-taper of the evanescent coupler can be placed anywhere on the SOI, however its millimeter long foot print must be kept into account when designing a PIC.

**Figure 2.2**: Schematic of the adiabatic evanescent coupling between SOI and polymer waveguides. The theoretical simulation of the optical coupling at  $\lambda$ =1550 nm show how (a) the light completely confined in the SOI waveguide, (b) is gradually squeezed in the polymer waveguide. (c) At the end of the taper all the light is completely confined in the polymer waveguide. [20].

### Light edge-coupling

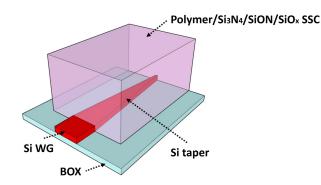

Light edge-coupling is achieved when butt coupling two waveguides one in front of the other. The edge-coupling has been widely applied in the light coupling between optical fibers and PICs and in commercial packaging of laser-chips to optical fibers [21] thanks to its broadband, polarization agnostic insertion-losses of better than -1 dB [22]. The mode mismatch between the two waveguides represents the main source of injection losses in this approach [23], [24], [25], [26]. In this configuration, the light is injected at the edge of the PIC into a mode-matched mode-size-converter (MSC) evanescent coupled to an underlying tapered SOI [Fig. 2.3]. MSCs can be made of SiON, polymer, SiO<sub>x</sub>, Si<sub>3</sub>N<sub>4</sub> waveguides embedding the inverted taper on the SOI waveguide [27]. Despite the many advantages offered, this strategy has not been widely applied to lasers integrated on-chip to silicon photonics due to the technological issues related to bulky packaging of lasers [28], [29], alignment and mode mismatch between the III-V laser waveguide and the SOI and due to requirement of using the etched facet technology. The particular application of the edge coupling to on-chip lasers and the state art of the device development is discussed more in detail in section 2.1.4.

**Figure 2.3:** Diagram of a MSC for light edge coupling to a single mode SOI waveguide. The MSC can be made by an overlay of polymer, Si3N4, SiON or SiOx deposited over the taper defined on the SOI, this allow evanescent coupling and mode size conversion. [27].

## 2.1.2 External laser source

The light from an external laser source can be delivered to the SOI-PIC through an optical fiber and injected at an angle into a grating coupler on the SOI as already described. Another option is to cut the fiber facet at an angle and polish it to create a mirror that reflects the light down to the grating at the correct angle; this strategy offers a quasi-planar approach and reduced packaging dimensions [30], [31]. Alternatively, the fiber can be edge coupled to a mode transformer positioned at the edge of the SOI chip. These two strategies offer good light coupling efficiencies usually achieved through active alignment, however the injection of the light at the edge of the chip can be a limitation and requires use of large foot-print connection blocks [11]. In the edge coupling the SOI-PIC requires high precision dicing and polishing of the edges for achieving highly smooth matching surfaces on the SOI side. Another way to integrate lasers to the SOI is to pre-fabricate and pre-test a laser chip that can be light coupled in a dedicated location on the SOI as patented by Macom [32], or as demonstrated by Kotura and Oracle or by Luxtera [33], [34], [35]. This solution offers good alignment (<1  $\mu$ m) and light coupling efficiency but is quite bulky (>100  $\mu$ m thick) due to the packaging and can be not suitable for 3D stacking of SOI-PICs. Bulky PICs are usually more functional for stand alone applications as medical devices and sensors. A more compact layout is achieved by edge-coupling InP reflective semiconductor optical amplifier chips to silicon or silicon nitride photonics in external cavity laser configuration as demonstrated by Zilkie et al. [33] and more recently by Iadanza et al. [36]. In this case the coupling efficiency reaches up to 80 % for <1  $\mu$ m and <0.5  $\mu$ m lateral and vertical misalignment respectively.

**Figure 2.4**: Schematics of the hybrid laser in external cavity configuration. The optical amplifier has a SiN mirror at the back facet and is edge-coupled to a SiN waveguide on the emitting side. The front reflector is on the SiN waveguide and consists in a Bragg grating. [36].

## 2.1.3 Monolithically grown III-V laser on silicon photonics

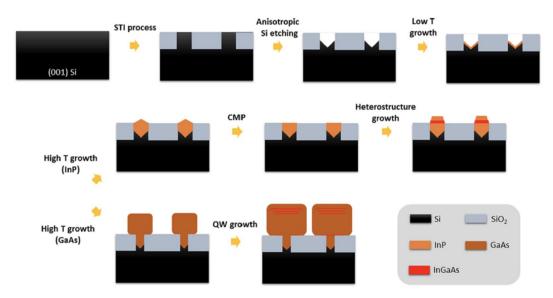

The development of a monolithic laser for silicon photonics is an hot topic in recent research [37], [38]. Germanium has been proposed as a possible monolithic light source due to its availability in CMOS factories today. Ge lasers monolithically grown on silicon have been demonstrated [39], however they show a threshold current density more than three orders of magnitude higher than that of III-V based lasers. This makes Ge lasers not applicable for commercial devices where low operating power is a key requirement for most applications. III-V monolithically grown on Si can be achieved by direct hetero-epitaxy and selective area hetero-epitaxy [40], [41], [42]. III-V laser epitaxial structures grown on Si have been grown directly on SOI allowing to create monolithic laser sources [43], [44], [45], [46]. Heteroepitaxial growth of III-V to SOI can be achieved by molecular beam epitaxy (MBE) or metal-organic vapour phase epitaxy (MOVPE, also known as MOCVD). MOVPE and MBE allow very high control over thickness, composition and doping. In MOVPE, in contrast to MBE, the growth of crystals is by chemical reaction and not physical deposition. All these techniques provide high quality material only when grown on a substrate with the same lattice constant. Silicon and III-V present a mismatch in the lattice constant of 4.1 % for GaAs and of 8.1 % for InP, a different interface polarity and thermal expansion difference of  $\sim$ 120 % for GaAs and  $\sim$ 77 % for InP which make the direct growth of III-V to Si particularly challenging, especially for large area III-V grown on silicon. Different methods as special surface treatment, strained super-lattices, low-temperature buffers growth on patterned substrates have been used to reduce the lattice mismatch defects to <110

$cm^{-2}$ , but this value is still about two orders of magnitude higher than that achieved with InP- or GaAs-based epitaxial wafers for room-temperature CW lasers. An alternative approach to reduce stress created by lattice mismatch between III-V and Si is to grow small area systems as quantum dots (QDs) or nano wires [47], [48], [49], [50]. Huge progress has been made with QDs laser grown on Si by Liu et al. [51], however a buffer layer and more development to combine this technology with silicon photonics are required. More recently aspect ratio trapping (ART) hetero-epitaxy has been used to mechanically trap a III-V seed on the Si substrate or the SiO<sub>2</sub> BOX in the SOI and grow locally the remaining layer structure [37], [52], [53], [54], [55]. ART eliminates the dislocations due by lattice mismatch between Si and III-V by selective growth of the III-V in high aspect ratio holes or trenches. The ART technique is suitable for integrating Ge or III-V devices with CMOS back-end process, it provides low thermal budget and can be applied to large wafers. However, the approach still requires a strategy to efficiently couple the light to the SOI. Moreover the III-V device fabrication on the SOI shows reliability issues [55], raises the complexity of the process and the risk of contamination of the CMOS.

**Figure 2.5**: Schematic of the aspect ratio trapping hetero-epitaxy process for creating a III-V laser epitaxial structure in pre-fabricated trenches on the SOI. [56].

## 2.1.4 Heterogeneously integrated laser

A III-V die can be heterogeneously integrated to a desired location on the SOI-PIC for creating a silicon optical amplifier (SOA) or a laser. The III-V amplification cavity is usually arranged parallel to the plane of the SOI

waveguiding layer and the light coupling strategy chosen determines the final layout of the integrated device. Among the main heterogeneous lasers developed it is possible to classify them as evanescent lasers, laser coupled through gratings and edge-coupled laser. For each of these devices different layout of integration can be applied and by including components such as mode size converters, inverted tapers or a combination of the two.

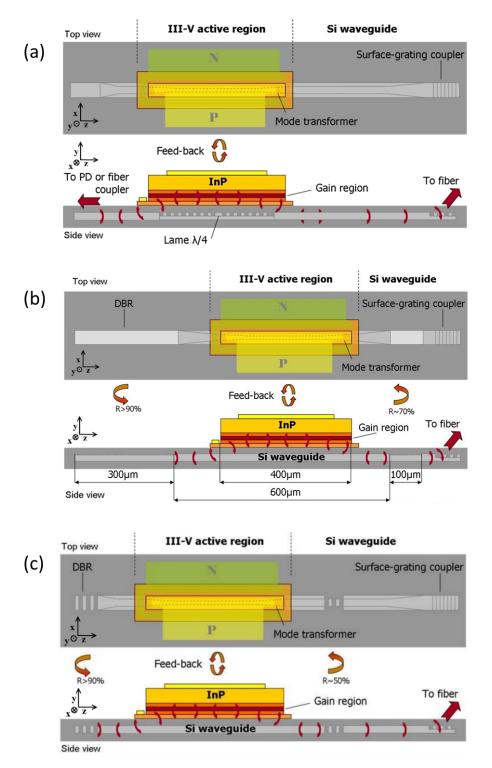

#### **Evanescent lasers**

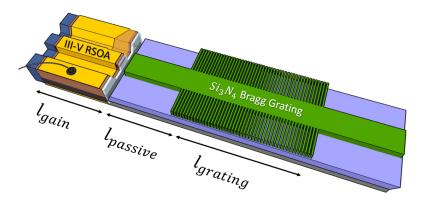

An evanescent laser is obtained by integrating a III-V waveguide on top of an SOI waveguide and by evanescent-coupling the light through inverted tapers that can be defined on the III-V, on the SOI or on both of them. The footprint of the device changes accordingly to the configuration used. The laser is usually hybrid, with the two grating reflectors defined on the SOI waveguide at the nano-scale that allow tuning the reflectivity and act as filters. Micro-ring reflectors can be used alternatively. The evanescent laser denomination differs according to the mirrors configuration adopted, the main layout developed are the distributed feedback (DFB) laser, the distributed bragg reflector (DBR) laser, the Fabry-Perot (FP) laser and the micro-ring-based laser. In the DFB configuration two shallow etched gratings separated by a  $\lambda/4$  long section are defined on the SOI under the III-V die and interact with the evanescent part of the mode resonating inside the active region of the III-V. Inverted tapers are defined at the edges of the III-V die and on the SOI (or only on the SOI) to allow the light transfer from the SOI to the III-V and vice versa [Fig. 2.6 (a)] [57]. In the DBR configuration [Fig. 2.6 (b)], shallow etch gratings are defined on the SOI before and after the SOA, the evanescent-coupling of the light between the SOI and the III-V-SOA is provided by a double inverted taper structure [58], [16], [59]. A FP laser configuration can be achieved by using the same layout of the DBR except that the gratings are created by deep etching into the SOI. In this arrangement every grating acts as a facet with characteristic effective reflectivity and as a wavelength filter [Fig. 2.6 (c)] [60], [61]. Micro-ring reflectors are often employed in tunable lasers and can be defined on the SOI with different sizes that work as filters and reflectors for a particular mode of the laser [62], [63]. The evanescent coupling has been exploited more recently to couple the light of III-V devices heterogeneously integrated to the SOI by *µ*TP [64], [65].

**Figure 2.6**: Schematic top view and longitudinal cross section for three different laser configurations developed by Leti (France). The light is evanescent-coupled between the III-V and the SOI by tapers. (a) A DFB laser is achieved by creating a DFB grating on the SOI, under the III-V [16]. (b) Two shallow etch DBR gratings defined on the SOI before and after the III-V section act as mirrors and wavelength selectors providing a DBR laser configuration [58]. (c) two deeply etched gratings provide a FP laser [60].

#### **Edge-coupled** laser

The edge-coupling configuration can be applied to heterogeneously integrate III-V lasers to a desired location on the SOI platform. A demonstration was given by Roelkens et al. [66], [67]. A III-V die is attached to the SOI with an intermediate benzocyclobutene (BCB) adhesive layer by using the die to wafer bonding technique (see section 2.2.1). A ridge waveguide and two dry-etched facets defined post integration create a Fabry-Perot resonating cavity on the III-V, next a mode size matched polymer MSC is butt-coupled to the ridge waveguide while being positioned on top of an inverted taper defined at the end of the SOI. The light is coupled from the polymer to the SOI by evanescent coupling. The optical mode in the III-V has to be optically insulated, this sets the height of the active region to the SOI and it makes challenging to match the mode to the polymer MSC. As we will see in the fourth chapter, devices integrated on the SOI show reduced thermal sink, especially if bonded with an intermediate thermally insulating layer. The post-integration fabrication of the ridge waveguide allows precise alignment to the SOI, on the other side the alignment of pre-fabricated III-V devices by using wafer bonding can be challenging. Other lasers edge coupled to a polymer waveguide section have been integrated on chip with a similar approach by Tseng et al. [29].

Another example of device on-chip edge-coupled to the SOI waveguide has been reported by Skorpios Technologies, III-V dies were integrated through an intermediate metal layer inside recesses on the SOI and have been edge coupled to the SOI to create lasers [68], [69]. The approach involves a >10  $\mu$ m spacing between the emitting facet on the III-V and the SOI. This requires re-constructing the buried oxide layer in the gap and building an amorphous silicon waveguide with identical cross section to that of the crystalline silicon waveguide.

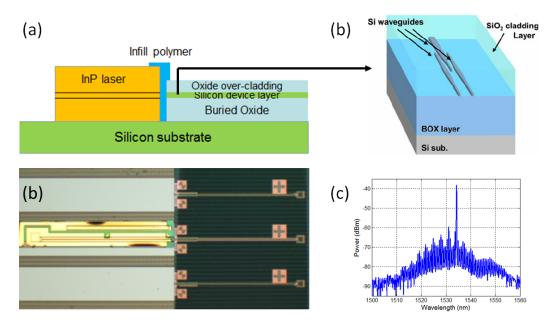

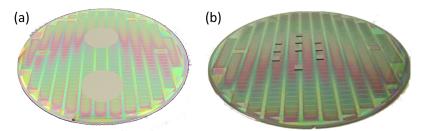

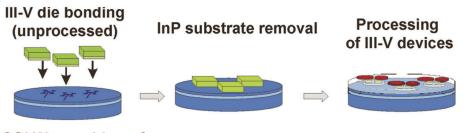

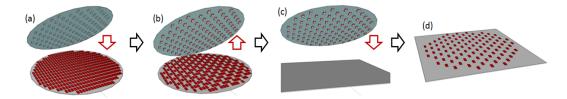

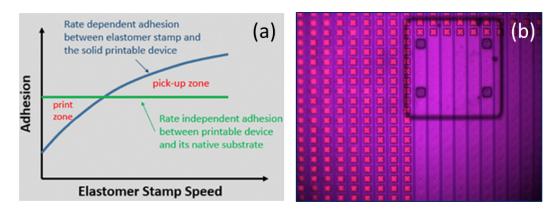

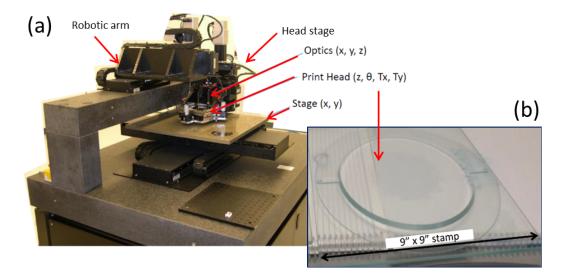

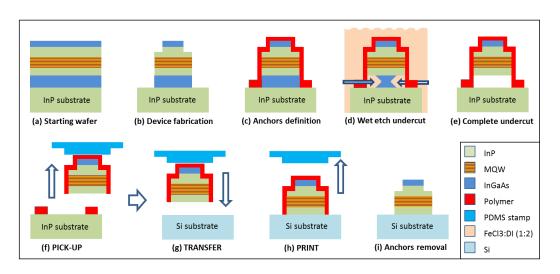

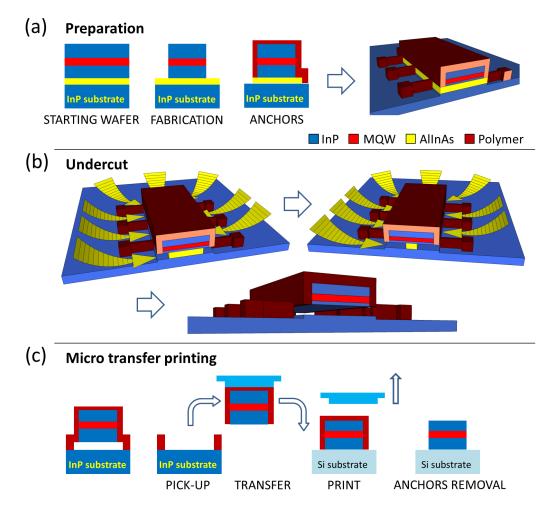

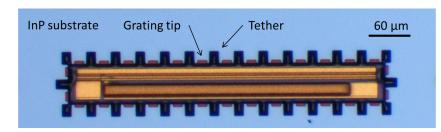

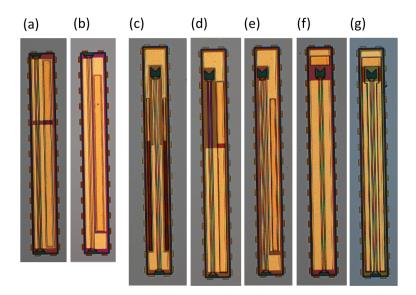

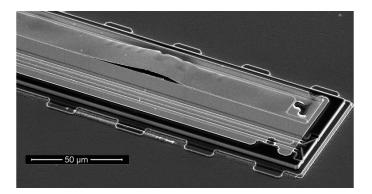

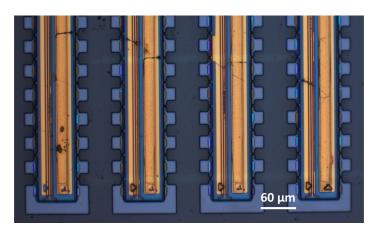

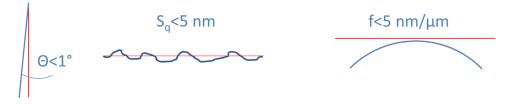

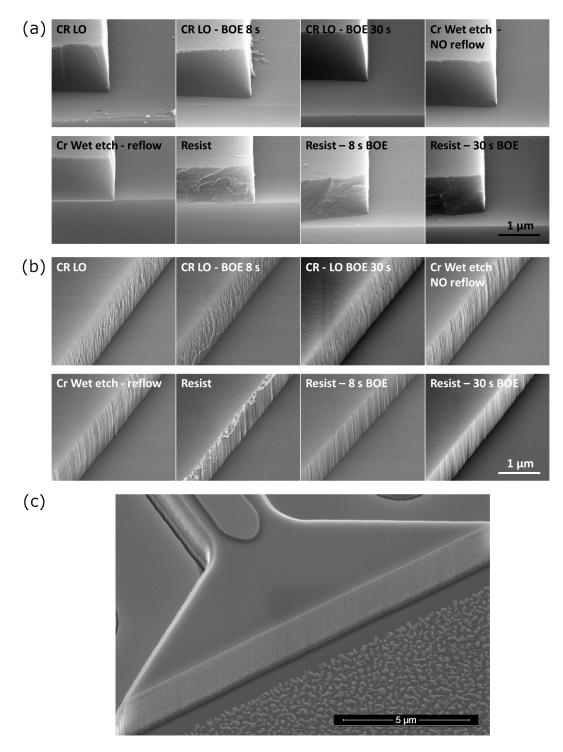

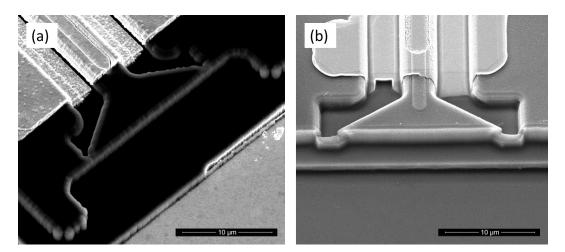

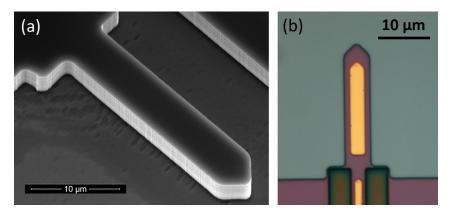

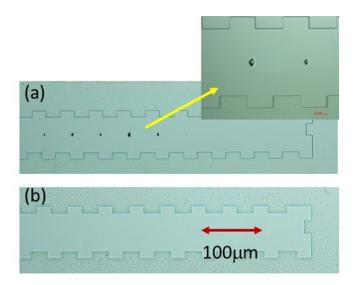

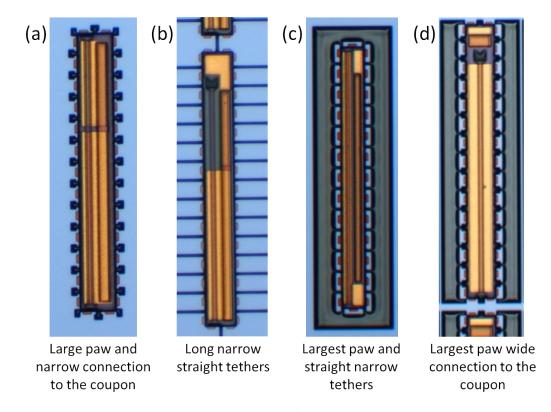

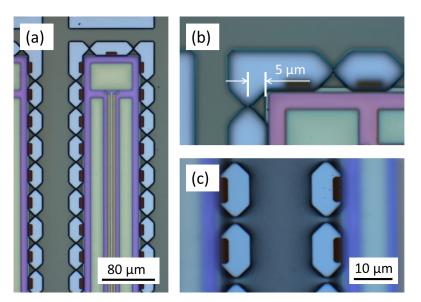

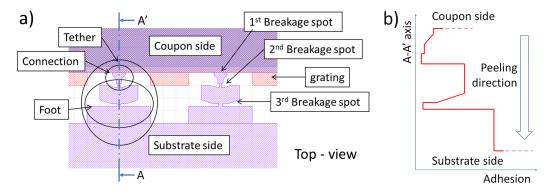

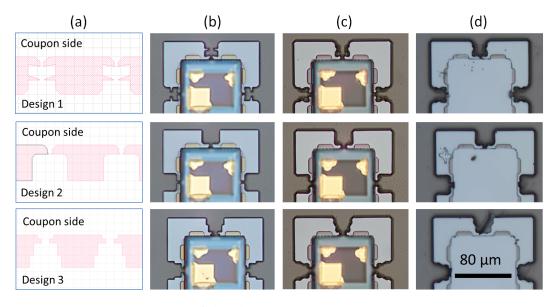

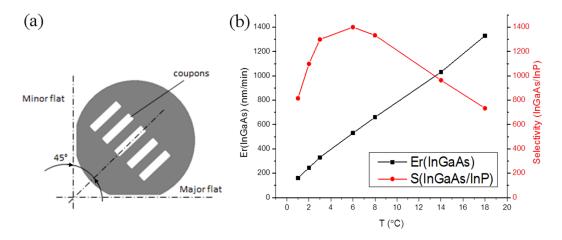

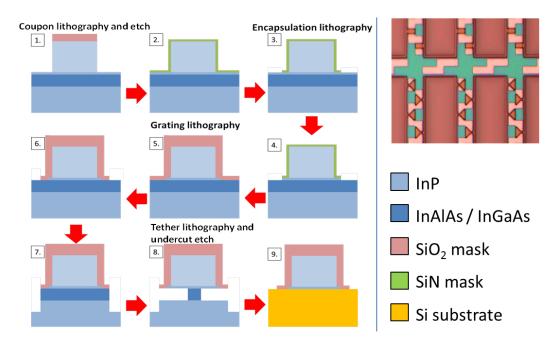

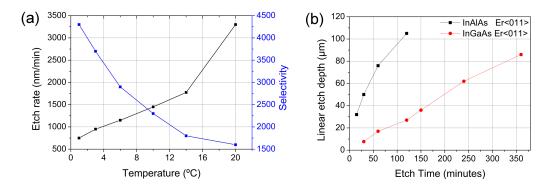

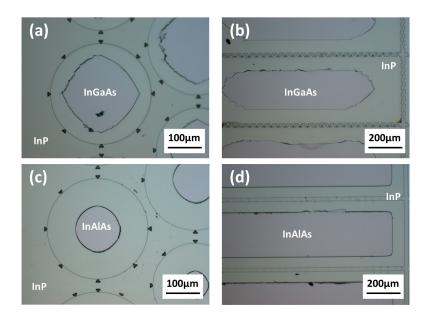

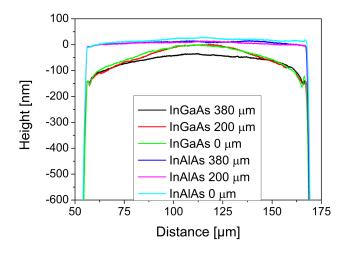

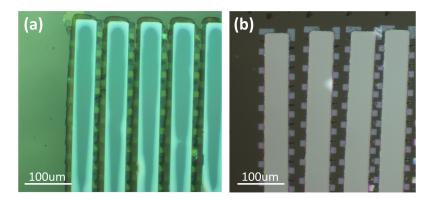

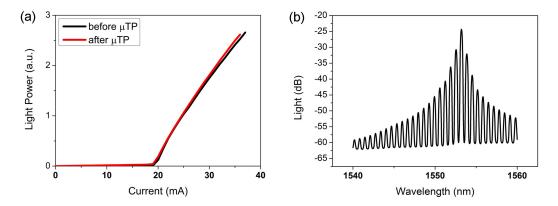

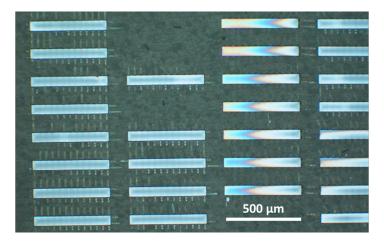

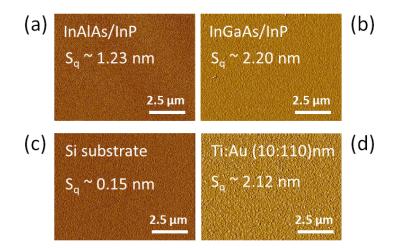

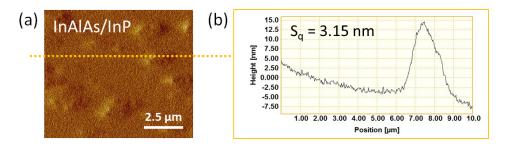

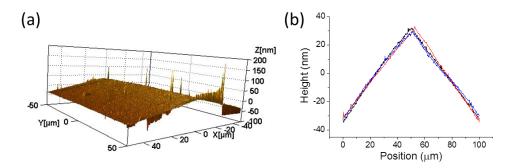

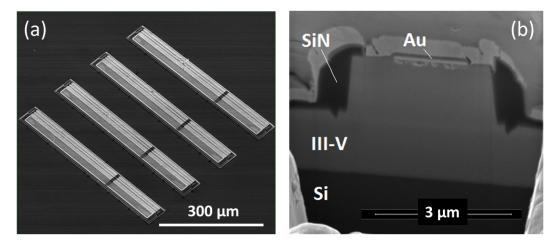

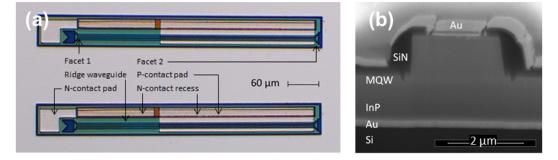

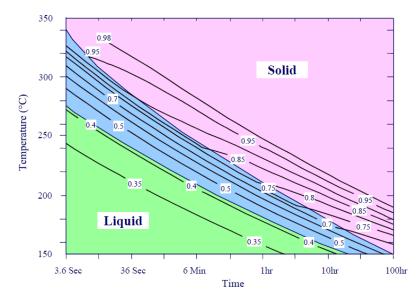

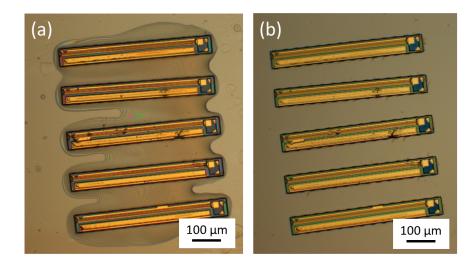

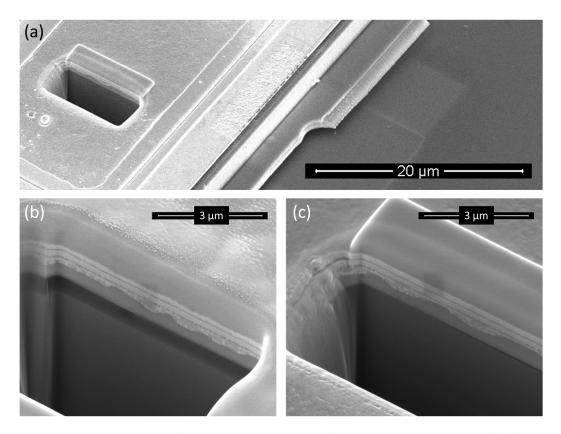

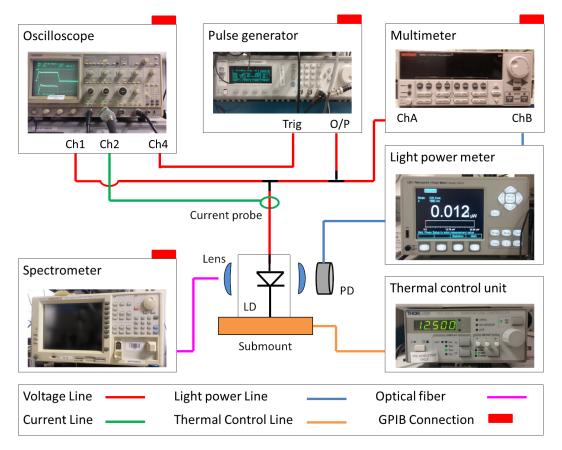

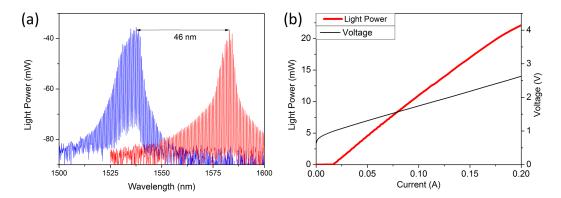

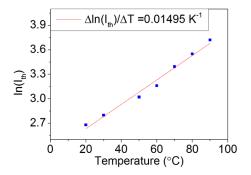

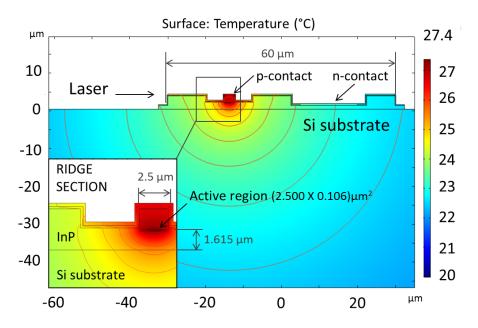

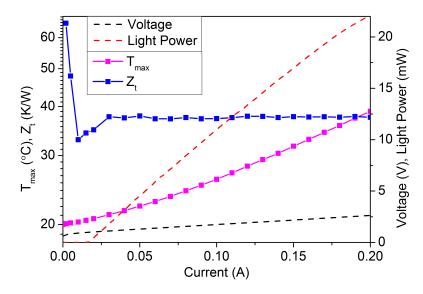

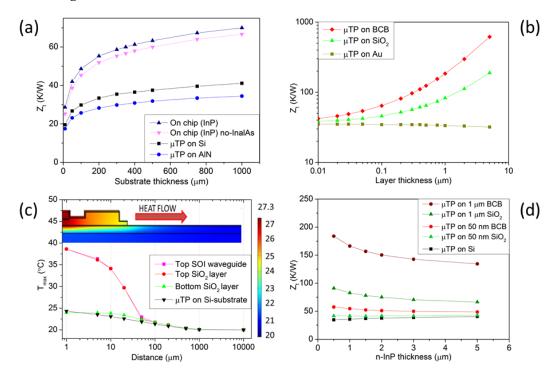

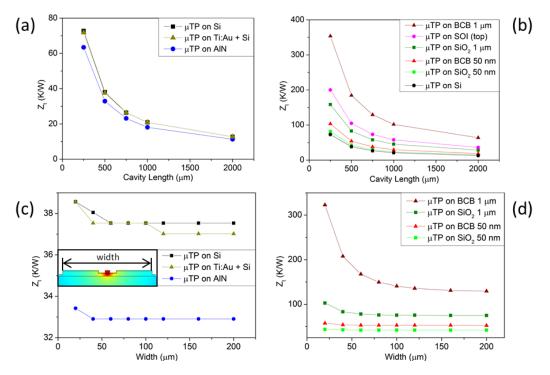

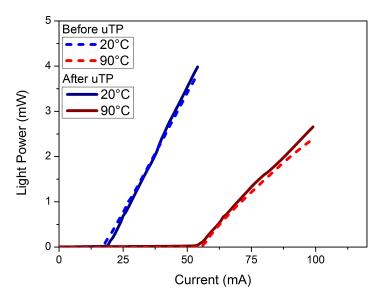

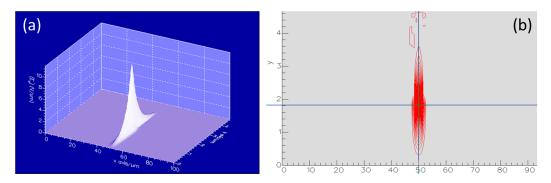

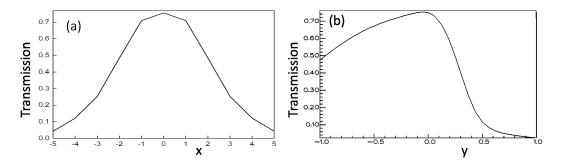

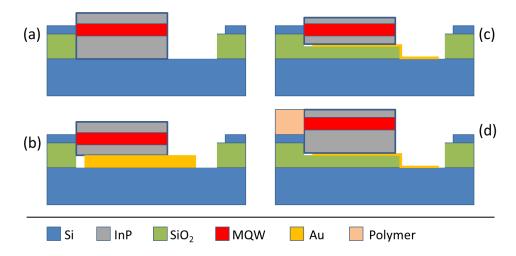

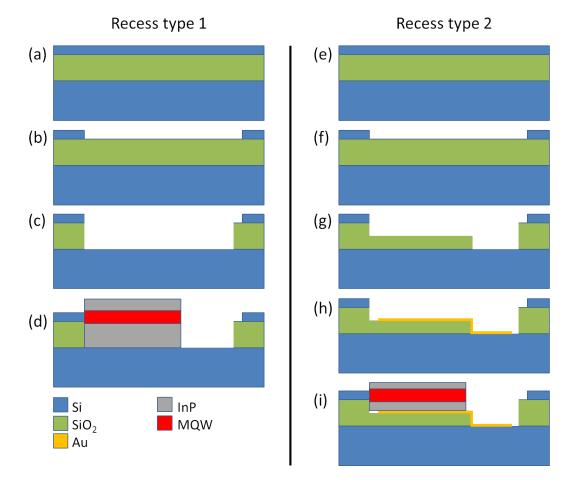

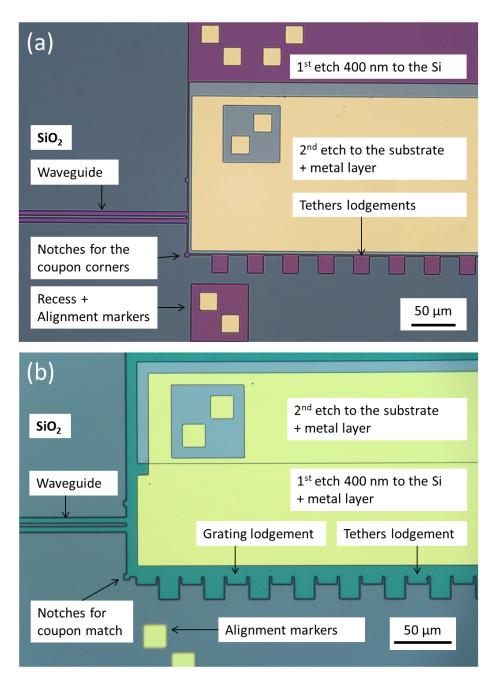

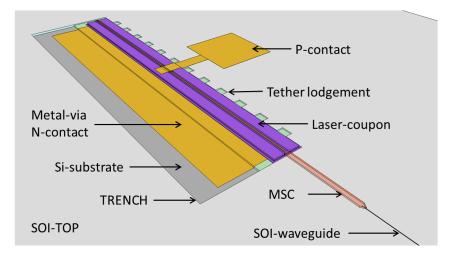

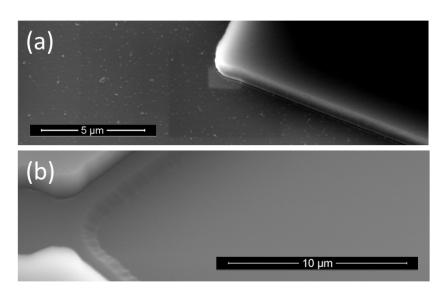

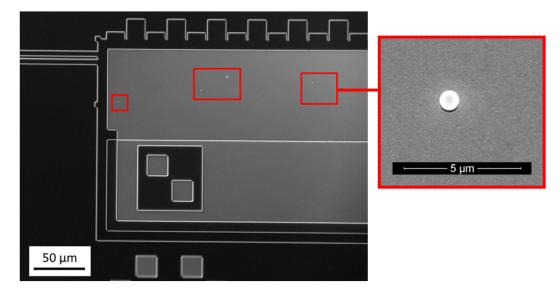

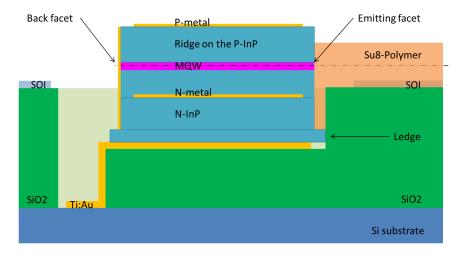

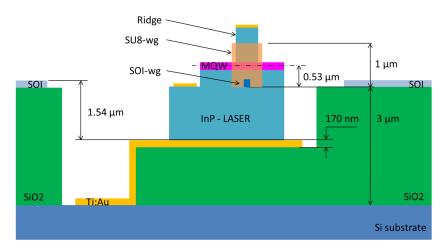

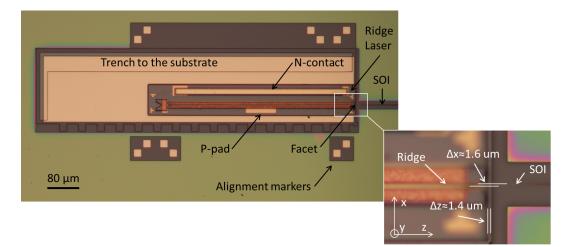

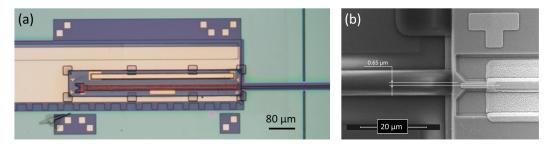

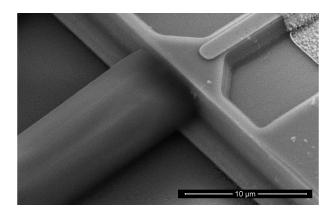

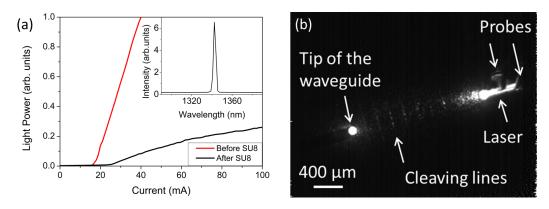

The strategies developed in this thesis for the heterogeneous integration of InP components to silicon photonics by using micro transfer printing technology enabled new architectures, parallel integration and precise alignment of the components involved [70]. InP Fabry-Perot laser coupons of calibrated thickness have been integrated by  $\mu$ TP inside recesses fabricate on a SOI wafer and edge-coupled to a trident MSC defined on the SOI [Fig. 2.7(a)], [71], [72]. The trident is made by two double tapers coupled to a taper defined at one end of the SOI [Fig. 2.7(b)] and can be defined during the SOI processing. The epitaxial structure of the lasers in ref. [71] provided large spot size (LSS) lasers with a mode enlarged along the vertical axis compared to standard InP lasers, the cross section of the laser mode was simulated (with FIMMWAVE, by Photon Design [73]) of  $5.5 \times 2.7 \ \mu m^2$  at  $1/e^2$ . The LSS lasers offer more relaxed tolerances on the vertical alignment in an edge-coupling configuration. The actual trident was mode matched to the LSS laser and squeezes the light in the SOI of mode size  $0.5 \times 0.3 \ \mu m^2$ . The devices were printed directly on the Si substrate inside the recesses while a n-InP cladding layer of calibrated thickness provided vertical alignment of the laser waveguide to the MSC. The layout developed involved the creation of recesses. The main technological issues related to the creation and integration of a III-V die in a recess on the SOI are discussed more in detail in chapter 5 (sections 5.2 and 5.3). Figure 2.7(c) shows the laser integrated and the emission spectrum [Fig. 2.7(d)] detected through an out-couplinggrating and an optical fiber.