| Title                       | Inversion in the In0.53Ga0.47As metal-oxide-semiconductor system: Impact of the In0.53Ga0.47As doping concentration                                                                                                                                                                    |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | O'Connor, Éamon;Cherkaoui, Karim;Monaghan, Scott;Sheehan,<br>Brendan;Povey, Ian M.;Hurley, Paul K.                                                                                                                                                                                     |

| Publication date            | 2017-01-19                                                                                                                                                                                                                                                                             |

| Original Citation           | O'Connor, É., Cherkaoui, K., Monaghan, S., Sheehan, B., Povey, I. M. and Hurley, P. K. (2017) 'Inversion in the In0.53Ga0.47As metal-oxide-semiconductor system: Impact of the In0.53Ga0.47As doping concentration', Applied Physics Letters, 110, 032902 (5pp). doi:10.1063/1.4973971 |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                |

| Link to publisher's version | 10.1063/1.4973971                                                                                                                                                                                                                                                                      |

| Rights                      | © 2017, the Authors. Reproduced with the permission of AIP Publishing from Applied Physics Letters, 110, 032902 (5pp). doi:10.1063/1.4973971 - https://publishing.aip.org/authors/copyright-reuse                                                                                      |

| Download date               | 2024-05-14 07:49:52                                                                                                                                                                                                                                                                    |

| Item downloaded from        | https://hdl.handle.net/10468/4021                                                                                                                                                                                                                                                      |

## Inversion in the $In_{0.53}Ga_{0.47}As$ metal-oxide-semiconductor system: Impact of the $In_{0.53}Ga_{0.47}As$ doping concentration

É. O'Connor, K. Cherkaoui, S. Monaghan, B. Sheehan, I. M. Povey, and P. K. Hurley

Citation: Appl. Phys. Lett. 110, 032902 (2017); doi: 10.1063/1.4973971

View online: http://dx.doi.org/10.1063/1.4973971

View Table of Contents: http://aip.scitation.org/toc/apl/110/3

Published by the American Institute of Physics

## Articles you may be interested in

Fabrication and characterization of Pt/Al<sub>2</sub>O<sub>3</sub>/Y<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs with low interface trap density Applied Physics Letters **110**, 043501 (2017); 10.1063/1.4974893

Yttrium passivation of defects in GeO<sub>2</sub> and GeO<sub>2</sub>/Ge interfaces

Applied Physics Letters 110, 032903 (2017); 10.1063/1.4974291

Gate-all-around junctionless silicon transistors with atomically thin nanosheet channel (0.65 nm) and record subthreshold slope (43 mV/dec)

Applied Physics Letters 110, 032101 (2017); 10.1063/1.4974255

On the mechanism of highly efficient p-type conduction of Mg-doped ultra-wide-bandgap AlN nanostructures Applied Physics Letters **110**, 032102 (2017); 10.1063/1.4973999

Tunneling field effect transistor integrated with black phosphorus-MoS<sub>2</sub> junction and ion gel dielectric Applied Physics Letters **110**, 033103 (2017); 10.1063/1.4974303

Thickness dependent thermal conductivity of gallium nitride Applied Physics Letters **110**, 031903 (2017); 10.1063/1.4974321

## Inversion in the In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor system: Impact of the In<sub>0.53</sub>Ga<sub>0.47</sub>As doping concentration

É. O'Connor, <sup>1,a)</sup> K. Cherkaoui, <sup>1</sup> S. Monaghan, <sup>1</sup> B. Sheehan, <sup>1</sup> I. M. Povey, <sup>1</sup> and P. K. Hurley <sup>1,2</sup>

(Received 10 September 2016; accepted 29 December 2016; published online 19 January 2017)

In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor (MOS) capacitors with an Al<sub>2</sub>O<sub>3</sub> gate oxide and a range of n and p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial concentrations were examined. Multi-frequency capacitance-voltage and conductance-voltage characterization exhibited minority carrier responses consistent with surface inversion. The measured minimum capacitance at high frequency (1 MHz) was in excellent agreement with the theoretical minimum capacitance calculated assuming an inverted surface. Minority carrier generation lifetimes,  $\tau_g$ , extracted from experimentally measured transition frequencies,  $\omega_m$ , using physics based a.c. simulations, demonstrated a reduction in  $\tau_g$  with increasing epitaxial doping concentration. The frequency scaled conductance,  $G/\omega$ , in strong inversion allowed the estimation of accurate  $C_{ox}$  values for these MOS devices. *Published by AIP Publishing*. [http://dx.doi.org/10.1063/1.4973971]

Historically, a variety of issues have impeded progress for the incorporation of high-k dielectrics on III-V semiconductors for future CMOS applications. 1,2 Not least among these is the complexity of the high-k/III-V interface, which typically has a high density of electrically active defects.<sup>3–5</sup> Interface state density ( $D_{it}$ ) values in excess of  $10^{12}$  cm<sup>-2</sup> are commonly reported, which is almost two orders of magnitude higher than that achievable in SiO<sub>2</sub>/Si systems. The high-k/III-V metal-oxide-semiconductor (MOS) system also exhibits electrically active defects in the interfacial transition region between the high-k oxide and the III-V semiconductor, "border traps," which can cause dispersion in the accumulation capacitance with a.c. signal frequency and also manifest as hysteresis.<sup>6,7</sup> Passivation of defects to acceptable levels has not proved to be trivial and also renders reliable characterization and interpretation of device behavior difficult. Such a high density of interface states can restrict Fermi level movement across the semiconductor bandgap and, in the case of In<sub>0.53</sub>Ga<sub>0.47</sub>As, prevent surface inversion at the semiconductor/oxide interface. To date, only a limited number of studies in the literature have demonstrated sufficient reduction in Dit to allow the observation of true surface inversion and an associated minority carrier behavior, in the capacitance-voltage (CV) response of MOS capacitors on either *n*-type or *p*-type  $In_{0.53}Ga_{0.47}As$ .

In recent work, we reported on a study of the minority carrier response of both *n*-type and *p*-type In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor (MOS) devices formed using an optimized 10% ammonium sulfide ((NH<sub>4</sub>)<sub>2</sub>S) treatment. Dit was sufficiently reduced such that a clear minority carrier response associated with inversion of the oxide/In<sub>0.53</sub>Ga<sub>0.47</sub>As surface was observed for both *n*-type and *p*-type devices. In order to extend this work, in this letter we present a method to confirm true surface inversion in Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS

capacitors based on the use of a wide range of n and p-type doping concentrations, ranging over two orders of magnitude from  $\sim 1 \times 10^{16}$  cm<sup>-3</sup> to  $\sim 2 \times 10^{18}$  cm<sup>-3</sup>. This is in order to examine if the measured minimum capacitance scales correctly with the In<sub>0.53</sub>Ga<sub>0.47</sub>As doping concentration based on a maximum depletion width calculated assuming that the surface is inverted. This follows an approach reported by Callegari et al. for GaAs MOS devices. 13 In addition, the effect of the doping concentration on the minority carrier generation lifetime in the  $In_{0.53}Ga_{0.47}As$ ,  $\tau_g$ , is examined. Finally, for these variable doping series samples, we utilize a recently reported method<sup>14</sup> to accurately estimate oxide capacitance, Cox, where it was found that the peak magnitude of the angular frequency scaled conductance,  $G/\omega$ , was equal to  $C_{ox}^{2}$  $2(C_{ox} + C_{D})$ , in strong inversion, where  $C_{D}$  is the semiconductor depletion capacitance.

The details of the In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial layers used in this work are as follows. First, using p-doped (Zn at  $\sim 2 \times 10^{18} \text{ cm}^{-3}$ ) InP(100) as a starting substrate,  $\sim 2 \,\mu\text{m}$ p-In<sub>0.53</sub>Ga<sub>0.47</sub>As layers were grown by MOVPE with the following dopant (Zn) concentrations (cm<sup>-3</sup>):  $1.4 \times 10^{16}$ ,  $3.3 \times 10^{16}$ ,  $1.8 \times 10^{17}$ ,  $2.7 \times 10^{17}$ , and  $1.2 \times 10^{18}$ . Using *n*-doped (S at  $\sim 2 \times 10^{18}$  cm<sup>-3</sup>) InP(100) as a starting substrate,  $\sim 2 \,\mu \text{m}$  n-In<sub>0.53</sub>Ga<sub>0.47</sub>As layers were grown by MOVPE with the following dopant (Si) concentrations  $(cm^{-3})$ :  $7.8 \times 10^{15}$ ,  $3.0 \times 10^{16}$ ,  $2.0 \times 10^{17}$ ,  $6.0 \times 10^{17}$ , and  $2.0 \times 10^{18}$ . These doping concentrations were determined by Electrochemical Capacitance-Voltage (ECV) Profiling. In<sub>0.53</sub>Ga<sub>0.47</sub>As surfaces were initially rinsed for 1 min each in acetone, methanol, and isopropanol, immediately followed by immersion for 20 min at room temperature in (NH<sub>4</sub>)<sub>2</sub>S with a concentration of 10% in deionised H<sub>2</sub>O. These optimized passivation parameters were determined from previous physical and electrical studies, 15,16 and subsequently also reported for MOSFET devices. 17 The Al<sub>2</sub>O<sub>3</sub> layers were grown by atomic layer deposition (ALD) at 300 °C (Cambridge NanoTech, Fiji F200LLC), using alternating

<sup>&</sup>lt;sup>1</sup>Tyndall National Institute, University College Cork, Cork, Ireland <sup>2</sup>Department of Chemistry, University College Cork, Cork, Ireland

a) Author to whom correspondence should be addressed. Electronic mail: eamonoconnor33@gmail.com

pulses of  $(Al(CH_3)_3)$  and  $H_2O$ . TEM indicated an  $Al_2O_3$  thickness of  $\sim$ 7 nm for the growth run on p-type samples and a thickness of  $\sim$ 5 nm for the separate ALD growth run on n-type samples. Finally, gate contacts  $\sim$ 160 nm thick were formed by e-beam evaporation of Ni (70 nm), and Au (90 nm), using a lift-off process. Electrical measurements were recorded using an Agilent E4980A and were performed on-wafer in a microchamber probe station (Cascade, Summit 12971B) in a dry air, dark environment (dew point  $\leq$ 203 K).

For an MOS device in strong inversion, the depletion layer width reaches a maximum value, which is related to the doping concentration and the relative permittivity of the semiconductor. The equation governing the maximum depletion width, included here for completeness, is given in Equation (1) below where:  $\varepsilon_0$  is the permittivity of free space;  $\varepsilon_s$  is the semiconductor permittivity; k is Boltzmann's constant;  $n_i$  is the intrinsic semiconductor carrier concentration; and  $N_D$  is the semiconductor doping concentration. The semiconductor doping concentration.

$$x_{d\_max} = \sqrt{\frac{4\varepsilon_0 \varepsilon_S kT \ln\left(\frac{N_D}{n_i}\right)}{q^2 N_D}}.$$

(1)

From this equation, as the semiconductor doping level is increased this maximum depletion width is reduced, which in turn is reflected in an increase in the depletion capacitance (C<sub>D</sub>) of the semiconductor in inversion. The theoretical minimum capacitance (Cmin-theor) of a gate stack is the series combination of CD and Cox. It is thus expected that for an inverted surface, the minimum measured gate stack capacitance (C<sub>min-meas</sub>) will increase as a function of doping concentration. Utilizing different doping concentrations C<sub>min-meas</sub> at high frequency can be compared with C<sub>min-theor</sub> as calculated by assuming that the semiconductor surface is inverted. In the case of devices where the D<sub>it</sub> is high, Fermi level movement will be restricted such that it will not be possible to reach the minimum capacitance. Where substrates with variable doping levels are available, this provides a means to investigate if the oxide-semiconductor interface state concentration has been reduced to levels which allow surface inversion to be achieved. This approach was used previously for GaAs MOS structures to investigate improvements in the CV characteristics of plasma deposited Ga oxide films on GaAs substrates. 13

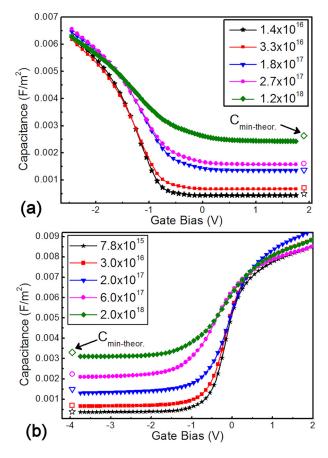

Figure 1(a) plots the 1 MHz CV responses for the *p*-type In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS devices with varying dopant concentrations. The 1 MHz curves were chosen in order to minimize any contribution of interface states to the measured CV response. Open symbols represent C<sub>min-theor</sub> for each doping concentration and calculated using a C<sub>ox</sub> value in this case of 0.0075 F/m<sup>2</sup>, taken from the measured capacitance at low frequency (20 Hz), and at a gate bias of 1.75 V. C<sub>ox</sub> was chosen at 20 Hz as this was the lowest frequency that could be measured with the instrument used, and previous work has shown that the CV at 20 Hz provides a very close approximation to the C<sub>ox</sub> obtained using a quasi-static CV.<sup>20</sup> It is clear that the measured minimum capacitance increases as expected with doping and that there is excellent agreement between the measured and theoretical minimum capacitance

FIG. 1. 1 MHz CV responses at 295 K for (a) Au/Ni/7 nm-Al $_2$ O $_3$ / $_p$ -In $_{0.53}$ Ga $_{0.47}$ As and (b) Au/Ni/5 nm-Al $_2$ O $_3$ / $_n$ -In $_{0.53}$ Ga $_{0.47}$ As MOS devices with dopant concentrations ranging from  $\sim 10^{16}$  cm $^{-3}$  to  $10^{18}$  cm $^{-3}$ . The theoretical values (open symbols) were estimated using  $C_{\rm ox}$  values of 0.0075 F/m $^2$  and 0.0093 F/m $^2$  for the p- and n-type devices, respectively.

values, providing strong evidence that the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface is inverted. This is notable considering that the change in doping concentration is over two orders of magnitude. It is also significant that the measured CV curves go flat with increasing positive gate bias, which is further support that Dit has been reduced to an extent to allow sufficient Fermi level movement that permits surface inversion. Figure 1(b) shows the 1 MHz CV responses for the *n*-type In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS devices with changing epitaxial layer dopant concentrations. As in the case of the p-type samples, there is excellent agreement between the measured (closed symbols) and theoretical (open symbols) capacitance values. The theoretical minimum capacitance, C<sub>min-theor</sub>, for each doping concentration was calculated using a Cox value in this case of 0.0093 F/m<sup>2</sup>, taken from the capacitance measured at low frequency (20 Hz), and at a gate bias of -3.75 V. When plotting the measured capacitance versus the theoretical value, (@1.75  $V_{gate}$  for p-type and at @-3.75  $V_{gate}$  for n-type), Figure 2 demonstrates that there is close to a linear relationship in both cases. The inversion of the *n*-type  $In_{0.53}Ga_{0.47}As$ MOS is of particular note, as for the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system the interface state density is generally reported to rise steeply towards the valence band edge, 21,22 and the ability to invert the Al<sub>2</sub>O<sub>3</sub>/n-InGaAs surface indicates that the surface preparation and ALD growth conditions have not only reduced Dit near the mid gap energy but also resulted in D<sub>it</sub> reduction from mid-gap to the valence band edge.

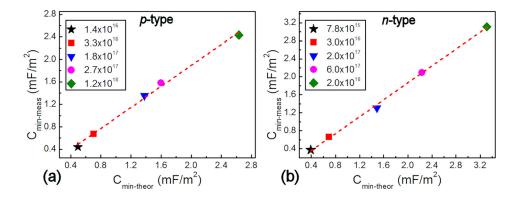

FIG. 2. Plot of measured versus theoretical minimum capacitance for: (a) different p-type doping concentrations, with the measured values being those at a gate bias of 1.75 V in Fig. 1(a); and (b) different n-type doping concentrations, with the measured values being those at a gate bias of -3.75 V in Figure 1(b).

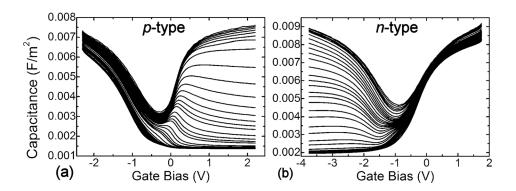

FIG. 3. Multi-frequency CV responses at 295 K of (a) p-type and (b) n-type Au/ Ni/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As, devices, with In<sub>0.53</sub>Ga<sub>0.47</sub>As doping concentrations of  $2.7 \times 10^{17}$  cm<sup>-3</sup> and  $6.0 \times 10^{17}$  cm<sup>-3</sup>, and Al<sub>2</sub>O<sub>3</sub> thicknesses of  $\sim$ 7 nm and 5 nm, respectively. The CV responses with increasing positive gate bias for the p-type devices, and with increasing negative gate bias for the n-type devices, are consistent with the CV behaviour arising from a minority carrier response in inversion.

For all samples, the multi-frequency CV and conductance voltage (GV) responses (20 Hz–1 MHz) also exhibited the characteristic signatures of inversion behavior for  $In_{0.53}Ga_{0.47}As$  MOS devices. As an example illustration, the CVs in Figures 3(a) and 3(b) are plotted for the devices in this study  $(1.8 \times 10^{17}~p$ -type and  $6.0 \times 10^{17}~n$ -type) having doping levels similar to those used in previous reports on inverted  $In_{0.53}Ga_{0.47}As$  MOS devices, in order to show that the behavior is consistent. Space limitations preclude showing the multi-frequency CV for all samples. One of the signatures for an inverted surface is that in strong inversion the measured conductance normalized by frequency,  $G/\omega$ , peaks at the transition frequency,  $\omega_{\rm m}$ . This relationship is observed for all samples in the study (not shown).

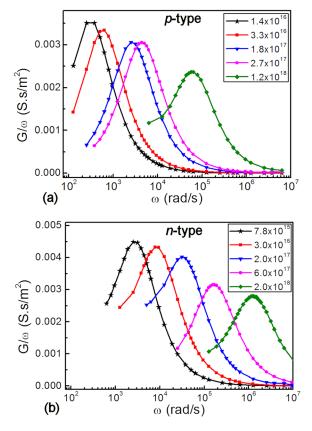

For an inverted surface, the multi-frequency CV and GV responses can also be used to investigate the minority carrier lifetime in the In<sub>0.53</sub>Ga<sub>0.47</sub>As layer and the capacitance of the gate oxide. 14,23 For the case of surface inversion, the transition frequency,  $\omega_{\mathrm{m}}$ , is inversely related to the minority carrier generation lifetime,  $\tau_g$ , in the  $In_{0.53}Ga_{0.47}As$ , and the peak value of  $G/\omega$  is related to the oxide capacitance,  $C_{ox}$ . Considering first the case of the minority carrier lifetime, the  $G/\omega$  recorded at a gate bias of 1.75  $V_{gate}$  for p-type and at  $-3.75 \text{ V}_{\text{gate}}$  for *n*-type are plotted in Figure 4. One observation of note over both n and p-type samples in Figure 4 is that the transition frequency at which  $G/\omega$  peaks in inversion increases as the semiconductor doping concentration is increased. Figure 5(a) plots this change for p-type and n-type devices. For a minority carrier supply provided through mid-gap state generation, this behavior is expected as the minority carrier lifetime  $\tau_g$  values generally decrease with increasing doping concentration. These observations are

FIG. 4.  $G/\omega$  plotted versus  $\omega$  in strong inversion for (a) Au/Ni/7 nm Al<sub>2</sub>O<sub>3</sub>/p-In<sub>0.53</sub>Ga<sub>0.47</sub>As and (b) Au/Ni/5 nm Al<sub>2</sub>O<sub>3</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As devices. The values of  $G/\omega$  were taken at a gate bias of 1.75 V for p-In<sub>0.53</sub>Ga<sub>0.47</sub>As devices and at a gate bias of -3.75 V for n-In<sub>0.53</sub>Ga<sub>0.47</sub>As devices, utilizing the multi-frequency GV data. Note, the frequency scaled conductance,  $G/\omega$ , can also be expressed in units of F/m<sup>2</sup>.

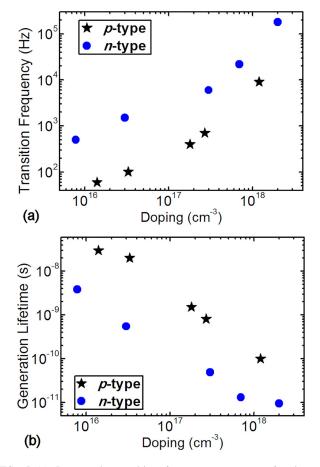

FIG. 5. (a) Increase in transition frequency,  $\omega_{\rm m}$ , as a function of In<sub>0.53</sub>Ga<sub>0.47</sub>As doping concentration for *p*-type (star) and *n*-type (circle) MOS devices. (b) Decrease in the minority carrier generation lifetime,  $\tau_{\rm g}$ , with increasing doping for *p*-type (star) and *n*-type (circle) MOS devices.

therefore consistent with previous work on similar device structures indicating that at room temperature the dominant mechanism for the supply of minority carriers is a generation-recombination process through mid-gap bulk defects in the  $In_{0.53}Ga_{0.47}As$  depletion region. These results are not consistent with a border trap contribution to the observed minority carrier response. The results in Figure 5(a) also indicate that at similar doping levels the transition frequency for the n-type samples is generally one order of magnitude higher than for the corresponding p-type samples.

A Synopsis Sentaurus device simulator was employed to perform physics based ac simulations, where the value of  $\tau_{\sigma}$  in the simulations is altered to achieve a match between the transition frequency of the physics based ac simulations and the experimental transition frequency values in Figure 5(a). The resulting  $\tau_g$  are plotted in Figure 5(b) demonstrating a marked decrease with increasing doping concentration for both n and p-type devices. The fact that higher generation lifetimes at similar doping levels are observed for p-type compared to *n*-type samples is possibly related to inequalities in the bulk In<sub>0.53</sub>Ga<sub>0.47</sub>As properties arising from differences in the epitaxial growth conditions for the p and n-type  $In_{0.53}Ga_{0.47}As$ layers. However, further analysis of this is beyond the scope of the current study. Previous work also demonstrated that it is possible to passivate some of the bulk mid-gap traps in In<sub>0.53</sub>Ga<sub>0.47</sub>As through H<sub>2</sub>/N<sub>2</sub> annealing, as indicated by an increase in  $\tau_{\rm g}$ .<sup>23,26</sup> It is noted that all samples in each doping series in this work were processed simultaneously with the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface seeing identical conditions and therefore should have comparable D<sub>it</sub>. Interface states do not contribute to the observed minority carrier response because in strong inversion interface states are either full (*p*-type) or empty (*n*-type). Therefore, changes in surface potential arising from modulation of the small signal a.c. voltage applied to the gate will not significantly affect their occupancy.<sup>23</sup>

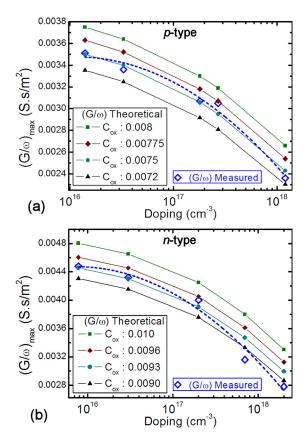

Cox is an important parameter in device analysis, for example, with regard to Dit extraction. These doping series samples can also be utilized with regard to the C<sub>ox</sub> extraction method we published recently, <sup>14</sup> where it was demonstrated that in strong inversion the maximum value of  $G/\omega$  and also  $-\omega \cdot dC/d\omega$  at  $\omega_{\rm m}$  is equal to  $C_{\rm ox}^2/2(C_{\rm ox}+C_{\rm D})$ . In the current study, the oxide thickness is fixed while the doping concentration is varied. Therefore, for a given Cox, as the doping concentration increases, CD will increase and it would be expected using the above relationship that the value of  $G/\omega$ would decrease. Figure 6 plots the expected theoretical values of  $G/\omega$  versus doping, for various values of  $C_{ox}$ . The measured  $G/\omega$  values are plotted as open symbols, with the dashed blue lines representing an approximate fitting to those points in each case. It is seen that the experimental values follow the trend of the theoretical values quite closely. In Figure 6(a), it is evident that the curve calculated using  $C_{ox}$

FIG. 6. Peak  $G/\omega$  in inversion as a function of doping concentration for (a) p-type and (b) n-type Au/Ni/Al $_2$ O $_3$ /In $_{0.53}$ Ga $_{0.47}$ As devices. Different  $C_{\rm ox}$  values were used to compute the corresponding theoretical  $G/\omega$  values at each doping level according to the  $(G/\omega)_{\rm max} = C_{\rm ox}^2/2(C_{\rm ox} + C_{\rm D})$  relationship. The measured peak  $G/\omega$  values in strong inversion are plotted as open symbols and fitted with the dashed line. Note, the frequency scaled conductance,  $G/\omega$ , can also be expressed in units of  $F/m^2$ .

of  $0.0075 \, \mathrm{F/m^2}$  is in very good agreement with the experimental  $\mathrm{G/\omega}$  data. In the case of the n-type devices, the  $0.0093 \, \mathrm{F/m^2}$  for  $\mathrm{C_{ox}}$  provides a good approximation over most of the doping range although some deviation is observed in the experimental data for the two highest doping concentrations. These observations are important also in validating the calculations of the theoretical minimum capacitances described earlier with regard to Figures 1 and 2, where the  $\mathrm{C_{ox}}$  values used to extract the theoretical minimum capacitances were  $0.0075 \, \mathrm{F/m^2}$  and  $0.0093 \, \mathrm{F/m^2}$  for p-type and n-type samples, respectively, determined from the measured capacitance at  $20 \, \mathrm{Hz}$ . Therefore, the  $\mathrm{C_{ox}}$  values that provide the best fit in both n and p-type cases in Figure 6 are in agreement with the  $\mathrm{C_{ox}}$  measured at low frequency ( $20 \, \mathrm{Hz}$ ).

In summary, p-type and n-type Au/Ni/Al<sub>2</sub>O<sub>3</sub>/ In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors with semiconductor doping concentrations ranging from  $10^{16} \text{ cm}^{-3}$  to  $10^{18} \text{ cm}^{-3}$  exhibited behaviour consistent with surface inversion. The measured minimum capacitance at 1 MHz scales correctly with the In<sub>0.53</sub>Ga<sub>0.47</sub>As doping concentration based on a maximum depletion width calculated assuming that the surface is inverted, providing evidence that the interface state concentration was reduced to a level which allows inversion of the  $Al_2O_3/In_{0.53}Ga_{0.47}As$  interface for both n and p type doped In<sub>0.53</sub>Ga<sub>0.47</sub>As. The minority carrier generation lifetime in the  $In_{0.53}Ga_{0.47}As$ ,  $\tau_g$ , was found to decrease with increasing doping concentration. Cox values extracted using a method based on the relationship between the capacitance and conductance in strong inversion exhibited excellent agreement with the  $C_{ox}$  measured at low frequency (20 Hz). It is notable that this was illustrated previously using an Al<sub>2</sub>O<sub>3</sub> thickness series on both n and p-type  $In_{0.53}Ga_{0.47}As$  in which case the doping was fixed and C<sub>ox</sub> varied with dielectric thickness,<sup>23</sup> and also that results from physics based a.c. simulations show the relationship to be generally true.<sup>14</sup> Those results, combined with the results of this variable doping study, indicate that the equality of the maximum value of  $G/\omega$  at  $\omega_m$  being equal to  $C_{ox}^{2}/2(C_{ox}+C_{D})$  in inversion is a reliable tool to obtain an accurate estimate of Cox and most significantly that this method can be applied for any MOS system in inversion, regardless of the oxide or semiconductor material.

The authors acknowledge the following colleagues from Tyndall National Institute for their contribution: Dr. Kevin Thomas and Dr. Emanuele Pelucchi for MOVPE growth, Dr. Pat Carolan for TEM analysis, and Dan O'Connell for lithography and gate metallization. The authors acknowledge Dr. Rafael Rios (retired) formerly of Intel Components Research, Oregon, for providing the physics based CV simulations. This work was supported in part by Science Foundation Ireland under the "INVENT" Project No. 09/IN.1/I2633; and in part by the European Commission through the project entitled "Compound Semiconductors for 3D Integration COMPOSE3" under

Grant No. FP7-ICT-2013-11-619325; and the project entitled "Integration of III-V Nanowire Semiconductors for Next Generation High Performance CMOS SOC Technologies, (INSIGHT)" under Grant No. H2020-ICT-2015-688784. É. O'Connor acknowledges the financial support of the European Union funded Marie Curie fellowship "FACIT" (FP7-PEOPLE-2013-IEF 628523).

<sup>1</sup>J. Del Alamo, Nature **479**, 317 (2011).

<sup>2</sup>I. Thayne, S. Bentley, M. Holland, W. Jansen, X. Li, D. Macintyre, S. Thom, B. Shin, J. Ahn, and P. McIntyre, Microelectron. Eng. **88**, 1070 (2011).

<sup>3</sup>C. L. Hinkle, E. M. Vogel, P. D. Ye, and R. M. Wallace, Curr. Opin. Solid State Mater. Sci. 15, 188 (2011).

<sup>4</sup>H.-P. Komsa and A. Pasquarello, Microelectron. Eng. **88**, 1436 (2011).

<sup>5</sup>J. Robertson, Y. Guo, and L. Lin, J. Appl. Phys. 117, 112806 (2015).

<sup>6</sup>H.-P. Chen, Y. Yuan, B. Yu, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, IEEE Trans. Electron Devices **59**(9), 2383 (2012).

<sup>7</sup>J. Lin, Y. Y. Gomeniuk, S. Monaghan, I. M. Povey, K. Cherkaoui, E. O'Connor, M. Power, and P. K. Hurley, J. Appl. Phys. **114**, 144105 (2013).

<sup>8</sup>R. Engel-Herbert, Y. Hwang, and S. Stemmer, J. Appl. Phys. **108**, 124101 (2010).

<sup>9</sup>E. O'Connor, S. Monaghan, K. Cherkaoui, I. M. Povey, and P. K. Hurley, Appl. Phys. Lett. **99**, 212901 (2011).

<sup>10</sup>H. C. Lin, W.-E. Wang, G. Brammertz, M. Meuris, and M. Heyns, Microelectron. Eng. 86, 1554 (2009).

<sup>11</sup>H. D. Trinh, E. Y. Chang, P. W. Wu, Y. Y. Wong, C. T. Chang, Y. F. Hsieh, C. C. Yu, H. Q. Nguyen, Y. C. Lin, K. L. Lin, and M. K. Hudait, Appl. Phys. Lett. **97**, 042903 (2010).

<sup>12</sup>T. D. Lin, Y. H. Chang, C. A. Lin, M. L. Huang, W. C. Lee, J. Kwo, and M. Hong, Appl. Phys. Lett. **100**, 172110 (2012).

<sup>13</sup>A. Callegari, P. D. Hoh, D. A. Buchanan, and D. Lacey, Appl. Phys Lett. 54, 332 (1989).

<sup>14</sup>S. Monaghan, É. O'Connor, R. Rios, F. Ferdousi, L. Floyd, E. Ryan, K. Cherkaoui, I. M. Povey, K. J. Kuhn, and P. K. Hurley, IEEE Trans. Electron Devices 61, 4176 (2014).

<sup>15</sup>É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, J. Appl. Phys. 109, 024101 (2011).

<sup>16</sup>B. Brennan, M. Milojevic, C. L. Hinkle, F. S. Aguirre-Tostado, G. Hughes, and R. M. Wallace, Appl. Surf. Sci. 257, 4082–4090 (2011).

<sup>17</sup>J. J. Gu, A. T. Neal, and P. D. Ye, Appl. Phys. Lett. **99**, 152113 (2011).

<sup>18</sup>S. M. Sze, *Physics of Semiconductor Devices* (John Wiley & Sons, 1981).

<sup>19</sup>See http://www.ioffe.ru/SVA/NSM/Semicond/GaInAs/index.html for the In0.53Ga0.47As permittivity and intrinsic carrier concentration parameters.

<sup>20</sup>S. Monaghan, É. O'Connor, I. M. Povey, B. J. Sheehan, K. Cherkaoui, B. J. A. Hutchinson, P. K. Hurley, F. Ferdousi, R. Rios, K. J. Kuhn, and A. Rahman, J. Vac. Sci. Technol. B 31, 01A119 (2013).

<sup>21</sup>D. Varghese, Y. Xuan, Y. Q. Wu, T. Shen, P. D. Ye, and M. A. Alam, in Proceedings of the IEEE International Electron Devices Meeting (2008), p. 379.

<sup>22</sup>G. Brammertz, H. C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, Appl. Phys. Lett. 95, 202109 (2009).

<sup>23</sup>E. O'Connor, K. Cherkaoui, S. Monaghan, B. Sheehan, I. M. Povey, and P. K. Hurley, Microelectron. Eng. 147, 325 (2015).

<sup>24</sup>E. Nicollian and J. Brews, *MOS Physics and Technology* (Wiley, 1982).

<sup>25</sup>Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, IEEE Electron Device Lett. 32, 485 (2011).

<sup>26</sup>V. Djara, K. Cherkaoui, M. Schmidt, S. Monaghan, É. O'Connor, I. M. Povey, D. O'Connell, M. E. Pemble, and P. K. Hurley, IEEE Trans. Electron Device 59, 1084 (2012).