| Title                       | A study of capacitance-voltage hysteresis in HfO2/InGaAs metal-<br>oxide-semiconductor systems                                                                                                                                                                                                                                                                                                   |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Lin, Jun;Monaghan, Scott;Cherkaoui, Karim;Povey, Ian<br>M.;O'Connor, Éamon;Sheehan, Brendan;Hurley, Paul K.                                                                                                                                                                                                                                                                                      |

| Publication date            | 2015-02-26                                                                                                                                                                                                                                                                                                                                                                                       |

| Original Citation           | Lin, J., Monaghan, S., Cherkaoui, K., Povey, I. M., O'Connor, É., Sheehan, B. and Hurley, P. K. (2014) 'A study of capacitance-voltage hysteresis in Hf02/InGaAs metal-oxide-semiconductor systems', 2014 IEEE International Integrated Reliability Workshop Final Report (IIRW), pp. 36-40. doi: 10.1109/IIRW.2014.7049503                                                                      |

| Type of publication         | Conference item                                                                                                                                                                                                                                                                                                                                                                                  |

| Link to publisher's version | https://www.aconf.org/conf_52662.html - 10.1109/<br>IIRW.2014.7049503                                                                                                                                                                                                                                                                                                                            |

| Rights                      | © 2014, IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. |

| Download date               | 2025-02-05 18:07:23                                                                                                                                                                                                                                                                                                                                                                              |

| Item downloaded from        | https://hdl.handle.net/10468/13319                                                                                                                                                                                                                                                                                                                                                               |

# A study of capacitance-voltage hysteresis in the HfO<sub>2</sub>/InGaAs metal-oxide-semiconductor system

Jun Lin, Scott Monaghan, Karim Cherkaoui, Ian Povey, Éamon O'Connor, Brendan Sheehan, and Paul Hurley

Tyndall National Institute, University College Cork, Cork, Ireland

E-mail address of corresponding author: jun.lin@tyndall.ie

#### **Abstract**

In this work, we performed a study of capacitance-voltage (C-V) hysteresis in HfO<sub>2</sub>/InGaAs metal-oxide-semiconductor (MOS) systems. The charge trapping density estimated from the C-V hysteresis is comparable to or even greater than the typical interface state density in high-k/InGaAs MOS systems. Based on an oxide thickness series, it is demonstrated that the magnitude of C-V hysteresis increases linearly with the increasing HfO<sub>2</sub> thickness, with the corresponding density of trapped charge being a constant value over the range of oxide thicknesses, indicating that the charge trapping is occurring in a plane near/at the HfO<sub>2</sub>/InGaAs interfacial transition region. C-V hysteresis with a hold in accumulation was also investigated. It is observed that the C-V hysteresis has a power law dependence on the stress time in accumulation at the initial stage of stressing and tends to reach a plateau for sufficiently long stress times. Moreover, a larger gate voltage used during the stress increases the oxide field, allowing more border traps to be accessed.

## Keywords - HfO2; InGaAs; C-V hysteresis; stress

#### 1. Introduction

High-dielectric constant (high-k) gate materials in conjunction with high mobility channel materials (e.g. InGaAs) are under investigation in order to improve metal oxide semiconductor field effect transistor (MOSFET) performance. However, the highk/InGaAs MOS system exhibits a high density of interface states (Dit) and fixed oxide charges, both of which can affect device performance by degrading the subthreshold slope and shifting the MOSFET threshold voltage (V<sub>t</sub>), and have been examined in some detail [1-5]. Charge trapping sites (referred to as "slow states" or "border traps") can also be located within the interfacial transitional region between the high-k oxide and the crystalline InGaAs. These border traps can cause device instability, and now represent the main challenge for the development of the highk/InGaAs gate stacks. Border traps have been examined based primarily on the frequency dispersion of the accumulation capacitance for high-k/InGaAs MOS structures [6-8]. However, this accumulation frequency dispersion can also include the contribution of interface states which have short time constants and energy levels inside the conduction band [9-11]. An alternative way in which border traps manifest themselves in device behavior, is that they will induce hysteresis exhibited in the capacitance-voltage (C-V) response, and an analysis of C-V hysteresis presents as alternative method to characterize the density and charge trapping dynamics of high-k/InGaAs border traps. In the literature, very little attention has been paid to the issue of C-V hysteresis exhibited in highk/InGaAs MOS systems [12-14]. In this study, we extend the work reported in [12] to study C-V hysteresis in HfO<sub>2</sub>/InGaAs MOS capacitors with an emphasis on the charge trapping distribution in the HfO<sub>2</sub> film and a study of the charge trapping dynamics through analysis of the C-V hysteresis evolution with the hold in accumulation.

#### 2. Experimental

The samples used in this work were *n*-doped and *p*doped InP (100) substrates with 2 µm n-type (S at 4  $x10^{17}cm^{-3}$ ) and p-type (Zn at 4  $x10^{17}cm^{-3}$ ) InGaAs (indium concentration = 53%) epitaxial layers, respectively, grown by metal organic vapour phase epitaxy (MOVPE). Prior to oxide deposition, all the samples were immersed in (NH<sub>4</sub>)<sub>2</sub>S solutions (10% in deionized H<sub>2</sub>O) for 20 min at room temperature (~295 K) [15]. The samples were then introduced to the atomic layer deposition (ALD) chamber within a minimum transfer time (~3 min) after the removal from the 10% (NH<sub>4</sub>)<sub>2</sub>S solution to minimize the formation of InGaAs native oxide due to air exposure. HfO<sub>2</sub> was deposited as the high-k oxide on the InGaAs surface. The HfO2 dielectric has a series of thicknesses (10 nm, 15 nm, 20 nm, 25 nm, 30 nm) deposited by ALD at 250 °C using Hf[N(CH<sub>3</sub>)C<sub>2</sub>H<sub>5</sub>]<sub>4</sub> (TEMAH) and H<sub>2</sub>O as precursors. Pd (160 nm) was used as the metal contacts and formed by electron beam evaporation and a lift-off process. During the measurements, the samples were placed in a Cascade Microtech probe station (model Summit 12971B) in a dry air, dark environment. The C-V hysteresis measurements were recorded using either an Agilent CV-enabled B1500A semiconductor device analyser or an E4980 LCR meter. The C-V hysteresis responses were measured starting from inversion and sweeping towards accumulation, and subsequently sweeping back towards inversion. All the C-V hysteresis sweeps were recorded at room temperature and a high frequency of 1 MHz to minimize the Dit contribution to the C-V. The charge trapping density is quantified using equation (1).

$Q_{trapped} = (\Delta V \times C_{ox})/q \ (cm^{-2}) \qquad (1)$  where  $Q_{trapped}$  is the density of trapped charge in cm<sup>-2</sup>,  $\Delta V$  is the C-V hysteresis in V,  $C_{ox}$  is the oxide capacitance in F/cm<sup>2</sup>, and q is the elementary charge in C. Equation (1) assumes the charge trapping is taking place predominantly near/at the high-k/InGaAs

interfacial transition region, as reported in [12] for HfO<sub>2</sub>/InGaAs and Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS systems. The validity of this assumption for the HfO<sub>2</sub>/InGaAs structure is explored further in this paper.

#### 3. Results and Discussion

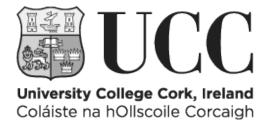

Fig.1 shows double C-V hysteresis sweeps for HfO<sub>2</sub>(15nm) over (a) n-InGaAs and (b) p-InGaAs MOS capacitors. The  $\Delta V$  estimated from the first C-V hysteresis sweep corresponds to an electron trapping level of  $2.4 \times 10^{12}$  cm<sup>-2</sup> for the *n*-InGaAs, and a hole trapping level of 8.9x10<sup>12</sup> cm<sup>-2</sup> for the p-InGaAs, both of which are comparable to or even greater than the typical Dit integrated across the energy gap in highk/InGaAs MOS systems, indicating that C-V hysteresis is an important problem to resolve. In addition, it is noted that the relaxation process for trapped charges in the InGaAs MOS structure is very fast when compared to silicon based MOS devices, with significant recovery occurring at time scales < 0.1 s [16]. As a consequence, the total trapped charge density could exceed the values quoted above when using fast pulse measurements on MOSFET structures. From Fig.1, it is also evident that the majority of the charge trapping is a reversible process as indicated by the almost overlapping 1st and 2nd sweeps in the inversion to accumulation (upwards) direction. There is a large shift between the 1st and 2nd upward C-V sweeps in the case of p-InGaAs, which is due to the charges being trapped in the defect sites which cannot be removed even when pushing the MOS capacitor back into inversion. More details are discussed in [12].

Fig.1: Double C-V hysteresis for (a) Pd/HfO<sub>2</sub>(15nm)/n-InGaAs and (b) Pd/HfO<sub>2</sub>(15nm)/p-InGaAs MOS capacitors. The charge trapping density estimated from the C-V hysteresis (measured at the mid-point along the C-V) is comparable to or even greater than the typical  $D_{it}$  in high-k/InGaAs MOS systems.

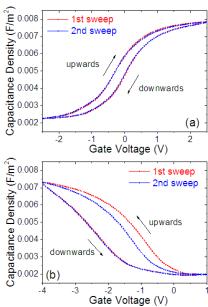

The use of a HfO<sub>2</sub> thickness series allows for an investigation of the distribution of trapped charge in the HfO<sub>2</sub> film. The maximum electric field, as determined by the maximum voltage (V<sub>max</sub>) in accumulation, is kept at the same value for all thicknesses for both the *n*-InGaAs and *p*-InGaAs, neglecting the effect of different oxide electric fields due to small variations in oxide thickness. It is observed in our experiments that the C-V hysteresis window increases for the samples with a thicker HfO<sub>2</sub> film. It is expected that, for a trapped charge located in a plane (in unit of cm<sup>-2</sup>) near/at the oxide/semiconductor interface, ΔV is proportional to oxide thickness. This linear relation can be expressed using equation (2).

$\Delta V = (q \times Q_{trapped} \times t_{ox})/(\epsilon_0 \times k)$  (2) where  $t_{ox}$  is the oxide thickness,  $\epsilon_0$  is the vacuum permittivity, and k is the relative permittivity of the oxide. For a trapped charge distributed throughout the oxide layer (in unit of cm<sup>-3</sup>),  $\Delta V$  will be proportional to the square of the oxide thickness [12, 17].

The C-V hysteresis magnitude ( $\Delta V$ ) and the corresponding charge trapping density are plotted as a function of oxide thickness as shown in Fig.2 for (a) n-InGaAs and (b) p-InGaAs MOS capacitors, which demonstrates a linear dependence of the C-V hysteresis magnitude on the HfO<sub>2</sub> thickness with the corresponding  $Q_{trapped}$  being a constant value for all HfO<sub>2</sub> thicknesses. This is consistent with charge trapping occurring in a plane (in cm<sup>-2</sup>) at the HfO<sub>2</sub>/InGaAs interfacial transition region.

Fig.2: C-V hysteresis (ΔV) and charge trapping density (Q<sub>trapped</sub>) as a function of HfO<sub>2</sub> thickness for (a) Pd/HfO<sub>2</sub>/n-InGaAs and (b) Pd/HfO<sub>2</sub>/p-InGaAs MOS capacitors. The maximum electric field is kept at the same value for all thicknesses. C-V hysteresis is estimated at either the flatband capacitance or half the maximum capacitance. ΔV increases linearly with increasing HfO<sub>2</sub> thickness and the corresponding Q<sub>trapped</sub> is a constant value over the range of oxide thicknesses used, consistent with charge trapping occurring in a plane near/at the HfO<sub>2</sub>/InGaAs interfacial transition region.

Extracting the gradient of  $\Delta V$  versus the oxide thickness from Fig.2 and using equation (2) yield an electron trapping density of  $7.0 \times 10^{12} \, \mathrm{cm}^{-2}$  for the *n*-InGaAs and a hole trapping density of  $8.1 \times 10^{12} \, \mathrm{cm}^{-2}$  for the *p*-InGaAs. The linear dependence of C-V hysteresis on oxide thickness has also been observed in other high-*k* oxides (e. g. Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, HfAlO, HfSiO, etc) measured on InGaAs MOS systems as reported previously in [12, 18], all of which indicate that the trapped charge is localized in a plane and not distributed throughout the high-*k* oxide.

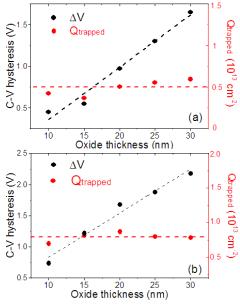

C-V hysteresis with a hold in accumulation (at V<sub>max</sub>) was also investigated in this work. The measurements were performed using an E4980 LCR meter through labview which is capable of measuring C-V from inversion to accumulation at a gate voltage (Vg) equals to  $V_{max}$  and holding MOS capacitor at  $V_{max}$  for a period of time ( $t_{\text{stress}}$ ) before sweeping the C-V back towards inversion. Measurements with different stress times were performed on different sites in order to minimize the possible contribution of stress induced interface states to the measured value of  $\Delta V$ . The behavior of these sites has been confirmed to be similar by comparing the double C-V hysteresis measured on them prior to the stress measurements. Fig.3 shows the evolution of the C-V hysteresis with increasing stress hold time in accumulation for a Pd/HfO<sub>2</sub>(15nm)/n-InGaAs MOS capacitor. It is important to emphasize that  $\Delta V \neq 0$  V even without a hold time at  $V_{\text{max}}$  (see Fig.1 and Fig.3), and this  $\Delta V$ value is denoted as  $\Delta V_0$ .  $\Delta V$ - $\Delta V_0$  is plotted as a function of stress time for HfO<sub>2</sub>(15nm) over (a) n-InGaAs and (b) p-InGaAs MOS capacitors using different values of  $V_{\text{max}}$  as shown in Fig.4 in log-log scale. It is observed that  $\Delta V$ - $\Delta V_0$  increases with a power law dependence with the increasing stress time at the initial stage of stressing and tends to reach a plateau when the stress time is sufficiently long. This relation is similar to the previous model proposed by S. Zafar et al [19], who performed positive bias stress pulses on HfO2 and Al2O3 on Si substrate n-channel MOSFET and demonstrated that the threshold voltage shift  $(\Delta V_t)$  increases with a power law dependence on the stress time at the initial stage of stressing. This model also predicts that the  $\Delta V_t$  will eventually reach a plateau if the n-channel MOSFET is stressed at positive gate bias for a sufficiently long time providing that no new border traps are created during the stress. The relation between  $\Delta V$ - $\Delta V_0$  and stress time ( $t_{stress}$ ) can be expressed using equation (3) on the premise that no new traps are generated during the stress.

$\Delta V - \Delta V_0 = \Delta V_{max0} \times \{1 - exp(-(t_{stress}/\tau_0)^\gamma)\} \qquad (3)$  where  $\tau_0$  and  $\gamma$  are fitting parameters associated with the gate leakage current and the capture cross section of the traps, and  $\Delta V_{max0}$  is associated with the maximum trapping density [19]. For  $t_{stress} << \tau_0$ ,  $\Delta V - \Delta V_0 \approx \Delta V_{max0} \times (t_{stress}/\tau_0)^\gamma$  (i.e. a power law dependence of  $\Delta V - \Delta V_0$  on  $t_{stress}$ ), and for  $t_{stress} >> \tau_0$ ,  $\Delta V - \Delta V_0 \approx \Delta V_{max0}$  (i.e. a plateau). Once  $\Delta V_{max0}$  is obtained

(i.e. the saturation value of  $\Delta V$ - $\Delta V_0$  in Fig.4), the maximum trapping density corresponding to a certain value of  $V_{max}$  used, can be calculated using equations (1) and (3).

Fig.3: C-V hysteresis responses with an increasing stress time in accmulation (at  $V_{max} = 2.5 \text{ V}$ ) for a Pd/HfO<sub>2</sub>(15nm)/n-InGaAs MOS capacitor.

Fig.4:  $\Delta V$ -  $\Delta V_0$  as a function of stress time for (a)  $Pd/HfO_2(15nm)/n$ -InGaAs and (b)  $Pd/HfO_2(15nm)/p$ -InGaAs MOS capacitors.  $\Delta V$ -  $\Delta V_0$  increases with a power law dependence with the increasing  $t_{stress}$  at the initial stage of stressing and tends to reach a plateau at sufficiently long stress times.

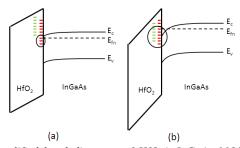

Fig.5: Simplified band diagrams of HfO<sub>2</sub>/n-InGaAs MOS capacitor which have (a) smaller  $E_{ox}$  and (b) larger  $E_{ox}$ . The border traps that are involved in the trapping process leading to C-V hysteresis are circled. Using a larger  $V_{max}$  thus a larger  $E_{ox}$  allows more border traps to be accessed, resulting in a larger  $\Delta V$ .

It is noted in Fig.4 that using different  $V_{\text{max}}$  results in different saturation values at the plateau. Border

traps can be distributed at different energy levels and also at different depth into the oxide near/at the high-k/InGaAs interface (Fig.5). Firstly, using a larger  $V_{max}$  pushes the Fermi level further into the InGaAs conduction/valence bands, thus accessing border traps over a wider energy range resulting in a larger  $\Delta V$ . Secondly, a larger  $V_{max}$  increases the electric field across the oxide ( $E_{ox}$ ), which can result in additional oxide traps being aligned with the Fermi level at the high-k/InGaAs interface during the stress (see Fig.5).

#### 5. Conclusion

C-V hysteresis measurements were performed on Pd/HfO<sub>2</sub>/InGaAs/InP MOS capacitors. The C-V hysteresis corresponds to a charge trapping level comparable to or even greater than the typical Dit in high-k/InGaAs MOS systems, indicating the importance of C-V hysteresis behavior. The results indicated that the trapping occurs primarily in a plane near/at the HfO2/InGaAs interface and not distributed throughout the oxide, indicating that the engineering of the interface transition region between the HfO<sub>2</sub> and the InGaAs is central to minimizing C-V hysteresis and thus device instabilities. In addition,  $\Delta V - \Delta V_0$  increases with a power law dependence on stress time in accumulation and approaches to a plateau at sufficiently long stress times, consistent with trapping in pre-existing border traps which have a wide range of capture cross sections. A larger V<sub>max</sub> used in the study of C-V hysteresis with a hold at V<sub>max</sub> in accumulation results in a larger  $\Delta V$ . This is because a larger V<sub>max</sub> results in a larger E<sub>ox</sub> which allows more border traps to be assessed.

### Acknowledgements

The authors acknowledge Science Foundation Ireland for financial support of the research work through the INVENT project (09/IN.1/I2633).

#### References

- [1] P. K. Hurley, É. O'Connor, S. Monaghan, R. D. Long, A. O. 'Mahony, I. M. Povey, K. Cherkaoui, J. MacHale, A. J. Quinn, and G. Brammertz, *Electrochemical Society Transactions* **25**(6) 113-127 (2009).

- [2] É. O'Connor, R. D. Long, K. Cherkaoui, K. K. Thomas, F. Chalvet, I. M. Povey, M. E. Pemble, P. K. Hurley, B. B. Brennan, G. Hughes, and S. Newcomb, *Applied Physics Letters* **92**, 022902 (2008).

- [3] R. Engel-Herbert, Y. Hwang, and S. Stemmer, *Journal of Applied Physics* **108**,124101 (2010).

- [4] B. Shin, J. R. Weber, R. D. Long, P. K. Hurley, C. G. Van de Walle, and P. C. McIntyre, *Applied Physics Letters* **96**, 152908 (2010).

- [5] R. D. Long, B. Shin, S. Monaghan, K. Cherkaoui, J. Cagnon, S. Stemmer, P. C. McIntyre, and P. K. Hurley, *Journal of the Electrochemical Society* **158**, G103 (2011).

- [6] Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, *IEEE Electron Device Lett.*, **32**(4) 485–487 (2011).

- [7] G. Brammertz, A. Alian, D. H. C. Lin, M. Meuris, M. Caymax, and W. E. Wang, *IEEE Trans. Electron Devices* **58**(11), 3890–3897 (2011).

- [8] E. J. Kim, L. Wang, P. M. Asbeck, K. C. Saraswat, and P. C. McIntyre, *Applied Physics Letters* **96**, 012906 (2010). [9] É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K.Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb, V.V. Afanas'ev, and P. K. Hurley, Applied Physics Letters **94**, 102902 (2009).

- [10] G. Brammertz, H. C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, *Applied Physics Letters* **95**, 202109 (2009).

- [11] N. Taoka, M. Yokoyama, S.H. Kim, R. Suzuki, R. Iida, S. Lee, T. Hoshii, W. Jevasuwan, T. Maeda, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M.Takenaka and S.Takagi, Proceedings of the IEEE International Electron Devices Meeting IEDM, p. 610 (2011).

- [12] J. Lin, Y. Y. Gomeniuk, S. Monaghan, I. M. Povey, K. Cherkaoui, É. O'Connor, M. Power, and P. K. Hurley, *Journal of Applied Physics* **114**, 144105 (2013).

- [13] Y. Y. Gomeniuk, A. N. Nazarov, S. Monaghan, K. Cherkaoui, E. O'Connor, I. Povey, V. Djara, and P. K. Hurley, in *Proceedings of the International Conference on nanomaterials: Applications and Properties* (2012), Vol. 1, No. 3, p. 03TF16.

- [14] N. Goel, D. Heh, S. Koveshnikov, I. Ok, S. Oktyabrsky, V. Tokranov, R. Kambhampatic, M. Yakimov, Y. Sun, P. Pianetta, C. K. Gaspe, M. B. Santos, J. Lee, S. Datta, P. Majhi, and W. Tsai, *Tech. Dig. –Int. Electron Devices Meet.* 363-366 (2008).

- [15] É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, *Journal of Applied Physics* **109**, 024101 (2011).

- [16] J. Franco, A. Alian, B. Kaczer, D. Lin, T. Ivanov, A. Pourghaderi, K. Martens, Y. Mols, D. Zhou, N. Waldron, S. Sioncke, T. Kauerauf, N. Collaert, A. Thean, M. Heyns1, and G. Groeseneken, In *Reliability Physics Symposium*, 2014 IEEE International (pp. 6A-2). IEEE.

- [17] R. S. Muller, T. I. Kamins, Device Electronics for Integrated Circuits, Wiley, New York, 1986

- [18] N. Goel, D. Heh, S. Koveshnikov, I. Ok, S. Oktyabrsky, V. Tokranov, R. Kambhampatic, M. Yakimov, Y. Sun, P. Pianetta, C. K. Gaspe, M. B. Santos, J. Lee, S. Datta, P. Majhi, and W. Tsai, *Tech. Dig. –Int. Electron Devices Meet.* 363-366 (2008)

- [19] S. Zafar, A. Callegari, E. Gusev and M. V. Foschetti, *Journal of Applied Physics* **93**, 9298 (2003).