| Title                       | Investigating the transient response of Schottky barrier back-<br>gated MoS2 transistors                                                                                                                                                                                     |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Marquez, Carlos;Salazar, Norberto;Gity, Farzan;Navarro,<br>Carlos;Mirabelli, Gioele;Galdon, Jose Carlos;Duffy, Ray;Navarro,<br>Santiago;Hurley, Paul K.;Gamiz, Francisco                                                                                                     |

| Publication date            | 2020-02-13                                                                                                                                                                                                                                                                   |

| Original Citation           | Marquez, C., Salazar, N., Gity, F., Navarro, C., Mirabelli, G., Galdon, J. C., Duffy, R., Navarro, S., Hurley, P. K. and Gamiz, F. (2020) 'Investigating the transient response of Schottky barrier backgated MoS2 transistors', 2D Materials. doi: 10.1088/2053-1583/ab7628 |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                      |

| Link to publisher's version | http://iopscience.iop.org/10.1088/2053-1583/ab7628 -<br>10.1088/2053-1583/ab7628                                                                                                                                                                                             |

| Rights                      | © 2020, IOP Publishing. This Accepted Manuscript is available for reuse under a CC BY-NC-ND 3.0 licence after a 12 month embargo period https://creativecommons.org/licenses/by-nc-nd/3.0/                                                                                   |

| Download date               | 2025-07-31 22:40:17                                                                                                                                                                                                                                                          |

| Item downloaded from        | https://hdl.handle.net/10468/9714                                                                                                                                                                                                                                            |

#### **ACCEPTED MANUSCRIPT**

# Investigating the transient response of Schottky barrier back-gated MoS<sub>2</sub> transistors

To cite this article before publication: Carlos Marquez et al 2020 2D Mater. in press https://doi.org/10.1088/2053-1583/ab7628

### Manuscript version: Accepted Manuscript

Accepted Manuscript is "the version of the article accepted for publication including all changes made as a result of the peer review process, and which may also include the addition to the article by IOP Publishing of a header, an article ID, a cover sheet and/or an 'Accepted Manuscript' watermark, but excluding any other editing, typesetting or other changes made by IOP Publishing and/or its licensors"

This Accepted Manuscript is © 2020 IOP Publishing Ltd.

During the embargo period (the 12 month period from the publication of the Version of Record of this article), the Accepted Manuscript is fully protected by copyright and cannot be reused or reposted elsewhere.

As the Version of Record of this article is going to be / has been published on a subscription basis, this Accepted Manuscript is available for reuse under a CC BY-NC-ND 3.0 licence after the 12 month embargo period.

After the embargo period, everyone is permitted to use copy and redistribute this article for non-commercial purposes only, provided that they adhere to all the terms of the licence <a href="https://creativecommons.org/licences/by-nc-nd/3.0">https://creativecommons.org/licences/by-nc-nd/3.0</a>

Although reasonable endeavours have been taken to obtain all necessary permissions from third parties to include their copyrighted content within this article, their full citation and copyright line may not be present in this Accepted Manuscript version. Before using any content from this article, please refer to the Version of Record on IOPscience once published for full citation and copyright details, as permissions will likely be required. All third party content is fully copyright protected, unless specifically stated otherwise in the figure caption in the Version of Record.

View the article online for updates and enhancements.

Carlos Marquez<sup>1,2</sup>, Norberto Salazar<sup>1</sup>, Farzan Gity<sup>2</sup>, Carlos Navarro<sup>1</sup>, Gioele Mirabelli<sup>2</sup>, Jose C. Galdon<sup>1</sup>, Ray Duffy<sup>2</sup>, Santiago Navarro<sup>1</sup>, Paul K. Hurley<sup>2</sup> and Francisco Gamiz<sup>1</sup>

- <sup>1</sup> Nanoelectronics Research Group (CITIC-UGR), Department of Electronics, University of Granada, Granada 18071, Spain

- <sup>2</sup> Nanoelectronic Materials and Devices Group, Tyndall National Institute, University College Cork, Lee Maltings, Cork T12 R5CP, Ireland

E-mail: carlosmg@ugr.es

December 2019

Abstract. Molybdenum disulfide (MoS<sub>2</sub>) MOSFETs have been widely reported to exhibit hysteresis behavior, which is usually attributed to charge trapping effects due to defective/sub-stoichiometric compositions in the material, or defects near, or at, the oxide/channel interfaces. It is also suggested that defective  ${\rm MoS}_2$  transistors show current limitations caused by the Schottky barrier junctions formed at the contacts. Here, we report on the static and dynamic device response of back-gated MoS<sub>2</sub> transistors directly fabricated on a SiO<sub>2</sub>/Si substrate using chemical vapor deposition synthesis, without film transfer, and standard CMOS optical lithography. The devices exhibit an atypical hysteresis in the transfer characteristics, as well as a delayed response in the formation of the conducting channel in response to voltage pulses applied to the back gate. Analysis of the output characteristic is consistent with two back-to-back Schottky diodes, allowing the Fermi level pinning position at the Ni/MoS<sub>2</sub> source and drain contacts and blocking the MoS<sub>2</sub> hole channel. Capacitancevoltage characterization demonstrates that the grown MoS<sub>2</sub> thin film is p-type, resulting in a nominally-off, inversion mode, n-channel device. Analysis of the transient response and hysteresis as a function of device temperature, illumination and ambient conditions indicates that the dynamic response of the device is determined by the net charge in the MoS<sub>2</sub> film combined with the minority carrier generation lifetime in the underlying silicon substrate. The work demonstrates the strong dependence of the device response time on substrate, temperature, illumination, and net charge in the  $\mathrm{MoS}_2$  layer opening the possibility of applications in photo-detectors and sensors.

Keywords: Defects, hysteresis,  $MoS_2$ , Schottky barrier transistors, two-dimensional materials, reliability

#### 1. Introduction

The exfoliation of graphene, leading to the Nobel Prize in Physics in 2010 to A. Geim and K. Novoselov [1, 2], and the successful demonstration of molybdenum disulfide  $(MoS_2)$  field-effect transistor (FET) in 2011 [3] triggered a tremendous amount of research into two-dimensional (2D) materials. Due to the reduced thickness, these thin materials present an optimal electrostatic control of the channel providing better immunity to short channel effects than the planar silicon counterparts [4]. In addition, the wide variety of electronic and optical properties exhibited by thin semiconducting materials is also attracting interest in fields such as: photovoltaic cells [5, 6], supercapacitors [7, 8] or nanophotonics and quantum optics [9] are demonstrating a change towards to these promising options. Among the thin materials family, the transition metal dichalcogenides (TMDs) and especially MoS<sub>2</sub> present interesting properties like an indirect to direct bandgap transition as the film thickness is reduced from multilayer to monolayer due to quantum confinement and optical band gaps in the range of 1.2-1.8 eV [10], making them suitable for near-infrared absorption and emission with strong photoluminescence. Regarding electrical properties. according to the International Roadmap for Devices and Systems (IRDS) guideline [11], TMDs devices present advantages in terms of higher on/off ratios, enabling reduced power consumption, current leakage and good switching delay with respect to silicon devices.

Fundamental physics and devices on 2D TMDs have relied on the exfoliation method due to the high crystalline quality of natural and synthetic crystals. However, the critical limitations of the flake dimension and film uniformity have restricted its development beyond the fundamental studies. Scalable application of atomically thin TMDs requires wafer-scale deposition of films with well-controlled properties. Vapor deposition techniques have been most extensively explored due to their potential for high scalability and morphological control. Chemical Vapor Deposition (CVD) has emerged as the growth method used to produce largearea TMD films suitable for research and industrial purposes. However, the experimental results rarely accomplish the promising theoretical properties for these 2D materials. Since Novoselov et al. [2] demonstrated very poor properties in few-layer MoS<sub>2</sub> FETs (e.g. mobility of 0.53 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>), different strategies have been developed to overcome the device limitations: Dielectric engineering has been proposed to suppress Coulomb scattering and reduce the impact of Schottky barriers [12, 13, 14, 15, 16]; metal contact engineering [17, 18] and surface and defect engineering [19, 20] to improve the contact resistance and the Schottky

barrier limitations or pulsed voltage measurements to achieve current hysteresis reduction [21]. In addition, material doping [22, 23, 24, 25], fabrication advances by atomic layer deposition [26], lithography alternatives [27] and double gate architectures [28, 29, 3] have been proposed as well. Unfortunately, despite these advances, defects and impurities (grain boundaries, corrugation, sulfur vacancies, oxygen incorporation, moisture molecules and oxide ions) still play an important role on the actual drop in performance of the fabricated devices. Predominantly, defects have demonstrated the influence of Schottky barriers underneath the contact pads by pinning the metal Fermi level [17, 18]. Additionally, depending on their energy positions inside the bandgap, defects can act as either donors or acceptors centers near the conduction and valence bands, or as generation-recombination centers (R-G) if they are located near the mid-gap energy. The presence of these defects, and their associated energy levels, can dominate the device performance. In this regard, it has been commonly reported that the effect of defects in exfoliated  $MoS_2$  results in a n-type behavior [30]. The resulting devices are junctionless [31] accumulation mode n-channel MOSFETs [32, 33, 34, 35, 29] which usually present high power consumption limitations due to the normally-on characteristic.

In addition to defects which yield n- and p-type dopants in  $MoS_2$ , a number of papers have reported hysteresis in the transfer characteristics of MoS<sub>2</sub> channel MOSFETs, which is attributed to electron trapping and emission from oxide defects and interface or surface states [33, 36, 37, 35, 32, 38]. Hysteresis analysis have been carried out demonstrating carrier tunneling through oxide defects for the anti-clockwise behaviors [39] and trapping/detrapping of carriers in oxide and at the interface defects for clockwise operations [33], both with reversible effect. Other works have demonstrated the implication of the traps in the photoconductivity of these devices [34]. Theoretical and modeling works have also been addressed to shed light on these instabilities [40, 41, 42, 43]. However, due to the huge amount of variables (synthesis precursors, growth conditions, insulating and substrate materials, processing metals and annealing options) the limiting mechanisms and the defect implications on the performance and reliability of the device are as yet not entirely understood.

In this work, we report on the static and dynamic response of back-gated  $MoS_2$  transistors, where the  $MoS_2$  is grown by CVD directly on  $SiO_2/Si$  substrate and the devices are fabricated using standard lithography and etching without  $MoS_2$  films transfer. Following an analysis of the static device characteristics, the hysteresis and transient response

of the back-gated MoS<sub>2</sub> MOSFETs are reported. The results highlight the role of MoS<sub>2</sub> charged defects, and the silicon substrate, in the the hysteresis and transient response of the back gated MoS<sub>2</sub> MOSFETs.

#### 2. Results and discussions

#### 2.1. Structural characterization

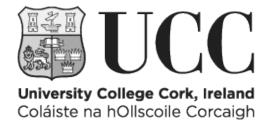

The direct synthesis of large-area MoS<sub>2</sub> films on a n-type silicon substrate covered by a 100 nmthick SiO<sub>2</sub> layer was accomplished via CVD through sulfurization of molybdenum trioxide (MoO<sub>3</sub>) at a maximum temperature of 680 °C (see Methods for details). An optical image of the resultant deposition is provided in Figure 1.a. The CVD-grown  $MoS_2$  and the SiO<sub>2</sub> substrate are easily distinguishable. Figure 1.b depicts the Raman spectrum of the MoS<sub>2</sub> layer excited by a 532 nm line laser at ambient conditions. The MoS<sub>2</sub> film exhibits two Raman characteristic bands at 387 and 410  $cm^{-1}$ , corresponding to the in-plane  $(E_{2q}^1)$  and the out-of-plane  $(A_{1q})$  modes, respectively. The difference of the peaks  $(\Delta)$  remains between 21- $23 \text{ cm}^{-1}$  across the MoS<sub>2</sub> layer which is consistent with the presence of thin  $MoS_2$  layers [44, 45, 46, 47]. These values are larger than expected for monolayer  $MoS_2$  (18-19  $cm^{-1}$ ) [44, 45], but smaller than the typical value for bulk  $MoS_2$  (26  $cm^{-1}$ ) [46], suggesting few-layer MoS<sub>2</sub>. Additionally, the Raman spectrum presents a peak centered around 450  $cm^{-1}$ . This controversial peak can be assigned to the combinations of different contributions [45]: i) One corresponding to the double frequency of the LA(M) mode (227  $cm^{-1}$ ) [47], attributed to disorder-induced Raman scattering or due to an increased level of partial oxidation on the  $MoS_2$  samples [48]; ii) the first-order optical phonon peak  $A_{2u}$  which involves asymmetric translations of both Mo and S atoms in the c-axis direction [49, 50]; and, iii) the Raman peak D which can be ascribed to Mo-S vibrations for oxysulfide species [51]. The bands are attributed to bridging Mo-S-Mo species for reduced molybdenum compounds or Mo<sup>6+</sup> oxysulfide species [51, 45]. X-ray photoelectron spectroscopy (XPS) analysis was used to measure binding energies of molybdenum (Mo, Figure 1.c) and sulfur (S, Figure Figure 1.c shows two broad peaks 1.d) atoms. positioned at around 229.2 eV and 232.3 eV, which correspond respectively to the main doublet Mo  $3d_{5/2}$ and Mo  $3d_{3/2}$  ( $3d_{5/2}$ : $3d_{3/2}$  ratio of 0.66 and a spin-orbit splitting of 3.10 eV) of Mo<sup>4+</sup> chemical state [52, 53]. Also, a minor peak observed at 226.3 eV is attributed to S 2s component. S 2p peaks at 161.9 eV and 163.1 eV (Figure 1.d) are ascribed respectively to spin orbits of S  $2p_{3/2}$  and S  $2p_{1/2}$  ( $2p_{3/2}$ : $2p_{1/2}$  ratio of 0.5 and a spin-orbit splitting of 1.2 eV). These results are in good agreement with the reported binding energy values for

${\rm MoS_2}$  [54]. Moreover, smaller contributions at around 235.3 and 234.0 eV coincide with the binding energy typically assigned to  ${\rm Mo^{6+}}$  and  ${\rm Mo^{5+}}$  oxidation states that correspond to the possible deposition of  ${\rm MoO_3}$  in the CVD synthesis process and/or the presence of suboxides species and S vacancies [55, 53, 56]. The  ${\rm Mo^{6+}}$  and  ${\rm Mo^{5+}}$  peaks found would indicate that some oxygen is incorporated in the grown  ${\rm MoS_2}$  film [57, 58, 59, 53], which was also demonstrated with the Raman results aforementioned. These results suggest the presence of defects distorting the stoichiometry of the synthesized  ${\rm MoS_2}$  films.

The determination of the thickness of the fabricated devices is carried out after the etching process through an atomic force microscopy (AFM) analysis. Figure 1.e. depicts the structure of the well-defined MoS<sub>2</sub> channel where triangular-shape MoS<sub>2</sub> domains are observed on the top layer. The AFM image reveals a MoS<sub>2</sub> channel of approximately 3 nm of height. Other devices along the sample have been characterized presenting similar thicknesses in agreement with Raman results. The structural studies have been complemented with a scanning electron microscope (SEM) characterization to verify the device homogeneity, the physical dimension of the channel and the effectiveness of the etching process. Figure 1.f corroborates a homogeneous channel and contacts.

#### 2.2. Electrical characterization

#### 2.2.1. Transistor characterization

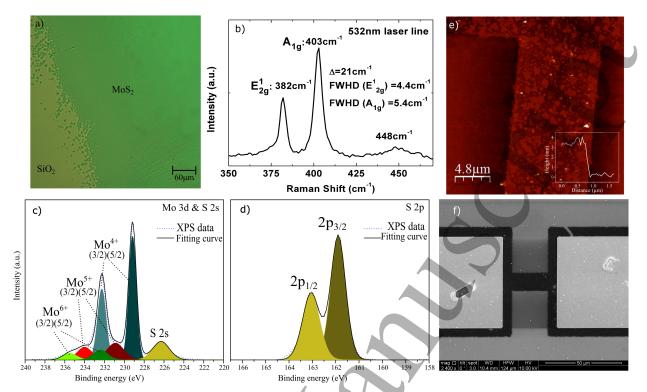

Regarding the performance of the fabricated devices as field-effect transistors, Figure 2.a shows the transfer characteristic ( $I_{DS}$ - $V_G$ ) of a back-gated MoS<sub>2</sub> device with channel dimensions of 25  $\mu$ m length and 25  $\mu$ m width in logarithmic (left axis) and linear (right axis) scales, at different drain biases (grounded source). These curves reveal a clear n-type operation with close to 0 V threshold voltages,  $V_{TH}$  (corresponding to low density of fixed charges). According to the Schottky-Mott theory [60, 61, 62], for a defect-free Ni/MoS<sub>2</sub> interface, and the case where the  $MoS_2$  is undoped with the Fermi level near mid gap, the expected barrier height should be close to zero, as  $\Phi_{Ni} = 5.1 \text{ eV}$ and  $\Phi_{MoS_2} = 5.05 \text{ eV}$  (electron affinity  $\chi_{MoS_2} \approx 4.4$ eV and  $E_q/2 \approx 0.65$  eV in a non-intentional doped material [63, 64]). This barrier height should, in theory, facilitate an ambipolar transfer characteristic [17]. However, in novel materials like 2D or III-V channel devices, it has been widely reported that the barrier height is a less sensitive function of  $\Phi_M$ than expected in Schottky-Mott theory due to the effect of surface states at the interface between the semiconductor and the metal [17, 63, 18]. Furthermore, density functional calculations have confirmed that the metal-MoS<sub>2</sub> interaction pins the Fermi level at

Figure 1. a) Optical image of a MoS<sub>2</sub> layer grown on a SiO<sub>2</sub>/Si substrate. b) Raman spectrum of the MoS<sub>2</sub> layer using a 532 nm line laser at atmospheric conditions. c) and d) high resolution XPS spectra of Mo and S peaks. e) Atomic force microscopy image of a continuous  $L=25~\mu m$  and  $W=10~\mu m$  MoS<sub>2</sub> channel device. Inset: height profile of the MoS<sub>2</sub> channel. f) Scanning electronic microscopy image of a  $L=25~\mu m$  and  $W=10~\mu m$  back-gated device. Scratches observed in the contact pads are due to the electrical probe contact during the electrical characterization process.

0.1-0.3 eV below the conduction band edge of the semiconductor [65]. This Fermi level pinning has been attributed to the basic metal-MoS<sub>2</sub> interface physics [66]. The absence of ambipolar operation is therefore attributed to the suppression of hole current by the Schottky barriers. Figure 2.b shows the transfer characteristic for transistors presenting different physical dimensions on the same sample. Transconductance  $(g_m = \partial I_D/\partial V_G)$  is depicted in the right y-axis. Interestingly,  $g_m$  follows a monotonic increasing trend with no saturation due to channel series resistance. This observation should be attributed to the Schottky barrier narrowing by increasing the vertical field which implies a more probable tunneling for electrons from the contacts to the channel. Note that the dependence of the threshold voltage on the drain bias in Figure 2.a could also have its origin in the Schottky barrier [63]. A considerable deviceto-device threshold voltage variability can also be inferred from Figure 2.b. Concerning this point, standard electrical parameters are presented in the Supplementary Material to allow comparison with other devices. Figure S1.a shows the threshold voltage variability for several devices with different physical dimensions with no clear trend as a function of the width or length. The field-effect mobility  $(\mu_{FE})$  is

shown in Figure S1.b as a function of the physical dimensions for a fixed overdrive voltage  $(V_{OV} = V_G - V_{TH} = 15 \text{ V})$ . The highest mobility of the characterized devices corresponds to  $\mu_{FE} = 2.35 \ cm^2 V^{-1} s^{-1}$ , which is comparable to the values typically reported for CVD grown MoS<sub>2</sub> devices in literature [67]. Finally, the subthreshold slope and the sheet resistance are depicted in Figure S1.c and S1.d, respectively. From the experimental extrapolation, material resistivity  $\rho \approx 8.5 \ \Omega.cm$  and contact resistance  $R_C \approx 4.75 \ \text{M}\Omega$  are extracted  $(V_{OV} = 5 \ \text{V})$  and  $V_{DS} = 0.1 \ \text{V})$ .

#### 2.2.2. Schottky barrier characterization

To investigate the Schottky barriers formation, Figure 2.c depicts the drain-source current-voltage characteristic of a 50  $\mu$ m-length and 45  $\mu$ m-width device in absence of back-gate bias (black square symbols). The curve shows a clear non-Ohmic rectifying behavior with exponential growing current at negative voltages confirming the formation of Schottky barriers in the metal-semiconductor junctions. To clarify this effect, the schematic illustration for two Schottky contacts in equilibrium condition resulting in two back-to-back junctions and considering a pinned metal work function is shown in Figure 2.d. According to the energy band diagram, the current through the

Figure 2. a) Transfer characteristic  $(I_{DS}-V_G)$  in logarithmic and linear scales for different drain biases. b) Transfer characteristic for different physical dimensions and the extracted transconductance  $(g_m)$ . c) Output characteristic of a device with grounded gate bias  $(V_G = 0 \text{ V})$  in two different representations,  $I_{DS}-V_{DS}$  (black) and  $ln(I_{DS})-V_{DS}^{1/4}$  (red). Drain currents  $I_{DS}$  are presented in absolute value. d) Schematic illustration of the device modelled by two back-to-back diodes and a channel resistance. e) Energy band diagram of the Schottky diodes under negative (top-left) and positive (top-right) drain biases. Energy band diagram when accounting the image force lowering effect under negative drain bias (bottom). Arrows indicate the electron flow. f)  $I_{DS}-V_{DS}$  behavior at different temperatures. The insets depict the fitting for the barrier heights extraction.

device will be limited either by the Schottky diodes or the corresponding channel series resistance. Energy band diagrams based on the two back-to-back Schottky barriers with negative and positive drain biases are presented in Figure 2.e (forced and grounded contacts are considered as drain and source, respectively). It is worth mentioning that regardless of the sign of  $V_{DS}$ , one of the Schottky diodes will always present a reverse configuration. Figure 2.e (top-left) depicts the case for negative drain bias. Under this condition, the drain/MoS<sub>2</sub> junction is biased in reverse while the

MoS<sub>2</sub>/source is in forward configuration (for electrons). The opposite case is presented in Figure 2.e (topright), where a positive drain bias sets the MoS<sub>2</sub>/drain junction in forward condition while the source/MoS<sub>2</sub> is in reverse. As observed, electrons have to overcome the corresponding reverse bias junction barrier in each case. According to the thermionic-emission theory [62], the current in a reversed Schoktty diode junction should saturate at the value:

$$I_0 = AA^{**}T^2 exp(\frac{-q\Phi_B}{kT}) \tag{1}$$

where A is the contact area of the junction,  $A^{**}$  is the Richardson constant for thermionic emission, q is the magnitude of the electron charge,  $\Phi_B$  is the Schottky barrier height,  $k_B$  is the Boltzmann constant and T is the temperature. This fact explains the behavior of the device when a positive voltage is forced: Although the drain/MoS<sub>2</sub> junction is forward biased, the current is limited by the reversed source/MoS<sub>2</sub> diode, Figure 2.d. However, this assumption cannot explain the currentvoltage dependence observed at negative drain biases (Figure 2.c), neither considering the forward nor the reverse contributions of the diodes involved (in forward operation, the current should follow a linear fit with drain bias). Nevertheless, a departure from the ideal behavior can be explained by image force lowering effect [62, 63]. Increasing the reverse junction bias induces a reduction of the Schottky barrier and the current does not saturate but increases proportionally to  $exp(q\Delta\Phi_B/kT)$ , where  $\Delta\Phi_B$  is the barrier lowering due to image charges. Energy barrier diagram taking into account this effect is depicted in Figure 2.e (bottom). Under these conditions, the corresponding value of  $\Delta \Phi_B$  follows a  $\Delta \Phi_B = \alpha V^{1/4}$  expression, where  $\alpha$  is a constant depending on the donor/acceptor concentration and the relative dielectric constant of the material [63]. Figure 2.c demonstrates a linear dependence of  $ln(I_{DS})$  as a function of  $V^{1/4}$  (red circle symbols), corroborating the barrier lowering effect at negative drain biases. This effect has also been observed in recent works on  $MoS_2$  devices [63]. Therefore, the current through the device is limited by the reversed biased junction between the drain and the MoS<sub>2</sub> channel following the lowering barrier height effect at the negative drain biases and by the reversed biased junction between the source and the  $MoS_2$  channel when the drain is positively biased. The current during the  $V_{DS} > 0$  V operation is saturated by the reversed junction and weakly affected by image force due to the absence of reversed bias in this interface (source is grounded) and the long distance to the drain ( $L = 45 \mu m$ ). This fact is confirmed by reversing the contact configuration (not shown). Including the image force lowering effect, the reverse current under negative applied voltages can be expressed as [63]:

$$I_{DS} = AA^{**}T^{2}exp[\frac{-q}{k_{B}T}(-\Phi_{B} + \alpha\sqrt[4]{V_{DS} - R_{S}I_{DS}})](2)$$

where  $\alpha$  is a dimensional constant and  $R_S$  the series resistance of the channel.

To determine the height of the barriers, the Schottky diode behavior is characterized at different temperatures and low gate biases, Figure 2.f. According to the Equation 2,  $I_{DS0}$  values  $(I_{DS}(V_{DS}=0~{\rm V}))$ , calculated for zero-bias extrapolation at different temperatures, should follow a trend as  $ln(I_{DS0}/T^2)=1$

$ln(AA^{**}) - (q\Phi_B/k_BT)$  when negative drain voltages are applied, Figure 2.f. The barrier  $\Phi_{B1}$  can be extracted from the linear dependence [63]. According to the fitting in Figure 2.f (left inset), the barrier height value for this specific device is  $\Phi_{B1} = 0.36$  eV for the reversed drain bias. In the case of a positive  $V_{DS}$ , the barrier which limits the current corresponds to the reversed source-semiconductor junction. This barrier height can be directly extracted from the reversed saturated current according to Equation 1, being for this specific device  $\Phi_{B2} = 0.24$  eV (Figure 2.f, right inset). As Figure 2.c (bottom) depicts  $\Phi_{B1}$  corresponds to the barrier height before subtracting the barrier height lowering effect. Therefore, the resulting barrier height corresponds to  $\Phi_{B1}$ - $\Delta\Phi_{B}$  should be lower than  $\Phi_{B2}$ according to the higher current for negative biases observed in Figure 2.c and Figure 2.f.

So far, the thermionic-emission has been considered as the main transport mechanism under these conditions of temperature and bias, statement which is validated by the fit of the experimental current (Figure 2.c) to the thermionic emission model (Equation 1 and Equation 2). Due to the absence of intentional doping (low acceptor/donor concentrations) and room temperature conditions, the contribution of other phenomena such as field or thermionic-field emission is discarded [62]. However, lowering the temperature or increasing vertical fields, these phenomena contribute to the transport mechanism. Figure S1 in the Supplementary Material (Section Schottky barrier characterization) validates that the main mechanism at room and higher temperatures is thermionic-emission while at low temperatures and at high gate biases thermionicfield emission contributes considerably to the current.

#### 2.3. Device Instability

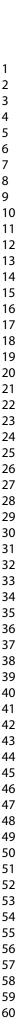

The  $I_{DS} - V_G$  double sweep (forward/backward) characteristic of the same 50  $\mu$ m-length and 45  $\mu$ mwidth device as in Figure 2.c is shown in Figure 3.a for different drain biases. A hysteresis cycle can be observed regardless of the selected drain bias. However, this reported behavior does not fit with the usual clockwise hysteresis, attributed to carrier trapping in  $MoS_2$  devices [32, 33, 34, 35]. The observed crossing point in the hysteresis suggests an additional mechanism taking place in the carrier transport (not a pure clockwise or anti-clockwise behavior is observed). Figure 3.b shows the same operation when increasing the delay time between sweep points, implying longer sweep times. The shortest sweep time (black square symbols) presents the same behavior as the previous device: a cross point in the hysteresis. However, when increasing the delay time, the cross point disappears and pure clockwise hysteresis is observed. A zoom-in of the cross region is presented in the inset of Figure

3.b.

To shed light on this unusual behavior, Figure 3.c shows the transfer characteristic at different temperatures. At relatively low temperatures (black squares and red circles), the drain-source current presents the mentioned crossing behavior, i.e.  $I_{DS}$ increases with  $V_G$  and it continues rising even when the voltage sweep changes the direction and decreases from the maximum ( $V_G = 30 \text{ V}$ ). This unexpected behavior suggests that the threshold voltage is being shifted to negative voltages or carrier injection is still taking place. However, this behavior is not permanent. During the reverse sweep at around  $V_G \approx 10 \text{ V}$  (at T =255 K), the current suddenly drops crossing the value of the forward sweep and finishing the reverse sweep with a higher threshold voltage than for the forward sweep direction (arrows indicate the sweep direction). When increasing the temperature, the cross point is shifted upward and disappears at room temperature, where hysteresis presents a purely clockwise operation. Therefore, the crossing effect observed in the hysteresis is originated by a thermally activated mechanism. A detailed analysis of the temporal characteristic of the current as a function of temperature at high vertical field is presented in Figure 3.d. Note here the bias conditions and that the voltage step is applied at t = 0 s. In this representation, the contribution of the two competing mechanisms is inferred: i) An initial phenomenon showing a temporal current level increment and ii) a second one which is responsible for a current level decay. These two mechanisms explain the crossing effect in the hysteresis depending on the sweep time: for sweep times shorter than the time needed to reach the maximum current at a given temperature and bias condition  $(\tau)$ , the first mechanism prevails and devices show anti-clockwise hysteresis (not shown). However, if the sweep time is long enough to allow both mechanisms to take place, the hysteresis shows a cross point once the first mechanism ends (crossing effect in Figure 3.c). Finally, if the sweep time is long enough, the second mechanism will prevail over the first and devices will show clockwise hysteresis (higher temperatures in Figure 3.c). Due to the temperature dependence of the first effect, the hysteresis also depends on the temperature. Despite the origin of this initial effect not being clear, the second phenomenon causing a temporal current decay and a clockwise operation has been widely reported in  $MoS_2$  devices [32, 33, 34, 35]. This effect is usually attributed to charging/discharging of carriers through oxide [33, 68] or interface traps [69]. In case of oxide traps, these are traps located within a few nanometers from the interface and thus can follow the change in the applied voltage by tunneling exchange with the channel. Illustratively, when a forward gate

bias is applied, the traps whose energy levels are below the Fermi level are filled by electrons with different characteristic times. The trapped electrons contribute to the increase of negative charge (reduction of positive charge considering donor traps) and therefore, increase the threshold voltage. A schematic representation is shown in Figure 3.e, where oxide and intrinsic traps are taken into account. This effect can be partially or totally recovered by applying a negative voltage to the gate according to Figure 3.f. These observations are consistent with the behavior predicted by theoretical modeling [33, 68, 70]. These defects are associated with both extrinsic (diffused water molecules and the chemisorption of oxygen [71]), which can be desorbed at high temperatures or under vacuum conditions, [33, 32] and intrinsic defect at the interface due to oxygen and sulfur vacancies, or even defects due to a non-passivated surface bonds of the MoS<sub>2</sub> [72].

On the other hand, the phenomenon occurring at the initial times, competing at lower temperature and causing the cross effect is not common. The mechanism presents a clear thermal activation signature (Figure 3.d) suggesting a Shockley-Read-Hall (SRH) mechanism involved. Carrier tunneling through oxide defects or thermal activation of oxide ions have been reported for the anti-clockwise behaviors [39]. However these effects can be discarded in this work due to the negligible gate current and the reduced implication of the phenomenon by increasing the temperature, opposite to the expected behavior when taking into account the thermally activated oxide ions. Another possible explanation could consist in a slow generation of carriers in the channel at the initial times, low intrinsic carrier density or even carrier injection limitations to the channel through the Schottky barriers at source and drain.

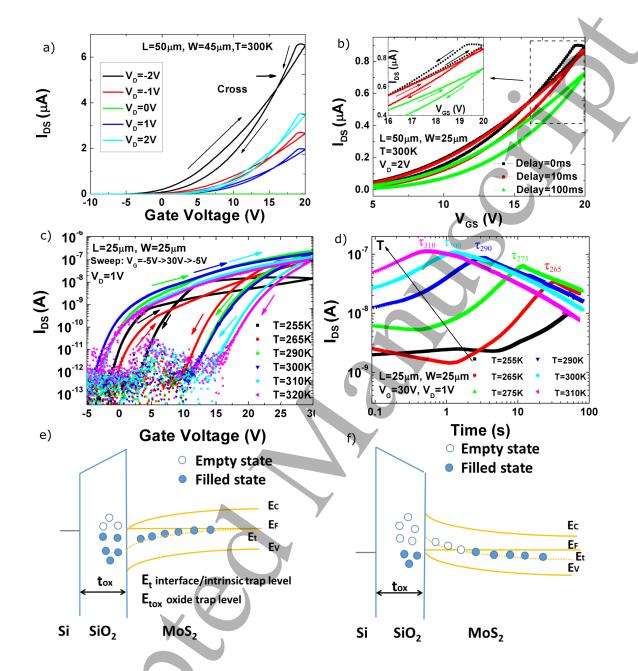

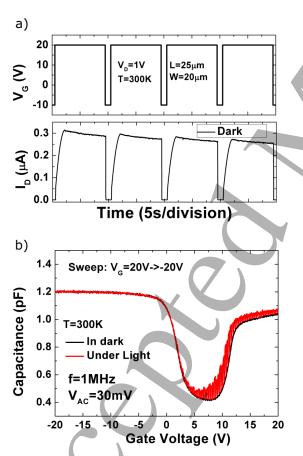

To further analyze this initial effect, devices are characterized under microscope white light conditions. Figure 4.a shows the response of the device to a sequence of successive positive gate voltage pulses (up to  $V_G = 20 \text{ V}$ ) starting from a negative bias  $(V_G = -10 \text{ V})$  (Figure 4.a, top). As observed, (Figure 4.a, bottom) the black curve depicts the behavior previously reported, an initial current increase followed by the expected current decay once the trapping effect dominates. However, under microscope white light conditions (red line), this first phenomenon is suppressed and only the characteristic decay, attributed to the trapping/detrapping phenomena, is observed. Successive pulses present lower current due to the overall threshold voltage shift to positive voltages (the recovery periods at  $V_G = -10 \text{ V}$  are shorter than the stress periods at  $V_G = 20 \text{ V}$ ). The same behavior is observed in the  $I_D - t$  characteristic at two different temperatures in Figure 4.b. The exposure

Figure 3. a) Transfer characteristic (absolute value) with double sweep (forward and backward) of a 50  $\mu$ m-length and 45  $\mu$ m-width device for different drain biases. b) Transfer characteristic for another device with a 50  $\mu$ m-length and 25  $\mu$ m-width as a function of the sweep delay time. Inset shows a zoom-in of the cross point area. c) Current hysteresis for different temperatures. d) I<sub>D</sub>-t characteristic when a positive gate voltage pulse is applied at t=0 s at different temperatures for the same device as in c). Energy diagram scheme of the trap behavior: e) When a positive voltage is applied at the back-gate. The bending of the energy bands allows traps (in the oxide and at the interface) to be filled with electrons once they are below the Fermi level; f) when a negative voltage is applied, the energy band bending makes electrons to escape from the traps.

to the light can generate electron-hole pairs when the energy of the light is larger than the semiconductor band-gap. The photogenerated excess of electrons can directly contribute to the current presenting a faster response to the voltage rise. This fact points to difficulties in the formation of the channel as the

origin of the aforementioned initial current increase.

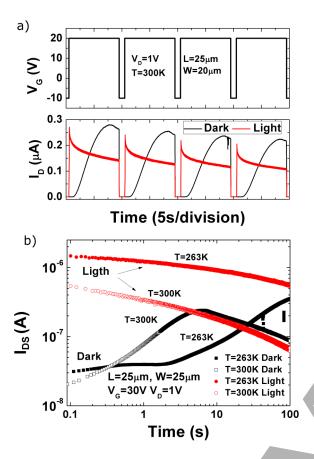

Capacitance-voltage (C-V) characterization is performed in order to gain further insight into the particular origin of the delay in the electron channel formation. This characterization is carried out directly on the fabricated MOSFET devices (Si/SiO<sub>2</sub>/MoS<sub>2</sub>),

Figure 4. a) Gate voltage pulsed response under dark and illumination conditions. b) Comparison of the  $I_D$ -t characteristic at high gate voltage for dark and illumination conditions at different temperatures.

where the force and low biases are applied at the Si substrate and at the drain contact, respectively (Inset Figure 5.a). Figure 5.a shows the gate capacitance measured through the structure at low temperature. Two frequencies (low, f = 1 kHz, and high, f = 1 MHz) are recorded both for double voltage sweep measurements. The structure presents a clear accumulation channel, a depletion region and almost no inversion channel corresponding to the electron carriers (positive voltages at the back gate). It should be noted that the measured maximum capacitance  $(C_{ox} = 1.24 \text{ pF})$  agrees with the theoretical oxide capacitance value  $(C_{ox})$  according to 100 nm-thick SiO<sub>2</sub> oxide and the area of the contact. The maximum capacitance at high frequency occurs for negative biases at the substrate (Figure 5.a), suggesting that the majority carriers are holes at the MoS<sub>2</sub>/SiO<sub>2</sub> interface and electrons at the SiO<sub>2</sub>/Si interface (in agreement with the n-type Si substrate). However, according to Figure 5.a, when positive voltages are applied at the back gate, the device is not able to form the inversion charge following the bias signal.

This result could be initially in agreement with the time associated to form an inversion layer of holes at the he Si/SiO<sub>2</sub> interface. Due to the n-type doping characteristic, holes have to be thermally generated, a slow process taking into account a highly crystalline Si layer. To form the inversion channel, minority carriers must be thermally generated in the spacecharge region (SCR) of the junctions and minority carrier generation lifetimes are manifestly longer than majority ones, presenting a slow generation rate and limiting the inversion charge response [73]. here that any of the two interfaces could impose the operation limit under these considerations, but initially the high quality n-type silicon substrate should present higher minority carrier lifetimes than the defective MoS<sub>2</sub> layer. If the source of the initial instability in the devices is the thermal generation of minorities, this effect can be relaxed by increasing the minority carrier density through higher temperature  $(n_i \text{ increases})$  or photo-generation conditions (photogenerated minority carriers). C-V characterization performed under microscope white light and high temperature conditions shown in Figure 5.b and Figure 5.c, respectively, validates this statement demonstrating that the photo (Figure 5.b) or thermal (Figure 5.c) generation enhance the inversion charge increasing the minority population. According to these results, the slow formation of the inversion layers, which requires time to thermally generate minority carriers, explains the initial current delay (current increase with time). Therefore, the observed current delay in the devices ( $\tau$  in Figure 3.d) can be related to the inversion layer formation (minority carrier should be thermally generated). Section Device instability in the Supplementary Material demonstrates that this delay is governed by a SHR mechanism with an energy activation of 0.64 eV above the valence band suggesting thermal generation of minorities through generationrecombination of electron-hole pairs thanks to states in the mid-gap state. Moreover, the measured  $\tau$  values (Figure 3.d) agree with the expected response time for minorities carriers in this doped silicon layer according to  $\tau=\tau_g\cdot N_A/n_i$  [74], where  $N_D=10^{15}$  cm<sup>-3</sup>,  $n_i=10^{10}$  cm<sup>-3</sup> and  $\tau_g$  between  $10^{-3}$  s and  $10^{-4}$  s for this specific doping level at room temperature [75].

The  $I_D$ - $V_G$  and C-V responses suggest that due to the limitation of high Schottky barriers blocking the holes current, the device should operate in inversionmode. Therefore, an electron channel should be formed entailed by the thermal generation of the minority carriers at the  $Si/SiO_2$  interface (holes). It is worth mentioning that due to this combination of phenomena the behavior of these devices corresponds to back-gated Schottky barrier field-effect transistors (SB-FET) operating with inversion channel rather

Figure 5. a) Capacitance-voltage (C-V) characteristics for two frequencies at low temperature and under dark conditions. b) C-V characteristic under microscope white light. Arrows indicate the sweep direction. c) C-V characteristic at high temperature under dark conditions. The black curve (the first measured) still presents an initial delay to reach the inversion layer. d) C-V characteristics for different structures with and without  $MoS_2$  layer on top under different light conditions at 313 K. e) Transfer characteristic of one fresh device, under vacuum and in atmospheric pressure (AP). f)  $I_D$ -t characteristic of the device in vacuum and air conditions.

than the usual n-type transistors (junctionless), widely reported in literature, presenting accumulation-mode operations [63, 69, 35, 32, 76, 17, 30]. Moreover, this operation ensures normally-off devices with potential

less power consumption than the normally-on ones, typically presented in literature.

However, due to the intriguing structure with two semiconductor interfaces further corroborations

should be carried out. Figure 5.d shows the C-V characteristic of one reference structure without  $MoS_2$  layer (in the same sample). As expected, the structure (Metal/SiO<sub>2</sub>/n-type Si) presents a clear ntype behavior with accumulation, depletion and almost no inversion. Note that the high potential (Inset in Figure 5.a) is applied at the silicon gate, therefore the curve should be reversed. These results agree with the previous calculations with a high frequency CV obtained for frequencies above  $1/\tau$  ( $\approx$  from 0.01 Hz to 0.1 Hz). However, the depletion of the substrate is reached at more positive voltages than in the devices presenting the MoS<sub>2</sub> layer, Figure 5.b and Figure 5.c. This fact points to the different charge density at the surface below the contacts. In this regard, when the MoS<sub>2</sub> layer is presented, red curve in Figure 5.d, the depletion regime shifts to the left. Interestingly, higher inversion is observed in this case. change in the C-V characteristic suggests additional mechanisms inducing unusual inversion channel at this high frequency (1 MHz). This effect is even clearer for a typical device with  $\mathrm{MoS}_2$  channel (Figure 5.d green curve). In this case, the maximum inversion capacitance is higher but the initial time  $\tau$  to reach this capacitance level (attributed to thermal generation of minorities) is still present. As expected, if a source of artificial light is applied (blue curve), the minority carrier density increases and the thermal generation is not necessary to achieve the maximum inversion capacitance which is approximately the same as in dark conditions. Therefore, the MoS<sub>2</sub> layer has an important role on the response of the device where, despite the limitation that the silicon layer imposes, the maximum inversion capacitance reached is controlled by the  $MoS_2$  layer. One possible explanation for this unexpected inversion level that the devices present at high frequency could reside in the charges and defects in the  $MoS_2$  layer (as demonstrated in the structural characterization) and at the top interface (not passivated). It is reported that inducing surface charge of the same type as the silicon doping (negative in this case of n-type substrate), it will induce a corresponding charge opposite sign in the semiconductor at the oxide/Si interface and will give rise to an inversion region in the peripheral area (called peripheral inversion) [77]. The presence of an inversion layer in an area outside the region defined by the gate, provides a source of minority carriers to the inversion region in the area defined by the gate, with a resulting ac inversion response, which does not originate from the generation of minority carriers. This effect is expected if the surface charge is higher than the semiconductor charge associated with the maximum depletion width,  $\approx 8 \cdot 10^{10} \text{ cm}^{-2} \text{ for } 10^{15} \text{ cm}^{-3} \text{ Si substrate doping}$

concentration [77], charge densities which within the range expected for a defective MoS<sub>2</sub> layer as suggested in the structural characterization. Moreover, this surface charge value could be in agreement with the calculated charge for the  $V_{FB}$  shift of 15 V ( $\approx 10^{12}$  $cm^{-2}$ ) observed in Figure 5.d when the MoS<sub>2</sub> layer is presented in the structure. The other possible explanation for the observed inversion capacitance behavior is the formation of the electron channel in the  $MoS_2$  layer being the limiting phenomenon in the device operation. It means that the MoS<sub>2</sub> layer also has to generate minority carriers (electrons) at the  $MoS_2/SiO_2$  interface, presenting a p-type behavior. However, due to the reported defective characteristic of the MoS<sub>2</sub> in these devices, shorter carrier minority lifetimes than in silicon are expected and therefore faster response. Despite this, it is worth noticing that if a perfect peripheral inversion is achieved in the silicon, the limiting factor should be the electron carrier generated in the  $MoS_2$ .

To study the influence of the surface charge density on the device operation, Figure 5.e shows the transfer characteristic under different ambient conditions. When the device is under vacuum conditions, the hysteresis cycle is narrower because, while the initial time in the formation of the channel prevails, the carrier trapping phenomenon at interface decreases, suggesting a reduction of active defects. However, once the device is under atmospheric pressure (AP), the second phenomenon takes over and a wider clockwise hysteresis appears. Figure 5.f shows the temporal comparison with the  $I_D$ -t curves in both under atmospheric pressure and vacuum conditions corroborating the surface charge density effect. The decay part of the curve falls more abruptly (higher power exponent) on the device exposed to atmospheric pressure than under vacuum conditions due to the presence of higher active trap density. This part of the curve fits perfectly with a time power law observed in silicon transistors which is attributed to hydrogen and other species diffusion generating oxide and interface states [33, 78, 79]. In MoS<sub>2</sub> devices, this widely reported behavior has been attributed to the trapping of carriers at interface and oxide defects produced by dissociative adsorption of oxygen on the defective surface of MoS<sub>2</sub>, moisture at room conditions and oxide species together with sulfur vacancies in the structure. However, the decreasing of active defects (and surface charges) under vacuum condition makes that the rising part of the curve takes more time to reach to the maximum current level  $(\tau)$ . This effect is consistent with less charge density at the surface resulting in a weaker peripheral inversion at the Si/SiO<sub>2</sub> interface and longer time to reach the same inversion charge density. Note that the higher current presented under

vacuum condition is due to the lower threshold voltage.

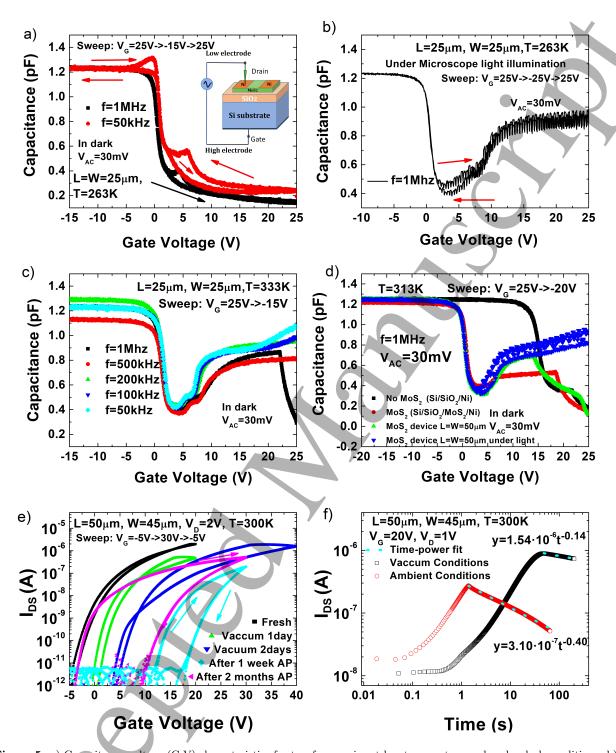

Final corroboration of the influence of the defects on MoS<sub>2</sub> top surface and at MoS<sub>2</sub>/SiO<sub>2</sub> interface on the operation and performance of the back-gated devices is demonstrated by fabricating and characterizing another sample grown under a slightly different synthesis process on the same Si substrates (additional synthesis data in the Supplementary Material). This sample presents a more defective MoS<sub>2</sub> layer where higher density of imperfections in the channel are easily discernible in the SEM characterization (Figure S4). The comparison with the previous sample also suggests a thinner MoS<sub>2</sub> layer (AFM profile, Figure 6.a shows the same pulses not shown). characterization as in Figure 4.a demonstrating shorter initial delay in this more defective sample. result is consistent with higher charge density on the surface inducing higher peripheral inversion level at the Si/SiO<sub>2</sub> interface. Additionally, capacitance-voltage

**Figure 6.** a) Gate voltage pulsed response under dark conditions for a more defective MoS<sub>2</sub> device. b) Capacitance-voltage (C-V) characteristics at room temperature under dark and microscope white light conditions (same device as shown in Figure 6.a).

characteristic of the same sample (Figure 6.b) presents a clear inversion channel even at room temperature and higher frequency. The capacitance in the inversion regime presents almost no differences between illuminated and not illuminated characterizations and the values are higher compared to the thicker MoS<sub>2</sub> device (Figure 5.c). A comparison is shown in Figure These results indicate that the magnitude of the capacitance in inversion is not limited by thermal generation of minority carriers in the silicon, but is provided by a peripheral source of inversion charge (see inset Figure 5.a) at the Si/SiO<sub>2</sub> interface. The density of this inversion charge at the  $\mathrm{Si}/\mathrm{SiO}_2$  interface is set by the negative charge density associated with the overlying  $MoS_2$ . This density of charge in the  $MoS_2$ (bulk and surface) can vary from sample to sample, and also varies with the ambient conditions (as shown in Figure 5.f).

As a final remark, the results described in this work highlight that these devices present: i) a Fermi level pinning at the metal/MoS<sub>2</sub> interface which blocks the hole current resulting in an n-channel behavior in the transfer characteristic; and ii) a net p-type structure which requires the formation of an electron channel due to the inversion of the interfaces, entailed by the thermal generation of minority carriers and/or the a supply of minority carriers in an area peripheral to the contacted area. In this process, the defect density and sign in the defective MoS<sub>2</sub> and at the surface of MoS<sub>2</sub> (not passivated) play an important role in the formation of the channel. However, the thermal generation of minority carriers in the silicon layer can still delay the channel formation modulating the current hysteresis in the device which is also affected by the trapping/detrapping of carriers. The fact that isolated mechanisms such as the trapping/detrapping phenomena, peripheral inversion and the thermal generation of minority carriers affect the current in these devices opens the way to modulate the device to operate in a mode which utilizes one or more of the mechanisms responsible for the transient response depending on the intended application. The results suggest that a relatively slow response which is strongly dependent upon light and temperature could be achieved with passivated and/or by non-defective  $MoS_2$  devices. Photo-detectors and temperature sensors could be the potential applications. the other hand, inducing negative charges on the surface, improves the channel inversion resulting in faster response. Such devices can also operate as bio or gas sensors. From the electronic point of view, the current device, made with large-area grown MoS<sub>2</sub> films, have demonstrated normally-off operation with potential low-power consumption and with electrical parameters such as mobility, on/off ratio and on-resistance comparable to reported parameters in literature.

# 3. Conclusions

Investigating the transient response of Schottky barrier back-gated MoS<sub>2</sub> transistors

The results in this work demonstrate that CVD grown MoS<sub>2</sub> MOSFETs can present a combination of a net p-type MoS<sub>2</sub> and Fermi level pinning at the metal/MoS<sub>2</sub> interface of the source and drain regions, where the pinning level is located in the upper half of the  $MoS_2$  energy gap. These combined effects result in a nominally-off MOSFET, which requires the formation of a n-type inversion region for the onstate condition. In this condition, the MoS<sub>2</sub> MOSFET illustrates a complex time dependent and hysteresis response which is determined by the net charge in the MoS<sub>2</sub> film, the trapping/detrapping effects and the minority carrier generation lifetime in the underlying silicon substrate. In this process the defects in the MoS<sub>2</sub> play an important role determining both the time to generate the n-type inversion layer in the  $MoS_2$  and the current decay due to carrier trapping. The connection of the net charge in the  $MoS_2$  to the device response time to a gate voltage pulse, occurs because the charge density and type in the  $MoS_2$  determines the corresponding charge density in the underlying silicon substrate. If the charge in the MoS<sub>2</sub> is negative, it creates a corresponding positive (inversion charge for n-type silicon) in the substrate, which can reduce, or potentially eliminate the time taken to form an inversion layer in the silicon, and also influences the hysteresis behaviour of the MOSFET. This interpretation is consistent with measurements under microscope white light, and increasing temperate, which both show a marked reduction in the device response time. Finally, measurements under vacuum and in air conditions demonstrate a marked change in the response time of the MoS<sub>2</sub> MOSFETs, consistent with the ambient impacting on the net charge density in the MoS<sub>2</sub> layer through interaction with oxygen, moisture and absorbates on the MoS<sub>2</sub> surface. Additionally, different samples have demonstrated that the device transient response following the application of a gate pulse is controllable by the defect density and by the MoS<sub>2</sub> growth parameters opening the door to engineer these mechanisms for specific target applications such as light-detector, gas or bio sensors.

#### Methods

## 3.1. Synthesis of $MoS_2$

Chemical vapor deposition through sulfurization of molybdenum trioxide  $(MoO_3)$  using elemental sulfur was carried out. The synthesis process for the  $MoS_2$  growth was as follows: two alumina crucibles, one containing 0.6 mg of  $MoO_3$  (Aldrich 99.5) and one containing 0.3 g of sulfur powder (Alfa 99.5) were

placed in a quartz process tube (2 inch diameter). The quartz tube was introduced into a two-zone furnace (PlanarTech) placing the sulfur crucible upstream and the  $MoO_3$  downstream. The substrate  $(10^{15} cm^{-3} n^{-3})$ type doped silicon covered by a 100 nm-thick thermal grown SiO<sub>2</sub> layer) was first cleaned with an IPA rinse followed by a piranha etch (three parts sulfuric acid to one part hydrogen peroxide) for 1 h. The pressure was set to 1 Torr during all the process. A flow of argon gas was initially used to purge the tube (300 sccm) for 20 min at room temperature and then 15 min to 150 °C in the MoO<sub>3</sub> stream. Afterthat, the argon flow was reduced to 100 sccm and the downstream and upstream furnaces were heated to 680 °C and 160 °C, respectively, as measured by a type-K thermocouple at the outer surface of the process tube. Growth time was 5 min for the MoS<sub>2</sub> film synthesis. Subsequently, the upstream furnace was turned off and the downward one was naturally cooled to 540 °C in 10 min followed by a fast cooling to room temperature in argon ambient.

#### 3.2. Device Fabrication

Firstly, the sample was spin-coated with standard lift-off and image resist, and photo lithography was employed to define the source and drain patterns. Then, electron beam evaporation was used to deposit the Ni/Au electrodes. The thicknesses of the Ni and Au were 20 nm and 200 nm, respectively. A lift-off process was carried out to complete contact fabrication of the  $\rm MoS_2$  FET. Then, a new resist layer was deposited and a dry etching of the  $\rm MoS_2$  material outside the channel between S/D contacts was carried out. Finally, the resist mask was removed.

#### 3.3. Experimental

The elemental composition analysis was carried out by fundamental X-ray photoelectron spectroscopy (XPS, Kratos Axis Ultra- DLD). Scanning electron microscope (SEM) characterization was performed in a FEI Quanta FEG 650 under high vacuum (0.1 mB) conditions using using an ETD (Everhart-Thornley Detector) for secondary electrons-topography. Raman spectra was obtained thanks to a Jasco NRS-5100 employing a 532 nm laser to excite the samples. A laser power of 4.4 mW with 30 s of exposure time with 5 accumulations were applied during the measurements. The topography and thickness of the MoS<sub>2</sub> samples were characterized using an atomic force microscope (NTMDT NTEGRA) in semicontact mode and with metallic tips. The air conditions electrical characteristics were measured in a semiautomatic Suss PA200 probe station with temperature capability. The low temperature characterization under vacuum conditions was carried out in cryogenic Lake Shore

59 60 Janis ST-500 probe station working with liquid nitrogen. The dc characteristic were recorded using a Keithley SCS 4200 and an Agilent B1500 systems. The capacitance-voltage (C-V) and conductance-voltage (G-V) measurements were performed using either an Agilent 4294A or CV enabled B1500 LCR meter (MFCMU).

#### Acknowledgments

This work was partly supported by Spanish National Program (grant No. TEC2017-89800-R), by ASCENT access to nanoelectronics infrastructure (EU Horizon 2020 programme grant No 654384), and Science Foundation Ireland, through the IvP award INVEST (SFI-15/IA/3131) and AMBER (12/RC/2278-P2). C.M. acknowledges the financial support from the Jose Castillejo mobility (grant No. CAS18/00460) and the University of Granada Plan Propio Programme 8.

### Supplementary Data

Supplementary material for this article is available online.

#### 4. ORCID iDs

Carlos Marquez https://orcid.org/0000-0003-0159-9951 Norberto Salazar https://orcid.org/0000-0002-0204-

Farzan Gity https://orcid.org/0000-0003-3128-1426 Carlos Navarro https://orcid.org/0000-0002-7846-4599 Gioele Mirabelli https://orcid.org/0000-0001-7060-4836

Jose C. Galdon https://orcid.org/0000-0003-3342-3627 Ray Duffy https://orcid.org/0000-0002-6362-3489 Santiago Navarro https://orcid.org/0000-0003-1868-7288

Paul K. Hurley https://orcid.org/0000-0001-5137-721X

Francisco Gamiz https://orcid.org/0000-0002-5072-7924

#### References

- [1] Novoselov K S, Geim A K, Morozov S V, Jiang D, Zhang Y, Dubonos S V, Grigorieva I V and Firsov A A 2004 Science **306** 666–9 ISSN 1095-9203

- [2] Novoselov K S, Jiang D, Schedin F, Booth T J, Khotkevich VV, Morozov SV and Geim AK 2005 Proceedings of the National Academy of Sciences 102 10451–10453 ISSN 0027-8424

- [3] Radisavljevic B, Radenovic A, Brivio J, Giacometti V and Kis A 2011 Nature Nanotechnology 6 147-150 ISSN 1748-3387

- [4] Chhowalla M, Jena D and Zhang H 2016 Nature Reviews Materials 1 16052 ISSN 2058-8437

- [5] Hu X, Tao J, Chen S, Xue J, Weng G, Kaijiang, Hu Z, Jiang J, Chen S, Zhu Z and Chu J 2018 Solar Energy Materials and Solar Cells 187 170-175 ISSN 09270248

- [6] Cao Y, Zhu X, Jiang J, Liu C, Zhou J, Ni J, Zhang J and Pang J 2020 Solar Energy Materials and Solar Cells 206  $110279 \ \mathrm{ISSN} \ 09270248$

- [7] Xia G T, Li C, Wang K and Li L W 2019 Science of Advanced Materials 11 1079-1086 ISSN 1947-2935

- [8] Zhou Y, Huang Y, Pang J and Wang K 2019 Journal of Power Sources 440 227149 ISSN 03787753

- [9] Shiue R J, Efetov D K, Grosso G, Peng C, Fong K C and Englund D 2017 Nanophotonics 6 1329-1342 ISSN 21928614

- [10] Lee H S, Min S W, Chang Y G, Park M K, Nam T, Kim H, Kim J H, Ryu S and Im S 2012 Nano Letters 12 3695-3700 ISSN 15306984

- [11] IRDS 2017 International Roadmap for Devices and

- Systems: Beyond CMOS

[12] Huang J K, Pu J, Hsu C L, Chiu M H, Juang Z Y, Chang

[14] The start T and Li L 12014 Y H, Chang W H, Iwasa Y, Takenobu T and Li L J 2014 ACS Nano 8 923-930 ISSN 19360851

- [13] Wang J, Yao Q, Huang C W, Zou X, Liao L, Chen S, Fan Z, Zhang K, Wu W, Xiao X, Jiang C and Wu W W 2016 Advanced Materials 8302-8308 ISSN 15214095

- [14] Illarionov Y Y, Smithe K K H, Waltl M, Knobloch T, Pop E and Grasser T 2017 IEEE Electron Device Letters 38 1763–1766 ISSN 0741-3106

- [15] Illarionov Y Y, Banshchikov A G, Polyushkin D K, Wachter S, Knobloch T, Thesberg M, Mennel L, Paur M, Stöger-Pollach M, Steiger-Thirsfeld A, Vexler M I, Waltl M, Sokolov N S, Mueller T and Grasser T 2019 Nature Electronics 2 230-235 ISSN 25201131

- [16] Illarionov Y Y, Banshchikov A G, Polyushkin D K, Wachter S, Knobloch T, Thesberg M, Vexler M I, Waltl M, Lanza M, Sokolov N S, Mueller T and Grasser T 2019 2D Materials 6 045004 ISSN 2053-1583

- Das S, Chen H Y, Penumatcha A V and Appenzeller J 2013 Nano Letters 13 100-105 ISSN 15306984

- [18] Liu Y, Guo J, Zhu E, Liao L, Lee S j, Ding M, Shakir I, Gambin V, Huang Y and Duan X 2018 Nature 557 696-700 ISSN 0028-0836

- [19]Bhattacharjee S, Ganapathi K L, Nath D N and Bhat N 2016 IEEE Transactions on Electron Devices 63 2556-2562 ISSN 0018-9383

- [20] Bhattacharjee S, Vatsyayan R, Ganapathi K L, Ravindra P, Mohan S and Bhat N 2019 Advanced Electronic Materials 5 1–6 ISSN 2199160X

- [21] Datye I M, Gabourie A J, English C D, Smithe K K H, McClellan C J, Wang N C and Pop E 2018 2D Materials 6 011004 ISSN 2053-1583

- [22] Zhang K, Bersch B M, Joshi J, Addou R, Cormier C R, Zhang C, Xu K, Briggs N C, Wang K, Subramanian S, Cho K, Fullerton-Shirey S, Wallace R M, Vora P M and Robinson J A 2018 Advanced Functional Materials 28 1-7 ISSN 16163028

- [23] Mouri S, Miyauchi Y and Matsuda K 2013 Nano Letters **13** 5944–5948 ISSN 15306984

- [24] Yang L, Majumdar K, Liu H, Du Y, Wu H, Hatzistergos M, Hung PY, Tieckelmann R, Tsai W, Hobbs C and Ye P D 2014 Nano Letters 14 6275–6280 ISSN 1530-6984

- [25] Wu S, Zeng Y, Zeng X, Wang S, Hu Y, Wang W, Yin S, Zhou G, Jin W, Ren T, Guo Z and Lu J 2019 2D Materials 6 025007 ISSN 2053-1583

- $[26]\ Zhang\ T,$  Wang Y, Xu J, Chen L, Zhu H, Sun Q, Ding S and Zhang D W 2017 2D Materials 5 015028 ISSN 2053-1583

- [27] Ashokbhai Patel K, Grady R W, Smithe K K H, Pop E and Sordan R 2019 2D Materials 7 015018 ISSN 2053-1583

- [28] Bolshakov P, Khosravi A, Zhao P, Hurley P K, Hinkle C L, Wallace R M and Young C D 2018 Applied Physics Letters 112 253502 ISSN 0003-6951

[29] Liu H and Ye P D 2012 IEEE Electron Device Letters 33 546–548 ISSN 07413106

Investigating the transient response of Schottky barrier back-gated MoS<sub>2</sub> transistors

- [30] Fang N and Nagashio K 2018 ACS Applied Materials & Interfaces 10 32355–32364 ISSN 1944-8244

- [31] Colinge J P, Lee C W, Afzalian A, Akhavan N D, Yan R, Ferain I, Razavi P, O'neill B, Blake A, White M et al. 2010 Nature nanotechnology 5 225

- [32] Late D J, Liu B, Matte H S S R, Dravid V P and Rao C N R 2012 ACS Nano **6** 5635–5641 ISSN 1936-0851

- [33] Illarionov Y Y, Rzepa G, Waltl M, Knobloch T, Grill A, Furchi M M, Mueller T and Grasser T 2016 2D Materials 3 035004 ISSN 2053-1583

- [34] Di Bartolomeo A, Genovese L, Foller T, Giubileo F, Luongo G, Croin L, Liang S J, Ang L K and Schleberger M 2017 Nanotechnology 28 214002 ISSN 0957-4484

- [35] Di Bartolomeo A, Genovese L, Giubileo F, Iemmo L, Luongo G, Foller T and Schleberger M 2017 2D Materials 5 015014 ISSN 2053-1583

- [36] Zhao P, Padovani A, Bolshakov P, Khosravi A, Larcher L, Hurley P K, Hinkle C L, Wallace R M and Young C D 2019 ACS Applied Electronic Materials 1 1372–1377 ISSN 2637-6113

- [37] Takenaka M, Ozawa Y, Han J and Takagi S 2017 Technical Digest - International Electron Devices Meeting, IEDM 5.8.1–5.8.4 ISSN 01631918

- [38] Urban F, Giubileo F, Grillo A, Iemmo L, Luongo G, Passacantando M, Foller T, Madauß L, Pollmann E, Geller M P, Oing D, Schleberger M and Di Bartolomeo A 2019 2D Materials 6 ISSN 20531583

- [39] Kaushik N, Mackenzie D M A, Thakar K, Goyal N, Mukherjee B, Boggild P, Petersen D H and Lodha S 2017 npj 2D Materials and Applications 1 34 ISSN 2397-7132

- [40] Mirabelli G, Hurley P K and Duffy R 2019 Semiconductor Science and Technology 34 055015 ISSN 0268-1242

- [41] KC S, Longo R C, Addou R, Wallace R M and Cho K 2014 Nanotechnology 25 375703 ISSN 0957-4484

- [42] Zhou W, Zou X, Najmaei S, Liu Z, Shi Y, Kong J, Lou J, Ajayan P M, Yakobson B I and Idrobo J C 2013 Nano Letters 13 2615–2622 ISSN 1530-6984

- [43] Hong J, Hu Z, Probert M, Li K, Lv D, Yang X, Gu L, Mao N, Feng Q, Xie L, Zhang J, Wu D, Zhang Z, Jin C, Ji W, Zhang X, Yuan J and Zhang Z 2015 Nature Communications 6 1–8 ISSN 20411723

- [44] Lee Y H, Zhang X Q, Zhang W, Chang M T, Lin C T, Chang K D, Yu Y C, Wang J T W, Chang C S, Li L J and Lin T W 2012 Advanced Materials 24 2320–2325 ISSN 09359648

- [45] Li H, Zhang Q, Yap C C R, Tay B K, Edwin T H T, Olivier A and Baillargeat D 2012 Advanced Functional Materials 22 1385–1390 ISSN 1616301X

- [46] Liu Y J, Hao L Z, Gao W, Liu Y M, Li G X, Xue Q Z, Guo W Y, Yu L Q, Wu Z P, Liu X H, Zeng H Z and Zhu J 2015 RSC Advances 5 74329–74335 ISSN 2046-2069

- [47] Chen J and Wang C 1974 Solid State Communications 14 857–860 ISSN 00381098

- [48] Mignuzzi S, Pollard A J, Bonini N, Brennan B, Gilmore I S, Pimenta M A, Richards D and Roy D 2015 Physical Review B - Condensed Matter and Materials Physics 91 195411 ISSN 1550235X

- [49] Frey G L, Tenne R, Matthews M J, Dresselhaus M S and Dresselhaus G 1999 Physical Review B 60 2883–2892 ISSN 0163-1829

- [50] Golasa K, Grzeszczyk M, Bożek R, Leszczyński P, Wysmołek A, Potemski M and Babiński A 2014 Solid State Communications 197 53–56 ISSN 00381098

- [51] Schrader G and Cheng C 1983 Journal of Catalysis 80 369– 385 ISSN 00219517

- [52] Park W, Baik J, Kim T Y, Cho K, Hong W K, Shin H J and Lee T 2014 ACS Nano 8 4961–4968 ISSN 1936086X

- [53] Hussain S, Singh J, Vikraman D, Singh A K, Iqbal M Z,

- Khan M F, Kumar P, Choi D C, Song W, An K S, Eom J, Lee W G and Jung J 2016 Scientific Reports 6 1–13 ISSN 20452322

- [54] Xia P, Feng X, Ng R J, Wang S, Chi D, Li C, He Z, Liu X and Ang K W 2017 Scientific Reports 7 40669 ISSN 2045-2322

- [55] Kim I S, Sangwan V K, Jariwala D, Wood J D, Park S, Chen K S, Shi F, Ruiz-Zepeda F, Ponce A, Jose-Yacaman M, Dravid V P, Marks T J, Hersam M C and Lauhon L J 2014 ACS Nano 8 10551–10558 ISSN 1936086X

- [56] Salazar N, Beinik I and Lauritsen J V 2017 Physical Chemistry Chemical Physics 19 14020–14029 ISSN 1463-9076

- [57] Lince J R, Hilton M R and Bommannavar A S 1990 Surface and Coatings Technology 43-44 640-651 ISSN 02578972

- [58] Fleischauer P D and Lince J R 1999 Tribology International 32 627–636 ISSN 0301679X

- [59] Muratore C, Hu J J, Wang B, Haque M A, Bultman J E, Jespersen M L, Shamberger P J, McConney M E, Naguy R D and Voevodin A A 2014 Applied Physics Letters 104 261604 ISSN 0003-6951

- [60] Schottky W 1939 Zeitschrift for Physik 113 367–414 ISSN 1434-6001

- [61] N F Mott 1939 Proceedings of the Royal Society of London. Series A. Mathematical and Physical Sciences 171 27– 38

- [62] Sze S and Ng K 2006 Metal-Semiconductor Contacts Physics of Semiconductor Devices (Hoboken, NJ, USA: John Wiley & Sons, Inc.) pp 134–196

- [63] Di Bartolomeo A, Grillo A, Urban F, Iemmo L, Giubileo F, Luongo G, Amato G, Croin L, Sun L, Liang S j and Ang L K 2018 Advanced Functional Materials 28 1800657 ISSN 1616301X

- [64] Howell S L, Jariwala D, Wu C C, Chen K S, Sangwan V K, Kang J, Marks T J, Hersam M C and Lauhon L J 2015 Nano Letters 15 2278–2284 ISSN 15306992

- [65] Farmanbar M and Brocks G 2015 Physical Review B -Condensed Matter and Materials Physics 91 1–5 ISSN 1550235X

- [66] Kang J, Liu W, Sarkar D, Jena D and Banerjee K 2014 Physical Review X 4 031005 ISSN 2160-3308 (Preprint 0807.1678)

- [67] Shen P C, Lin Y, Wang H, Park J H, Leong W S, Lu A Y, Palacios T and Kong J 2018 IEEE Transactions on Electron Devices 65 4040–4052 ISSN 0018-9383

- [68] Knobloch T, Rzepa G, Illarionov Y Y, Waltl M, Schanovsky F, Stampfer B, Furchi M M, Mueller T and Grasser T 2018 IEEE Journal of the Electron Devices Society 6 972–978 ISSN 21686734

- [69] Zhao P, Azcatl A, Gomeniuk Y Y, Bolshakov P, Schmidt M, McDonnell S J, Hinkle C L, Hurley P K, Wallace R M and Young C D 2017 ACS Applied Materials and Interfaces 9 24348–24356 ISSN 19448252

- [70] Illarionov Y Y, Knobloch T, Waltl M, Rzepa G, Pospischil A, Polyushkin D K, Furchi M M, Mueller T and Grasser T 2017 2D Materials 4 025108 ISSN 2053-1583

- [71] Qiu H, Pan L, Yao Z, Li J, Shi Y and Wang X 2012 Applied Physics Letters 100 123104 ISSN 0003-6951

- [72] Shu J, Wu G, Guo Y, Liu B, Wei X and Chen Q 2016 Nanoscale 8 3049–3056 ISSN 20403372

- [73] Schroder D K 2005 Semiconductor Material and Device Characterization: Third Edition 3rd ed (John Wiley & Sons) ISBN 0471739065

- [74] Nayak P, Seacrist M and Schroder D K 2011 IEEE Electron Device Letters 32 1659–1661 ISSN 0741-3106

- [75] del Alamo J A and Swanson R M 1987 Solid-State Electronics 30 1127–1136 ISSN 00381101

- [76] Hu Y, Jiang H, Lau K M and Li Q 2018 Semiconductor Science and Technology 33 045004 ISSN 13616641

- [77] O'Connor É, Cherkaoui K, Monaghan S, O'Connell D,

Investigating the transient response of Schottky barrier back-gated  $MoS_2$  transistors

- [78] Schroder D K 2007 Microelectronics Reliability 47 841–852

- [79] Marquez C, Rodriguez N, Fernandez C, Ohata A, Gamiz