| Title                   | Semiconductor nanowire fabrication via bottom-up & top-down paradigms                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Authors                 | Hobbs, Richard G.                                                                                                                    |

| Publication date        | 2011-10                                                                                                                              |

| Original Citation       | Hobbs, R.G., 2011. Semiconductor nanowire fabrication via<br>bottom-up & top-down paradigms. PhD Thesis, University College<br>Cork. |

| Type of publication     | Doctoral thesis                                                                                                                      |

| Rights                  | © 2011, Richard G. Hobbs - http://creativecommons.org/licenses/<br>by-nc-nd/3.0/                                                     |

| Download date           | 2025-08-17 02:53:21                                                                                                                  |

| Item downloaded<br>from | https://hdl.handle.net/10468/535                                                                                                     |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

## Semiconductor Nanowire Fabrication via Bottom-

## **Up & Top-Down Paradigms**

Richard George Hobbs, BSc. (Hons)

Department of Chemistry,

University College Cork,

Ireland.

Coláiste na hOllscoile Corcaigh, Éire University College Cork, Ireland

## Presented for the PhD. Degree to the National University of

Ireland

Supervisor

**Dr. Justin D. Holmes**

October 2011

Declaration

I, Richard George Hobbs, certify that this Thesis is my own work and I have not obtained a degree in this University or elsewhere on the basis of this PhD Thesis.

Richard George Hobbs

#### Abstract

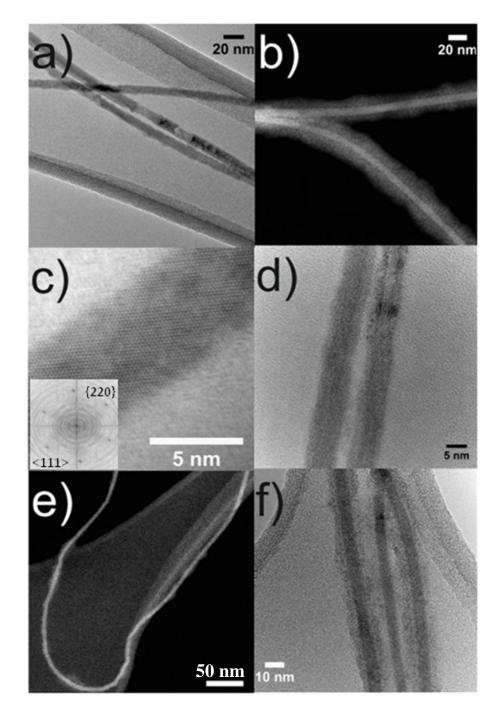

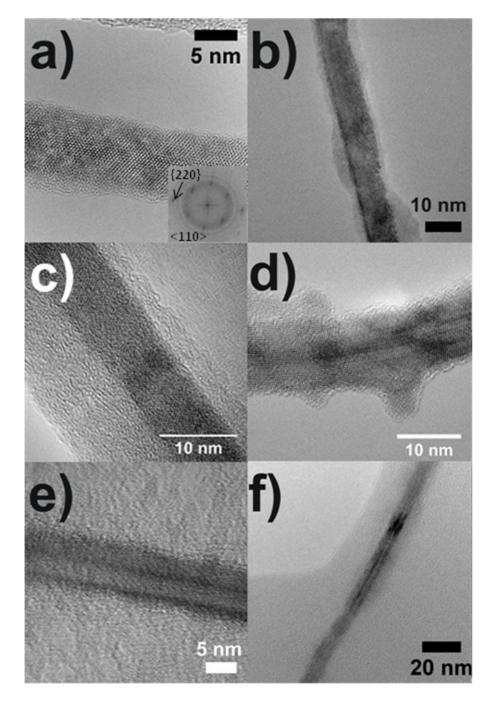

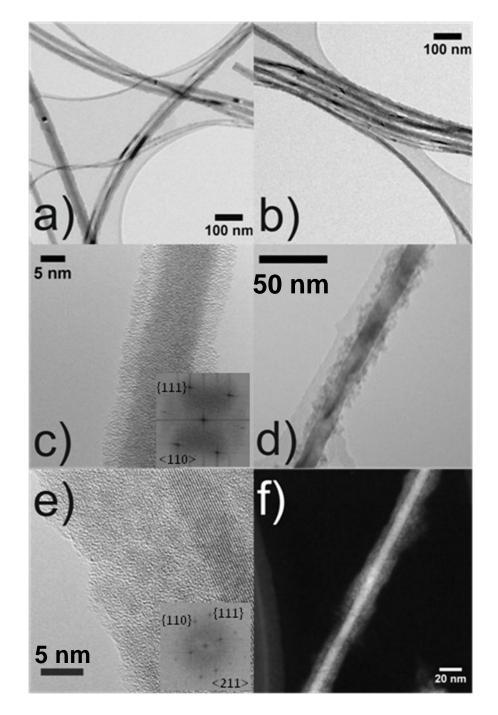

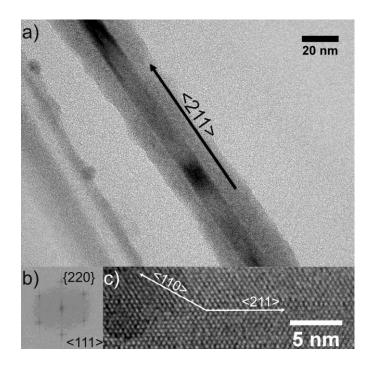

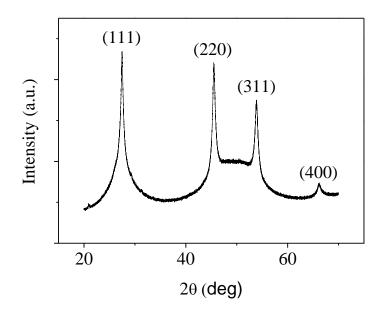

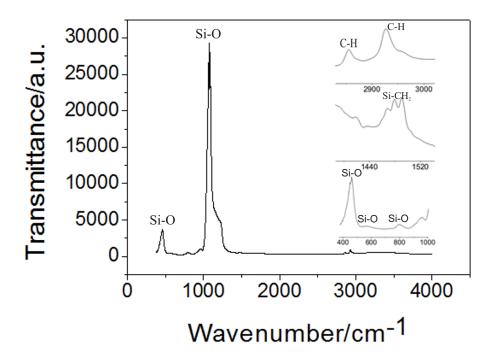

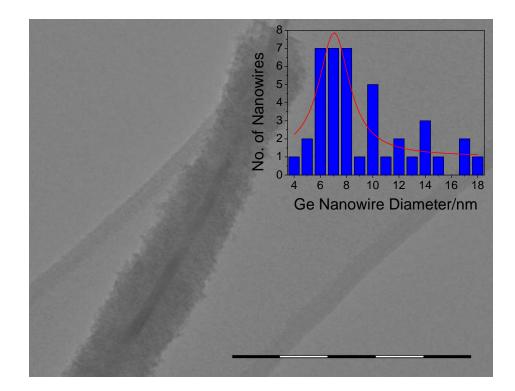

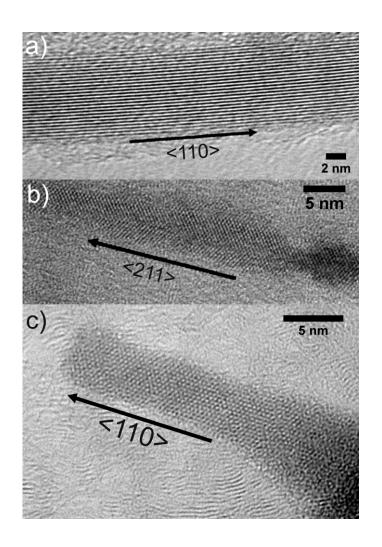

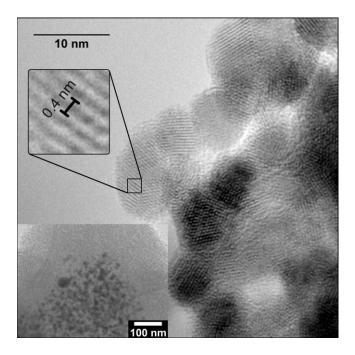

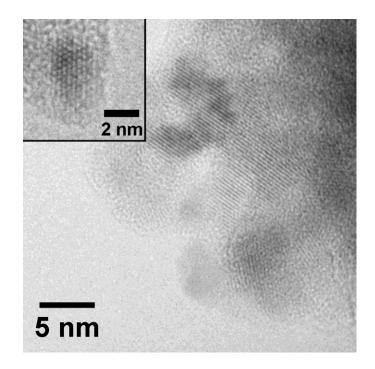

Semiconductor nanowires are pseudo 1-D structures where the magnitude of the semiconducting material is confined to a length of less than 100 nm in two dimensions. Semiconductor nanowires have a vast range of potential applications, including electronic (logic devices, diodes), photonic (laser, photodetector), biological (sensors, drug delivery), energy (batteries, solar cells, thermoelectric generators), and magnetic (spintronic, memory) devices. Semiconductor nanowires can be fabricated by a range of methods which can be categorised into one of two paradigms, bottom-up or top-down. Bottom-up processes can be defined as those where structures are assembled from their sub-components in an additive fashion. Top-down fabrication strategies use sculpting or etching to carve structures from a larger piece of material in a subtractive fashion. This thesis details a number of novel routes to fabricate semiconductor nanowires by both bottom-up and top-down paradigms. Chapter 3 describes a novel bottom-up route to fabricate Ge nanowires with controlled diameter distributions in the absence of a foreign metal catalyst. The nanowires produced by the method outlined in chapter 3 consist of highly crystalline Ge nanowire cores encapsulated in a shell of amorphous Si-based material derived from the hexakis(trimethylsilyl)digermane precursor compound. Furthermore, the diameter of the Ge nanowire core was found to be related to the nanowire synthesis temperature, and as such the nanowire diameter distribution may be controlled by careful control of the synthesis temperature.

Hydrogen silsesquioxane (HSQ) is a high resolution, negative tone, inorganic electron beam lithography (EBL) resist which is capable of producing features with

sub-10 nm dimensions on Si substrates. However, the use of HSQ to pattern non-Si based materials is less well developed. Chapter 4 outlines the importance of surface chemistry in high-resolution EBL using HSQ to fabricate arrays of Ge and Bi<sub>2</sub>Se<sub>3</sub> nanowires. Finally, Chapter 5 describes the use of a high-resolution EBL process to produce arrays of Si nanowires from silicon-on-insulator (SOI) substrates. Additionally, chapter 5 details a process to create templates for the directed self-assembly of a diblock copolymer, in this case polystyrene-*b*-polydimethylsiloxane. Directed self-assembly of diblock copolymers is of interest for advanced lithography applications, whereby pattern multiplication can be achieved within sparsely patterned templates by directed self-assembly of suitable diblock copolymers.

#### Acknowledgments

First and foremost let me state my profound thanks to my supervisor, Dr. Justin Holmes, for his pragmatic and unintrusive style of guidance. He was always available when advice was required and when blind panic obstructed logic he was the voice of sense.

Next, I must offer by deepest thanks to Nikolay for his creativity and endless streams of suggestions, without which I would have been in danger of getting a moments peace. He is a very talented scientist and future generations of students could do well to pay attention to 50% of his ideas (the 50% that stand a chance of working).

I have been privileged to have had access to a number of outstanding consultants in my time at U.C.C., each with their own wealth of expertise, and all of whom have gone beyond the call of duty in their advice and time that they have devoted to me during my PhD studies. I would like to thank each of these consultants for their support and friendship, to Yordan, Sven, Richie, Michael, and Ran, thank you.

I have been lucky to have had access to the support and skills of a number of talented engineers during the course of my research studies, these include Richard Murphy, Vladimir, Kohsin, Brendan McCarthy, Brendan O'Neill, Dan O'Connell, Alan Blake, Joe O'Brien, John Pike, Carmel Murphy, Krimo, Markus Boese, Matt Shaw and Calum Dickinson. Likewise, I have benefitted greatly from the advice and help afforded me by so many others. Let me thank all those at Tyndall that I have gotten to know over the past few years for their kindness and helpful discussions. I would also like to sincerely thank my collaborators for their great efforts, discussions and support, Faxi, and Prof. Wang at U.C.L.A., Stephen and Vojislav at CRANN, Olga at NPL and J-P at Tyndall, thank you all for your support. Additionally, I would like to thank our neighbours in Lab 343 for their enthusiasm and support throughout my term at U.C.C.

I must also thank the 115 alumni for the great times during those formative years of my PhD, thanks to Jubo, John O'Callaghan, Pal Delaney, Joe, Kamil, Machteld, Tricky Dicky Phelan, Tim Gabriel, Gill, Arun and Donna Arnold. Also, the 343 alumnists, Pete, Keith, Lacky McMadman, Mahony, Tom and Louise.

To my friends and colleagues in 115 I would like to thank you for all the laughs and discussions that we have had, thanks to Olan, Mark, Justin 'Nani' Varghese, Subha, Dave, and Colm O'Reganator.

Thanks to all the staff in the Chemistry department for their endless reserves of 'favours' and 'loans'. Thanks to the fellas banging next door, Johnny, Mick and Tony, and to the girls in the office, Christine, Colette, Claire, Eileen, and Mary. Many thanks to Pat, Terry, Donal, Rose, Agnes, Derry, Donncha, Tina, Chrissie, Noel, Trev and Mattie for bringing life to the dullest building on campus, you were all great friends to me and everyone in the group.

Lastly, I would like to thank those who chased my blues away and made the stress of doing a PhD, whilst running one of one of the biggest clubs in the university that bit more bearable. To my parents Margaret and Winston, thank you for your patience, love and support and for allowing me opportunities that you were not. To Ciara, I thank you for the balance that you brought to so many days and for your seemingly limitless kind words, you have been a great source of strength to me and I couldn't have asked for more.

Dedicated to my parents

### **Table of Contents**

| Declarationii                                                                             |

|-------------------------------------------------------------------------------------------|

| Abstractiii                                                                               |

| Acknowledgementsv                                                                         |

| 1. Introduction1                                                                          |

| 1.1. Semiconductor Nanowires2                                                             |

| 1.2. Bottom-Up Semiconductor Nanowire Fabrication4                                        |

| 1.2.1. Semiconductor Nanowire Growth Methods4                                             |

| 1.2.2. Nanowire Alignment Techniques7                                                     |

| 1.2.3. Vertical Nanowire Field Effect Transistors10                                       |

| 1.2.4. Bottom-Up Semiconductor Nanowire Outlook                                           |

| 1.3. Top-Down Semiconductor Nanowire Fabrication15                                        |

| 1.3.1. Optical Lithography15                                                              |

| 1.3.2. Next Generation Lithography: Electron Beam Lithography and Competing Techniques 20 |

| 1.3.3. Top-Down Semiconductor Nanowire Fabrication Outlook                                |

| 1.4. Integration of Bottom-Up and Top-Down Nanowire                                       |

| Fabrication Processes29                                                                   |

| 1.4.1. Directed Self-Assembly                                                             |

| 1.4.2. EBL Catalyst Placement for Bottom-Up Nanowire Growth                               |

| 1.4.3. Nanosphere Lithography                                                             |

| 1.5. Emerging Semiconductor Nanowire Materials                                                                                                                                                                                                                                       | 41                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1.5.1. High Mobility Materials for Next Generation CMOS Devices                                                                                                                                                                                                                      | 41                                           |

| 1.5.2. Thermoelectric Nanowires                                                                                                                                                                                                                                                      | 44                                           |

| 1.6. Nanowire Fabrication Outlook                                                                                                                                                                                                                                                    | 45                                           |

| 1.7. Thesis Summary                                                                                                                                                                                                                                                                  | 46                                           |

| 1.8. Bibliography                                                                                                                                                                                                                                                                    | 47                                           |

| 2. Experimental                                                                                                                                                                                                                                                                      | 59                                           |

| 2.1. Self-Seeded Supercritical Fluid (SCF) Phase                                                                                                                                                                                                                                     |                                              |

| Synthesis of Ge Nanowires                                                                                                                                                                                                                                                            | 60                                           |

|                                                                                                                                                                                                                                                                                      |                                              |

| 2.2. Self-Seeded Solution Phase Synthesis of Ge                                                                                                                                                                                                                                      |                                              |

|                                                                                                                                                                                                                                                                                      |                                              |

| 2.2. Self-Seeded Solution Phase Synthesis of Ge                                                                                                                                                                                                                                      | 62                                           |

| 2.2. Self-Seeded Solution Phase Synthesis of Ge<br>Nanowires                                                                                                                                                                                                                         | 62                                           |

| <ul> <li>2.2. Self-Seeded Solution Phase Synthesis of Ge<br/>Nanowires</li> <li>2.3. Electron Beam Lithography</li> </ul>                                                                                                                                                            | 62<br>64                                     |

| <ul> <li>2.2. Self-Seeded Solution Phase Synthesis of Ge<br/>Nanowires</li> <li>2.3. Electron Beam Lithography</li> <li>2.3.1. Background</li> </ul>                                                                                                                                 | 62<br>64<br>64                               |

| <ul> <li>2.2. Self-Seeded Solution Phase Synthesis of Ge<br/>Nanowires</li></ul>                                                                                                                                                                                                     | 62<br>64<br>64<br>68<br>73                   |

| <ul> <li>2.2. Self-Seeded Solution Phase Synthesis of Ge<br/>Nanowires</li></ul>                                                                                                                                                                                                     | 62<br>64<br>64<br>68<br>73<br>76             |

| <ul> <li>2.2. Self-Seeded Solution Phase Synthesis of Ge<br/>Nanowires</li> <li>2.3. Electron Beam Lithography</li> <li>2.3.1. Background</li> <li>2.3.2. PMMA Positive-Tone EBL</li> <li>2.3.3. Hydrogen Silsesquioxane Negative-Tone EBL</li> <li>2.3.4. Ge Patterning.</li> </ul> | 62<br>64<br>64<br>                           |

| <ul> <li>2.2. Self-Seeded Solution Phase Synthesis of Ge<br/>Nanowires.</li> <li>2.3. Electron Beam Lithography</li></ul>                                                                                                                                                            | 62<br>64<br>64<br>64<br>73<br>76<br>77<br>78 |

| 2.4.1. | X-ray Diffraction                | 83 |

|--------|----------------------------------|----|

| 2.4.2. | Electron Microscopy              | 84 |

| 2.4.3. | X-ray Photoelectron Spectroscopy | 86 |

| 2.4.4. Fourier Transform Infrared Spectroscopy                      | 87        |

|---------------------------------------------------------------------|-----------|

| 2.5. Bibliography                                                   | 88        |

| 3. Self-Seeded Growth of Sub-10 nm Germa                            | nium      |

| Nanowires                                                           | 91        |

| 3.1. Abstract                                                       | 92        |

| 3.2. Germanium Nanowire Growth                                      | 92        |

| 3.3. Results                                                        | 97        |

| 3.4. Conclusions                                                    | 126       |

| 3.5. Bibliography                                                   | 127       |

| 4. Resist-Substrate Interface Tailoring for G                       | enerating |

| High Density Arrays of Ge and Bi <sub>2</sub> Se <sub>3</sub> Nanov | vires by  |

| Electron Beam Lithography                                           | 131       |

| 4.1. Abstract                                                       | 132       |

| 4.2. Introduction                                                   | 132       |

| 4.2.1. Hydrogen Silsesquioxane                                      |           |

| 4.2.2. Germanium                                                    |           |

| 4.2.3. Bismuth Selenide                                             |           |

| 4.3. Results                                                        | 135       |

| 4.3.1. Ge Lithography                                               |           |

| 4.3.2. Bi <sub>2</sub> Se <sub>3</sub> Lithography                  | 146       |

| 4.4. Conclusions151                                  |

|------------------------------------------------------|

| 4.5. Bibliography152                                 |

| 5. High Resolution Electron Beam Lithography for the |

| Fabrication of Si Nanowire Arrays and the Directed   |

| Self Assembly of Block Copolymers 154                |

| 5.1. Abstract155                                     |

| 5.2. Introduction155                                 |

| 5.3. Fabrication of Si Nanowire Arrays157            |

| 5.4. Directed Self-Assembly of PS-b-PDMS161          |

| 5.4. Conclusions167                                  |

| 5.5. Bibliography168                                 |

| 6. Conclusions170                                    |

| 6.1. Conclusions171                                  |

| 6.2. Bibliography175                                 |

# Chapter 1

# Introduction

"....whoever could make two ears of corn, or two blades of grass, to grow upon a spot of ground where only one grew before, would deserve better of mankind, and do more essential service to his country, than the whole race of politicians put together."

Jonathan Swift, Gulliver's Travels, 1726.

#### **1.1. Semiconductor Nanowires**

Semiconductor nanowires are pseudo 1-D structures where the magnitude of the semiconducting material is confined to a length of less than 100 nm in two dimensions. Semiconductor nanowires have a vast range of potential applications<sup>1</sup>, including electronic (logic devices, diodes)<sup>2</sup>, photonic (laser, photodetector)<sup>3–5</sup>, biological (sensors, drug delivery)<sup>6</sup>, energy (batteries, solar cells, thermoelectric generators)<sup>7,8</sup>, and magnetic (spintronic, memory)<sup>9–11</sup> devices. Semiconductor nanowires can be fabricated by a range of methods which can be categorised into one of two paradigms, bottom-up or top-down. Bottom-up processes can be defined as those where structures are assembled from their sub-components in an additive fashion. Top-down fabrication strategies use sculpting or etching to carve structures from a larger piece of material in a subtractive fashion. The challenge of continuous microelectronic device scaling to meet industry targets, *e.g.* 'Moore's Law'<sup>12</sup>, and the diversification of the microelectronics industry into new materials for specialised applications ('More than Moore')<sup>12</sup>, has motivated research in semiconductor

nanowires for the past number of decades. The massive competition for a share of the global 304 billion USD semiconductor market<sup>13</sup>, has driven the expansion of the semiconductor nanowire research area, resulting in the evolution of, new fabrication techniques, innovative processes, new materials and creative advancements in semiconductor nanowire device design.

This chapter aims to summarise and compartmentalise the various approaches taken by both the bottom-up and top-down paradigms in this field, whilst identifying potential spaces in which both top-down and bottom-up approaches may be used in tandem. Primarily, this chapter will focus on Si and promising high charge carrier mobility materials for logic device applications, although other noteworthy applications of semiconductor nanowires and nanoribbons for other applications will be discussed.

Firstly, the major fabrication routes to production of semiconductor nanowires in both paradigms will be discussed, whilst identifying recent advances and highlighting the benefits and drawbacks of these routes. The synergistic use of both top-down and bottom-up approaches to produce structures unattainable by either route alone will also be considered. Next, the most promising materials for high mobility logic device fabrication will be considered. The current issues with processing these materials within each fabrication paradigm will also be addressed. Lastly, the application of semiconductor nanowires in the field of thermoelectric materials will be discussed with respect to their use in energy recovery applications.

#### **1.2. Bottom-Up Semiconductor Nanowire Fabrication**

#### 1.2.1. Semiconductor Nanowire Growth Methods

Numerous routes exist to the bottom-up fabrication of semiconductor nanowires. The vapour-liquid-solid (VLS) mechanism and analogues thereof, is the most commonly used route to semiconductor nanowire production.<sup>14,15,1</sup> The VLS mechanism relies on a vapour phase precursor of the nanowire material which impinges on a liquid phase seed particle, from which unidirectional nanowire growth proceeds. The choice of an appropriate seed material has the benefit of allowing control over the diameter of the nanowires produced, whilst the seed material can also significantly affect the crystalline quality of the nanowire.<sup>16,17</sup> At this point, the importance of selection of an appropriate precursor material should be highlighted. Within a given precursor, MR<sub>x</sub>, where 'M' represents the semiconductor element, or elemental component of a compound semiconductor, and 'R', represents a protecting group, the M-R bond should be sufficiently labile under nanowire synthesis conditions to liberate reactive M species for nanowire growth. Furthermore, the R group liberated upon precursor decomposition should ideally exist as a gas phase species to prevent contamination of the nanowire product with liquid or solid phase by-product. Consequently, metal hydrides are often used as precursor compounds for nanowire growth, as H<sub>2</sub> gas is an especially clean by-product which has the benefit of inhibiting undesirable oxide formation for non-oxide semiconductor nanowire growth. Metal hydride precursors are commonly used in the growth of nanowires by chemical vapour deposition (CVD), given that metal hydrides such as SiH<sub>4</sub> and GeH<sub>4</sub> generally exist as gas phase compounds<sup>18</sup>. Metal-organic precursors, such as diphenylsilane and diphenylgermane, often used in solution phase and supercritical fluid phase nanowire synthesis can produce carbonaceous by-products

which may be difficult to completely separate from the nanowire product.<sup>19,20</sup> Semiconductor nanowire synthesis conditions often encourage the formation of reactive radical species which can initiate polymerisation reactions resulting in unwanted contaminating by-products,<sup>21</sup> and as such, precursor design should always be considered when designing an experiment for semiconductor nanowire synthesis. Analogues of the VLS mechanism include supercritical fluid-liquid-solid (SFLS)<sup>15</sup>, solution-liquid-solid (SLS)<sup>22</sup>, vapour-solid-solid (VSS)<sup>23,24</sup> and oxide assisted growth (OAG)<sup>25</sup> mechanisms. Common to all of these analogues is the existence of a collector or seed particle which acts as a sink for the nanowire material, and from which unidirectional growth proceeds.<sup>26</sup> Conventionally, the seed particle is a metal with which the nanowire material or component thereof forms an alloy. However, autocatalytic or self-seeded semiconductor growth has also been demonstrated.<sup>27–33</sup> Self-seeded VLS-type nanowire growth is most commonly observed for compound materials such as InP, GaN and SnO<sub>2</sub> whereby the metallic component of the material, In, Ga and Sn for InP, GaN and SnO<sub>2</sub> respectively, forms seed particles for nanowire growth of the compound material.<sup>33,32,34</sup> However, there have also been reports of self-seeded nanowire growth for elemental materials where a VLS-type mechanism has been invoked.<sup>35</sup> Chapter 3 of this thesis discusses a novel mechanism of Ge nanowire growth in the absence of a metal seed catalyst particle. The most commonly used metal catalyst for VLS-type nanowire growth is Au, prepared either as colloidal Au nanoparticles or as an evaporated or sputtered thin film. However, Au is inherently incompatible with semiconductor device manufacturing. Au has a high diffusivity in Si and also acts as a deep level acceptor and thus has detrimental effects on device performance.<sup>36–38</sup> Furthermore, Au is a highly inert material which makes cleaning of instrumentation contaminated with Au

extremely difficult. For example, traditional Au etchants include aqua regia (concentrated nitric acid and hydrochloric acid solution), KI/I<sub>2</sub> solution and alkali cyanide solutions, all of which would corrode stainless steel equipment and in the case of alkali solutions result in detrimental effects on semiconductor device performance, such as shifting of threshold voltage  $(V_t)$ .<sup>39,40</sup> Consequently, there has alternative, complementary been significant research into metal-oxidesemiconductor (CMOS) production compatible, metal seeds for catalysed VLS semiconductor nanowire growth.<sup>41–43</sup> Acceptable metals should have ionisation energies far from the mid band-gap region of the semiconductor material. Si nanowire growth has been demonstrated using a number of Si CMOS compatible metals including Bi<sup>22</sup> and Al.<sup>44</sup>

One benefit of bottom-up nanowire growth over top-down processing is that nanowires grown by bottom-up methods may be doped in-situ during crystal growth by incorporating dopant precursors in the nanowire synthesis procedure. Consequently, bottom-up grown nanowires may not require destructive techniques such as ion implanting to generate additional charge carriers. Ion implanting can destroy atomic ordering in the implanted region of the semiconductor crystal and requires subsequent thermal annealing steps to restore crystal ordering.<sup>45</sup>

In addition to VLS-type nanowire growth mechanisms there exists a range of other routes to produce bottom-up grown nanowires. These routes include, oriented attachment,<sup>46,47</sup> metal organic vapour phase epitaxy (MOVPE),<sup>48,49</sup> molecular beam epitaxy (MBE),<sup>50</sup> soft templating,<sup>51–53</sup> dislocation driven unidirectional growth<sup>29</sup> and crystal habit modification.<sup>54–56</sup>

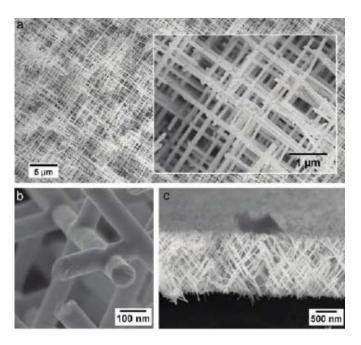

#### **1.2.2.** Nanowire Alignment Techniques

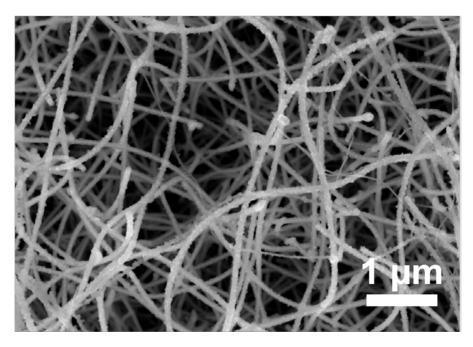

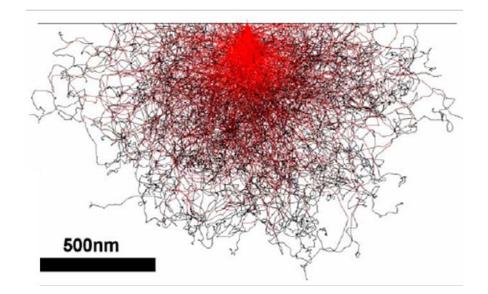

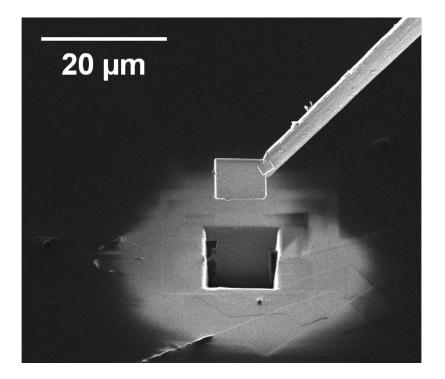

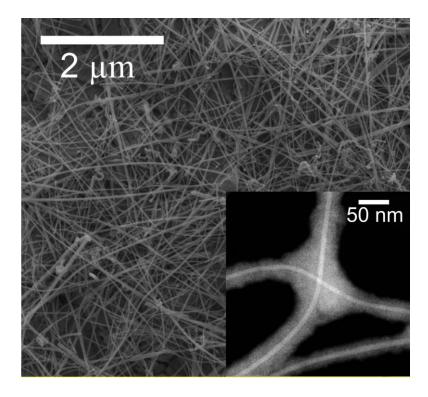

Bottom-up grown semiconductor nanowires fabricated by the methods outlined above are typically produced as entangled meshes of nanowires and as a result lack the periodic ordering and placement required for large-scale semiconductor device processing. Figure 1.1 displays an SEM image of an entangled mesh of SiO<sub>2</sub>-coated Ge nanowires.

**Figure 1.1.** An SEM image of an entangled mesh of  $SiO_2$ -coated Ge nanowires grown from colloidal Au nanoparticles by the SFLS method.

Recently there have been a number of techniques developed to align semiconductor nanowires produced as entangled meshes. Examples include alignment of polar nanowires within strong electric fields,<sup>57,58</sup> dielectrophoresis,<sup>59,60</sup> microfluidic alignment,<sup>61</sup> lubricant assisted contact printing,<sup>62–64</sup> and evaporation-induced alignment.<sup>65–67</sup> Electric field-based alignment techniques, including dielectrophoresis, have been shown to allow precise control over nanowire position with respect to metallic contact pads, however, these techniques have not yet

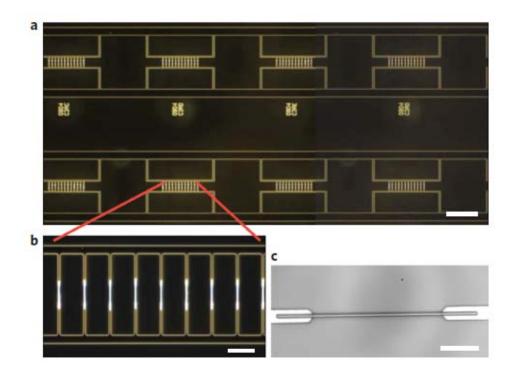

demonstrated the high density of aligned nanowires required for high volume manufacturing (HVM), which is currently approaching a device half-pitch of 20 nm.<sup>12</sup> Figure 1.2 displays images of nanowires aligned by dielectrophoresis at a pitch of  $\sim 20 \,\mu$ m.

**Figure 1.2.** Optical dark-field and DUV images of nanowires assembled onto electrodes by dielectrophoresis: (a) dark-field image of defect-free nanowire assembly arranged on electrode arrays (scale bar =  $200 \ \mu$ m), (b) high magnification dark-field image of nanowires aligned on 2  $\mu$ m wide electrodes (scale bar =  $20 \ \mu$ m) and (c) DUV image of a single nanowire aligned on electrodes separated by 12  $\mu$ m (scale bar =  $4 \ \mu$ m).<sup>60</sup>

Microfluidic alignment, contact printing and evaporation induced alignment techniques have all demonstrated the capability to create parallel nanowire arrays, in some cases with high areal density. Fan *et al.*, for example, have demonstrated aligned nanowires at a density of ~ 10 nanowires/ $\mu$ m.<sup>62</sup> However, these techniques

lack the prerequisite precision of control over nanowire placement, required for individual nanowire addressability within very large scale integrated circuit (VLSI) technology. Nevertheless, such techniques have been used not only to demonstrate successful individual device operation, but, also to demonstrate integrated devices in a fully functioning nano-processor.<sup>63</sup>

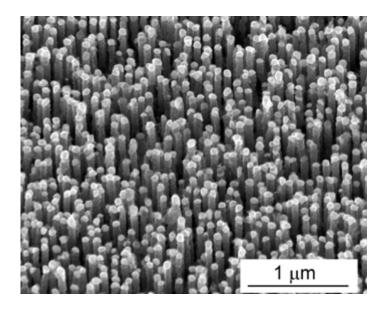

A change of direction may be required for bottom-up approaches to achieve the requisite nanowire density, placement control and alignment required for VLSI manufacturing. High density vertical semiconductor nanowire films have been produced using a range of bottom-up techniques. These techniques include, epitaxial nanowire growth,<sup>68–70,16,71–73,44,49</sup> and hard-templated nanowire growth.<sup>74,75</sup> Figure 1.3 shows an SEM image of vertically aligned epitaxially grown nanowires, where the diameter was controlled by an anodised aluminium oxide (AAO) template.

**Figure 1.3.** SEM image of epitaxial vertical Si nanowire arrays grown within an AAO hard template (template removed in image). Nanowire crystal orientation is controlled epitaxially by the substrate, whilst diameter and placement of the nanowires is controlled by the template.<sup>74</sup>

The epitaxial route to semiconductor nanowire synthesis has the advantage of controlling nanowire crystal orientation through the selection of an appropriate substrate crystal orientation. Wang et al. for example, have demonstrated the epitaxial growth of vertically aligned <111> oriented Si nanowires on a <111> Si substrate by CVD using an Al catalyst. Nanowires can also be produced epitaxially when there is a large lattice mismatch between the nanowire material and the substrate material. Tomioka et al. reported the growth of <111> oriented InAs nanowires on a Si <111> substrate, despite an 11.6 % lattice mismatch between the two crystals, by using a selective area MOVPE technique whereby lattice mismatch strain was dissipated by limiting the interfacial area between the two crystals.<sup>49</sup> Shimizu et al. have shown that the combined use of epitaxial nanowire growth and an ordered template such as AAO to control the position of these nanowires, allows a route to ordered arrays of vertically aligned, coaxial, Si nanowires suitable for use in vertical nanowire device fabrication (figure 1.3).<sup>74</sup> Ordering of pores in AAO spontaneously occurs during AAO formation as a mechanism to reduce internal strain in the AAO film.<sup>76</sup> The formation of AAO with hexagonally close packed (HCP) pores can be considered a bottom-up process, as the pores self-assemble into a HCP arrangement from an initial disordered state, pore by pore.<sup>76</sup>

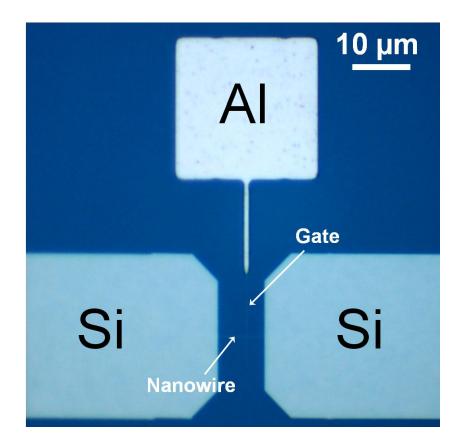

#### 1.2.3. Vertical Nanowire Field Effect Transistors

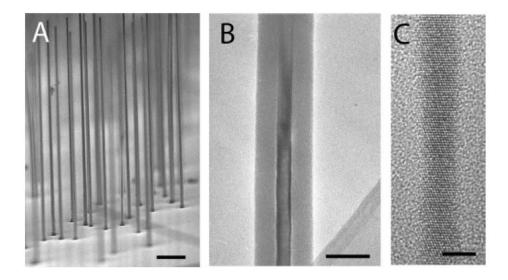

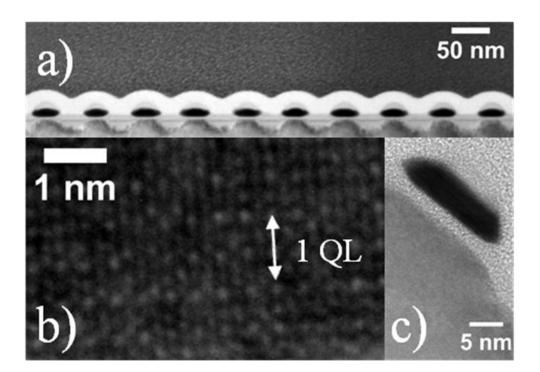

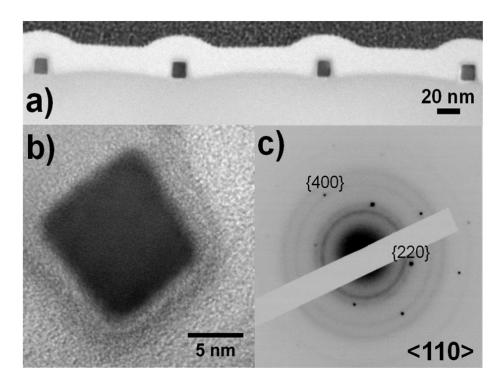

There have been several reports of field effect transistor (FET) devices produced using vertically aligned, bottom-up grown semiconductor nanowires.<sup>77–84</sup> Figure 1.4 shows electron microscopy images of vertical Si nanowires used to create vertical nanowire FET devices.

**Figure 1.4.** Vertically aligned, epitaxial, Au seeded, Si nanowires with thermally grown SiO<sub>2</sub> shells. Scale bars represent lengths of 1  $\mu$ m, 75 nm and 4 nm in (a), (b) and (c) respectively.<sup>83</sup>

The reported devices showed reasonable performance characteristics with observed  $I_{ON}/I_{OFF}$  ratios > 10<sup>5</sup> and a sub-threshold slope of 120 mV/decade, although their performance was still significantly poorer than current state-of-the-art, top-down, strained Si devices.<sup>85</sup> The vertical nanowire devices demonstrated significantly lower on/off ratios and shallower sub-threshold slopes than their top-down counterparts. The reasons for their inferior performance can be attributed to a number of issues including, contact resistance at the source and drain interfaces, non-uniform dopant distribution within the nanowire channel, charge trapping at the gate dielectric interface, or charge carrier recombination due to Au incorporation within Au-seeded Si nanowires. Some of these issues may be rectified, for example, the choice of an appropriate seed metal for nanowire growth is important. Not only should the seed metal allow production of the desired nanowire structure, the metal should also have an appropriate work function to form an ohmic contact to the semiconductor nanowire.<sup>86,87</sup> Au tends to form Schottky contacts to n-Si resulting in

high contact resistance to the semiconductor nanowire channel.<sup>88</sup> The choice of metal also depends strongly on the majority charge carrier and carrier concentration in the nanowire device, for example p-type devices require metals with increased work function values compared to n-type devices, and higher semiconductor charge carrier concentrations result in reduced depletion layer widths at the metalsemiconductor junction which facilitates carrier tunnelling and thus reduced contact resistance.<sup>88</sup> Alternatively, the option exists to use a seed metal which has an inappropriate work function to produce the nanowires and subsequently strip this metal away by chemical etching, followed by the deposition of a suitable electrical contact metal. However, this approach introduces additional device processing steps and complete removal of the seed metal after chemical etching is unlikely, especially when alloys may have formed with the semiconductor during nanowire growth. The issue of dopant distribution is critical to device performance. A homogeneous, activated dopant distribution is desired within semiconductor devices in order to assure a stable threshold voltage  $(V_t)$ .<sup>89</sup> Perea *et al.* have mapped the dopant distribution within an individual VLS grown Ge nanowire, and have shown the dopant distribution to be non-uniform along the nanowire growth axis and radially across the nanowire.<sup>90</sup> Techniques such as single ion implantation have been shown to improve the homogeneity of dopant incorporation in the nanowire structure resulting in improved  $V_t$  stability from device to device.<sup>89</sup> A number of approaches have been taken to improve semiconductor nanowire surface passivation to remove surface state charge trapping sites, which can have capacitive effects at the nanowire surface and hinder device performance. These approaches include organic passivation of the nanowire surface,<sup>91</sup> dielectric deposition of materials such as SiO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub> and nitridation or sulfidation of the nanowire surface.<sup>92,93</sup> Finally, issues

arising due to metal dopants from the catalyst metal particle can be negated through the use of an appropriate metal for the semiconductor of choice. The metal should not have ionisation energies at or near the centre of the band-gap of the semiconductor. For example, Al and Bi seeds would be compatible with Si nanowire production for FET applications as both have ionisation energies near the centre of the band-gap of Si. Once the outstanding issues detailed above have been addressed, bottom-up grown vertical nanowire FETs may become a practical route toward continued device footprint scaling within VLSI technology.

#### **1.2.4. Bottom-Up Semiconductor Nanowire Outlook**

There are a number of outstanding issues associated with the integration of bottomup grown semiconductor nanowires into conventional integrated circuit (IC) design and processing. Conventional IC design is based on the active channel of the logic devices lying coplanar to the Si wafer substrate, and requires a very high degree of control over placement of the devices so that they may be individually addressed for successful IC operation. Traditionally, bottom-up grown semiconductor nanowires are grown as entangled meshes and consequently lack the prerequisite ordering, and control of placement required for IC manufacturing.<sup>15,27,94</sup> Although there have been recent advances in extracting nanowires from such entangled meshes and aligning them on substrates, these approaches can produce neither the high density of nanowires desired. nor the large scale areal coverage required, for HVM.<sup>60,59,63,58,95,65,61</sup> As such, industrial applications of entangled meshes of semiconductor nanowires may be limited to the production of nanowire composites, which may have applications in areas such as batteries, flexible electrodes and thermoelectric generators.<sup>96–98</sup> However, there still remains significant value to be

gained from the study of individual, novel, nanoscale structures, from a conceptual standpoint. Given the issues associated with the alignment of bottom-up grown semiconductor nanowires in the substrate coplanar orientation, it seems imperative that another route to IC fabrication be devised. Perhaps the most promising route toward integration of bottom-up grown semiconductor nanowires into an IC compatible arrangement is that of a vertically oriented active channel with respect to the substrate. Transferring to a vertical orientation would be a huge change for a very mature technology. However, recent developments in the industry with the adoption of tri-gate and finFET structures have shown that movement out of the plane of the Si substrate is possible and as such presents an opportunity for the development of 3-D device architectures. Advances in CVD techniques for nanowire growth have allowed the production of epitaxial nanowires whereby the crystalline orientation of the nanowires with respect to a substrate is controlled at the epitaxial interface. Operational vertically integrated nanowire field effect transistors (VINFETs), produced using bottom-up grown semiconductor nanowires have been reported by several groups.<sup>80,99,83,84</sup> The VINFET concept remains a viable option for future semiconductor device processing as it potentially offers a route to high density stacks of gate all-around (GAA) nanowire FET devices. The vertical orientation with respect to the substrate allows devices to be stacked on the substrate which ultimately increases the density of devices and thus computing power per chip area. A wrap around gate or GAA structure also offers superior electrostatic control of the channel compared to current devices in production, which may allow improved switching of the device. However, a great amount of work is still required to individually contact each device within such a high density, stacked architecture and consequently IC fabrication using VINFET devices is still in its infancy.

Furthermore, the International Technology Roadmap for Semiconductors (ITRS) has targeted a line width roughness (LWR) value of 1.4 nm  $3\sigma$  for device structures by 2015.<sup>12</sup> LWR values in the targeted range are not yet achievable in semiconductor nanowire fabrication by bottom-up means, where typical variation in nanowire diameter values are ~3 nm  $3\sigma$ .<sup>100,101</sup> Consequently, further work is required in the areas of alloy engineering and nanowire catalyst control to achieve the targeted control of nanowire diameter for device components in future VLSI manufacturing.

#### **1.3. Top-Down Semiconductor Nanowire Fabrication**

#### **1.3.1.** Optical Lithography

Optical lithography has been the industry standard for semiconductor device definition and placement for decades. In that time there have been significant developments in optical lithography, both in terms of resist technology and optics.<sup>102–105</sup> There has been a general trend toward shorter wavelength radiation sources to achieve higher image resolution as given by the relationship in equation 1.1 derived from the Rayleigh criterion.<sup>105</sup>

$$CD = \frac{k\lambda}{NA} \tag{1.1}$$

*CD* represents the minimum critical dimension that can be imaged in a photoresist using a given process having a process latitude factor of k, an emission wavelength  $\lambda$ (nm), and a numerical aperture *NA*, where  $NA = n\sin\theta$ , where *n* represents the refractive index of the medium in which the final projection lens is operating and  $\theta$ represents the half-angle of the maximum cone of light that exits the final lens of the system. In the 1970s, Hg G-line emission, at a wavelength of 436 nm, was the lightsource of choice for optical lithography. Current VLSI manufacturing employs an

ArF laser with an emission wavelength of 193 nm. In addition to reducing the wavelength of the radiation source, other measures have also been taken to improve image resolution. DUV scanners and steppers regularly incorporate a reduction lens as the final projection lens of the lithography system. Reduction lenses typically allow  $4 \times \text{ or } 5 \times \text{ reduction of features in the photomask.}^{104}$  The use of reduction lenses in scanners and steppers results in a consequent scaling of the image field, which translates as an increase in the number of exposure fields per wafer and thus a lower throughput of wafers. Consequently,  $2 \times$  reduction lenses are often used as a compromise between reduced critical dimension (CD) and wafer throughput. Although reduction lenses do not increase the resolution of the lithography process, they can be used to scale larger features in the photomask to a fraction of that size in the image projected on the photoresist. This scaling reduces some of the demands placed on mask manufacturing, as low density larger features are typically produced with fewer defects than high density, smaller features in mask fabrication. Interference lithography can be used to create arrays of features with CD values a fraction of the wavelength of the radiation source.<sup>106–108,104</sup> Interference lithography requires a number of coherent beams of radiation to be focused on a spot to create an interference pattern, where the period of the pattern is a fraction of the initial radiation wavelength. Typically interference lithography is only used to produce arrays of structures such as gratings. Immersion lithography is a technique whereby the final projection lens of the radiation source is immersed in a medium with a higher refractive index than air, e.g. water 1.436 at 193 nm. Increasing the refractive index of the medium in which the final lens operates, effectively increases the NA value of the system and as such reduces the minimum CD of features that can be imaged in the photoresist.<sup>104</sup> Media with higher refractive indices than water are also

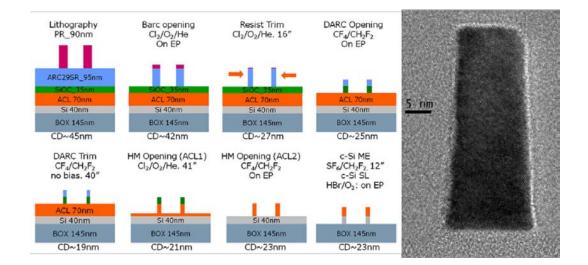

being investigated to further increase the process resolution.<sup>104</sup> The '*k*-factor' or process latitude factor given in equation 1.1, is a broad term which depends on a number of process dependant parameters. The '*k*-factor' accounts for photoresist effects, developer effects and reticle (photomask) effects, amongst others, and as such is a difficult term to predict for a new process. In essence, a high '*k*' value is representative of a lower resolution process, where process parameters limit the achievable resolution. Typical '*k*' values can be as low as 0.15, thus allowing features with dimensions a fraction of the wavelength of the incident light, to be imaged in the photoresist.<sup>109,104</sup> Techniques that can be used to reduce '*k*' values include the use of high resolution resists and resist trimming processes, as shown in figure 1.5.

**Figure 1.5.** (Left) Schematic representation of a process flow used to trim photoresist features to achieve reduced critical dimensions in Si features. (Right) TEM image of a cross-section of a 10 nm  $\times$  40 nm Si nanowire produced from SOI using a 193 nm immersion lithography process incorporating resist trimming steps and overetching.<sup>110</sup>

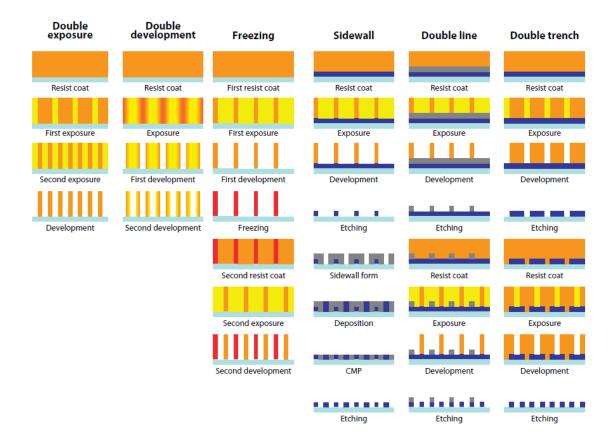

However, even with such low 'k' values, achieving the high feature densities desired for current semiconductor device production requires further process developments such as, optical proximity correction (OPC), phase shift masks (PSM),<sup>111</sup> and double patterning (figure 1.6).<sup>112,110</sup> Ultimately continued device scaling and increased device density may require extreme ultra-violet (EUV) or x-ray lithography (XRL) due to the dramatically reduced wavelengths of these techniques, typically 13.5 nm for EUV and < 1 nm for XRL, compared to current UV lithography techniques. Whilst short wavelength techniques like EUV and XRL offer significant potential for nanolithography, they do have drawbacks. EUV lithography tools have to operate in vacuum due to strong EUV absorption by air. Consequently, EUV resists should not be volatile or swell or under vacuum.<sup>113</sup> Additionally, the requirement for loading and unloading wafers from vacuum chambers puts significant time demands on the Furthermore, shot noise, proximity effects and flare issues remain process. outstanding, all of which will hinder the ultimate resolution of the lithography process. XRL too has a number of issues which may prove to be prohibitive for HVM. XRL requires synchrotron radiation sources which may prove to be too large an investment for an unproven manufacturing process with considerable associated risk. However, XRL does not demonstrate the significant, detrimental, radiationmaterial interactions observed for EUV and as such it remains a pursued and viable option for further technological development.<sup>105</sup>

**Figure 1.6.** Schematic of a number of approaches for double-patterning lithography. CMP, refers to chemical mechanical planarisation.<sup>104</sup>

The significant technological advancements in the field of optical lithography outlined above demonstrate the suitability of these techniques to fabricate ordered arrays of semiconductor nanowires with excellent control over placement and feature-size. Lateral nanowires may be fabricated from layered substrates such as silicon-on-insulator (SOI), or epitaxial thin films, prepared by molecular beam epitaxy (MBE), or metal organic vapour phase epitaxy (MOVPE). Arrays of lateral nanowires can be prepared by fabricating gratings or line structures in the resist material and transferring the grating pattern to the substrate through the use of an appropriate etch process. Figure 1.5 displays a TEM image of a cross-section through a 10 nm wide Si nanowire fabricated from SOI using 193 nm immersion lithography.

Similarly, vertical nanowires may be prepared from bulk or layered substrates by using a resist mask consisting of dot or polygonal structures with maximum lateral dimensions below 100 nm and transfer of the mask pattern deep in to the substrate, again using an appropriate anisotropic etch process.<sup>114</sup> Inductively coupled plasma (ICP) and reactive ion etch (RIE) techniques are most commonly used for pattern transfer, although anisotropic wet etch and metal assisted etch (MAE) procedures have also been used.<sup>115,114</sup>

#### 1.3.2. Next Generation Lithography: Electron Beam Lithography and

#### **Competing Techniques**

A number of lithography processes are being considered to extend lithography scaling beyond current UV lithography capabilities, for semiconductor device manufacturing. These techniques include, electron beam lithography (EBL),<sup>116–118</sup> nanoimprint lithography (NIL),<sup>119,120</sup> x-ray lithography (XRL),<sup>121,122</sup> extreme ultraviolet (EUV) lithography,<sup>123,124</sup> scanning probe lithography (SPL),<sup>125</sup> and electron beam induced deposition (EBID) lithography.<sup>126–128</sup> EBL is at the heart of many of these techniques, including the optical lithography processes. EBL is generally used for the fabrication of high-resolution photomasks for DUV, EUV and XRL. NIL stamps are also produced using EBL direct-write processes. EBID lithography is essentially an EBL process that incorporates the use of a gas injection system which disperses a gaseous precursor that decomposes under the electron beam and directionally deposits on the substrate surface forming a mask. As such, current and

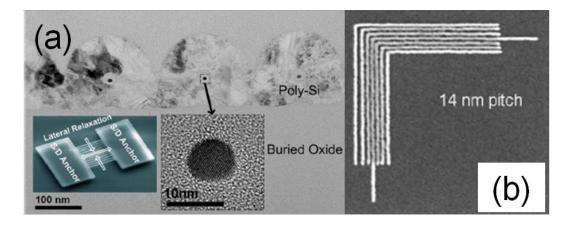

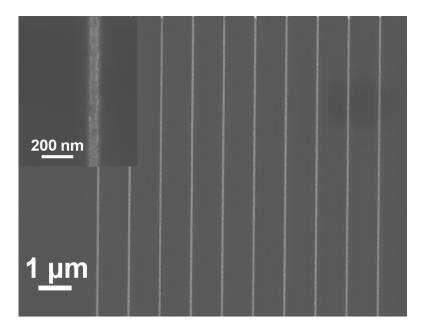

future VLSI manufacturing is heavily dependent on the development of EBL processes and instrumentation. EBL has been shown to be capable of producing sub-10 nm features at sub-20 nm pitches.<sup>129,130</sup> Figure 1.7 displays examples of high-resolution EBL processes used to produce line-widths as small as 4.5 nm at pitches as low as 9 nm.

**Figure 1.7.** High resolution features produced by EBL: (a) 8 nm diameter strained n-Si nanowires produced using a hydrogen silsesquioxane (HSQ) EBL process for gate all-around FET devices and (b) nested lines at a pitch of 14 nm.<sup>130,118</sup>

However, the primary concern with the implementation of EBL techniques in HVM is the low throughput of wafers due to the exposure times required for full wafer layouts. Exposure times depend on several factors which include the tone of the resist, the area of the wafer to be exposed, the electron beam current, electron energy, and the sensitivity of the resist (electron dose required to completely chemically alter the resist).<sup>105,131</sup> Resist technology may have a significant role to play in the reduction of EBL exposure times. Increasing the resist sensitivity will significantly reduce the required time for exposure; however, increased sensitivity should not compromise the ultimate resolution of the resist. Hydrogen

silsesquioxane (POSS) family, is an example of one of the highest resolution negative-tone EBL resists. However, HSQ exposure doses are considered too high for use in HVM. Chemically amplified resists (CARs) have been developed with significantly increased sensitivity with respect to HSQ, but these resists offer lower ultimate resolution. The field of EBL resist research is an active one and recent demonstrations of EBL using analogues of HSQ with increased electron beam sensitivity are promising.<sup>132</sup>

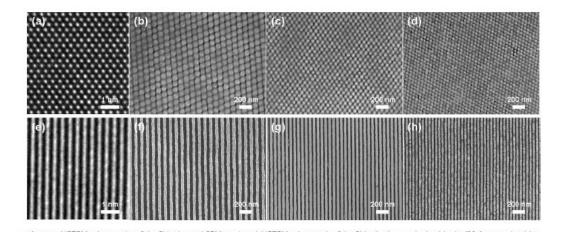

Multi-beam EBL systems are under development which will increase wafer throughput either through beam-splitting techniques, or through the use of instruments with multiple electron sources, however, the technology is still not mature and as such has yet to be implemented on a HVM scale.<sup>133</sup> Lee *et al.*<sup>134</sup> have reported a particularly innovative example of multi-beam EBL using a Si crystal as an electron beam mask (figure 1.8). A transmission electron microscope (TEM) was used to create arrays of electron beams where the shape and separation of the beams was governed by the crystal structure and crystal orientation of the mask with respect to the incident electron beam. Atomic resolution images of the Si crystal lattice were magnified and projected onto HSQ films creating arrays of nanostructures in the resist. This technique shows promise for increased throughput where periodic arrays of simple nanoscale structures are desired.

Chapter 1:Introduction

**Figure 1.8.** Arrays of HSQ nanostructures produced using projection of the atomic lattice of a Si crystal (a) and (e) in a TEM. SEM images (b-d) and (f-h) respectively show the critical dimension and pitch scaling of the structures with increasing TEM magnification,  $160 \times (b,f)$ ,  $200 \times (c,g)$  and  $300 \times (d,h)$ .<sup>134</sup>

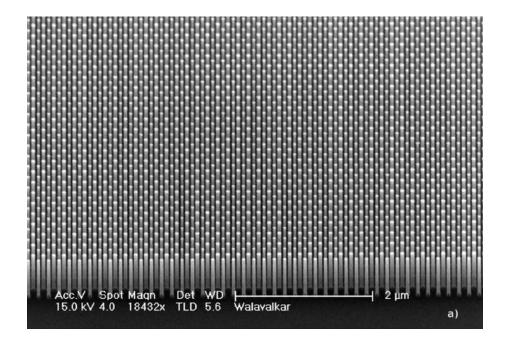

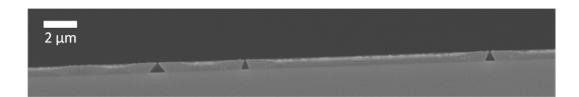

Arrays of dot structures produced by EBL can be used to fabricate vertical nanowire arrays through the use of a deep anisotropic etch.<sup>135–137</sup> The use of an etch resistant material to form the dot structures is paramount to facilitate deep etching to form high aspect ratio nanowires. Typically,  $Al_2O_3$ , Al, and  $SiN_x$ , have been used as etch masks for vertical Si nanowire fabrication. Figure 1.9 shows an SEM image of arrays of vertical Si nanowires produced using an EBL process.<sup>137</sup>

Commonly encountered issues for EBL processes include electron-substrate or electron-resist interactions and surface charging of insulating substrates. Electron-substrate and electron-resist effects can be grouped into three sub-classes, forward scattered electrons (scattering angle < 90°), back-scattered electrons (scattering angle > 90°) and secondary electrons.<sup>105</sup>

Figure 1.9. SEM image of an array of 50 nm diameter Si nanowires etched into a Si wafer. A sputtered  $Al_2O_3$  hard mask, patterned by EBL was used as the Si etch mask.<sup>137</sup>

Forward scattered electron effects are most important within the resist as electrons which are forward scattered in the substrate have little contribution to resist exposure. Forward scattering can be minimised by using a high accelerating voltage (higher energy electrons) or a thinner resist layer. Backscattered electron exposure effects are more prominent for high atomic weight (*Z*) materials and as such are more commonly a consequence of electron-substrate interactions. Secondary electrons are the primary electron-solid interaction, and as such they make the largest contribution to resist exposure. Importantly, although secondary electrons are responsible for most of the resist exposure, their path length in the resist is short, typically < 10 nm, and as such these electrons do not have a significant contribution to proximity effects. Proximity effects can largely be attributed to backscattered electrons which experience large angle scattering and can commonly travel large

distances laterally in the substrate and resist (~ 1  $\mu$ m for 10 keV incident beam energy). Proximity effects due to electron-solid interactions can be corrected through careful modelling of electron scattering, typically as a point spread function (PSF) and the use of appropriate electron dose contour maps based on these models.<sup>133,138</sup> Experimentally derived data can also be used to develop PSFs for use in proximity effect correction (PEC). PEC is particularly important for the exposure of high density features and large structures where electron scattering effects become prominent.

EBL on insulating substrates can be hampered due to surface charging upon electron beam exposure. Surface charging results in an associated electric field at the substrate surface which acts to deflect the incident electron beam with detrimental effects on the EBL process. Surface charging effects can be avoided by several Deposition of a thin layer of conducting material (Au, Cr, Al or methods. conducting polymers) atop the resist can remove surface charging effects, with the drawback of the introduction of an additional layer of material in the EBL process. Conducting polymers such as ESPACER (Showa-Denko), a member of the polythiophene family, are preferable to metals such as Au due to their superior process compatibility.<sup>105</sup> ESPACER is soluble in water and as such can be easily removed following electron beam exposure and prior to developing the resist, where as complete removal of Au and similar metals requires harsh etching conditions which may alter the resist, and the substrate. Much work has been performed in the field of electron-solid interactions and as such modelling and correcting undesired electron-solid interactions is now possible.<sup>138</sup> However, until EBL sample throughput times are reduced to acceptable levels for HVM, EBL will remain confined to tasks such as quantum device demonstration, NIL stamp fabrication and high-resolution photomask fabrication.

Electron beam induced deposition (EBID) can be used as a lithographic tool to produce sub-10 nm features.<sup>139,127</sup> As stated previously, EBID essentially involves introducing a gaseous precursor species into the path of an electron beam in an EBL system. The precursor decomposes upon electron beam exposure and directionally deposits the solid decomposition product, typically a metal such as W, or Pt, on the substrate. EBID is a capable lithographic tool for the production of devices on a small scale.<sup>126</sup> However, EBID suffers from inherent drawbacks such as metal contamination of device structures and low throughput. EBID is more suited to small-scale applications such as photomask defect repair.

Many of the issues associated with the implementation of EUV, and XRL techniques in HVM have been discussed in the previous section. NIL is a mechanical lithography technique whereby a stamp or template created in a robust material, usually Ni or Si, for thermal NIL; PDMS for soft NIL; and quartz for step and flash NIL (S-FIL a trademark of Molecular Imprints Inc.), is pressed into a deformable resist on a substrate. The resist is then hardened so that when the template is removed the contours of the template are transferred to the resist. The patterned resist can then be used for subsequent pattern transfer procedures. NIL is a relatively inexpensive technique when compared to other nanolithography techniques and has demonstrated the production of very fine features at high areal densities.<sup>119</sup> Furthermore, NIL can be used to directly pattern interlayer dielectric (ILD) materials such as low-*k* silsesquioxanes (SSQs) thus reducing the number of process steps required in the dual-damascene process typically used to form metallic interconnects.<sup>140,141</sup> However, there are outstanding issues concerning overlay accuracy, defect density and throughput. Additionally, NIL may not be compatible with pattern transfer to porous low-k materials used as back-end-of-line (BEOL) insulators, which are inherently brittle and may be deformed by the pressure applied during NIL.<sup>119</sup>

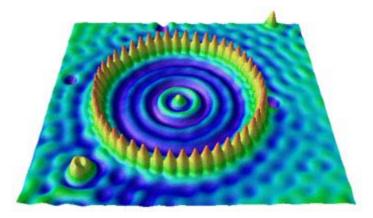

Scanning probe lithography (SPL) encompasses a range of lithography techniques including, dip-pen nanolithography (DPN), local oxidation nanolithography (LON), atomic force microscope (AFM) lithography and scanning tunnelling microscope (STM) lithography. Common to these techniques is the use of a scanning nanoscale probe, typically an AFM tip, to pattern a resist or substrate directly.<sup>142,143</sup> In the case of DPN an AFM tip is used to transfer a material to the surface which can subsequently act as an etch mask or may act as an active device component itself. LON is used to locally oxidise a material thus forming a patterned surface oxide by applying a voltage bias between a conductive AFM tip and the substrate material in the presence of water vapour to induce localised oxidation of the substrate through electrochemical reaction with the water vapour. AFM lithography can operate in contact mode or non-contact mode. Contact mode AFM lithography involves the mechanical patterning of a substrate much like NIL. An AFM tip can be used to scratch or stamp a pattern into a resist material or into the substrate itself. Noncontact mode AFM can be used to pattern materials through local oxidation of the substrate surface as in the case of LON, through local heating of a resist material using a heated AFM tip, or through local electron exposure via a field emission AFM tip.<sup>142,143</sup> STM lithography has been used to produce nanostructures by a variety of means. Scappucci *et al.* have reported the use of STM to selectively dope regions on a H-terminated Ge (100) surface where H atoms have been removed by STM, thus creating doped nanowire structures.<sup>125</sup> STM can also be used for the individual manipulation of atoms on a surface to produced quantum structures, such as the quantum corral reported by Crommie *et al.* in 1993 (figure 1.10).<sup>144</sup> SPM lithography techniques are inherently slow even when multiple probes are used.<sup>145</sup> As such, low throughput will prevent such techniques from being used in HVM.<sup>143</sup>

**Figure 1.10.** False colour STM image of a quantum corral structure created by the atomic manipulation of 48 Fe atoms on a Cu  $\{111\}$  surface. The Fe ring confines the surface electron wavefunction of the defect free Cu surface within.<sup>144</sup>

#### **1.3.3.** Top-Down Semiconductor Nanowire Fabrication Outlook

Top-down semiconductor lithography processes have dominated the area of semiconductor device definition and placement for decades. However, as the density of devices on a chip continues to scale significant difficulties are encountered. Techniques such as EBL and XRL with significantly reduced wavelengths, may readily achieve the high densities of devices desired by the semiconductor industry, however, there are a number of difficulties associated with the integration of these short wavelength techniques in VLSI manufacturing. Consequently, it seems

increasingly likely that current top-down processes may have to 'reach out' to a bottom-up technology to achieve the future goals of the semiconductor industry.

# **1.4. Integration of Bottom-Up and Top-Down Nanowire Fabrication Processes**

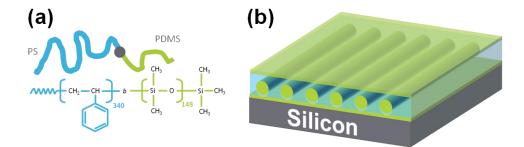

#### 1.4.1. Directed Self-Assembly

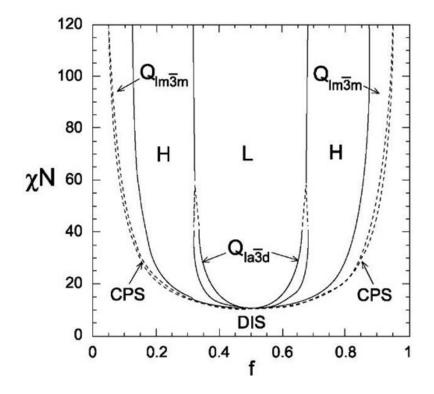

Directed self-assembly (DSA) is an advanced lithographic process based on the selfassembly of block copolymers (BCPs). BCP self-assembly involves the bottom-up, microphase separation of chemically different blocks within the BCP. Typically, A-B diblock copolymers are used for DSA, where an A-B diblock copolymer consists of a linear chain of a monomer A, joined at one end by a covalent bond, to a linear chain of monomer B. When the two blocks, A and B, are sufficiently chemically distinct from one another, they can microphase separate so as to minimise the interaction volume of blocks A and B, whilst maximising the interaction volume between similar blocks. The chemical interaction of the two blocks in a BCP is often quantised by the Flory-Huggins interaction parameter ( $\chi$ ) for that BCP system which is related to the enthalpy of mixing for that polymer system.<sup>146</sup> Self-consistent mean field theory has been used to generate theoretical phase diagrams for diblock copolymer melts (figure 1.11).<sup>147</sup> Mean field phase diagrams are presented as a plot of  $\chi N$  against f, where N is the degree of polymerisation of the BCP and f is the volume fraction of a reference block in the BCP.  $\chi N$  is representative of the thermodynamic driving force for microphase separation within the diblock copolymer melt.  $\chi$  represents the enthalpic component and is inversely related to temperature and directly related to polymer chain length, whilst N represents the entropic component, which depends on the chain length dependent number of conformations that can be adopted by the polymer.

**Figure 1.11.** Phase diagram of a diblock copolymer as predicted by self-consistent mean field theory. Phases are labelled L (lamellar), H (hexagonally arranged cylinders),  $Q_{la3d}$  (bicontinuous  $I_{a3d}$  cubic),  $Q_{lm3m}$  (body centred cubic spheres), CPS (close packed spheres), and DIS (disordered).<sup>147</sup>

Figure 1.12 shows schematic examples of phase morphologies within a microphase separated A-B diblock copolymer with increasing number fraction of block A  $(f_A)$ .<sup>146</sup>

Chapter 1:Introduction

**Figure 1.12.** Schematic representation of the microphase morphologies of an A-B diblock copolymer with increasing number fraction of block A from left to right.<sup>146</sup>

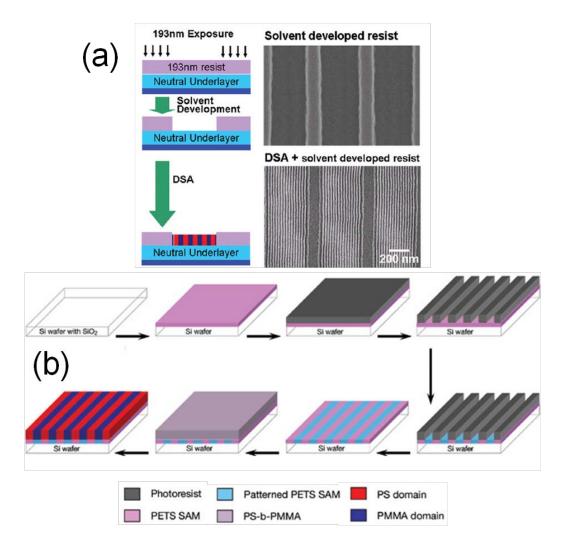

Lamellar and hexagonally close packed cylinder phases of BCPs are typically used in DSA, where the phase of the BCP can be controlled through selection of appropriate polymer fractions in the BCP, and suitable polymer chain lengths. The microphase separation of BCPs can be guided both chemically and physically through the use of careful templating techniques, *i.e.* directed self-assembly. Physically guided microphase separation of a BCP is often termed graphoepitaxy. DSA of lamella forming BCPs by graphoepitaxy, is generally achieved by creating trenches on a substrate where the trench width is an integer multiple of the block length.<sup>148,146</sup> Similarly, chemically guided microphase separation of a BCP is termed chemical epitaxy. DSA by chemical epitaxy is achieved using a substrate that has been chemically patterned to induce ordering during microphase separation of the BCP.<sup>149,150</sup> Consequently, DSA by both graphoepitaxy and chemical epitaxy is

**Figure 1.13.** Typical process flows used to produce DSA of BCPs via (a) graphoepitaxy and (b) chemical epitaxy, respectively.<sup>150,151</sup>

heavily dependent on conventional lithographic techniques such as those outlined in Section 1.3.

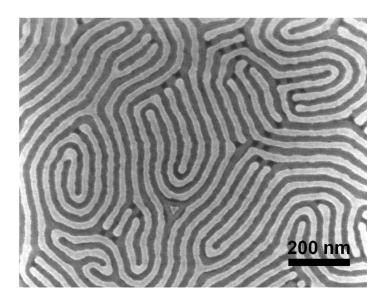

Ordered diblock copolymer films produced by DSA can be used as high-resolution etch masks for semiconductor nanowire fabrication. As such, DSA has gained significant interest in the field of nanolithography in recent years. DSA offers a number of advantages over conventional optical or direct-write lithography techniques. Firstly, DSA can achieve sub-lithographic resolution by pattern

multiplication, thus increasing the density of features within low density patterns produced by conventional optical or mask-less lithography techniques.<sup>152–155</sup> Additionally, the resolution of block copolymer lithography can be controlled by tuning the length of the polymer chains in the BCP. Reduction of the polymer chain length results in an equivalent reduction in the domain dimensions within the microphase separated BCP. Implementation of a pattern multiplication process in current lithographic methods for VLSI manufacturing would remove the necessity for complicated techniques such as double patterning and high density lithography.<sup>149</sup> DSA by chemical epitaxy has also been shown to exhibit self-healing properties, whereby defects in templates used to guide microphase separation are corrected in the extended pattern of the mask produced by DSA.<sup>156,157</sup> Additionally, DSA is a relatively inexpensive technique, depending on the process used to guide microphase separation. DSA has the potential to offer very high throughput if it were incorporated with current optical lithography processes, and can readily achieve sub-20 nm critical dimensions by controlling the molecular weight of the polymer blocks in the BCP. Furthermore, DSA has been shown to be capable of producing device specific geometries such as bends, T-junctions and jogs.<sup>158,152</sup> Parameters such as line-edge-roughness (LER) for DSA masks are determined by the quality of the microphase separation and associated guiding technique as well as the quality of the etch used to selectively remove one of the blocks of the BCP. LER values as low as 1.95 nm  $(3\sigma)$  have been reported for lines produced by DSA of a lamella forming BCP.<sup>149</sup>

However, there are a number of outstanding concerns associated with DSA as a lithographic technique. The primary concern with the process is high defect density, attributable to contamination, BCP purity, BCP molecular weight distribution, chemical uniformity of the substrate surface and defects within the DSA guiding template. Additionally, BCP layers are often prepared as thin monolayers and often have poor etch resistance, *e.g.* PMMA, PS.

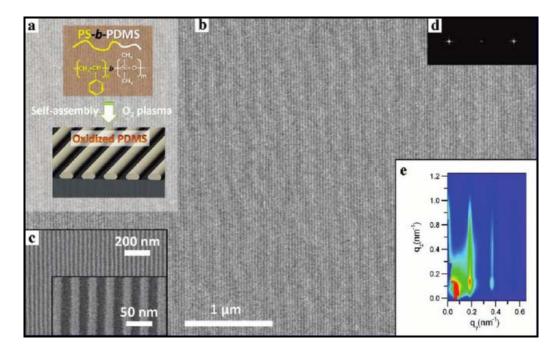

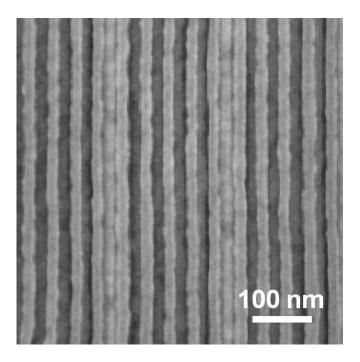

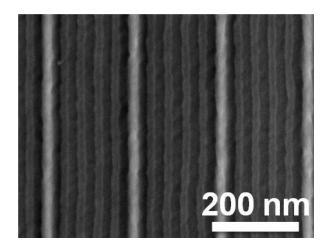

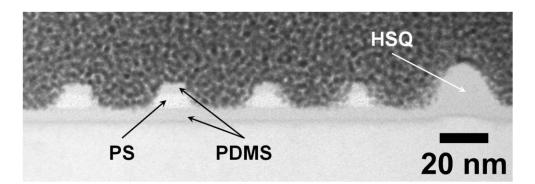

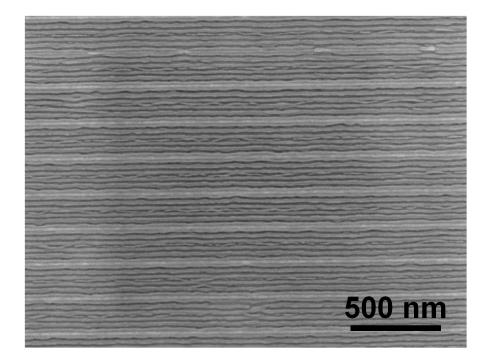

Whilst the defect density in DSA masks is improving with increased research investment, DSA processes still require further optimisation before they can be integrated into a HVM landscape. Figure 1.14 shows an example of relatively large area patterning achieved via the graphoepitaxy of PS-*b*-PDMS.<sup>153</sup>

**Figure 1.14.** (a) A schematic of the structure of PS-*b*-PDMS and the structure formed by DSA. (b) SEM image showing large-scale alignment of PDMS lines produced by the graphoepitaxy of PS-*b*-PDMS within 10  $\mu$ m wide, PDMS brush coated trenches etched in a Si wafer. (c) Higher magnification images of the aligned PDMS lines. (d) FFT of the image in (b) consistent with excellent long-range ordering. (e) Grazing incidence small angle x-ray scattering (GISAXS) pattern generated from a 1 cm<sup>2</sup> area of the PDMS line pattern.<sup>153</sup>

Chemical epitaxy DSA techniques can 'heal' defects present in the guiding template; however, chemical epitaxy has not yet demonstrated pattern multiplication to the extent of graphoepitaxy based techniques. Thus, it is likely that each approach, chemical epitaxy and graphoepitaxy, will find their own niche application within the semiconductor industry. Development of DSA masks with sufficient etch resistance will depend on the specific process requirements. PS-*b*-PDMS for example, is a promising material for DSA when a high etch resistance to Si etchants is required. PDMS has an inorganic Si-O backbone and as such offers superior etch resistance relative to organic polymers.

The outlook for DSA is promising. DSA has already demonstrated the requisite resolution capabilities for continued device scaling outlined within the International Technology Roadmap for Semiconductors (ITRS), defect density levels are dropping with continued research investment and issues regarding production of device specific geometries appear to be resolvable using chemical epitaxy approaches.<sup>149</sup> LER and CD control issues also need to be addressed to meet ITRS specifications.<sup>149</sup> Theoretical models predict LER to be related to  $\chi^{-0.5}$ , in which case, BCP systems with high  $\chi$  values such as PS-*b*-PDMS ( $\chi \sim 0.26$  at room temperature) are worthy of further investigation.<sup>153</sup>

Self-assembly of cylinder and sphere forming BCPs has also been used to produce ordered arrays of metal nanoparticles by both additive<sup>159</sup> and subtractive<sup>160</sup>, processes. These metal nanoparticles may then be used to produce epitaxial growth of semiconductor nanowires by means of the relevant techniques outlined in Section 1.2. Furthermore, the metal nanoparticles may be used as etch masks to produced ordered arrays of vertical nanowires by a top-down approach. The use of BCP films to template catalysts for epitaxial nanowire growth and to template hard masks for top-down vertical nanowire array formation is an example of a synergistic process, employing both bottom-up and top-down methods. This synergistic process is to date, a poorly explored application of BCP lithography which warrants further investigation.

DSA is a promising blend of top-down and bottom-up techniques for advanced lithography applications. DSA allows a route to increased pattern resolution and feature density relative to conventional optical lithographic means, and whilst concerns still exist over LER, CD control and reproducibility, these concerns are gradually being improved by continued advances in the field. DSA depends on conventional lithography techniques such as optical lithography, interference lithography and EBL to form guiding templates to direct the self-assembly of BCPs and as such it will remain a complementary lithography technique. However, if and when the issues associated with DSA are resolved, this lithography technique may alleviate the growing demands on optical lithography and EUV for continued device scaling, thus extending the use of current optical lithography techniques in VLSI manufacturing.

#### **1.4.2. EBL Catalyst Placement for Bottom-Up Nanowire Growth**

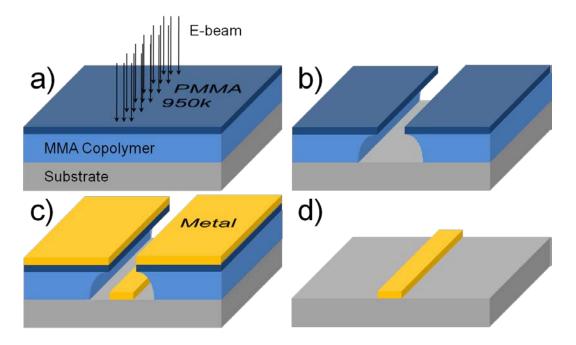

EBL is a suitable tool for the preparation of ordered arrays of metal nanoparticles by subtractive or additive processes. Ordered arrays of metal nanoparticles can be readily prepared using a positive tone EBL process to generate a metal lift-off mask.<sup>161,16,81,72</sup> This process can be used to produce epitaxial nanowire growth via a

VLS-type mechanism through careful control of the metal substrate interface, and choice of an appropriate substrate material, using nanowire growth methods such as those outlined in section 1.2. Coupling EBL and self-assembly of BCPs allows the production of defect free high-density arrays of dot structures.<sup>162</sup>

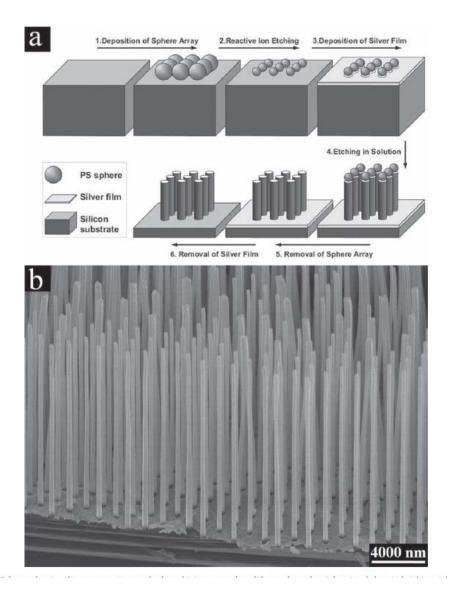

#### 1.4.3. Nanosphere Lithography

Nanosphere lithography (NSL) can be used to produce ordered arrays of vertical nanowires. NSL uses the bottom-up self assembly of spherical particles, such as polystyrene spheres, to create dot/anti-dot arrays on the surface of a substrate, which then may be used to transfer the pattern to the substrate creating structures such as vertically aligned nanowire arrays.<sup>163–166</sup> NSL can be used to produce arrays of vertical Si nanowires using a metal-assisted etching approach as shown in figure 1.15 below. Combined use of NSL and metal-assisted etching (MAE) provides a route to forming arrays of long (> 10  $\mu$ m) Si nanowires which have applications in fields such as vertical ICs and solar cells (figure 1.14).<sup>166</sup> NSL can also be used to create an anti-dot array mask for the evaporation of arrays of metal nanoparticles for use as catalysts for epitaxial nanowire growth.<sup>163</sup>

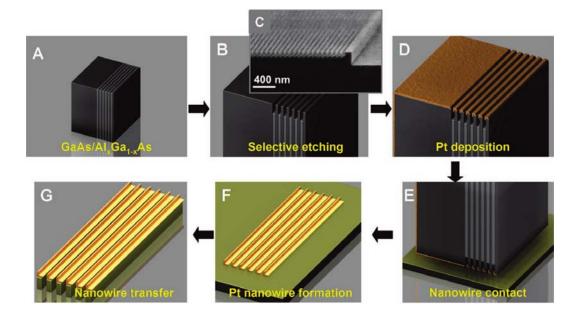

### 1.4.4. Miscellaneous Synergistic Nanowire Fabrication Processes

A range of processes exist which use both bottom-up and top-down techniques in tandem to produce semiconductor nanowires. One example of such a technique is the supperlattice nanowire pattern transfer (SNAP) technique.<sup>167</sup> The SNAP technique is based on the formation of a stamp by selectively etching one of the layers in a superlattice material grown by a bottom-up epitaxy technique, such as MBE. Angular deposition of a metal on the etched superlattice then allows creation

Chapter 1:Introduction

**Figure 1.15.** Schematic of NSL process for the fabrication of vertical Si nanowire arrays via MAE.<sup>165,168</sup>

of a metal stamp which is pressed against the material of choice producing a metal grating which acts as an etch mask for the fabrication of nanowire arrays by pattern transfer. Figure 1.16 shows a schematic of the SNAP process. The SNAP process has been used successfully to produce arrays of Si nanowires from SOI, as well as metal nanowires formed directly from the stamp. However, the technique is limited in terms of the geometries of the structures that can be produced, and the complexity of the process for large-scale nanowire fabrication. Furthermore, the SNAP

Figure 1.16. Schematic of the SNAP process for production of aligned nanowires.<sup>167</sup>

technique is susceptible to many of the pitfalls associated with NIL outlined in section 1.3.2.

NIL can be used to created arrays of metal nanoparticles for bottom-up nanowire growth.<sup>169</sup> This process involves imprinting a bilayer positive-tone resist, developing the imprinted resist and evaporating a metal layer to produce arrays of metal nanoparticles by lift-off. The metal nanoparticles can subsequently be used as catalysts for nanowire array production by standard nanowire growth procedures.

AAO membranes with HCP pore arrangements are formed by a bottom-up process, as discussed in Section 1.2.2. These ordered porous membranes can be used as masks to produce patterned metal films on Si substrates for MAE of Si, producing ordered arrays of vertical Si nanowires.<sup>170,171</sup> MAE techniques using patterned metal layers are successful at producing dense, ordered arrays of vertical nanowires with high aspect ratios. However, as with all MAE techniques, the nanowires produced

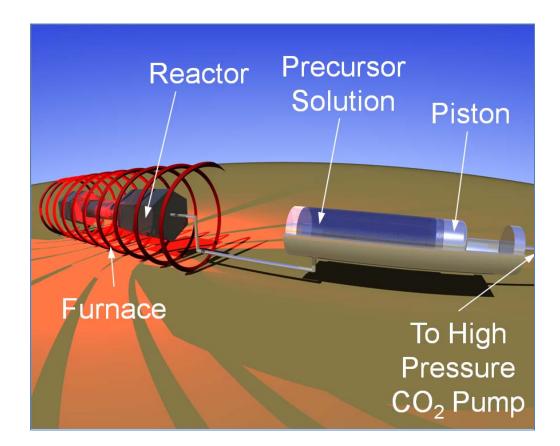

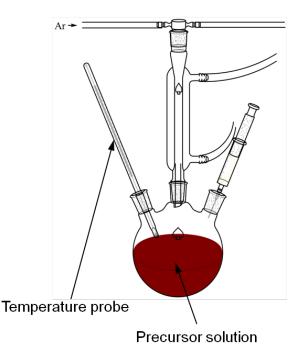

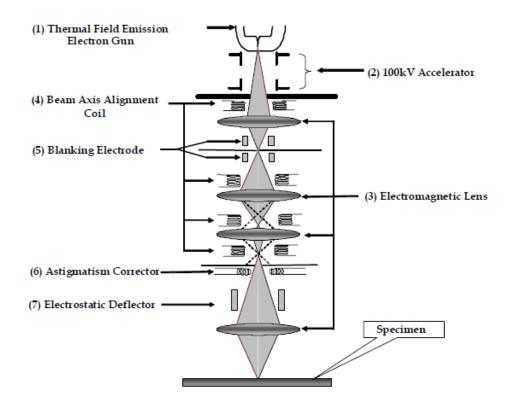

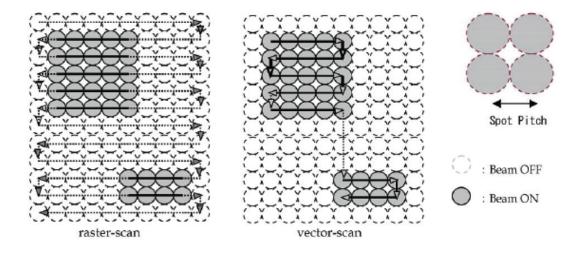

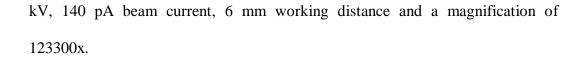

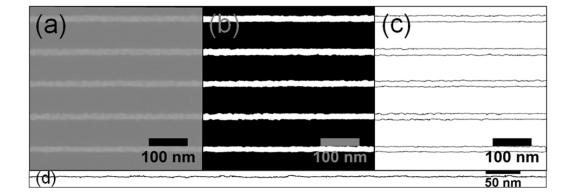

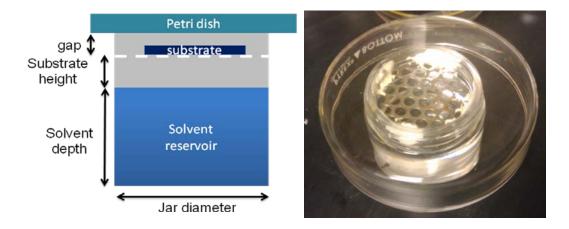

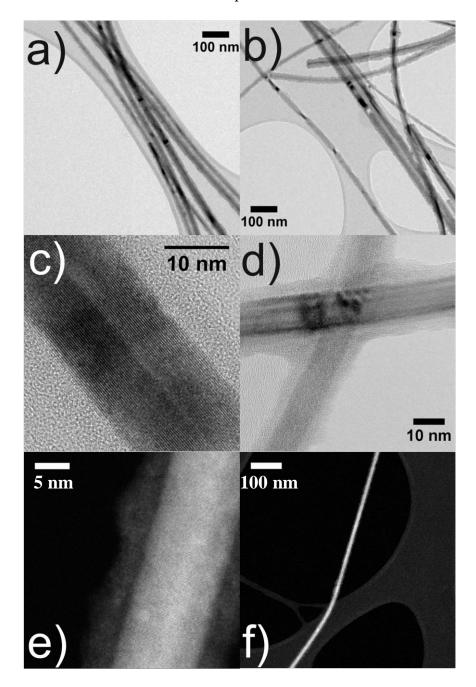

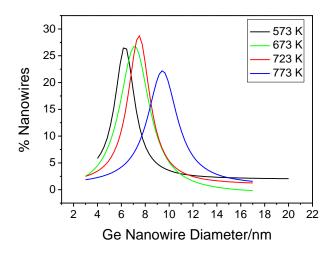

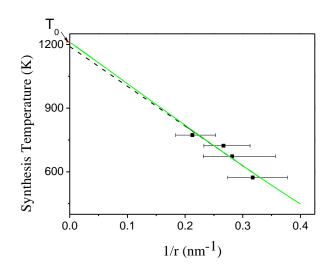

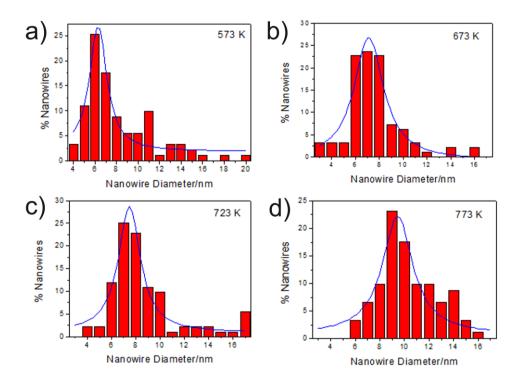

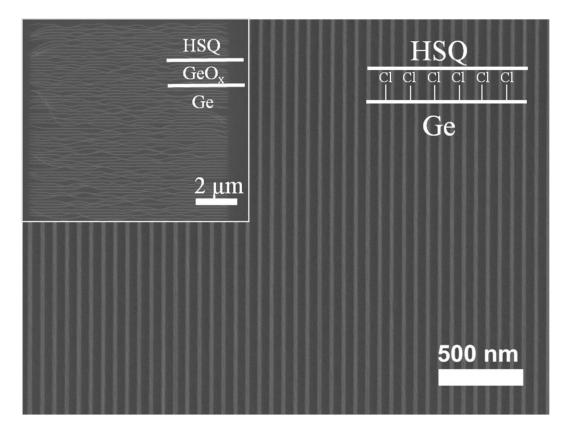

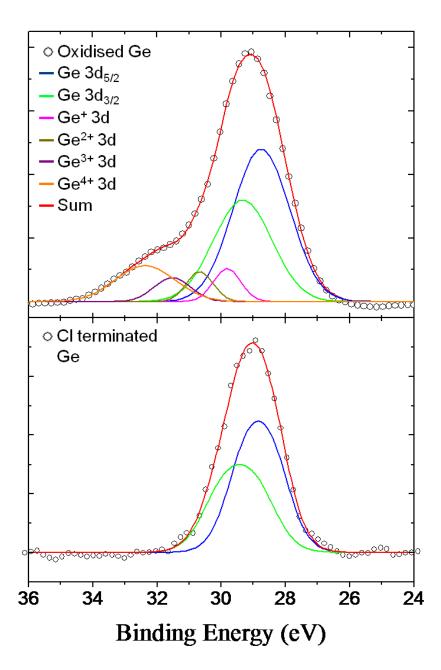

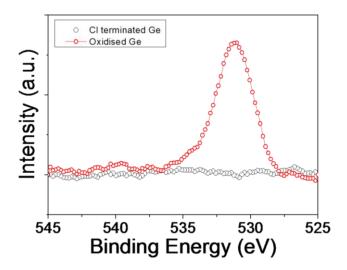

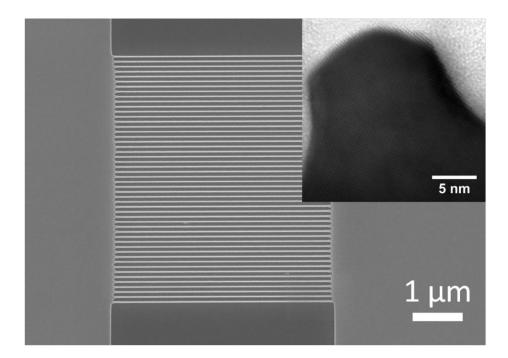

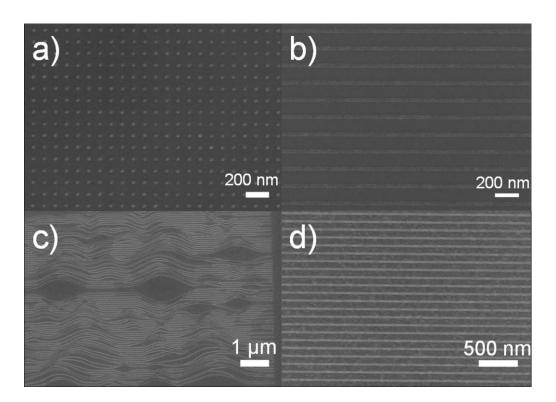

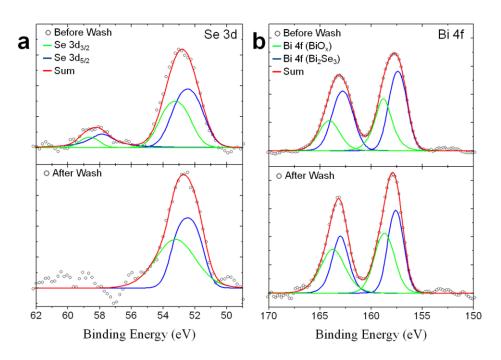

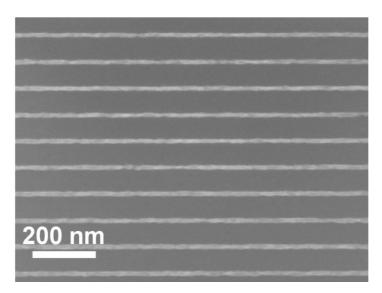

have rough sidewalls thus inhibiting their use in logic applications where surface scattering of charge carriers is a significant drawback.<sup>165,172</sup> Nanowires produced by these methods are likely to find applications in solar cell, thermoelectric generator, sensor or battery anode applications where the increased surface area of nanowires with rough sidewalls may be beneficial to device performance.<sup>173,174</sup>