| Title                   | Micro-transfer printing of micro-structured, ultra-thin light-<br>emitting devices                                                          |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                 | Shaban, Zeinab                                                                                                                              |

| Publication date        | 2023-03                                                                                                                                     |

| Original Citation       | Shaban, Z. 2023. Micro-transfer printing of micro-structured,<br>ultra-thin light-emitting devices. PhD Thesis, University College<br>Cork. |

| Type of publication     | Doctoral thesis                                                                                                                             |

| Rights                  | © 2023, Zeinab Shaban https://creativecommons.org/licenses/<br>by-nc-nd/4.0/                                                                |

| Download date           | 2025-08-25 23:53:59                                                                                                                         |

| Item downloaded<br>from | https://hdl.handle.net/10468/14474                                                                                                          |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# Micro-transfer printing of micro-structured, ultra-thin light-emitting devices

Zeinab Shaban

Thesis submitted in partial fulfilment of the requirements of the degree of Doctor of Philosophy

> at the Department of Physics, University College Cork, National University of Ireland

Supervisor: Brian Corbett Co-supervisor: Peter James Parbrook Head of Department: Prof. John G. McInerney

March 2023

# Contents

| Li | st of | Figur   | es                                                       |    |       |   | $\mathbf{iv}$  |

|----|-------|---------|----------------------------------------------------------|----|-------|---|----------------|

| Li | st of | Table   | S                                                        |    |       |   | ix             |

| Li | st of | Acror   | ıyms                                                     |    |       |   | x              |

| Li | st of | Publi   | cations                                                  |    |       |   | xii            |

| D  | eclar | ation o | of Authorship                                            |    |       |   | $\mathbf{xiv}$ |

| A  | cknov | wledge  | ements                                                   |    |       |   | xvii           |

| D  | edica | tion    |                                                          |    |       |   | xviii          |

| 1  | Intr  | oduct   | ion                                                      |    |       |   | 1              |

|    | 1.1   | Introd  | luction of integration techniques                        |    | <br>• |   | 2              |

|    |       | 1.1.1   | Monolithic integration                                   | •  | <br>• | • | 2              |

|    |       | 1.1.2   | Hybrid and heterogeneous integration                     | •  | <br>• | • | 2              |

|    |       | 1.1.3   | Micro-transfer printing technology                       | •  | <br>• | • | 3              |

|    | 1.2   | Light-  | emitting diodes                                          | •  | <br>• | • | 6              |

|    |       | 1.2.1   | Brief history of GaN LEDs                                |    |       |   | 6              |

|    |       | 1.2.2   | Fundamentals of LED operation                            | •  | <br>• | • | 8              |

|    |       | 1.2.3   | GaN-based LEDs                                           | •  | <br>• | • | 10             |

|    |       | 1.2.4   | Efficiency of GaN LEDs                                   |    |       |   | 11             |

|    | 1.3   | GaN 1   | LEDs on various substrates                               | •  | <br>• |   | 14             |

|    |       | 1.3.1   | Advantages and disadvantages of sapphire substrate       | •  | <br>• | • | 14             |

|    |       | 1.3.2   | Advantages and disadvantages of Si substrate             |    |       |   | 15             |

|    |       | 1.3.3   | Advantages and disadvantages of GaN substrate            |    |       |   | 16             |

|    | 1.4   | Thesis  | s outline                                                | •  |       | • | 17             |

| 2  | Pro   | cess o  | ptimization of GaN LEDs based on Si for transfer printin | ıg |       |   | 19             |

|    | 2.1   | Introd  | luction                                                  |    |       |   | 19             |

|    | 2.2   | Fabric  | cation process flow of releasable LEDs                   |    |       |   | 21             |

|    |       | 2.2.1   | Wafer material                                           |    | <br>• |   | 21             |

|    |       | 2.2.2   | Wafer surface cleaning                                   |    |       |   | 22             |

|    |       | 2.2.3   | P-contact deposition                                     |    |       |   | 23             |

|    |       | 2.2.4   | Mesa etch, insulation layer and metal deposition         | •  |       |   | 23             |

|    |       | 2.2.5   | Coupon and Si etch                                       |    | <br>• |   | 24             |

|    |       | 2.2.6   | Define anchor and tether                                 |    |       |   | 24             |

|   |      | $2.2.6.1  \text{Tether tests} \dots \dots$                         |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 2.2.6.2 Optimization of anchors to enable releasing and roughening the                                                                                                   |

|   |      | devices $\ldots \ldots 20$                                                    |

|   |      | 2.2.7 Undercut of LEDs from Si substrate                                                                                                                                 |

|   | 2.3  | Stress management                                                                                                                                                        |

|   |      | 2.3.1 Methods                                                                                                                                                            |

|   |      | 2.3.2 Investigation of the effects of initial wafer stress on device formation $35$                                                                                      |

|   |      | 2.3.3 Investigation of the effects of compensation layer on device flatness 37                                                                                           |

|   | 2.4  | Conclusion                                                                                                                                                               |

| 3 | Lig  | ht extraction improvement of transfer-printed LEDs 43                                                                                                                    |

|   | 3.1  | Introduction                                                                                                                                                             |

|   | 3.2  | Back side roughening to improve the light extraction                                                                                                                     |

|   |      | 3.2.1 Surface Roughening of N-Polar N-GaN                                                                                                                                |

|   |      | 3.2.2 Back side roughening of released LEDs                                                                                                                              |

|   | 3.3  | Transfer printing of released LEDs                                                                                                                                       |

|   |      | 3.3.1 Fabrication of reflective trench                                                                                                                                   |

|   |      | 3.3.2 Transfer printing of released LEDs                                                                                                                                 |

|   | 3.4  | Characterization of LEDs before and after transfer printing                                                                                                              |

|   |      | 3.4.1 Electrical characterization $\ldots \ldots \ldots$ |

|   |      | 3.4.2 Electroluminescence measurements                                                                                                                                   |

|   |      | 3.4.3 Light extraction assessment                                                                                                                                        |

|   | 3.5  | Visible light communication performance of printed LEDs                                                                                                                  |

|   | 3.6  | Conclusion                                                                                                                                                               |

| 4 | Lift | -off of GaN devices by Photoelectrochemical etching 70                                                                                                                   |

|   | 4.1  | Introduction                                                                                                                                                             |

|   | 4.2  | Principle of PEC etching                                                                                                                                                 |

|   | 4.3  | Study of sacrificial layer                                                                                                                                               |

|   |      | 4.3.1 Polarization                                                                                                                                                       |

|   |      | 4.3.2 Band diagram simulation                                                                                                                                            |

|   |      | 4.3.3 C-V measurement                                                                                                                                                    |

|   |      | 4.3.4 PEC etching of designed sacrificial layers                                                                                                                         |

|   |      | 4.3.5 Investigate the effect of AlInN                                                                                                                                    |

|   |      | 4.3.6 Effect of electrolytes in the PEC-etching                                                                                                                          |

|   |      | 4.3.7 Comparing conventional sacrificial layer with Sample B 94                                                                                                          |

|   | 4.4  | Conclusion                                                                                                                                                               |

| 5 | Cor  | nclusion and future work 99                                                                                                                                              |

|   | 5.1  | Results overview                                                                                                                                                         |

|   | 5.2  | Future work                                                                                                                                                              |

|   |      |                                                                                                                                                                          |

| Α | Appendix |                                      |     |

|---|----------|--------------------------------------|-----|

|   | A.1      | Sample structures                    | 103 |

|   | A.2      | Analyses of the C-V measurement      | 104 |

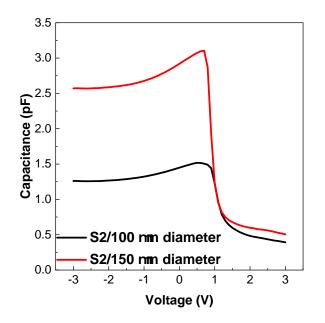

|   |          | A.2.1 Size dependency of capacitance | 104 |

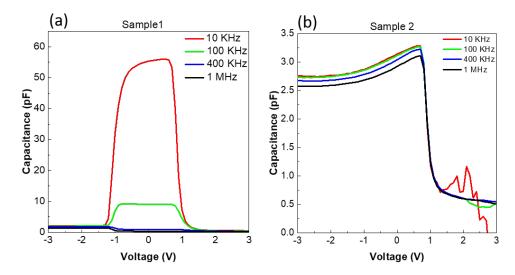

|     | A.2.2   | Effect of frequency on capacitance             | 105 |

|-----|---------|------------------------------------------------|-----|

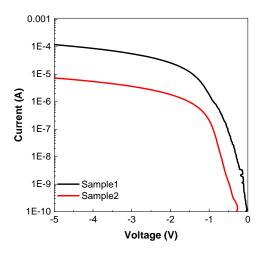

|     | A.2.3   | C-V results validity and carrier concentration | 106 |

| A.3 | Lift-of | f of LEDs using PEC etching                    | 109 |

### Bibliography

# List of Figures

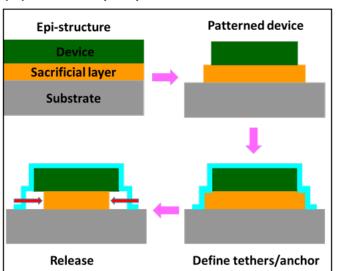

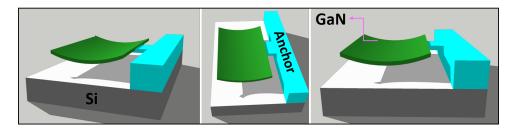

| 1.1 | Process overview for transfer printing: (a) the preparation of the devices and<br>the selective etching of the release layer while leaving the coupons suspended<br>by tethers and securely anchored on the substrate, (b) schematic micro-transfer<br>printing process for released LEDs.                                                                                                                                                                                                                                                       | 4        |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

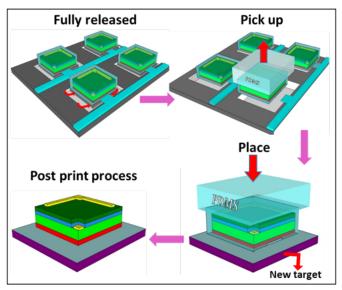

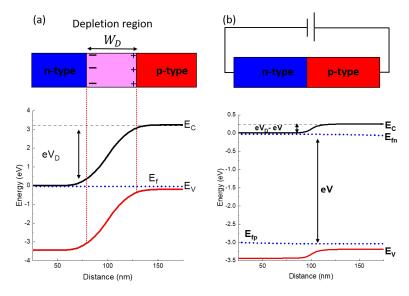

| 1.2 | The GaN p-n diode under zero bias showing the depletion region and the corresponding energy band diagram. (b) a diode under forward bias (3 V) with a                                                                                                                                                                                                                                                                                                                                                                                            |          |

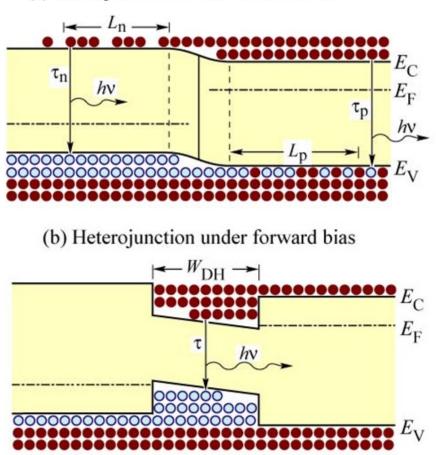

| 1.3 | reduced depletion region width and changed energy band diagram Under forward bias, the distribution of free carriers in (a) homojunctions and (b) heterojunctions. Adapted from [52]                                                                                                                                                                                                                                                                                                                                                             | 8<br>10  |

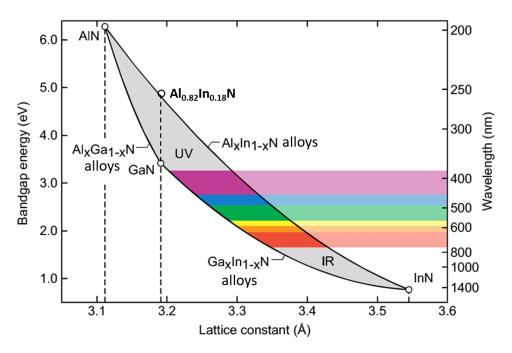

| 1.4 | The band gap energy of nitride semiconductors and emission wavelength as a function of the lattice constant. Adapted from [54]                                                                                                                                                                                                                                                                                                                                                                                                                   | 11       |

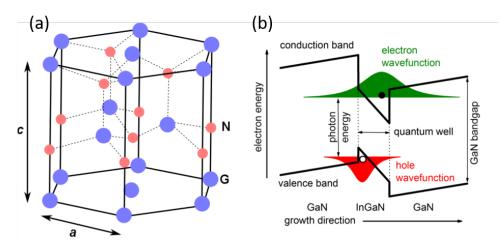

| 1.5 | <ul> <li>(a) The crystal structure of wurtzite GaN. Dashed lines indicate Ga-N bonds.</li> <li>(b) An illustration of the effects of polarization on an InGaN/GaN quantum well growing in the common Ga-polar or [0001] direction. Adapted from [57]</li> </ul>                                                                                                                                                                                                                                                                                  | 13       |

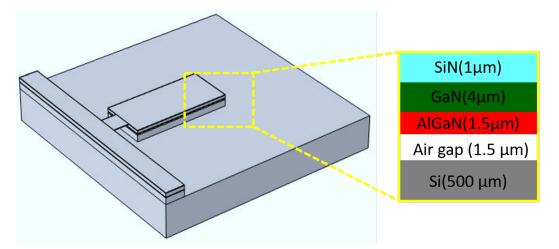

| 2.1 | A schematic 3D view of a released GaN device anchored to a substrate that bowed as a result of the stress.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21       |

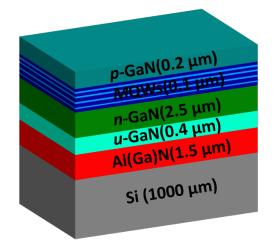

| 2.2 | Schematic structure of the LED wafer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22       |

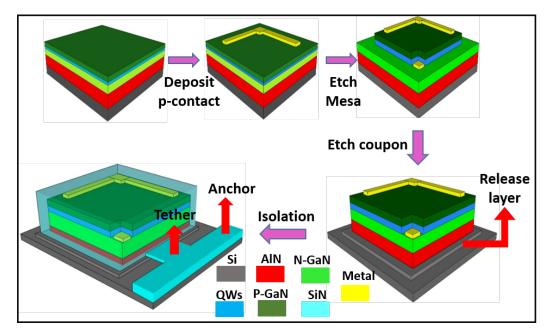

| 2.3 | Schematic of the LEDs fabrication process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24       |

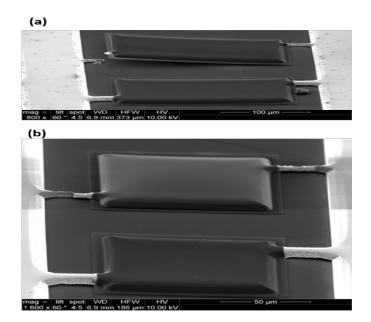

| 2.4 | Comparison between two tether widths (10 and 15 microns) for various coupon sizes (a) coupon with size of $50 \times 100 \ \mu m^2$ and (b) coupon with size of $50 \times 200$                                                                                                                                                                                                                                                                                                                                                                  |          |

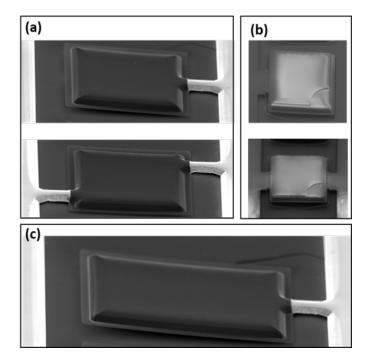

| 2.5 | $\mu m^2$ Comparison stability of devices with one and two tethers for different shape of coupons (a) coupon with size of $50 \times 100 \ \mu m^2$ , (b) with sized of $100 \times 100 \ \mu m^2$ .<br>and (c) rectangular coupon with size of $70 \times 150 \ \mu m^2$                                                                                                                                                                                                                                                                        | 25<br>26 |

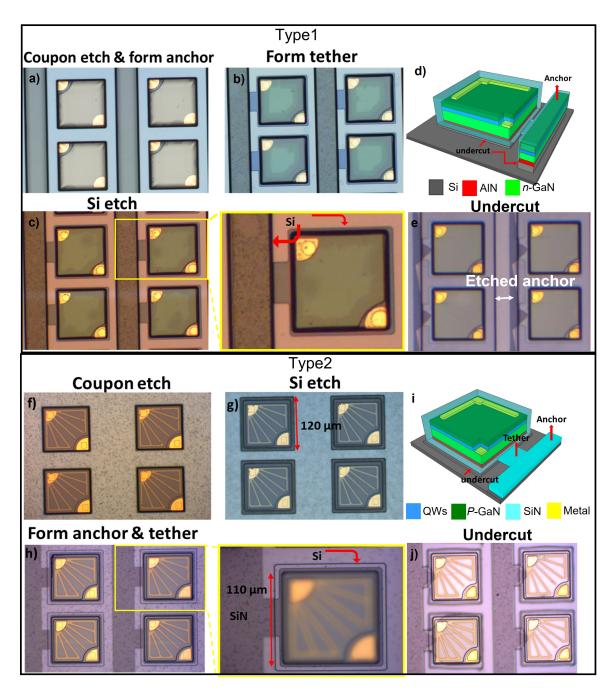

| 2.6 | Optical images of anchor type 1 process flow (a) Etching a coupon and forming<br>an anchor consisting of GaN epilayers. (b) Formation of tether using $SiN_x$ . (c)<br>Deep dry etching of Si (d) Schematic of fabricated LED (e) Released coupons<br>with etched anchor after undercut. Optical images depicting the process flow of<br>anchor type 2 (f) Coupon etch (g) Define a larger Si platform and dry etch (h)<br>Form anchor and tether with $SiN_x$ (i) Schematic of fabricated LED with SiN as<br>anchor (i) Fully undercut coupons. | 28       |

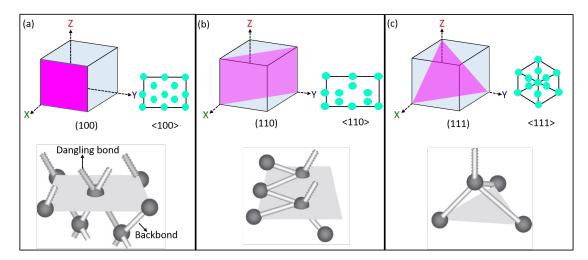

| 2.7 | Silicon crystal atomic planes (3D cube) and crystallographic directions (atomic lattice) and their corresponding configuration of Si-Si covalent bonds for a)(100), b)(110) and c)(111) low-index planes, respectively. The highlighted atoms are those composing the highlighted plane. Dangling bonds are indicated by dotted lines. The covalent bonds inhibiting one atom are illustrated in part. Adapted from [81].                                                                                                                        | 30       |

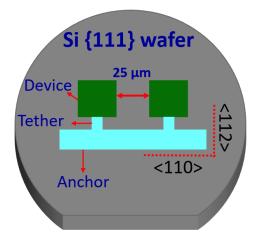

| 2.8 | A schematic of devices with a designed orientation on $a < 111 >$ oriented Si wafer.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

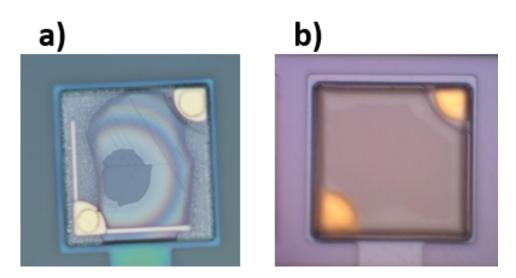

| 2.9      | Optical images of devices after full undercutting using TMAH (a) at $70^{\circ}C$ (b) at $50^{\circ}C$ .                                                                                                                                                                                                                           | 31       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

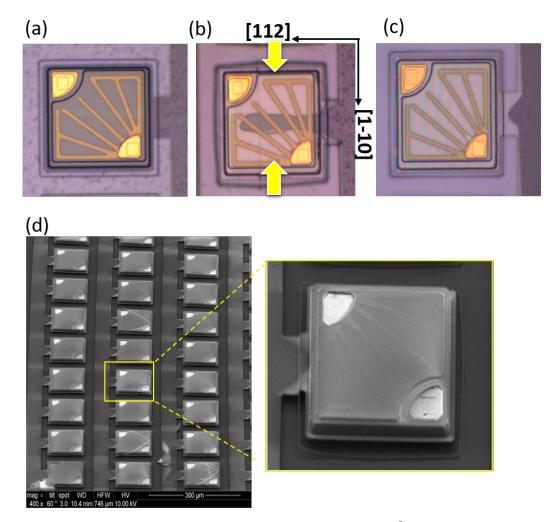

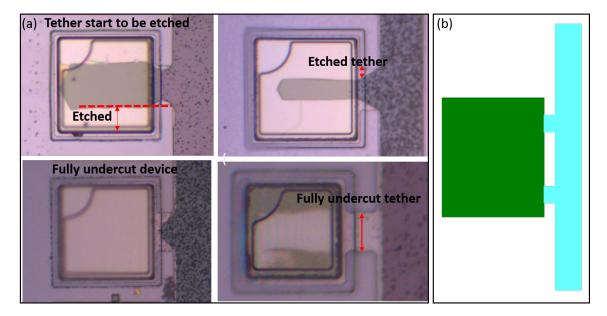

| 2.10     | Optical images of device with size of $110 \times 110 \ \mu m^2$ (a) before undercut, (b) during undercut and (c) after fully undercut. (d) SEM image of array of released LEDs with detail of an individual device.                                                                                                               | 32       |

| 2.11     | Schematic of released device used in COMSOL simulation.                                                                                                                                                                                                                                                                            | 33       |

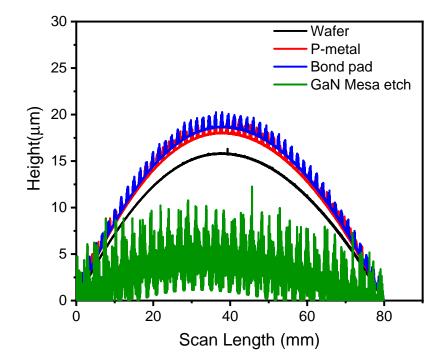

| 2.12     | Wafer bow measurement on a GaN wafer performed using a stylus profilometer<br>on a scan length of 80 mm during the fabrication process.                                                                                                                                                                                            | 34       |

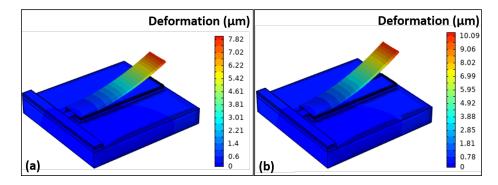

| 2.13     | Deformation comparison of released LEDs with size of $70 \times 300 \ \mu m^2$ due to thermal stress a) $SiN_x$ deposition on stress-free epilayer b) $SiN_x$ deposition on wafer with initial compressive stress.                                                                                                                 | 36       |

| 2.14     | Deformation comparison of released LEDs due to thermal stress (a) Coupon with size of $70 \times 150 \ \mu m^2$ (b) Coupon with size of $70 \times 300 \ \mu m^2$ . (c) SEM images of released LEDs with corresponding sizes.                                                                                                      | 36       |

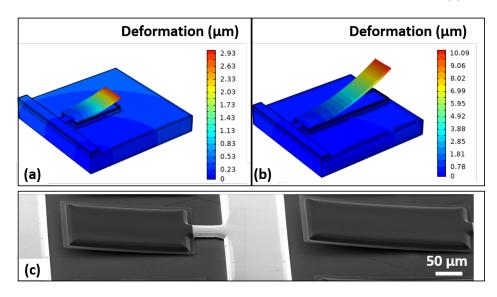

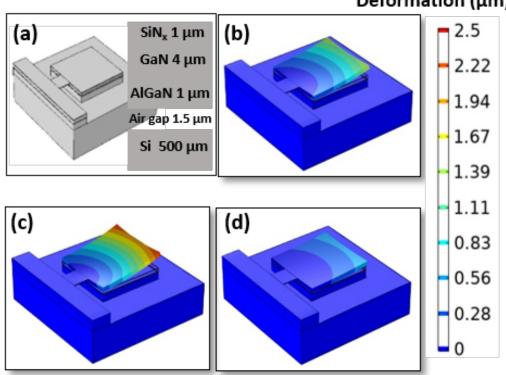

| 2.15     | Simulated deformation comparison for the coupon of size $110 \times 110 \ \mu m^2$ by deposition of $SiN_x$ with different stress. a) Simulation model,b) $SiN_x$ with neutral stress, c) $SiN_x$ with tensile stress, and d) $SiN_x$ with compressive stress.                                                                     | 37       |

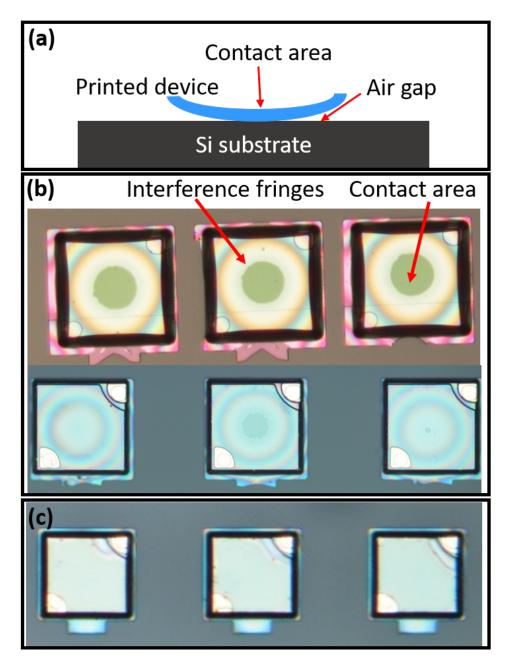

| 2.16     | a) A schematic of a printed bowed device on Si.Optical images of printed coupon<br>with size of $110 \times 110 \ \mu m^2$ with deposited $SiN_x$ with (b) neutral stress and (c)<br>compressive stress.                                                                                                                           | 39       |

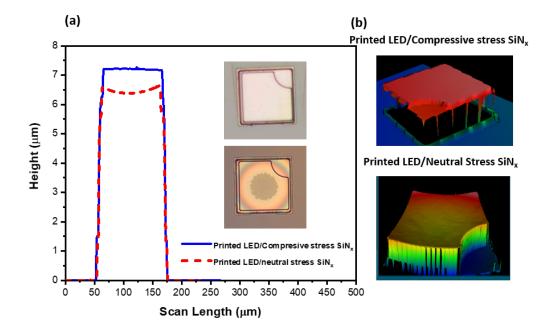

| 2.17     | Device curvature with and without compensating $SiN_x$ layer for device size of $110 \times 110 \ \mu m^2$ ; the inset shows optical images of printed LED swith compressive-<br>stress SiNx(upper) and neutral-stress SiNx(lower). b) 3D images of the printed                                                                    |          |

| 2.18     | devices                                                                                                                                                                                                                                                                                                                            | 40<br>41 |

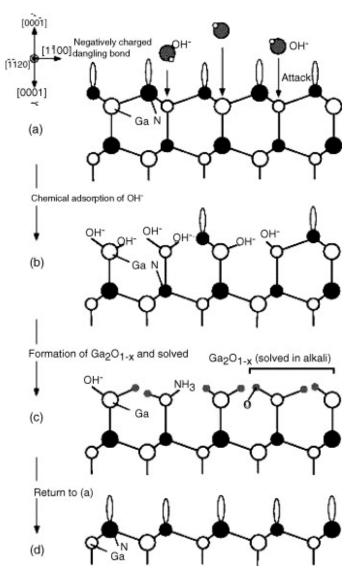

| 3.1      | Schematic diagram of the cross section of N-polar GaN viewed along direction $[\bar{1}\bar{1}20]$ to illustrate the mechanism of polarity selective etching.(a) Layer terminated by nitrogen with a negatively charged dangling bond on each nitrogen atom.(b) Hydroxide ion adsorption (c) Oxide formation (d) Oxide dissolution. |          |

|          | Adapted from [108]                                                                                                                                                                                                                                                                                                                 | 46       |

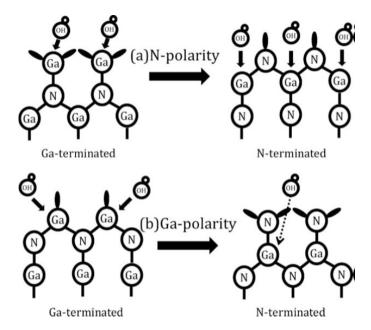

| 3.2      | GaN etching of different polarities: (a) N-polar GaN can be etched by alkaline,<br>and (b) dangling bonds of N atoms prevent Ga atoms from being attacking by<br>alkalizing in Ga-polar GaN. Adapted from [109]                                                                                                                    | 47       |

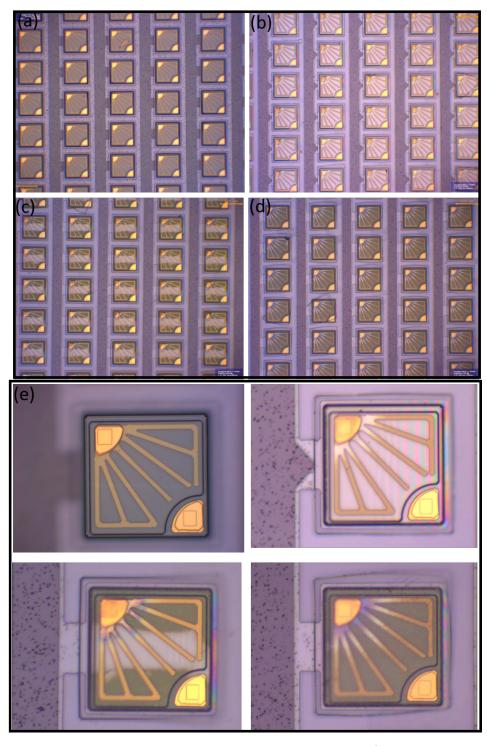

| 3.3      | Optical images of array of LEDs with size of $110 \times 110 \ \mu m^2$ (a) before undercut<br>(b) after fully undercut (c) released LEDs with partially roughened backside, (d)<br>with completely roughened backside and (e) showing the individual devices at                                                                   |          |

| <b>.</b> | each stage.                                                                                                                                                                                                                                                                                                                        | 50       |

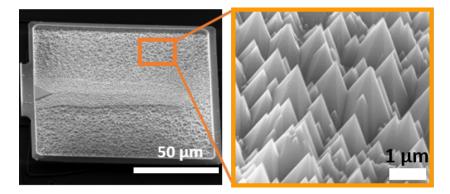

| 3.4      | SEM images of released LED with size of $110 \times 110 \ \mu m^2$ with roughened backside.                                                                                                                                                                                                                                        | 51       |

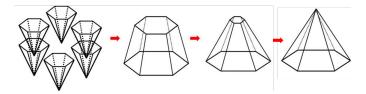

| 3.5      | A schematic representation of the formation and development of the pyramid.<br>Adapted from [124].                                                                                                                                                                                                                                 | 51       |

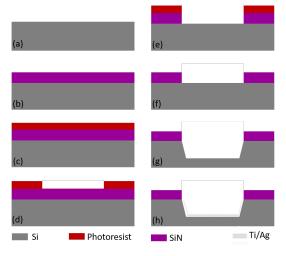

| 3.6      | Schematic diagram of fabrication process of trenches (a) Silicon wafer, (b) $SiN_x$ deposition, (c) photoresist deposition, (d) photoresist patterning, (e) dry etching of $SiN_x$ , (f) remove photoresist, (g) wet etching of Si and (g) deposition of reflective layer.                                                         | 53       |

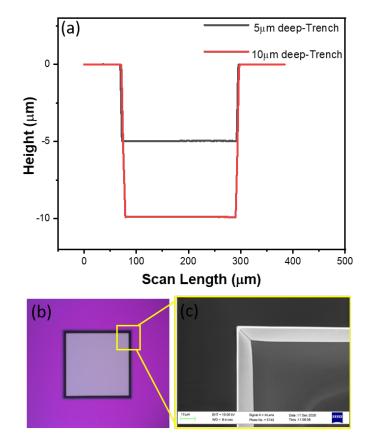

| 3.7      | (a) Depth of fabricated trench in Si, (b) Top-view optical image and (c) SEM                                                                                                                                                                                                                                                       | 03       |

| 0.1      | image of corner of trench.                                                                                                                                                                                                                                                                                                         | 53       |

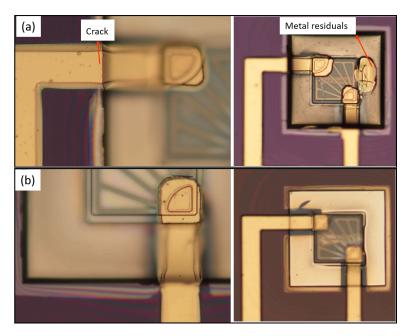

| 3.8          | Optical images of metal interconnection of device into trench (a) before opti-                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EE |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

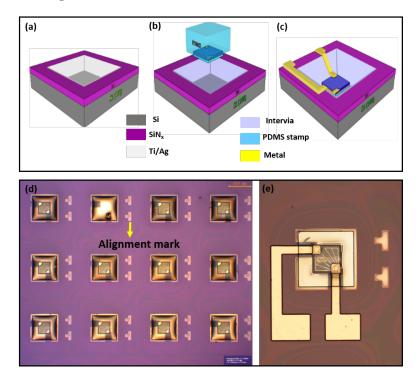

| 3.9          | mization of lithography step. (b) after optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55 |

|              | device into reflected-coated trench coated with Intervia. (c) Metal interconnec-                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|              | tion after printing device. Optical image of (d) printed LEDs into trenches. (e)                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55 |

| 3 10         | Metal interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55 |

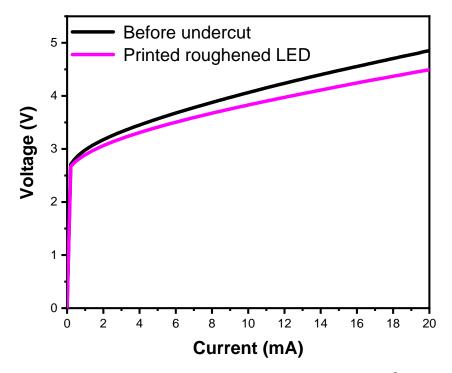

| 3.10         | undercut and after transfer printing. $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                  | 56 |

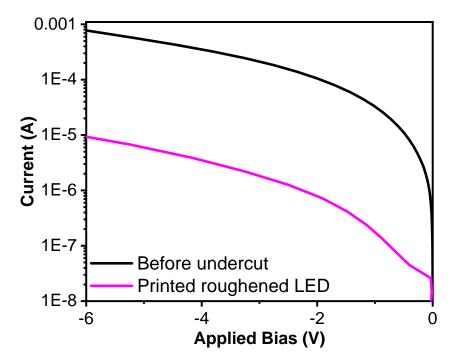

| 3.11         | I-V curves under reverse bias.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57 |

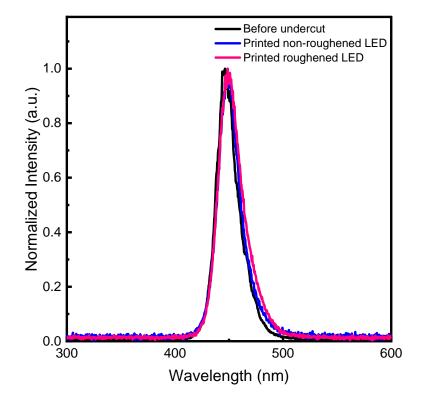

|              | Electroluminescence spectra of non-roughened and roughened $\mu$ LEDs before un-                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ۰. |

|              | dercut and after printing on flat surfaces at $15 mA$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58 |

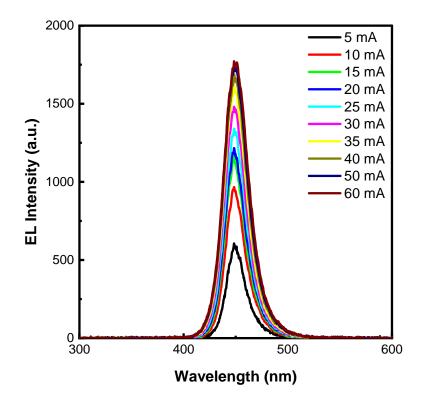

| 3.13         | EL spectra of transfer printed roughened $\mu \rm LED$ operating under different currents.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59 |

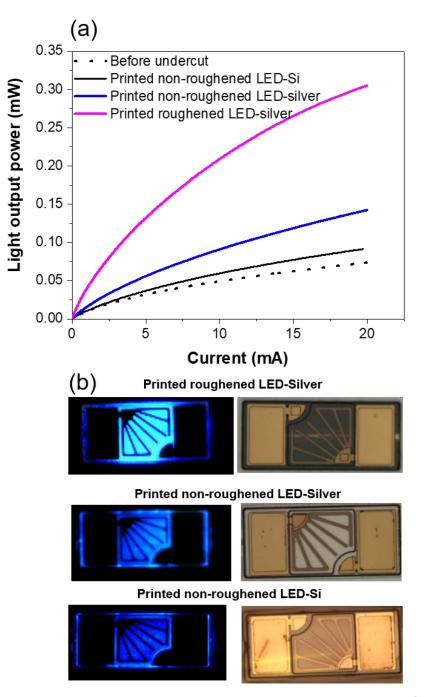

| 3.14         | (a) Light output power collected into NA=0.5 of $110 \times 110 \ \mu m^2$ LED before<br>undercut, non-roughened LED on Si and silver and roughened LED on silver. (b)<br>fluorescent microscope images of printed LEDs and their corresponding optical                                                                                                                                                                                                                                                                                    |    |

| _            | image on the right.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60 |

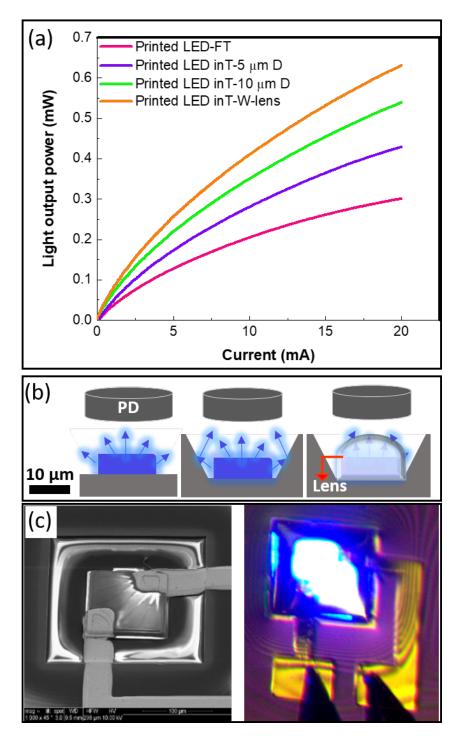

| 3.15         | (a) Light output collected from $110 \times 110 \ \mu m^2$ LED on original substrate, after<br>printing on flat target (FT), in trench with depth of 5 $\mu m$ (T-5 $\mu m$ D) and 10<br>$\mu m$ (T-10 $\mu m$ D) and printed LED into 10 $\mu m$ -deep trench with covered lens<br>(c-W-lens).(b) Schematic of printed LED on flat target, into trench and into<br>trench with lens to show the effect of sidewalls and lens in light redirection to<br>photo detector (PD). (c) SEM (left) and Optical image (right) of a lit-up printed |    |

|              | LED into 10 $\mu$ m-deep trench at 2 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62 |

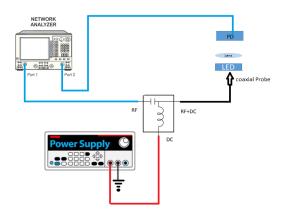

| 3.16         | Setup configuration for bandwidth measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63 |

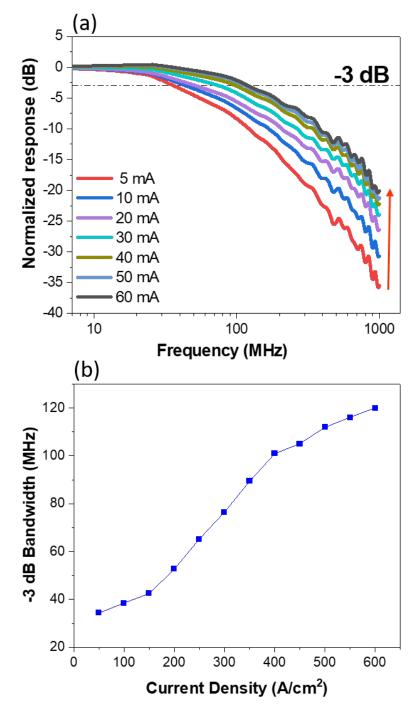

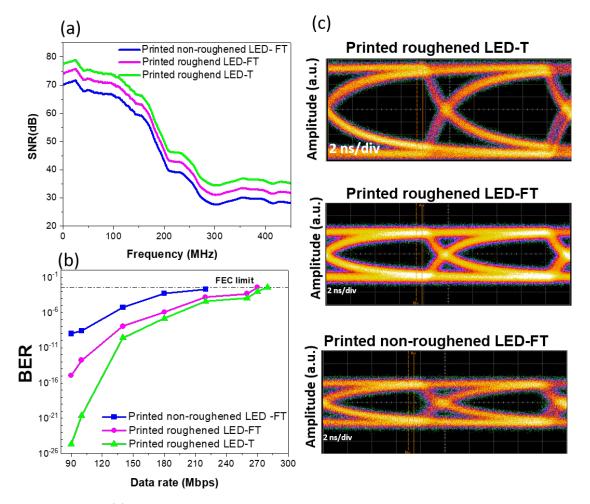

| 3.17         | $\mu m^2$ into reflective trench as a function of the injected current of the LED. (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 3.18         | Extracted $-3dB$ modulation bandwidth versus current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64 |

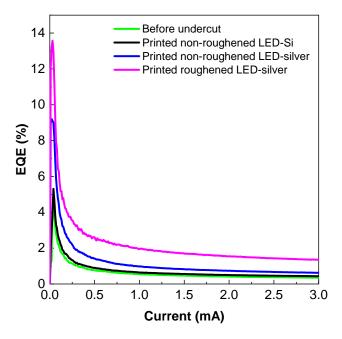

| 3.19         | platform at data rate of 100 Mbps and injection current of 40 mA Comparison of external quantum efficiency of $\mu$ LEDs before undercut, non-roughened $\mu$ LEDs on Si and silver and roughened $\mu$ LEDs on silver as a function                                                                                                                                                                                                                                                                                                       | 67 |

|              | of current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68 |

| 4 1          | Schementing of DEC stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70 |

| $4.1 \\ 4.2$ | Schematic of PEC etching.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72 |

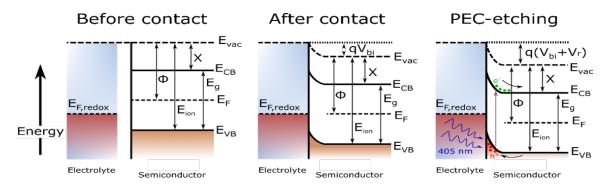

| 4.2          | Schematics of energy bands of semiconductor and electrolyte (a -b) before and<br>after contact and (c) during PEC-etching process where the photo-induced holes                                                                                                                                                                                                                                                                                                                                                                            |    |

|              | in the InGaN are trapped at the interface due to the band-bending                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73 |

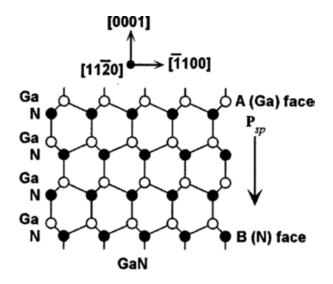

| 4.3          | Spontaneous polarization field direction of GaN. Note that open circles refer to                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|              | the Ga. Adapted from [179]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 75 |

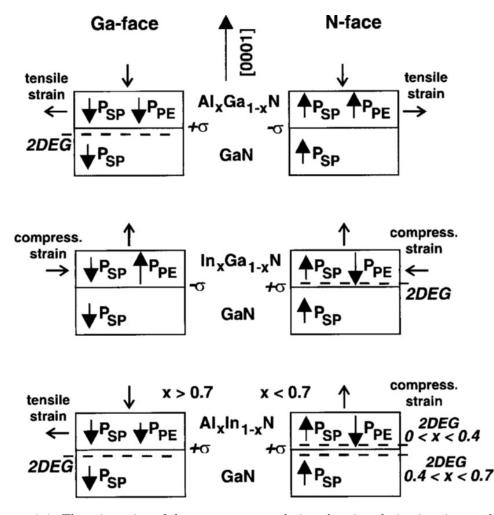

| 4.4          | The orientation of the spontaneous and piezoelectric polarizations in pseudomor-<br>phic grown wurtzite AlGaN/GaN, InGaN/GaN, and AlInN/GaN heterostruc-<br>tures with Ga- or N-face polarities. In the case where the polarization induced<br>charges is positive, a 2DEG can be confined close to the interface in the layer                                                                                                                                                                                                             |    |

|              | with a smaller bandgap. Adapted from [178]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76 |

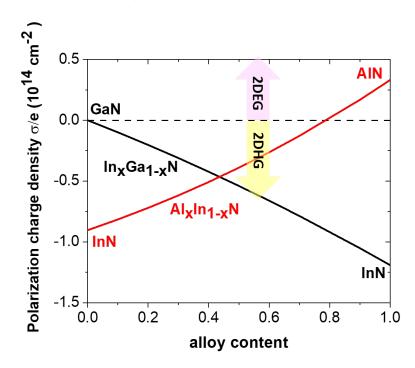

| 4.5          | The density of polarization charges bound at the heterointerface of InGaN/GaN and AlInN/GaN heterostructures grown on Ga-face GaN. Positive signs indicate                                                                                                                                                                                                                                                                                                                                                                                 |    |

|              | the presence of a 2DEG, while negative signs indicate the presence of a 2DHG.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 78 |

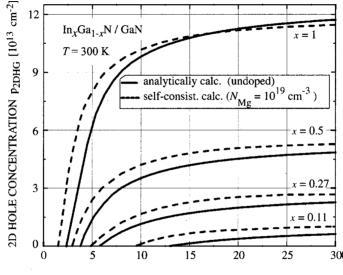

| 4.6  | The dependence of the 2DHG density on the thickness of the InGaN capping<br>layer for different indium contents x of the capping layer. Adapted from [182]                                                                                                                                                                         | 79  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

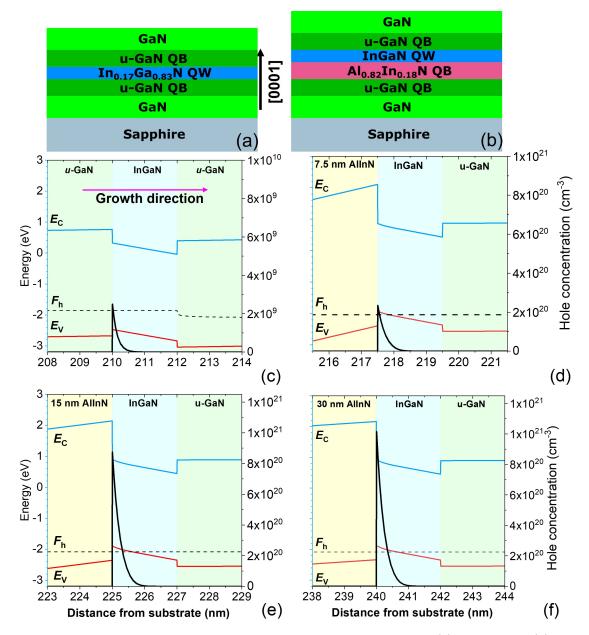

| 4.7  | Cross-sectional schematic of structures without AlInN (a) with AlInN (b) as<br>barrier. (c-f) Magnified of simulated energy band diagrams and calculated hole<br>concentrations at a bias of 2 V applied to the GaN for AlInN layer thicknesses<br>of 0, 7.5, 15 and 30 nm respectively are shown. The dashed line shows the Fermi |     |

|      | level.                                                                                                                                                                                                                                                                                                                             | 81  |

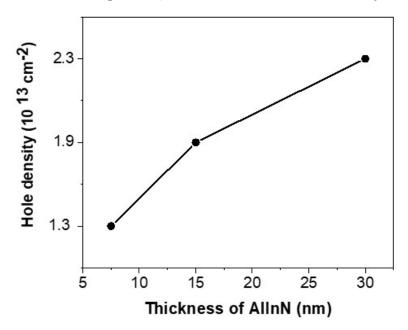

| 4.8  | Hole density as a function of AlInN thickness for a fixed thickness of InGaN of                                                                                                                                                                                                                                                    |     |

|      | 2 nm                                                                                                                                                                                                                                                                                                                               | 82  |

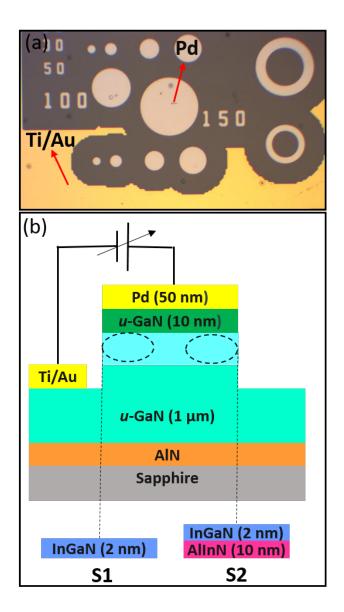

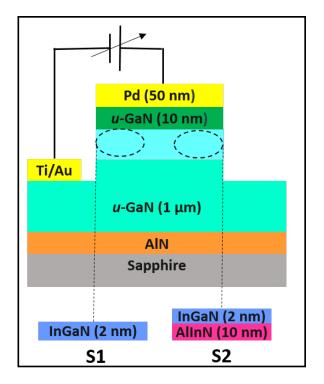

| 4.9  | (a) Optical image and (b) a schematic of the structures used in C-V measurement.                                                                                                                                                                                                                                                   | 84  |

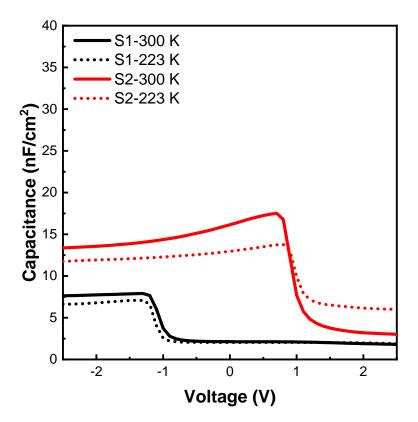

| 4.10 | C-V characteristics of samples without (S1) and with (S2) 10 nm AlInN measured                                                                                                                                                                                                                                                     |     |

|      | at 223 K and 300 K as a function of bias.                                                                                                                                                                                                                                                                                          | 85  |

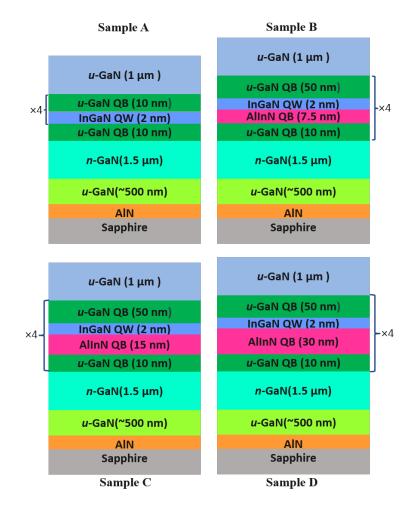

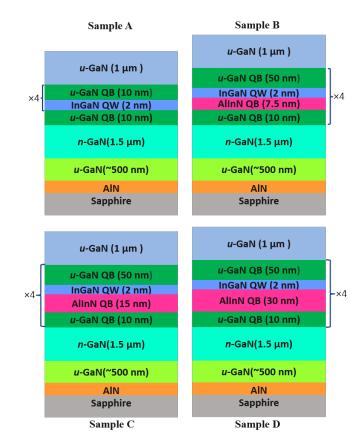

| 4.11 | Cross-sectional schematic showing the four types of structures utilized in PEC-                                                                                                                                                                                                                                                    | ~ - |

|      | etching experiments.                                                                                                                                                                                                                                                                                                               | 87  |

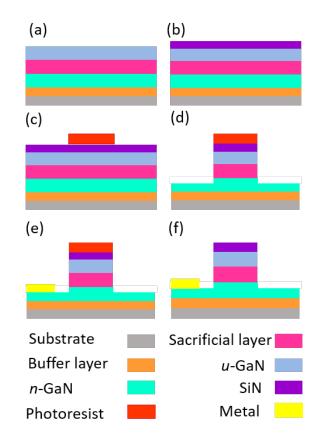

| 4.12 | Schemtatic of the process flow. (a) epitaxial structures of sample (b) SiN depos-<br>tion (c) Lithography for mesa patterning (d) dry etch to the n-GaN (e) Metal                                                                                                                                                                  |     |

|      | deposition (f) remove photoresist.                                                                                                                                                                                                                                                                                                 | 88  |

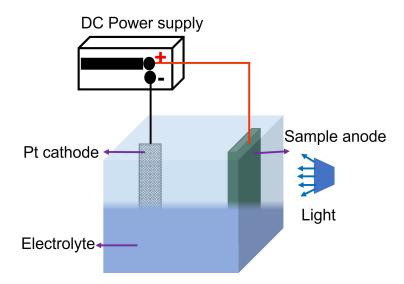

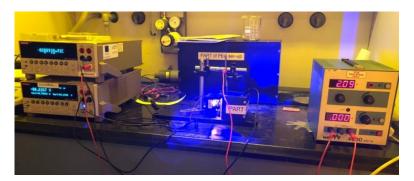

|      | PEC setup used in these experiments.                                                                                                                                                                                                                                                                                               | 89  |

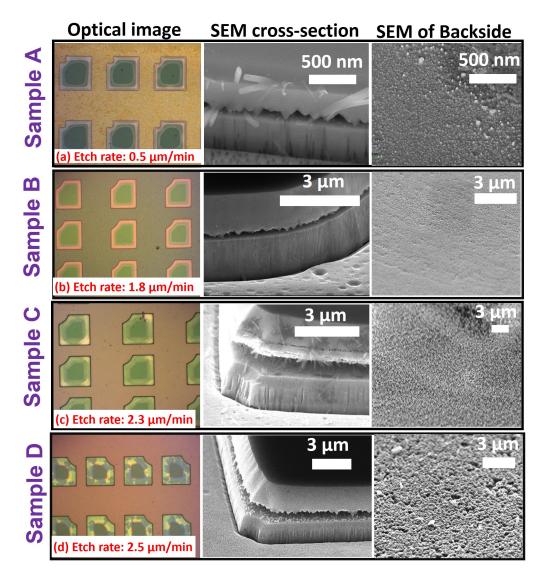

| 4.14 | Optical (top-view) and SEM (cross-section and center of backside) after PEC-<br>etching of samples (a) w/o, (b) 7.5 nm, (c) 15 nm and (d) 30 nm AlInN with size<br>of $50 \times 50 \ \mu m^2$ under front-illumination with a power density of 105 mW/cm <sup>2</sup> ,                                                           |     |

|      | a bias of 2 V and 0.1 M KOH solution.                                                                                                                                                                                                                                                                                              | 91  |

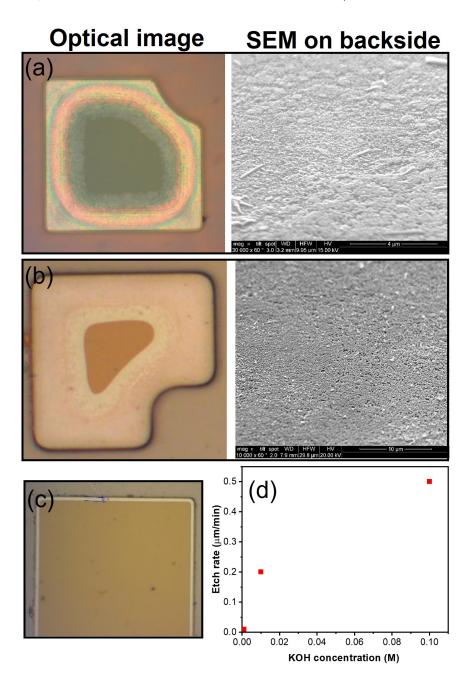

| 4.15 | The optical (top-view) image of sample A with size of $50 \times 50 \ \mu m^2$ during PEC                                                                                                                                                                                                                                          |     |

|      | etching and the corresponding SEM image of its backside in the center after fully                                                                                                                                                                                                                                                  |     |

|      | undercutting in (a) 0.1 M KOH (b) 0.01 MKOH (c) 0.001 M KOH and (d) shows                                                                                                                                                                                                                                                          |     |

|      | the etch rate of sample A versus the molarity of KOH                                                                                                                                                                                                                                                                               | 92  |

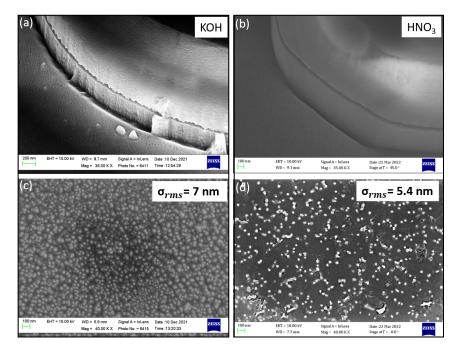

| 4.16 | SEM images of mesa sidewall after PEC-etching sample A in (a) KOH and (b)                                                                                                                                                                                                                                                          |     |

|      | $HNO_3$ . (c-d) The center of the backside of released devices after etching                                                                                                                                                                                                                                                       | 93  |

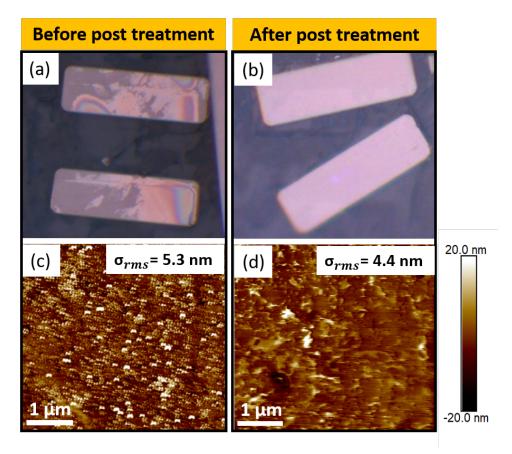

| 4.17 | Optical images of the backside of released devices with size of 20 $\mu m \times 100$                                                                                                                                                                                                                                              |     |

|      | $\mu m$ after PEC etching using $HNO_3$ (a) before post treatment (b) after post                                                                                                                                                                                                                                                   |     |

|      | treatment and (c-d) their corresponding AFM scan of the center over $5 \times 5 \mu m^2$ .                                                                                                                                                                                                                                         | 94  |

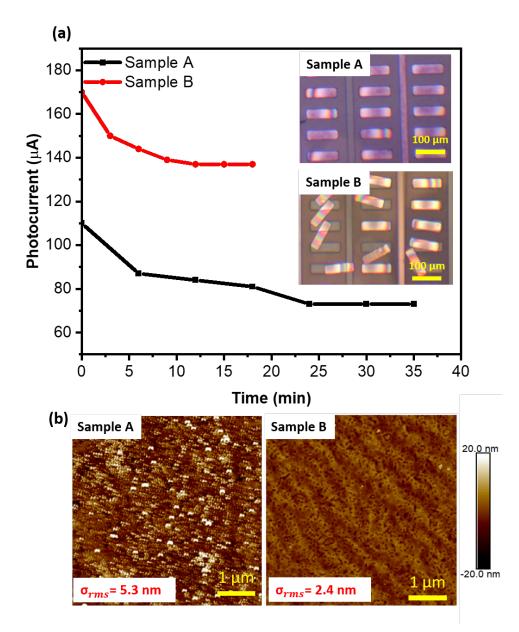

| 4.18 | (a) Photocurrent vs time for sample A (without -AlInN) and sample B (with 7.5-                                                                                                                                                                                                                                                     |     |

|      | nm-thick AlInN) with size of 20 $\mu m \times 100 \ \mu m$ . The inset shows optical images                                                                                                                                                                                                                                        |     |

|      | of the two samples after 20 min PEC-etching in HNO3. (b) AFM images of the                                                                                                                                                                                                                                                         |     |

|      | center of their backside surfaces.                                                                                                                                                                                                                                                                                                 | 96  |

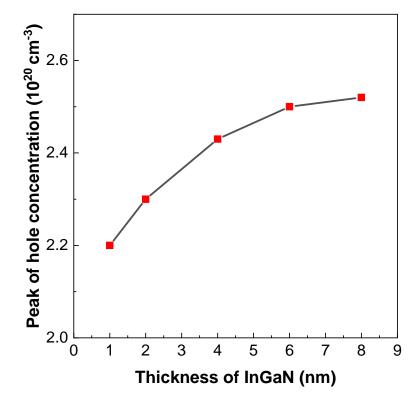

| 4.19 | The dependence of the peak of hole concentration on the thickness of InGaN for                                                                                                                                                                                                                                                     |     |

|      | a fixed thickness of AlInN (7.5 nm)                                                                                                                                                                                                                                                                                                | 97  |

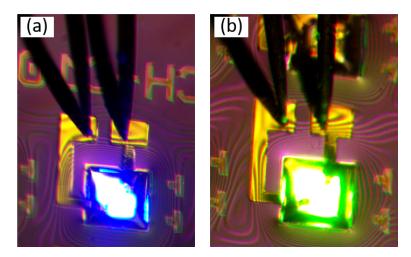

| 5.1  | Optical images of lit-up printed $\mu$ LEDs with size of 110 $\mu m \times 110 mum$ into                                                                                                                                                                                                                                           | 100 |

|      | trench a) Blue LED at 2 mA b) Green LED at 5 mA                                                                                                                                                                                                                                                                                    | 102 |

| A.1  | Schematic of four types of structures used in PEC etching experiments                                                                                                                                                                                                                                                              | 103 |

| A.2  |                                                                                                                                                                                                                                                                                                                                    | 100 |

| A.3  |                                                                                                                                                                                                                                                                                                                                    | 104 |

| A.4  | C-V curves of (a) Sample 1 and (b) Sample 2 with Schottky contacts of 150 $\mu m$                                                                                                                                                                                                                                                  | 100 |

| 11.4 |                                                                                                                                                                                                                                                                                                                                    | 106 |

| A 5  |                                                                                                                                                                                                                                                                                                                                    | 100 |

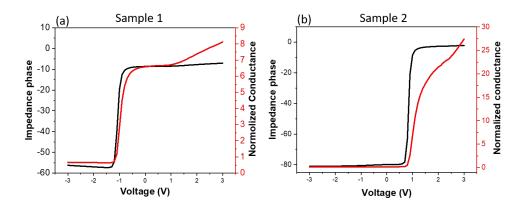

| A.6  | Impedance and normalized conductance as a function of voltage (a) Sample 1                                                                                                                                                                                                                                                         | 100 |

| 11.0 |                                                                                                                                                                                                                                                                                                                                    | 108 |

|      | and (o) semple 2                                                                                                                                                                                                                                                                                                                   | 100 |

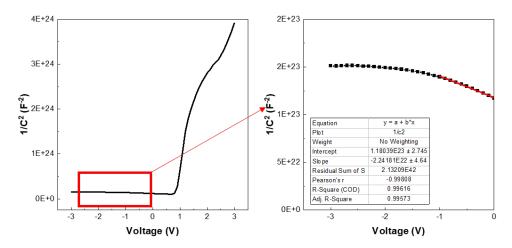

| A.7  | $1/C^2$ as a function of voltage for sample 2                              | 108 |

|------|----------------------------------------------------------------------------|-----|

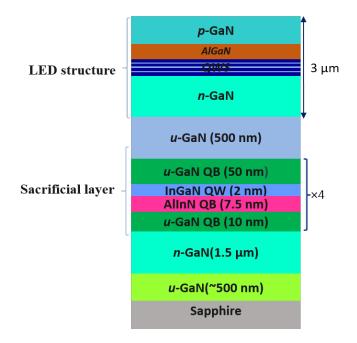

| A.8  | Cross-sectional schematic of LED structure on sacrificial layer.           | 109 |

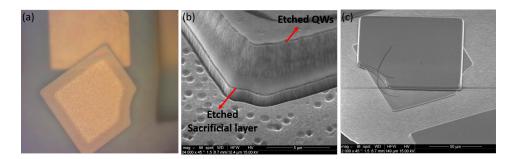

| A.9  | (a) Optical image of released LED after being fully undercut (b) SEM cross |     |

|      | section and (c) SEM (top-view) of released LED.                            | 109 |

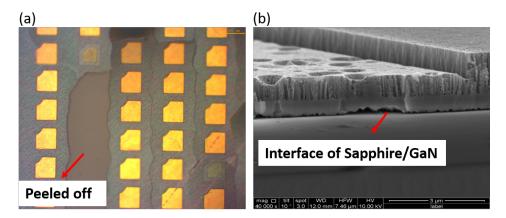

| A.10 | (a) Optical image of LED during the PEC etching when part of device peeled |     |

|      | off(b) SEM cross section of interface of sapphire/GaN                      | 110 |

|      |                                                                            |     |

# List of Tables

| 2.1 | Applied material properties for the model                                      | 34 |

|-----|--------------------------------------------------------------------------------|----|

| 2.2 | Calculated stress of wafer before and during microfabrication process of LEDs. | 35 |

| 4.1 | Applied material parameters for the calculation [180]                          | 78 |

# List of Acronyms

| GaN                 | <br>Gallium nitride                     |

|---------------------|-----------------------------------------|

| PICs                | <br>Photonic integrated chips           |

| $\operatorname{EL}$ | <br>Electroluminescence                 |

| HVPE                | <br>Hydride vapour phase epitaxy        |

| AlN                 | <br>Aluminium nitride                   |

| LEEBI               | <br>low energy electron beam irritation |

| KOH                 | <br>Potassium hydroxide                 |

| OFN                 | <br>Oxygen free nitrogen                |

| QW                  | <br>quantum well                        |

| $\mu \text{LED}$    | <br>micro-Light Emitting Diode          |

| InGaN               | <br>Indium gallium nitride              |

| $\mathrm{Si}O_2$    | <br>Silicon dioxide                     |

| $\mathrm{Si}N_x$    | <br>Silicon nitride                     |

| WPE                 | <br>Wall-plug efficiency                |

| IQE                 | <br>Internal quantum efficiency         |

| EQE                 | <br>External quantum efficiency         |

- $\ensuremath{\operatorname{QCSE}}$  ..... Quantum-confined stark effect

- BOE ..... Buffered Oxide Etch

TMAH ..... Tetramethylammonium hydroxide

TP ..... Transfer Print

PDMS ..... polydimethylsiloxane

ICP ..... Inductive coupled plasma

PECVD ..... plasma-enhanced chemical vapor deposition

PR ..... photoresist

GRIN ..... Gradient refractive index

2DHG ..... two-dimensional hole gas

2DEG ..... two-dimensional electron gas

# List of Publications

#### First author publications

- Z. Shaban, Z. Li, B. Roycroft, M. Saei, T. Mondal, and B. Corbett, "Transfer Printing of Roughened Gan-Based Light-Emitting Diodes into Reflective Trenches for Visible Light Communication", in Advanced Photonics Research, p.2100312, March 2022.

- Z. Shaban, M.saei, B. Corbett and Z.Li "Integration of high performance GaN LEDs for communication systems and smart society", in IEEE 72nd Electronic Components and Technology Conference (ECTC), pp. 2111-2115, 2022.

- Z. Shaban, V. Zubialevich, E.A. Amargianitakis, F. Bilge Atar, P.J. Parbrook, Z. Li and B. Corbett "InGaN/AlInN interface with enhanced holes to improve photoelectrochemical etching and GaN device release", in Semiconductor Science and Technology, March 2023.

#### **Conference** posters

- 1. **Z. Shaban**, Z.Li and B. Corbett "Light enhancement of GaN LEDs by transfer from original substrate to reflective trench", UK Nitride consortium, 2022.

- 2. Z. Shaban, Z.Li and B. Corbett "Stress management on GaN LEDs for Transfer Printing", Photonics Ireland conference, 2021.

Z. Shaban, Z.Li and B. Corbett "Controlling device bow for effective transfer of GaN LEDs to non-native substrates", IPIC, 2020.

## Declaration

I, Zeinab Shaban hereby declare that, unless otherwise stated, this work is my own, and that it has not been submitted for another degree, either at University College Cork or elsewhere.

Signed: Zeinab Shaban

### Abstract

3D integration of optoelectronic devices is a crucial future technology, which can be applied in the areas of photonic integrated circuits, flexible displays, communication and more. Among the various technologies, micro-transfer printing has emerged as a precise and cost-effective way to assemble devices for 3D integration. To enable this technology, devices must be released from their native substrates, which open up a lot of possibilities. It can achieve integration with flexible or heat-conductive backplanes, as well as heterogeneous integration of multiple materials on a common platform, resulting in miniaturised chips. Also one can benefit from reclaiming and reusing the original substrates to reduce the production cost significantly. On the other hand, GaN devices exhibit unique optical properties in optoelectronics compared to other semiconductors, and GaN-based LEDs have established themselves in a variety of applications, due to their low power consumption, long lifetime, short response time, and high brightness. This thesis has focused on releasing high performance GaN LEDs and addressing their associated issue for micro-transfer printing.

The first part of this work is focused on releasing and transfer-printing of GaN LEDs grown on Si substrate. There are several factors that limit the performance and manufacturing of GaN LEDs on Si. One issue is related to the deformation of the released coupons due to their high inbuilt strain, which could result in transfer-printing failures as well as challenges during the post-print integration process. To address this issue, COMSOL software was used to study the stress effect on the devices. Experimentally, the intrinsic deformation of the released LEDs was compensated by using compressed  $SiN_x$  layers that resulted in flat devices after release. Another issue is related to the low light extraction for GaN LEDs on Si. To solve this problem, the underside of the released LEDs is roughened during the coupon preparation process prior to transfer printing. Furthermore, using the unique properties of transfer printing, the roughened LEDs are printed inside a fabricated reflective trench with 10  $\mu m$  depth to direct the light to the surface normal. Results showed that roughening along with the reflective trench increased the collected power by a factor of ~ 7 compared with LEDs on the original substrate.

A second part of this study examines the release of GaN-based structures from substrates (i.e. sapphire or bulk GaN) by photoelectrochemical (PEC) etching when pure chemical etching is not possible. A sacrificial layer which can obtain smooth etch surfaces and uniform etching with high selectivity is needed. Also, from the perspective of transfer printing, thick rather than thin sacrificial layers are preferred to facilitate the releasing and picking process. In this work, 300 *nm*-thick releasing layers comprising of InGaN/AlInN stacks are proposed for PEC etching. The presence of two-dimensional hole gas at the interface of InGaN/AlInN due to the strong polarization field are indicated by modelling and capacitance-voltage measurement. This resulted in a smoother surface with a three times higher etch rate compared to the conventional InGaN/GaN superlattice structures used for PEC etching. Moreover, various electrolytes and post-PEC treatment were studied to improve the surface smoothness.

Further work should be done to determine the impact of the adhesion layer in transfer printing on heat generation and device performance. Using the optimized sacrificial layer to release other structures like lasers should also be investigated.

### Acknowledgements

I would like to thank my supervisor, Brian Corbett for giving me the opportunity to do my PhD in the III-V device group. Thank you for everything Brian, It has been a pleasure working with you, and I have learned so much from you both technically and personally. I am very grateful for all the support you have provided throughout my PhD without your help I could not have completed my PhD.

Beside my supervisor, I would like to thank Peter J. Parbrook and Peter O'Brien for their insightful comments and encouragement. Thanks also to Alan and Asa for their time and dedication as jury members. Your comments have been extremely helpful. Also, thanks to Pleun Maskant, who was a tremendous help to me during the early stages of my PhD, for all his advice and kindness.

As well, I would like to thank Zhi and Vitaly for their outstanding assistance during my studies. I greatly appreciate the guidance, discussions and knowledge exchange that you provided for me.

I wish to extend my special thanks to all my colleagues especially Fatih, John, Mahbub, Emmanouil, Brendan, Rory, Tanmay, Muhammet, Peter, James, Hema, Meena, Pietro and supportive individuals in the cleanroom: Dan, Carmel, Farzan, Alin, Raja and Colin who have helped me throughout these years since I joined Tyndall. I am also grateful to Antonio for all the valuable advice and information he provided to me in preparing for viva.

I would also like to thank my parents for their support, constant love and sacrifices without which I could not have achieved this far. In addition, I would like to express my gratitude to my siblings for their support throughout these years.

Finally and most importantly, I would like to express my deepest gratitude to my husband, Mehrdad, for his support. It is difficult to express my appreciation for you since it is so boundless. Thank you for always being there for me. Thanks for providing me with unfailing support, love and continuous encouragement throughout these years. None of this could have happened without your support. To my beloved Mehrdad Saei for his support

### Chapter 1

# Introduction

The increasing complexity of photonic device applications necessitates the integration of many components on one substrate in order to create a compact, efficient, and cost-effective chip. Over the past decade micro-transfer printing ( $\mu TP$ ) has emerged as a method for heterogeneously integrating components of different materials or fabrication platforms in order to achieve a variety of enhanced functions or applications [1]. It is necessary to release the devices from their growth substrate in order to utilize this technology. In this thesis, the focus is primarily on the release of devices from the growth substrate so that they can be printed using this technology. In particular, GaN LEDs are being released because integrated chips are increasingly demanding smaller and more efficient sources of light as applications in numerous industries become more complex [2]. LEDs based on gallium nitride (GaN) have gained a lot of interest for a variety of applications, especially in display and communication systems, due to their low power consumption, long lifetime, short response time and high brightness [3, 4]. An LED integrated directly onto a chip, for example, could provide a compact, low-cost, and reliable way to use LED for displays, sensors, or communications. This introduction provides an overview of integration techniques, with a particular emphasis on transfer printing technology and the process required to enable the transfer printing of devices. The development of GaN LEDs is discussed in this chapter as they are one of the main light sources used in a variety of applications. Moreover, the advantages and disadvantages of each substrate for GaN LEDs are discussed, as well as the methods for lift-off of GaN LEDs from their respective substrates.

#### **1.1** Introduction of integration techniques

3D integration of optoelectronic devices is a crucial technology for the development of practical devices such as photonic integrated circuits, flexible displays and communications. Various optoelectronic devices need to be packaged or coupled, either optically or electronically, with a variety of components to become functional. Manufacturing costs associated with packaging processes are significant, and these processes are often associated with reliability issues. Many years of effort have been devoted to developing an accurate and cost-effective integration technology [5, 6]. There are three principal approaches to wafer-level integration, which can be categorized as monolithic, hybrid, and heterogeneous. The following section discusses various integration techniques for light emitting devices.

#### 1.1.1 Monolithic integration

The monolithic integration method uses a single substrate to fabricate devices. The entire process is typically carried out at the wafer level. Lattice matching and epitaxial plane selection are vital requirements for this type of integration. As the optimal structure varies from device to device, the fabrication process needs to be adjusted accordingly [7, 8]. An example would be the development of highly efficient inorganic red, green, and blue emitting materials on a single wafer, which is still in its infancy and poses many challenges. Currently, the highly efficient blue and green emitting LED structures are GaN-based, while the efficient red emitters are AlGaInP-based [9, 10].

#### 1.1.2 Hybrid and heterogeneous integration

A hybrid integration approach can be used to avoid the problems associated with monolithic fabrication by fabricating the devices on separate substrates. Afterwards, they are diced into individual chips and assembled. As a hybrid integration approach, flip-chip integration is the most commonly adopted in the industry due to its environmental friendliness (eliminating lead material and flux cleaning), low temperature process and fine pitch capability. [11–13].

This technique allows different devices to be integrated on a variety of substrates due to the separate fabrication processes of each wafer. By using this technique, individual components are integrated after the overall fabrication process has been completed. As a result, this process

offers the advantage of testing and characterizing a component or device prior to its integration. In this manner, the best-performing devices can be selected, while the non-functional components can be discarded, thereby enhancing the quality of the chip [14]. However, as flip-chip assembly requires precise alignment, it limits the possibility of scaling up and reducing the cost of photonic integrated chips (PICs) [15–17].

As a solution to this challenge, heterogeneous integration has been explored in recent years using die-to-wafer or wafer-to-wafer bonding, where the critical alignment of the devices is achieved by lithography. A heterogeneous integration process involves the integration of two or more different materials technologies on a single chip [18]. The process is generally carried out during the initial to mid-stages of the fabrication of the PIC chip [19]. The main advantage of heterogeneous integration is that it can perform the same functions as monolithic integration, meaning that it provides accurate submicron alignment since alignment is achieved through wafer-scale lithography. Additional benefits include reliable performance and low costs due to economies of scale. This makes it suitable for high-volume applications [20]. One of the minor disadvantages with heterogeneous integration methods such as die-to-wafer bonding is that individual components cannot be tested before they are integrated into more complex PICs, resulting in reduced yield [19]. In addition, wafer bonding also requires a very clean and smooth surface to be used [21].

#### 1.1.3 Micro-transfer printing technology

Micro-transfer printing ( $\mu$ TP) is an emerging technology for heterogeneous integration of optoelectronics and electronics. This technology at the microfabrication and semiconductor level was developed by the Rogers' group at the University of Illinois in 2004 [22, 23].

This technology has become a promising candidate for the assembly of thin and small devices precisely and cost-effectively, combining the advantages of flip-chip and die-to-wafer bonding. With this technique, thin film devices with micron sizes can be transferred in a massively parallel manner from a native growth substrate to a non-native target substrate with an accuracy of  $\pm 1 \ \mu m$  [24]. Similar to die-to-wafer bonding, this technology offers high accuracy integration, and like flip-chip assembly, it allows prefabrication and pretesting of devices before integrating them into a new target [6].

This technique primarily involves pick up ink from the donor substrate and printing it on the target substrate [25]. The pick-up and printing process can be done by adjusting the peeling

velocity of the stamp, because the adhesion strength of the device(s) to the stamp varies with the rate of peeling [23, 26]. The elastomeric stamp is typically made of polydimethylsiloxane (PDMS). Most stamps rely on a stable and rigid backplate (typically made of glass), a bulk elastomeric material forming a mesa on the backplate, and stamp posts extending from the bulk material away from the backplate. The schematic of printing process is shown in Figure 1.1.

### (a) Device preparation & undercut

### (b) Micro-Transfer printing

FIGURE 1.1: Process overview for transfer printing: (a) the preparation of the devices and the selective etching of the release layer while leaving the coupons suspended by tethers and securely anchored on the substrate, (b) schematic micro-transfer printing process for released LEDs.

To prepare the sample for transfer printing onto new targets, the fabricated devices have to be released from their native substrates. The releasing is enabled by incorporating a sacrificial layer in the epitaxial layer stack between the device layer and the substrate, which can be selectively etched.

To undercut, the devices are patterned on the source wafer. After that, they are protected by a passivation layer with local openings that allow access to the sacrificial layer, which is then underetched. After underetching the sacrificial layer, the suspended devices are anchored to substrate with tethers. Note that the undercut etching method is determined by the type of substrate. The purpose of this study is releasing devices from different types of substrates in a manner that is compatible with transfer printing and does not degrade the quality of the epitaxial layers, as well as to optimize the fabrication process to increase printing yield.

Once the devices have been released, a PDMS stamp with a post array (or a single post) whose size and patch matching the device array arranged on the source wafer is used to pick them up. During the pick-up step, a PDMS stamp mounted on transparent glass is aligned and brought into contact with the desired devices on the source wafer, and is then pulled back at a high velocity. The tethers of the anchoring system are broken at engineered locations by pulling rapidly, allowing the devices to be picked up and adhered to the stamp posts [27, 28].