| Title                       | Profiling border-traps by TCAD analysis of multifrequency CV-curves in Al203/InGaAs stacks                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Caruso, Enrico;Lin, Jun;Burke, K. F.;Cherkaoui, Karim;Esseni, David;Gity, Farzan;Monaghan, Scott;Palestri, Pierpaolo;Hurley, Paul K.;Selmi, Luca                                                                                                                                                                                                                                                                     |

| Publication date            | 2018-05-07                                                                                                                                                                                                                                                                                                                                                                                                           |

| Original Citation           | Caruso, E., Lin, J., Burke, K. F.; Cherkaoui, K., Esseni, D., Gity, F., Monaghan, S., Palestri, P., Hurley, P. K. and Selmi, L. (2018) 'Profiling border-traps by TCAD analysis of multifrequency CV-curves in Al203/InGaAs stacks', Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Granada, Spain, 19-21 March. doi:10.1109/ULIS.2018.8354757 |

| Type of publication         | Conference item                                                                                                                                                                                                                                                                                                                                                                                                      |

| Link to publisher's version | 10.1109/ULIS.2018.8354757                                                                                                                                                                                                                                                                                                                                                                                            |

| Rights                      | © 2018, IEEE. Personal use of this material is permitted.  Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.                    |

| Download date               | 2024-03-28 15:32:25                                                                                                                                                                                                                                                                                                                                                                                                  |

| Item downloaded from        | https://hdl.handle.net/10468/7161                                                                                                                                                                                                                                                                                                                                                                                    |

# Profiling Border-Traps by TCAD analysis of Multifrequency CV-curves in Al<sub>2</sub>O<sub>3</sub>/InGaAs stacks

E. Caruso\*, J. Lin\*, K. F. Burke\*, K. Cherkaoui\*, D. Esseni\*, F. Gity\*, S. Monaghan\*, P. Palestri\*, P. Hurley\*, L. Selmi\*

\*Tyndall National Institute University College Cork, Cork, Ireland † DPIA, University of Udine, Via delle Scienze 206, 33100, Udine, Italy ¥ DIEF, University of Modena and Reggio Emilia, Via P. Vivarelli 10/1, 41125, Modena, Italy

Abstract— This paper reports physics based TCAD simulations of multi-frequency C-V curves of In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSCAPs including the AC response of the border traps. The calculations reproduce the experimental inversion and accumulation capacitance versus frequency, and provide a means to profile the space and energy density of states of border traps. A sensitivity analysis of the results to border traps' distribution is carried out changing the trap volume and the oxide capacitance.

Keywords—III-V compounds, TCAD simulation, border traps, parameter extraction, C-V, trap volume

#### I. INTRODUCTION

Compared to the Si/SiO<sub>2</sub> material system, high-k dielectrics deposited on III-V semiconductors exhibit large interface and border trap (BT) values, which induce mobility degradation [1,2], Fermi-level-pinning [3,4] capacitance-voltage (C-V) hysteresis [5] and 1/f noise [6]. Multi-frequency C-V measurements are highly sensitive to such traps and can be used to extract trap concentration profiles in energy and space [7,8,9]. Analysis of border traps to date has been based on an approach which models the border traps as a distributed capacitor/resistor model [7,10,11]. In this work, we extend on these studies to model the border trap response using a band to trap tunneling process. This allows the density of border traps to be varied in space and energy as well as allowing the impact of trap volume to be studied. The physics based models required to perform the simulations are already implemented in commercial TCAD tools (e.g. Sentaurus [12]), which include Fermi-Dirac statistics, multi-valley non-parabolic band structure and quantum corrections via the modified local density approximation MLDA [13]. Elastic and inelastic band-totrap tunneling models can be used to model the dynamics of border traps [14,15].

In this paper, we show how, with a suitable calibration, the TCAD model reproduces the frequency dispersion of state-of-the-art  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOSCAPs.

Simulations rely on small-signal AC analysis [16]. The response of the device to 'small' sinusoidal signals superimposed upon an established DC bias is computed as a function of frequency by solving the Poisson, drift-diffusion and charge conservation equations. The carrier recombination rates that influence the device dynamic depend on i) Generation–recombination processes governing carriers transitions between conduction and valence band, that are modelled using the Shockley–

Read-Hall theory and ii) the capture/ emission process of carriers in and from remote traps.

# II. DEVICE AND MODEL CALIBRATION

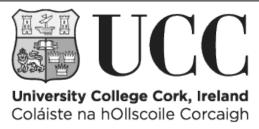

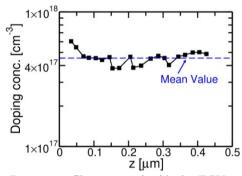

The n-type InGaAs MOSCAP fabrication starts with a  $n^+$  InP (100) substrate. A 2  $\mu m$  n-In $_{0.53}Ga_{0.47}As$  layer was grown by MOVPE using a nominal S doping concentration of  $4\cdot 10^{17}$  cm $^{-3}$ . The value measured by Electrochemical Capacitance-Voltage (ECV) [17] varies between 4 and  $6\cdot 10^{17}$  cm $^{-3}$  across the layer, as shown in Fig. 1. The Al $_2O_3$  dielectric (nominal thickness 8 nm) was grown by atomic layer deposition (ALD). TEM measurements indicate an actual thickness of 6  $\pm$  0.3 nm (Fig. 2). Ni(70 nm)/Au(90 nm) was used as the metal gate and was formed by electron beam evaporation and a lift-off process. MOS capacitors were treated by postmetal FGA (0.05H $_2$ ,0.95N $_2$ ) using the optimum temperature of 450 °C.

Fig. 1. Dopant profile measured with the ECV method. The mean value is reported as a guide to the eye.

Fig. 2. Cross-sectional TEM image shows an  $Al_2O_3$  gate oxide thickness of  $6 \pm 0.3$  nm.

Capacitance vs voltage characteristics have been measured between 1 kHz and 1 MHz using an E4980 LCR meter. The device area is large enough so that edge effects can be neglected.

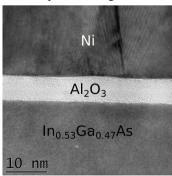

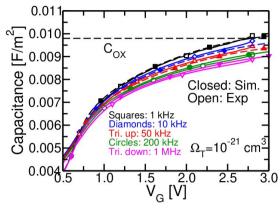

To simplify the analysis some parameters need to be set before running simulations with BTs. In particular, the value of  $\varepsilon_{ox}$  has been extracted by TCAD setting  $N_D\!\!=\!\!4\cdot 10^{17}~\text{cm}^{\text{-}3}$  and varying  $\epsilon_{ox}$  and  $T_{ox}.$  Under the assumption that traps do not affect the minimum capacitance in inversion (Cmin) at high-frequency, we found a set of parameters ( $T_{ox}$ =6.3 nm and  $\varepsilon_{ox}$ =7) that matches the experimental  $C_{min}$ , see Fig. 3. To determine the metal work function (WF), we identified the V<sub>G</sub> (~ 0.65 V) where the capacitance dispersion with frequency is minimum, i.e. the point where the amount of traps is the lowest one, so that the experimental capacitance at 1MHz should be very close to the simulations w/o BTs. This gives WF=5.2 eV, close to the metal work function of Nickel (5.04-5.35 eV [18]), meaning that in this sample the fixed charge inside the dielectric is quite low.

Fig. 3. Simulated (w/o BTs)  $C_{min}$  values (at 1 MHz and  $V_G$ =-3 V) using  $N_D$ =4·10<sup>17</sup> cm<sup>-3</sup> and changing  $T_{ox}$  and  $\epsilon_{ox}$ .  $T_{ox}$  is varied inside the confidence interval established by TEM (6  $\pm$  0.3 nm, Fig. 2). The experimental value of  $C_{min}$  is reported with the dashed line.

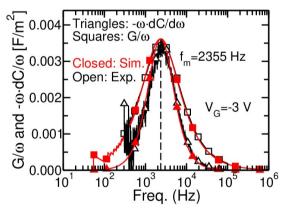

Fig. 4. Experimental (open symbols) and simulated (closed symbols, w/o BTs) curves of  $G/\omega$  and  $-\omega \cdot dC/d\omega$  plotted as a function of frequency ( $\omega$  is the angular frequency). The transition frequency  $f_m$  is reproduced using a minority carrier generation life time of  $\sim 92$  ps.

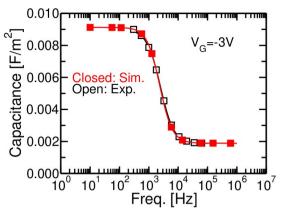

Minority carrier lifetime was calibrated to match the frequency position of the peaks in the  $G/\omega$  and  $-\omega \cdot dC/d\omega$  curves [19] in **Fig. 4**. This calibration also captures the

experimental inversion capacitance vs frequency (**Fig. 5**), proving that the sample is genuinely inverted.

Fig. 5. Experimental (open symbols) and simulated (closed symbols, w/o BTs) inversion capacitance (extracted at  $V_G$ =-3 V) as a function of frequency.

### III. RESULTS

Reproducing the frequency dispersion in accumulation requires determining the distribution of the BT ( $D_{BT}$ ). To simplify the problem, some assumptions are made: 1) the energy distribution has a Gaussian shape, also reported in [1,2,6]; 2) the spatial distribution is also Gaussian; 3) the tunneling mechanism of capture and emission is elastic. Using approximation 1) and 2) the BT distribution ( $D_{BT}$ ) as function of energy (E) and space (z) is given by:

$$D_{BT}(E, z) = N_{BT} \exp\left(-\frac{(E - \mu_E)^2}{2\sigma_E}\right) \cdot \exp\left(-\frac{(z - \mu_s)^2}{2\sigma_s}\right)$$

where  $N_{BT}$  is the peak value of the  $D_{BT}$ ,  $\mu_E$  and  $\mu_S$  are respectively the energy and space position of the peak and  $\sigma_E$  and  $\sigma_S$  are respectively the standard deviation of the energy and space Gaussian. The energy reference is the InGaAs conduction band, z is the distance of the BT from the high-k/III-V interface.

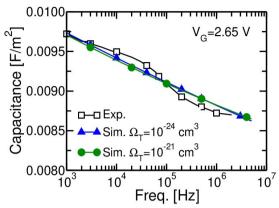

From the theory of interface traps we know that a typical range for the capture cross section  $(\sigma)$  is within  $10^{-16}$  to  $10^{-14}$  cm² [20,21]. This corresponds to a capture radius between 0.06 and 0.56 nm. Using these radiuses, we find a corresponding spherical trap volumes  $(\Omega_T)$  of  $0.75\cdot 10^{-24}$  and  $0.86\cdot 10^{-21}$  cm³. For this reason, we consider two values of  $\Omega_T$ :  $1\cdot 10^{-24}$  and  $1\cdot 10^{-21}$  cm³, close to the numbers above, and we check how they affect the shape of the BT distribution necessary to reproduce the experimental C-V curves.

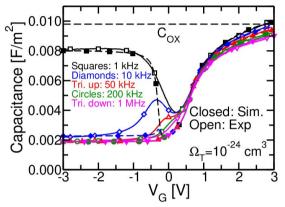

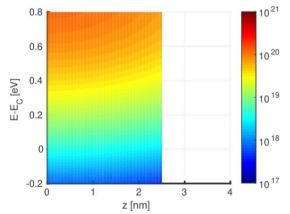

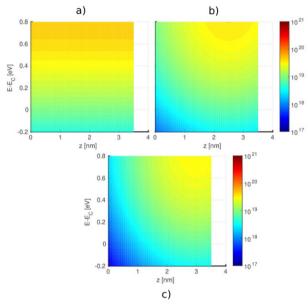

Considering  $\Omega_T$ =1·10<sup>-24</sup> cm<sup>3</sup>, a good agreement between experiments and simulations was achieved in accumulation and inversion regions, see **Fig. 6**. The BT distribution used has a peak value of  $1.34\cdot10^{20}$  cm<sup>-3</sup> eV<sup>-1</sup> and its energy and space dependences are reported in **Fig. 7**. Similar volume density of border traps have been found with alternatives techniques [1, 7, 8, 11].

Here we notice that AC simulations including interface traps are not reliable when one employs the MLDA model, because the electrons are set back from the high-

k/III-V interface so that the concentration at the interface vanishes. Because the calculation of emission rate from interface traps is local and relies on the carrier concentration at the interface [12], the emission rates become unphysically small. For this reason, in this work, we do not include interface traps and thus the capacitance in the depletion region cannot be reproduced correctly. In the subsequent figures we limit the comparison to the accumulation region, where border traps dominate.

Fig. 6. CV characteristics measured (open symbols) and simulated (closed symbols) including border traps at 300 K with a trap volume of  $1 \cdot 10^{-24}$  cm<sup>3</sup>. Negligible leakage current is observed during the measurements.

Fig. 7. Border traps distribution in energy and space assuming  $\Omega_T$ =1·10<sup>-24</sup> cm<sup>3</sup>. The BT parameters are:  $N_{BT}$ =1.34·10<sup>20</sup> cm<sup>-3</sup> eV<sup>-1</sup>,  $\sigma_E$ =0.42 eV,  $\mu_E$ =0.93 eV,  $\sigma_S$ =2.3 nm and  $\mu_s$ =0 nm.

We then study how the border traps distribution is affected by the trap volume. Considering  $\Omega_T = 1 \cdot 10^{-21}$  cm<sup>3</sup>, we can still reproduce the experimental data in accumulation, see **Fig. 8**, but using the BT distribution reported in **Fig. 9a.** It is interesting to note that increasing the trap volume, and therefore reducing the response time of the traps, the distribution that allows us to fit the experimental data penetrates deeper in space in the dielectric. In fact, it has: i) a lower peak value, ii) a uniform spatial distribution and iii) a wider trap region (the space region where the traps are defined changes from 2.5 to 3.5 nm). From this analysis, we see that  $\Omega_T$  is

a critical parameter for the extraction of the border trap distribution, in fact the same trend of accumulation capacitance as a function of frequency can be found (see Fig. 10) using different  $\Omega_T$  and different  $D_{BT}$ .

Fig. 8. Same of Fig. 6, but for  $V_G > 0.5 \text{ V}$  and assuming a trap volume of  $1 \cdot 10^{-21} \text{ cm}^3$ .

Fig. 9. Same of Fig. 7, but considering  $\Omega_T=1\cdot 10^{-21}$  cm³ and Tox= 6.3 (a), 6.0 (b) and 5.7 (c) nm. Changing Tox, DBT must be varied to reproduce the experimental C-V. The BT parameters are: a)  $N_{BT}=5\cdot 10^{19}$  cm⁻³ eV⁻¹,  $\sigma_E=0.5$  eV,  $\mu_E=0.93$  eV, with a constant distribution in space; b)  $N_{BT}=3.8\cdot 10^{19}$  cm⁻³ eV⁻¹,  $\sigma_E=0.5$  eV,  $\mu_E=0.93$  eV,  $\sigma_S=1.5$  nm and  $\mu_S=2.5$  nm; c)  $N_{BT}=3.2\cdot 10^{19}$  cm⁻³ eV⁻¹,  $\sigma_E=0.5$  eV,  $\mu_E=0.88$  eV,  $\sigma_S=1.3$  nm and  $\mu_S=3.0$  nm.

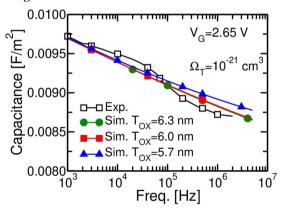

In presence of BTs, it is very difficult to determine the exact value of  $C_{\rm OX}$  directly from the experimental C-V. On the other hand, the dielectric thickness and the value of the oxide dielectric constant are often unknown. Slight adjustments to  $C_{\rm OX}$  entail different BT profiles to match the experimental data in accumulation.

To elaborate on this point, we modify the value of  $C_{OX}$  by changing  $T_{OX}$  within the range suggested by the TEM measurements (6  $\pm$  0.3 nm in **Fig.2**), and repeat the

extraction of the BT distribution. We set  $\Omega_T$ =1·10<sup>-21</sup> cm<sup>3</sup> and consider two additional values for Tox: 6.0 and 5.7 nm, in accordance with Fig. 2. The case with  $T_{OX} = 6.0$ nm reproduces the experiments very well (not shown) using the spatial distribution reported in Fig. 9.b.

Fig. 10. Experimental (open symbols) and simulated (closed symbols) accumulation capacitance (at V<sub>G</sub>=-2.65 V) vs frequency for different  $\Omega_T$  values.

It is worth noting that by reducing T<sub>OX</sub>, C<sub>OX</sub> increases and thus the simulated capacitance w/o BTs approaches the experimental capacitance at 1 MHz. Therefore, at high frequencies the contribution of BTs to the total capacitance is modest. To fit the experiments, it is thus necessary to reduce the amount of traps near the interface (the fastest ones) by moving the Gaussian peak inside the oxide of 2.5 nm. In the case with  $T_{OX} = 5.7$  nm, it is only possible to reproduce the accumulation region for V<sub>G</sub> < 2.0 V (not shown): since it is necessary to further reduce the D<sub>BT</sub> peak, see Fig. 9c, the Fermi level penetrates well inside the conduction band of the InGaAs, thus starting to occupy the L-valleys at Vg> 2 V. The L-valleys have larger DoS than the  $\Gamma$  valley, so that the simulated capacitance increases, overestimating the experiments, see Fig. 11.

Fig. 11. As Fig. 10, but for different value of Tox: 6.3 (circles), 6.0 (filled squares) and 5.7 (triangles) nm.

Although the origin of the border traps is still debated, it is believed these defects are located near the interface [22], where chemical analysis indicates an interfacial transition region of 1 to 2 nm which contains elements from both the InGaAs substrate and the oxide [23]. For this reason, although it is possible to get a good agreement between simulations and experiments using different values of Tox, a fitting that leads to lower density of border traps close to the interface than deep into the oxide looks suspicious.

## IV. CONCLUSIONS

In this paper, we used extensive physics based TCAD simulations to analyze the frequency dispersion of C-V curves for advanced InGaAs/Al<sub>2</sub>O<sub>3</sub> MOSCAPs and extract the minority carriers' lifetime and the border trap distribution. By making an analogy between the capture cross section of interface states and the capture volume of border traps we have identified a possible range of trap volume between  $1 \cdot 10^{-24}$  and  $1 \cdot 10^{-21}$  cm<sup>3</sup>.

We show that a proper estimate of COX is needed for a reliable estimation of D<sub>BT</sub>: if C<sub>OX</sub> is underestimated (e.g. the 5.7 nm case in this paper), simulations deviate from the experimental C-V. Using  $T_{OX} = 6.0$  nm instead of 6.3 nm, the number of trap states, obtained by integrating the D<sub>BT</sub> in energy and space is reduced by 43%.

Since different sets of geometrical and trap parameters still provide similarly good fits to the measured capacitance, a more robust and effective approach for determining DBT, might be reproduce both the experimental capacitance and conductance using a single set of border traps parameters.

#### **ACKNOWLEDGMENTS**

The research leading to these results has received funding from the European Commission FP7/2007-2013 under Grant Agreement III-V-MOS Project No. 619326 via the IUNET consortium and the H20202 INSIGHT project No 688784.

#### REFERENCES

- [1] S. Sioncke et al., VLSI, pp. T38-T39, 2017

- [2] P. Pavan at al., Phys. Status Solidi A, 214(3), 2017

- [3] N. Taoka, et al., IEDM, pp. 27-2, 2011

- [4] P. Osgnach et al., Solid State Electronics, vol. 108, pp. 90-96, 2015 [5] J. Lin et al., Journal of App. Phys, 114(14), p. 144105, 2013

- [6] T. A. Karatsori et al., ULIS, pp. 105-108, 2017

- G. Brammertz et al., IEEE Trans. Elect Dev, 58(11), p. 3890, 2011

- [8] G. Sereni et al., IEEE Trans. Elect Dev, 62(3), p. 705-, 2015

- [9] R. M. Sarkar et al., IEEE Trans. Elect Devi, 64(9), p. 3794-, 2017

- [10] Y. Yuan et al., IEEE Electron Device Lett., 32(4),p. 485, 2011

- [11] S. Johansson et al., IEEE Trans. Elect. Dev., 60(2), p. 776, 2013 [12] Synposys Inc., Sentaurus Device<sup>TM</sup>, v. L-2016.03-SP2, , 2016

- [13] G. Paasch et al., Physica Status Solidi (b), 113(1), p. 165, 1982

- [14] F. Jiménez-Molinos et al., J. of App. Phys, 91(8), p. 5116, 2002

- [15] A. Palma et al., Phys. Rev. B, 56, p. 9565, 1997

- [16] S. E. Laux, IEEE Trans. Elect. Dev, 32(10), p. 2028, 1985

- [17] P. Blood, Semicond. Sci. Technol., 1(1), p. 7, 1986

- [18] B.G. Baker et al., Surface Science, 24(2), p. 572, 1971

- [19] S. Monaghan et al., IEEE Trans. Elec. Dev. 61(12), p. 4176, 2014

- [20] H. Deuling et al., Solid-State Electronics, 15(5), p. 559, 1972

- [21] H. Knudsen et al., Phys. Rev. A, 23(2), 597, 1981

- [22] I. Krylov et al. Journal of App. Phys, 117(17), p. 174501, 2015

- [23] R. D. Long et al., Journal of App. Phys, 106(8), p. 084508, 2009