|                             | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title                       | Dual-gate MoS2 transistors with sub-10 nm top-gate high-k dielectrics                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Authors                     | Bolshakov, Pavel;Khosravi, Ava;Zhao, Peng;Hurley, Paul K.;Hinkle, Christopher L.;Wallace, Robert M.;Young, Chadwin D.                                                                                                                                                                                                                                                                                                                                                                                    |

| Publication date            | 2018-06-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Original Citation           | Bolshakov, P., Khosravi, A., Zhao, P., Hurley, P. K.; Hinkle, C. L., Wallace, R. M. and Young, C. D. (2018) 'Dual-gate MoS2 transistors with sub-10 nm top-gate high-k dielectrics', Applied Physics Letters, 112, 253502 (5pp). doi:10.1063/1.5027102                                                                                                                                                                                                                                                   |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Link to publisher's version | 10.1063/1.5027102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Rights                      | © 2018, Article authors. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in Bolshakov, P., Khosravi, A., Zhao, P., Hurley, P. K.; Hinkle, C. L., Wallace, R. M. and Young, C. D. (2018) 'Dual-gate MoS2 transistors with sub-10 nm top-gate high-k dielectrics', Applied Physics Letters, 112, 253502 (5pp). doi:10.1063/1.5027102, and may be found at https://doi.org/10.1063/1.5027102 |

| Download date               | 2025-07-31 12:45:22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Item downloaded from        | https://hdl.handle.net/10468/6407                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## Dual-gate MoS<sub>2</sub> transistors with sub-10 nm top-gate high-k dielectrics

Pavel Bolshakov, Ava Khosravi, Peng Zhao, Paul K. Hurley, Christopher L. Hinkle, Robert M. Wallace, and Chadwin D. Young

Citation: Appl. Phys. Lett. 112, 253502 (2018); doi: 10.1063/1.5027102

View online: https://doi.org/10.1063/1.5027102

View Table of Contents: http://aip.scitation.org/toc/apl/112/25

Published by the American Institute of Physics

## Articles you may be interested in

High quality gate dielectric/MoS<sub>2</sub> interfaces probed by the conductance method

Applied Physics Letters 112, 232101 (2018); 10.1063/1.5028404

Van der Waals epitaxy of two-dimensional single-layer h-BN on graphite by molecular beam epitaxy: Electronic properties and band structure

Applied Physics Letters 112, 253102 (2018); 10.1063/1.5029220

Gate-tunable quantum dot in a high quality single layer MoS<sub>2</sub> van der Waals heterostructure

Applied Physics Letters 112, 123101 (2018); 10.1063/1.5021113

Local carrier distribution imaging on few-layer MoS<sub>2</sub> exfoliated on SiO<sub>2</sub> by scanning nonlinear dielectric microscopy

Applied Physics Letters 112, 243102 (2018); 10.1063/1.5032277

Integration of graphene oxide buffer layer/graphene floating gate for wide memory window in Pt/Ti/Al<sub>2</sub>O<sub>3</sub>/GO/graphene/SiO<sub>2</sub>/p-Si/Au non-volatile (FLASH) applications

Applied Physics Letters 112, 252102 (2018); 10.1063/1.5030020

Negative differential resistance in GaN homojunction tunnel diodes and low voltage loss tunnel contacts Applied Physics Letters **112**, 252103 (2018); 10.1063/1.5035293

## Dual-gate MoS<sub>2</sub> transistors with sub-10 nm top-gate high-k dielectrics

Pavel Bolshakov, <sup>1</sup> Ava Khosravi, <sup>1</sup> Peng Zhao, <sup>1</sup> Paul K. Hurley, <sup>2</sup> Christopher L. Hinkle, <sup>1</sup> Robert M. Wallace, 1 and Chadwin D. Young 1

<sup>1</sup>Department of Materials Science and Engineering, The University of Texas at Dallas, 800 West Campbell Road, Richardson, Texas 75080, USA

(Received 27 February 2018; accepted 30 May 2018; published online 19 June 2018)

High quality sub-10 nm high-k dielectrics are deposited on top of MoS<sub>2</sub> and evaluated using a dualgate field effect transistor configuration. Comparison between top-gate HfO2 and an Al2O3/HfO2 bilayer shows significant improvement in device performance due to the insertion of the thin Al<sub>2</sub>O<sub>3</sub> layer. The results show that the Al<sub>2</sub>O<sub>3</sub> buffer layer improves the interface quality by effectively reducing the net fixed positive oxide charge at the top-gate MoS<sub>2</sub>/high-k dielectric interface. Dualgate sweeping, where both the top-gate and the back-gate are swept simultaneously, provides significant insight into the role of these oxide charges and improves overall device performance. Dual-gate transistors encapsulated in an Al<sub>2</sub>O<sub>3</sub> dielectric demonstrate a near-ideal subthreshold swing of  $\sim$ 60 mV/dec and a high field effect mobility of 100 cm<sup>2</sup>/V·s. Published by AIP Publishing. https://doi.org/10.1063/1.5027102

Transition metal dichalcogenides (TMDs) are being intensely investigated due to their unique 2D properties that can be utilized in low-power, high-mobility circuitry. 1-5 For semiconducting TMDs like MoS<sub>2</sub>, their integration with ultrathin high-k dielectrics such as HfO2 and Al2O3 has proven quite challenging due to the relatively inert TMD surface.<sup>6,7</sup> To achieve performance close to the current level of CMOS technology, deposition of uniform, pin-hole free sub-10 nm high-k dielectric films is necessary. Recent developments in surface functionalization have been used to demonstrate deposition of ultrathin high-k dielectric films on MoS<sub>2</sub> <sup>8–11</sup> The deposition of high-k dielectrics on the top surface of back-gate (BG) MoS<sub>2</sub> FETs has been shown to significantly affect the ON and OFF current as well as create a V<sub>T</sub> shift. 12,13 There have also been multiple studies demonstrating a significant influence of the back-gate bias 14-17 as well as the choice of dielectrics. <sup>18,19</sup> The use of a biasing method known as dual-gate (DG) sweeping<sup>20,21</sup> helps to further elucidate the effects of oxide charges on device performance and achieve overall better control of the MoS2 channel. In this study, we compare the effects of HfO<sub>2</sub> deposition to Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bilayer deposition on MoS<sub>2</sub> in terms of device performance and show how oxide charges play a role. Using the dual-gate sweeping methodology, this work shows significant improvements in threshold voltage, subthreshold swing (SS), mobility, and hysteresis, for the Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/ HfO<sub>2</sub> gate stack compared to the Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> gate stack due to the reduction of net fixed positive oxide charge at the top-gate MoS<sub>2</sub>/high-k dielectric interface. This results in a near-ideal SS of  $\sim 60 \,\mathrm{mV/dec}$ , high field effect mobility  $(\mu_{\rm FE})$  values  $> 100 \, {\rm cm}^2/{\rm V} \cdot {\rm s}$ , and an  ${\rm I}_{\rm ON}/{\rm I}_{\rm OFF}$  of  $\sim 10^6$ .

Atomic layer deposition (ALD) of  $Al_2O_3$  ( $\sim 27 \text{ nm}$ ) at 250 °C onto a p<sup>++</sup> Si wafer was used for back gate isolation. On the opposite side of the Si wafer, Al was deposited for a backside wafer contact followed by a 400 °C forming gas anneal to reduce oxide charge. The ALD Al<sub>2</sub>O<sub>3</sub> then serves as the "substrate" and back gate oxide for exfoliated multi-layer

MoS<sub>2</sub> flakes. 18 Using photolithography, source/drain contacts are defined on the transferred flakes (~4-8 nm thickness) followed by e-beam evaporation of Ti/Au contacts with a lift-off process. The flakes also undergo a 5 s O2 plasma exposure ("de-scum") at 50 W to remove photoresist residue prior to contact metal deposition on natural MoS2. Electrical back-gate measurements are then performed followed by a 300 °C UHV anneal for 2h to facilitate desorption of residual contaminants.<sup>22</sup> Then, a 15 min *in-situ*, room-temperature UV-ozone surface treatment with subsequent ALD of either HfO<sub>2</sub>(9 nm) or Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>(3 nm/6 nm) was deposited at 200 °C to produce  $p^{++}Si/Al_2O_3/MoS_2/HfO_2$  or  $p^{++}Si/Al_2O_3/MoS_2/Al_2O_3/HfO_2$ structures 10,11 (Fig. S1). After high-k dielectric deposition, back-gate electrical measurements are performed, followed by photolithography of a Pd/Au top-gate for further sequential device measurements. The structures are compared sequentially using a back-gate (BG) sweep mode, a top-gate (TG) sweep mode, and a dual-gate (DG) sweep mode for comparison of the device response. It is noted that no other post-metal gate deposition anneals were conducted in this study.

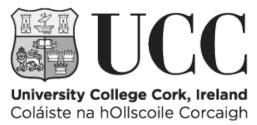

Prior to any top-gate high-k dielectric deposition, backgate MoS<sub>2</sub> FETs (p<sup>++</sup>Si/Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>) were electrically characterized in order to compare the I-V response before and after the top-gate ALD process. The transfer curves shown in Fig. 1(a) (left) compare the electrical response before and after HfO<sub>2</sub> deposition, where a significant increase in OFF current, an increase in ON current, and a negative threshold voltage shift  $(-\Delta V_T)$  are observed. However, as seen in Fig. 1(a) (right), the deposition of the high-k dielectric bilayer (Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>), where the Al<sub>2</sub>O<sub>3</sub> is deposited on MoS<sub>2</sub> before the HfO<sub>2</sub> cap, results in a slight increase in both OFF and ON currents as well as a positive threshold voltage shift  $(+\Delta V_T)$ . Previous studies that investigated the electrical response after high-k dielectric deposition demonstrated that both HfO<sub>2</sub> and  $Al_2O_3$  deposition result in a higher OFF current and a  $-\Delta V_T$ , but there was no inclusion of a UHV anneal to remove surface contaminants nor was there a functionalization treatment

<sup>&</sup>lt;sup>2</sup>Tyndall National Institute, University College Cork, Lee Maltings Complex, Dyke Parade, Mardyke, Cork,

FIG. 1. (a) The transfer characteristics of back gated MoS<sub>2</sub> MOSFETS  $(W = 15-20 \mu m \text{ and } L = 4 \mu m)$  before and after the HfO2 (left) and the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bilayer (right) deposition and (b) average ON and OFF currents as well average I<sub>ON</sub>/I<sub>OFF</sub> ratios for multiple BG MoS2 FETs pre- and posthigh-k dielectric deposition. The high OFF current after HfO2 deposition indicates the introduction of fixed positive oxide charge resulting in an actively conducting top channel. (c) The threshold voltage shift  $(\Delta V_T)$  after high-k dielectric deposition differs for each gate stack with a negative  $\Delta V_T$ for  $HfO_2$  and positive  $\Delta V_T$  for the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bilayer with the (d) TEM images illustrating Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> stack structures.

like UV-ozone to ensure a pin-hole free film.  $^{12,13}$  A recent study by Liu *et al.* demonstrated the same trends after  $Al_2O_3$  deposition as this work with the inclusion of their own functionalization treatment consisting of  $O_2$  plasma exposure prior to ALD. Here, they demonstrated a slightly higher OFF current and a  $+\Delta V_T$ , consistent with the results shown in Fig. 1(a). This suggests that the inclusion of a functionalization treatment is key for achieving enhanced device performance.

After looking at the electrical characteristics of multiple back-gate MoS<sub>2</sub> FETs, several trends emerge. The OFF and ON currents before and after high-k dielectric deposition in Fig. 1(b) demonstrate a trend of a significantly higher OFF current after  $HfO_2$  deposition, and a  $-\Delta V_T$  is observed as shown in Fig. 1(c). This suggests that there is significant fixed positive oxide charge at the MoS<sub>2</sub>/HfO<sub>2</sub> interface, which also likely accounts for the increase in ON current since the positive oxide charge may be inducing a higher electron concentration<sup>23</sup> in the channel. It is also prudent not to rule out the role of the UHV anneal and the ALD process on the contact interface, which may result in a reduction of contact resistance,<sup>24</sup> also potentially contributing to the increase in ON current. A potential mechanism behind the  $-\Delta V_T$  may be due to oxygen vacancies in the HfO2. Valsaraj et al.25 presented theoretical and experimental studies which indicate that a  $-\Delta V_T$  after deposition of HfO<sub>2</sub> on MoS<sub>2</sub> is due to oxygen vacancies in the HfO<sub>2</sub> film. Other works have shown the presence of positively charged oxygen vacancies from ALD HfO<sub>2.</sub><sup>26-28</sup> This positive charge results in a corresponding electron density on MoS2, which can be considered as an effective *n*-type doping of the MoS<sub>2</sub> channel.<sup>25</sup> The trends observed in Figs. 1(b) and 1(c) for the bilayer deposition (with Al<sub>2</sub>O<sub>3</sub> directly on the MoS<sub>2</sub> top interface instead of HfO<sub>2</sub>) show slight increases in OFF and ON currents as well as a  $+\Delta V_T$  suggesting a significant reduction of fixed positive oxide charge at the top-gate MoS<sub>2</sub>/high-k dielectric interface or potentially the introduction of negative oxide charge due to the insertion of the ultrathin Al<sub>2</sub>O<sub>3</sub> layer between MoS<sub>2</sub> and HfO<sub>2</sub>. The latter has been demonstrated for Al<sub>2</sub>O<sub>3</sub> deposited by ALD on InGaAs<sup>29</sup> and GaSb<sup>30</sup> surfaces, where negative charge at the Al<sub>2</sub>O<sub>3</sub>/III-V interface was found. Impedance spectroscopy is needed to definitively determine the source of the improvement in the I-V response after the introduction of Al<sub>2</sub>O<sub>3</sub> between MoS<sub>2</sub> and HfO<sub>2</sub>.<sup>31</sup> Overall, fixed positive oxide charge at the MoS<sub>2</sub>/HfO<sub>2</sub> interface after high-k dielectric deposition on MoS<sub>2</sub> appears to result in poor device characteristics, and the insertion of Al<sub>2</sub>O<sub>3</sub> on MoS<sub>2</sub> prior to HfO<sub>2</sub> allows for significantly improved device performance for the p<sup>++</sup>Si/Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> stack compared to the p<sup>++</sup>Si/Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> stack [stacks shown in Fig. 1(d)].

After the high-k dielectric deposition and BG-only device measurements, the top-gate metal electrode was deposited and patterned and the DG FETs were then electrically characterized using a BG sweep, a TG sweep, and our DG sweep approach. The motivation behind the development of the DG sweep stems from the extremely high OFF current following HfO<sub>2</sub> deposition, which, as reported previously,<sup>32</sup> often requires a high temperature anneal in order to remove the fixed positive oxide charge and achieve adequate channel depletion. Such annealing can have certain unwanted sideeffects such as formation of polycrystalline HfO2 or a reduction in ON current.<sup>33,34</sup> Additionally, the common use of a TG bias sweep with a fixed-BG bias—often employed with a thick SiO<sub>2</sub> back-gate dielectric in the literature—typically results in V<sub>T</sub> shifts and major changes in the OFF/ON currents. 14-16 By using multiple bias configurations, we are able to deconvolute the impact of each interface and dielectric.

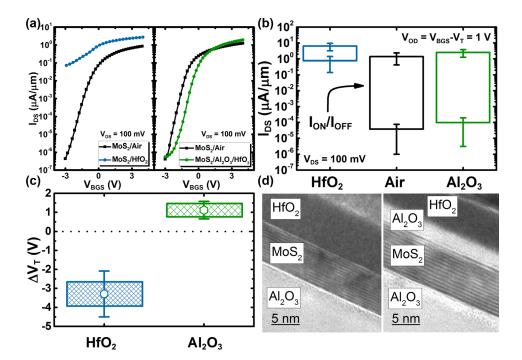

Starting with the  $Al_2O_3/MoS_2/HfO_2$  stack, a comparison can be made between a TG sweep with a fixed-BG bias and a DG sweep on the same device. For the TG sweep with a fixed-BG bias in Fig. 2(a) (left), there are changes in the OFF and ON currents as well as  $V_T$  shifts as the BG bias is stepped from  $-5\,V$  to  $5\,V$  for each TG sweep, similar to previous reports.  $^{15,16}$  While choosing a TG sweep at a  $-5\,V$  BG

FIG. 2. (a) Comparison between the commonly used TG sweep with a fixed-BG bias (left) and a DG sweep (right) demonstrating the lowest OFF current, the highest ON current, and a better overall subthreshold swing than any TG sweep with a BG bias. (b) The extracted maximum transconductance (gm) as a function of fixed-BG bias indicates a reduction in gm due to a fixed-BG bias which can lead to an underestimation of mobility. (c) The transfer curves before and after HfO2 deposition (left) along with the BG, TG, and DG sweeps (right) indicate the (d) formation of a secondary channel due to the introduction of fixed positive oxide charge with only a DG sweep being able to deplete both channels.

bias provides a low OFF current, there is a sacrifice of an order of magnitude in the ON current observed. The inverse is true for a BG bias of +5 V where there is not only a high OFF current but also a high ON current. In order to achieve the highest ON current and the lowest OFF current, a DG sweep, which sweeps the BG and TG simultaneously (Fig. S2) using the same voltage range and the same voltage step, was investigated.

As shown in Fig. 2(a) (right), the DG sweep provides the highest ON current and the lowest OFF current and a better overall SS than any of the TG sweeps with a fixed-BG bias [Fig. 2(a) (left)]. Furthermore, mobility is often extracted using the transconductance (g<sub>m</sub>) of a transfer curve that consists of a TG sweep with a fixed-BG bias. The behavior of g<sub>m</sub> as a function of the fixed-BG bias in Fig. 2(b), along with the position of the peak transconductance often used to extract the peak mobility, demonstrates a reduction in g<sub>m</sub> with any fixed-BG bias. This suggests that with a fixed-BG bias, there is an underestimation of the mobility where a TG sweep without any BG bias achieves the highest peak g<sub>m</sub> value. Similar to a FinFET, the DG sweep configuration allows for better overall control of the MoS<sub>2</sub> channel and does so without degrading g<sub>m</sub> nor the OFF and ON currents.

Using this electrical characterization methodology, the role of oxide charge in DG MoS<sub>2</sub> FET performance can be further elucidated. As shown in Fig. 1(a) (left), the deposition of HfO<sub>2</sub> on MoS<sub>2</sub> results in an extremely high OFF current which may completely be due to the introduction of fixed positive oxide charge. In Fig. 2(c), a comparison of the transfer curve before and after HfO<sub>2</sub> deposition and the BG, TG, and DG sweeping modes of the Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> stack are shown. In Fig. 2(c) (right), neither a BG sweep nor a TG sweep can deplete the MoS<sub>2</sub> channel to its original OFF state prior to any top dielectric deposition. This suggests that the introduction of fixed positive oxide charge induces the formation of a secondary conduction channel at the top MoS<sub>2</sub>/HfO<sub>2</sub> interface as illustrated schematically in Fig. 2(d) where

neither a BG nor TG sweep can turn off the device. With a DG sweep in Fig. 2(c) (right), the transfer curve shows full gate modulation with the OFF current almost the same value as prior to HfO<sub>2</sub> deposition as shown in Fig. 2(c) (left). The DG sweep is thus able to deplete "both" channels and turn off the FET, suggesting that the high OFF current after HfO<sub>2</sub> deposition is a phenomenon caused primarily by fixed positive oxide charge at the MoS<sub>2</sub>/HfO<sub>2</sub> interface. Although a DG sweep can neutralize the effects of the fixed positive oxide charge, the transfer curve, with a  $V_{\rm T}$  of -3.7 V as well as an SS of  $\sim$ 200 mV/dec, still lacks the optimal performance that is theoretically possible.

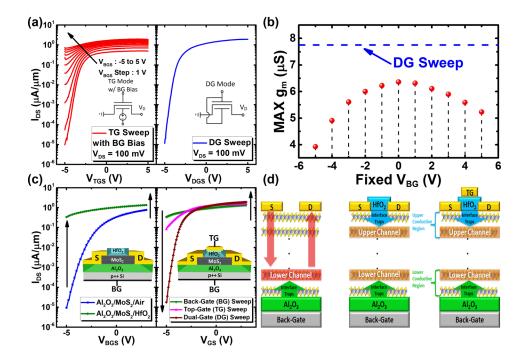

Introducing an ultrathin Al<sub>2</sub>O<sub>3</sub> layer between MoS<sub>2</sub> and HfO2 may be able to buffer some of the effects of the fixed positive oxide charge introduced by the HfO<sub>2</sub> as there appears to be minimal changes in OFF/ON currents and SS after the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bilayer deposition (see Fig. 1). Comparing the different sweeping modes for the Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> stack in Fig. 3(a) shows significant improvement going from BG sweep to TG sweep and then finally DG sweep where the transfer curve "straightens out," the OFF current decreases, the ON current increases, and the SS becomes steeper. As with the Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> stack, the DG sweep shows the best device characteristics due to better electrostatic control over the MoS<sub>2</sub> channel. As shown in Fig. 3(c), the DG sweep for the Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> gate stack demonstrates a near-ideal SS of  $\sim$ 60 mV/dec, an  $I_{ON}/I_{OFF}$  of  $\sim$ 10<sup>6</sup>, and a  $\mu_{FE}$ of 100 cm<sup>2</sup>/V·s. Furthermore, the output characteristics in Fig. 3(b) show linearity and have a Y-Function-extracted<sup>37</sup> contact resistance (R<sub>C</sub>) of  $\sim 1 \text{ k}\Omega \cdot \mu\text{m}$ , suggesting that reduction in R<sub>C</sub> is necessary to prevent underestimation of the device mobility.  $^{38,39}$  The value of  $R_C$  is sufficiently low that it does not have an impact on the evaluated SS (see Fig. S5). Comparing the DG sweeps of the two different gates stacks in Fig. 3(d), the insertion of Al<sub>2</sub>O<sub>3</sub> prior to HfO<sub>2</sub> deposition improves device performance on all fronts, specifically a more positive V<sub>T</sub>, steeper SS, and smaller hysteresis. Moreover, there is a

FIG. 3. (a) Transfer curves of the p<sup>++</sup>Si/Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> gate stack in BG, TG, and DG sweep modes with the inset showing the DG MoS<sub>2</sub> FET cross-section. (b) The output characteristics with linear I-V and (c) the DG sweep demonstrating a nearideal SS of  $\sim 60 \,\text{mV/dec}$ , an  $I_{ON}/I_{OFF}$ of  $\sim 10^6$ , and a  $\mu_{\rm FE}$  of  $100 \, {\rm cm}^2/{\rm V} \cdot {\rm s.}$  (d) Comparison between the p<sup>++</sup>Si/Al<sub>2</sub>O<sub>3</sub>/ MoS<sub>2</sub>/HfO<sub>2</sub> gate stack and the p<sup>+</sup> Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> shows a more positive V<sub>T</sub>, smaller hysteresis, and better overall device performance due to the insertion of the thin Al<sub>2</sub>O<sub>3</sub> layer between MoS<sub>2</sub> and HfO<sub>2</sub>.

significant improvement in mobility<sup>20</sup> (Fig. S3), which, according to Ma and Jena, has to do with the surrounding dielectric environment, among other factors. 40 Previous studies have shown the influence of the back-gate dielectric on top-gate performance, where changing the gate stacks from HfO<sub>2</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> to SiO<sub>2</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> to Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> improves the top-gate device performance, which is consistent with Ma et al. predictions. 18,19 The same consistency is evident in this study, where there is significant improvement in mobility going from Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/HfO<sub>2</sub> to Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub>/ Al<sub>2</sub>O<sub>3</sub>. Further improvements in device performance are dependent on impurity control and significant reductions in R<sub>C</sub>. The encapsulation of MoS<sub>2</sub> by high-k dielectrics to control the semiconductor/dielectric interface is also an aspect that requires further study. It has been shown, for example, that Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> have different ability to inhibit uncontrolled surface oxidation for III-V semiconductors,<sup>22</sup> and the impact of such effects is anticipated to also play a role for such TMD interfaces.

Comparison between top-gate HfO2 and Al2O3/HfO2 bilayer deposition in terms of DG MoS<sub>2</sub> FET performance demonstrates significant improvements due to the insertion of the Al<sub>2</sub>O<sub>3</sub> between MoS<sub>2</sub> and HfO<sub>2</sub>. DG MoS<sub>2</sub> FETs with a top- and back- Al2O3 gate dielectric demonstrate a nearideal SS of  $\sim 60 \,\mathrm{mV/dec}$ , an  $I_{\rm ON}/I_{\rm OFF}$  of  $10^6$ , and a  $\mu_{\rm FE}$  of 100 cm<sup>2</sup>/V·s. These improvements resulting from the bilayer gate oxide (Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>) can be attributed to the reduction of fixed positive oxide charge at the top-gate MoS<sub>2</sub>/high-k dielectric interface as well as the use of a DG sweeping mechanism. The DG sweeping, where both the BG and TG are swept simultaneously, helps further elucidate the role of oxide charge and, most significantly, provides better electrostatic control of the MoS<sub>2</sub> channel. This study provides significant insights into the influence of oxide charge on device performance as well the use of dual-gate electrical characterization methodology in order to integrate ultrathin high-k dielectrics with TMDs for future device applications.

See supplementary material for back-gate device structure schematic cross-sections, further details about dual-gate sweeping methodology, dual-gate mobility extraction, details about gate leakage after HfO<sub>2</sub> deposition, and the impact of contact resistance on evaluated subthreshold swing.

This work was supported in part by the US/Ireland R&D Partnership (UNITE) under the NSF Award No. ECCS-1407765, and the SFI Award No. 13/US/I2862.

<sup>1</sup>D. Jariwala, V. K. Sangwan, L. J. Lauhon, T. J. Marks, and M. C. Hersam, ACS Nano 8, 1102 (2014).

<sup>2</sup>S. J. McDonnell and R. M. Wallace, Thin Solid Films **616**, 482 (2016).

<sup>3</sup>A. Pospischil and T. Mueller, Appl. Sci. 6, 78 (2016).

<sup>4</sup>F. Schwierz, J. Pezoldt, and R. Granzner, Nanoscale 7, 8261–8283 (2015). <sup>5</sup>Q. H. Wang, K. Kalantar-Zadeh, A. Kis, J. N. Coleman, and M. S. Strano, Nat. Nanotechnol. 7, 699 (2012).

<sup>6</sup>Q. Qian, B. Li, M. Hua, Z. Zhang, F. Lan, Y. Xu, R. Yan, and K. J. Chen, Sci. Rep. 6, 27676 (2016).

<sup>7</sup>X. Wang, T. B. Zhang, W. Yang, H. Zhu, L. Chen, Q. Q. Sun, and D. W. Zhang, Appl. Phys. Lett. **110**, 053110 (2017).

<sup>8</sup>N. Liu, J. Baek, S. M. Kim, S. Hong, Y. K. Hong, Y. S. Kim, H.-S. Kim, S. Kim, and J. Park, ACS Appl. Mater. Interfaces 9, 42943 (2017).

<sup>9</sup>H. Zhang, G. Arutchelvan, J. Meersschaut, A. Gaur, T. Conard, H. Bender, D. Lin, I. Asselberghs, M. Heyns, I. Radu, W. Vandervorst, and A. Delabie, Chem. Mater. **29**, 6772 (2017).

<sup>10</sup>A. Azcatl, S. McDonnell, K. C. Santosh, X. Peng, H. Dong, X. Qin, R. Addou, G. I. Mordi, N. Lu, J. Kim, M. J. Kim, K. Cho, and R. M. Wallace, Appl. Phys. Lett. **104**, 111601 (2014).

<sup>11</sup> A. Azcati, S. Kc, X. Peng, N. Lu, S. S. McDonnell, X. Qin, F. De Dios, A. Rafik, J. Kim, M. J. Kim, K. Cho, and R. M. Wallace, 2D Mater. 2, 014004 (2015).

T. Li, B. Wan, G. Du, B. Zhang, and Z. Zeng, AIP Adv. 5, 057102 (2015).

J. Na, M.-K. Joo, M. Shin, J. Huh, J.-S. Kim, M. Piao, J.-E. Jin, H.-K. Jang, H. J. Choi, J. H. Shim, and G.-T. Kim, Nanoscale 6, 433 (2014).

<sup>14</sup>S. Bhattacharjee, K. L. Ganapathi, S. Mohan, and N. Bhat, ECS Trans. 80, 101 (2017).

<sup>15</sup>G. H. Lee, X. Cui, Y. D. Kim, G. Arefe, X. Zhang, C. H. Lee, F. Ye, K. Watanabe, T. Taniguchi, P. Kim, and J. Hone, ACS Nano 9, 7019 (2015).

<sup>16</sup>L. Cheng, J. Lee, H. Zhu, A. V. Ravichandran, Q. Wang, A. T. Lucero, M. J. Kim, R. M. Wallace, L. Colombo, and J. Kim, ACS Nano 11, 10243 (2017).

<sup>17</sup>E. Zhang, W. Wang, C. Zhang, Y. Jin, G. Zhu, Q. Sun, D. W. Zhang, P. Zhou, and F. Xiu, ACS Nano 9, 612 (2015).

- <sup>19</sup>P. Bolshakov, P. Zhao, A. Azcatl, P. K. Hurley, R. M. Wallace, and C. D. Young, Microelectron. Eng. 178, 190 (2017).

- <sup>20</sup>J. S. Kim, P. J. Jeon, J. Lee, K. Choi, H. S. Lee, Y. Cho, Y. T. Lee, D. K. Hwang, and S. Im, Nano Lett. **15**, 5778 (2015).

- <sup>21</sup>H. S. Ra, A. Y. Lee, D. H. Kwak, M. H. Jeong, and J. S. Lee, ACS Appl. Mater. Interfaces 10, 925 (2018).

- <sup>22</sup>S. McDonnell, H. Dong, J. M. Hawkins, B. Brennan, M. Milojevic, F. S. Aguirre-Tostado, D. M. Zhernokletov, C. L. Hinkle, J. Kim, and R. M. Wallace, Appl. Phys. Lett. **100**, 141606 (2012).

- <sup>23</sup>D. Kufer and G. Konstantatos, Nano Lett. **15**, 7307 (2015).

- <sup>24</sup>C. D. English, G. Shine, V. E. Dorgan, K. C. Saraswat, and E. Pop, Nano Lett. 16, 3824 (2016).

- <sup>25</sup>A. Valsaraj, J. Chang, A. Rai, L. F. Register, and S. K. Banerjee, 2D Mater. 2, 045009 (2015).

- $^{26}\mbox{P.}$  McIntyre, ECS Transactions (ECS, 2007), pp. 235–249.

- <sup>27</sup>S. Guha and V. Narayanan, Phys. Rev. Lett. **98**, 196101 (2007).

- <sup>28</sup>K. Tse, D. Liu, K. Xiong, and J. Robertson, Microelectron. Eng. 84, 2028 (2007).

- <sup>29</sup>P. K. Hurley, É. O'Connor, V. Djara, S. Monaghan, I. M. Povey, R. D. Long, B. Sheehan, J. Lin, P. C. McIntyre, B. Brennan, R. M. Wallace, M.

- E. Pemble, and K. Cherkaoui, IEEE Trans. Device Mater. Reliab. 13, 429 (2013).

- <sup>30</sup>A. Nainani, T. Irisawa, Z. Yuan, B. R. Bennett, J. B. Boos, Y. Nishi, and K. C. Saraswat, IEEE Trans. Electron Devices 58, 3407 (2011).

- <sup>31</sup>P. Zhao, A. Azcatl, Y. Y. Gomeniuk, P. Bolshakov, M. Schmidt, S. J. McDonnell, C. L. Hinkle, P. K. Hurley, R. M. Wallace, and C. D. Young, ACS Appl. Mater. Interfaces 9, 24348 (2017).

- <sup>32</sup>P. Zhao, A. Azcatl, P. Bolshakov, J. Moon, C. L. Hinkle, P. K. Hurley, R. M. Wallace, and C. D. Young, J. Vac. Sci. Technol., B 35, 01A118 (2017).

- <sup>33</sup>S. D. Namgung, S. Yang, K. Park, A.-J. Cho, H. Kim, and J.-Y. Kwon, Nanoscale Res. Lett. 10, 62 (2015).

- <sup>34</sup>M. Wen, J. Xu, L. Liu, P.-T. Lai, and W.-M. Tang, Appl. Phys. Express 9, 095202 (2016).

- <sup>35</sup>M. S. Fuhrer and J. Hone, Nat. Nanotechnol. **8**, 146 (2013).

- <sup>36</sup>B. Radisavljevic and A. Kis, Nat. Nanotechnol. **8**, 147 (2013).

- <sup>37</sup>D. Fleury, A. Cros, H. Brut, and G. Ghibaudot, in *IEEE International Conference on Microelectronic Test Structures* (IEEE, 2008), pp. 160–165.

- <sup>38</sup>H. Y. Chang, W. Zhu, and D. Akinwande, Appl. Phys. Lett. **104**, 113504 (2014).

- <sup>39</sup>S. McDonnell, R. Addou, C. Buie, R. M. Wallace, and C. L. Hinkle, ACS Nano 8, 2880 (2014).

- <sup>40</sup>N. Ma and D. Jena, Phys. Rev. X 4, 011043 (2014).