| Title                          | Wandering spur suppression in a 4.9-GHz fractional-N frequency synthesizer                                                                                                                                                                                                                                                              |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                        | Mai, Dawei;Donnelly, Yann;Kennedy, Michael Peter;Tulisi,<br>Stefano;Breslin, James;Griffin, Patrick;Connor, Michael;Brookes,<br>Stephen;Shelly, Brian;Keaveney, Mike                                                                                                                                                                    |

| Publication date               | 2022-04-15                                                                                                                                                                                                                                                                                                                              |

| Original Citation              | Mai, D., Donnelly, Y., Kennedy, M. P., Tulisi, S., Breslin, J.,<br>Griffin, P., Connor, M., Brookes, S., Shelly, B. and Keaveney, M.<br>(2022) 'Wandering spur suppression in a 4.9-GHz fractional-N<br>frequency synthesizer', IEEE Journal of Solid-State Circuits, 57(7),<br>pp.2011-2023. https://doi.org/10.1109/JSSC.2022.3163080 |

| Type of publication            | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                 |

| Link to publisher's<br>version | 10.1109/JSSC.2022.3163080                                                                                                                                                                                                                                                                                                               |

| Rights                         | © 2022 IEEE. For the purpose of open access, the authors have<br>applied a CCBY public copyright license to any author accepted<br>manuscript version arising from this submission https://<br>creativecommons.org/licenses/by/4.0/                                                                                                     |

| Download date                  | 2025-08-01 21:34:49                                                                                                                                                                                                                                                                                                                     |

| Item downloaded<br>from        | https://hdl.handle.net/10468/13106                                                                                                                                                                                                                                                                                                      |

University College Cork, Ireland Coláiste na hOllscoile Corcaigh

# Wandering Spur Suppression in a 4.9-GHz Fractional-*N* Frequency Synthesizer

Dawei Mai<sup>®</sup>, *Member, IEEE*, Yann Donnelly, *Member, IEEE*, Michael Peter Kennedy<sup>®</sup>, *Fellow, IEEE*, Stefano Tulisi<sup>®</sup>, James Breslin, Patrick Griffin<sup>®</sup>, Michael Connor, Stephen Brookes, Brian Shelly, and Mike Keaveney<sup>®</sup>, *Member, IEEE*

Abstract—Fractional-N frequency synthesizers that use a digital  $\Delta-\Sigma$  modulator (DDSM) to control the feedback divider can exhibit spurious tones that move about in the frequency domain; these are known colloquially as "walking" or wandering spurs. Building upon a theoretical explanation of the origin of wandering spurs, this article presents two methods to suppress them. It describes a 4.9-GHz 180-nm SiGe BiCMOS charge-pump phase-locked loop (CP-PLL) fractional-N frequency synthesizer platform with a divider controller that can function as: 1) a standard MASH 1-1-1; 2) a MASH 1-1-1 with high-amplitude dither; and 3) a MASH 1-1-1 with a modified third stage. Measurements confirm the effectiveness of the wandering spur suppression strategies.

Index Terms—Divider controller, fractional-N frequency synthesizers, MASH digital  $\Delta$ - $\Sigma$  modulator (DDSM), phase noise, phase-locked loops (PLLs), quantization noise, spurious tones.

# I. INTRODUCTION

**F** RACTIONAL-*N* frequency synthesizers are used in electronic systems where precise frequencies are required. Common applications include clock generation and local oscillators for wireline and wireless communications. They are also used in precision measurement equipment, such as signal generators and spectrum analyzers, and in radar.

The most common architecture is based on a phase-locked loop (PLL) with a feedback divider. The fractional part of the division ratio is controlled by a digital  $\Delta-\Sigma$  modulator (DDSM) that outputs a highpass-shaped stream of integers whose average is the required fraction. The DDSM introduces a quantization error that contributes directly to the output phase noise [1]. When the quantization noise introduced by the divider controller interacts with nonlinearity in the loop,

Manuscript received December 22, 2021; revised March 6, 2022; accepted March 16, 2022. This article was approved by Associate Editor Salvatore Levantino. This work was supported in part by the Science Foundation Ireland under Grant 13/IA/1979 and Grant 20/FFP-A/8371 and in part by Enterprise Ireland under Grant TC-2015-0019. For the purpose of open access, the authors have applied a CCBY public copyright license to any author accepted manuscript version arising from this submission. (*Corresponding author: Dawei Mai.*)

Dawei Mai and Michael Peter Kennedy are with the School of Electrical and Electronic Engineering, University College Dublin, Dublin 4, D04 V1W8 Ireland, and also with the Microelectronic Circuits Centre Ireland (MCCI), T12 R5CP Cork, Ireland (e-mail: dawei.mai@ucd.ie).

Yann Donnelly is with Qualcomm, T23 YY09 Cork, Ireland.

Stefano Tulisi, James Breslin, Patrick Griffin, Stephen Brookes, and Brian Shelly are with Analog Devices, V94 RT99 Limerick, Ireland.

Michael Connor is with Hanwha Phasor, London EC1N 7RJ, U.K.

Mike Keaveney is with Robert Bosch Ireland Ltd., V94 TRW8 Limerick, Ireland.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2022.3163080.

Digital Object Identifier 10.1109/JSSC.2022.3163080

an elevated in-band noise floor and spurious tones (spurs) appear at well-defined fixed offsets from the carrier [2], [3]. The latter is commonly called integer boundary spurs and/or fractional spurs [4].

In addition to fractional spurs that are fixed in frequency, a fractional-N frequency synthesizer with a DDSM-based divider controller can exhibit significant spurs that move about in the frequency spectrum. Depending on how the measurement equipment is configured, the phenomenon of wandering spurs can manifest itself in a variety of ways: one or more spurs that appear to "walk" across the screen of a spectrum analyzer, a noise floor that pulsates up and down erratically from sweep to sweep, or spurs that periodically appear and move toward the carrier and then away from it. When viewed with a spectrogram, the structure of the phenomenon in the frequency domain becomes evident. Since "walking" and "pulsating" are associated with the way data are presented by a measurement instrument-a spectrum analyzer-rather than the phenomenon itself, we prefer to use the term "wandering spurs" in this article.

In local oscillator applications, the fractional part of the division ratio is constant. The double accumulation of a non-zero constant within the divider controller, which could be its input, an internal initial condition, and/or the expected value of an LSB dither, causes the underlying pattern of wandering spurs that occur in the synthesizer [5], [6]. For a system that operates with a short time window, e.g., radar, burst communications, and precision instrumentation, such time-varying spurs, which can be as large as -30 to -20 dBc when they appear in-band, can have significant adverse consequences if they appear within the time window of interest. For example, wandering spurs may be interpreted as false targets in radar applications [7]. It is, therefore, desirable to suppress wandering spurs.

Modified MASH DDSM architectures for the mitigation of wandering spurs were proposed in [8], and preliminary measurement results were presented in [9]. In this work, we review the underlying mechanism that gives rise to wandering spurs in Section II and present details of the implementation of two wandering spur suppression techniques in a 4.9-GHz 180-nm SiGe BiCMOS charge-pump PLL (CP-PLL) synthesizer platform—high amplitude dither and a modified MASH DDSM—in Sections III and IV. The reference design, which has a MASH 1-1-1 divider controller, has 49.4 fs jitter but exhibits wandering spurs. We compare the effectiveness of the two spur suppression strategies with this reference design in

0018-9200 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

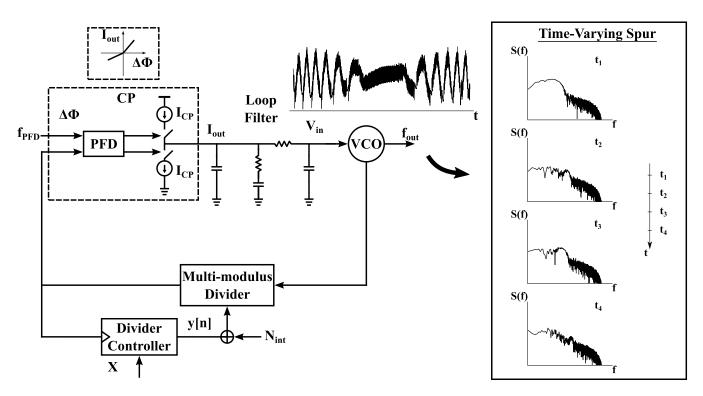

Fig. 1. Representation of the generating mechanism of nonlinearity-induced wandering spurs in a DDSM divider-based fractional-N synthesizer output (left). Short-term spectra of the output phase noise at four successive time instants ( $t_1-t_4$ ) showing a wandering spur moving away from the carrier (right).

Section V and show that wandering spurs are attenuated by more than 20 dB compared to the standard MASH with a jitter penalty of just 8 fs in the best case.

toward the zero offset frequency, which corresponds to the carrier and subsequently away from it.

# II. WANDERING SPURS IN FRACTIONAL-N FREQUENCY SYNTHESIZERS

#### A. DDSM Divider Controller and Wandering Spurs

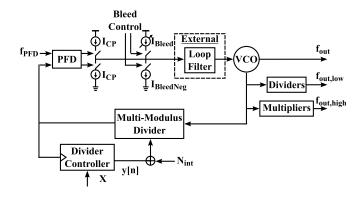

Consider a conventional CP-PLL fractional-N frequency synthesizer shown in Fig. 1 [10], [11]. It is configured to have an average divide ratio of

$$N_{\rm avg} = N_{\rm int} + \alpha = N_{\rm int} + \frac{X}{M} \tag{1}$$

with  $\alpha = X/M$ , where the input X and modulus M of the divider controller are integers. The accumulated quantization noise of the DDSM divider controller modulates the phase difference at the input of the phase/frequency detector (PFD) and, thus, contributes to the output phase noise. A chirp pattern can be observed at the input of the voltage-controlled oscillator [12]. This causes spurs that move at constant rates in the short-term spectrum of the synthesizer output, as the phase noise spectra in Fig. 1 show [6], [12].

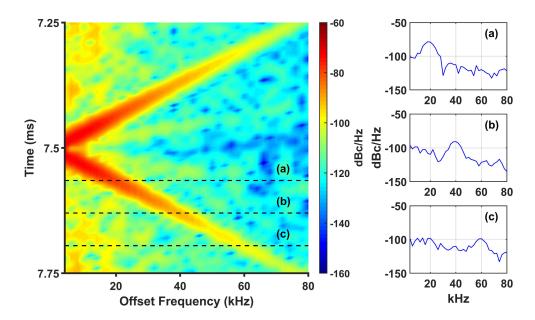

Since wandering spurs is a time-varying phenomenon, the *spectrogram* is more suitable than a spectrum for studying and evaluating these spurs. Qualitatively, the spectrogram is produced by arranging a set of short-term spectra in the order of time. The two axes in a spectrogram represent frequency and time, respectively. The amplitudes in the short-term spectra are represented by different colors. The example simulated spectrogram in Fig. 2 shows a V-shaped wandering spur event that occurs at around 7.5 ms, where the wandering spur moves

# B. Categorization of Wandering Spurs

The wandering spur phenomenon arises in a variety of divider controller architectures when the fractional divider ratio is fixed [12], [13]. In this article, we focus on a commonly used MASH 1-1-1 divider controller in this article.

The wandering spur generating mechanisms in a MASH 1-1-1 DDSM-based fractional-*N* frequency synthesizer have been elaborated in [6] and [14]. Wanderings spurs have been classified into three cases based on the input to the MASH 1-1-1 DDSM divider controller [6], [14]. Denote the constant input to the MASH 1-1-1 as x[n] = X, and express X in the form

$$X = \frac{kM+r}{D} = \frac{kM}{D} + X' \tag{2}$$

where k, D, and r are integers. k and D are coprime and non-negative. The wandering spurs can be categorized based on the constant input to the three-stage MASH 1-1-1 divider controller.

- 1) Case I: When k = 0, i.e., the small input case where the accumulation of the input X itself leads to a simple linear pattern in the first stage.

- 2) Case II: When k > 0 and  $r \neq 0$ , the residue r under modulo operation is non-zero and produces the most prominent linear pattern in the first stage after accumulation.

Fig. 2. Example spectrogram showing a wandering spur event. Conventional short-term frequency spectra (a)–(c) show that the spurious peak moves up in frequency with time during the event.

TABLE I EXAMPLE INPUTS OF DIFFERENT WANDERING SPUR CASES

| α                           | X                 | k | D | r | Input Case |

|-----------------------------|-------------------|---|---|---|------------|

| $\frac{1}{M}$               | 1                 | 0 | 1 | 1 | Case I     |

| $\frac{1}{2} + \frac{1}{M}$ | $\frac{M}{2} + 1$ | 1 | 2 | 1 | Case II    |

| $\frac{1}{2}$               | $\frac{M}{2}$     | 1 | 2 | 0 | Case III   |

3) *Case III:* When k > 0 and r = 0, no residue results under modulo operation, and the apparent linear pattern appears in the second stage.

In a hardware implementation, the divider controller modulus M is typically an integer power of two, i.e.,  $M = 2^N$  for a DDSM with a N-bit input. For a value of M that is not an integer power of two, the categorization above still applies.

Examples for all three MASH 1-1-1 DDSM input cases are shown in Table I. A small input X = 1, which gives  $\alpha = 1/M$ , causes Case I wandering spurs. When the input is just slightly offset from a fraction of M, e.g., when X = M/2 + 1 and  $\alpha = 1/2 + 1/M$ , Case II wandering spurs can be observed. When the input X is a simple fraction time of M, for instance, when X = M/2 and  $\alpha = 1/2$ , Case III wandering spurs may occur.

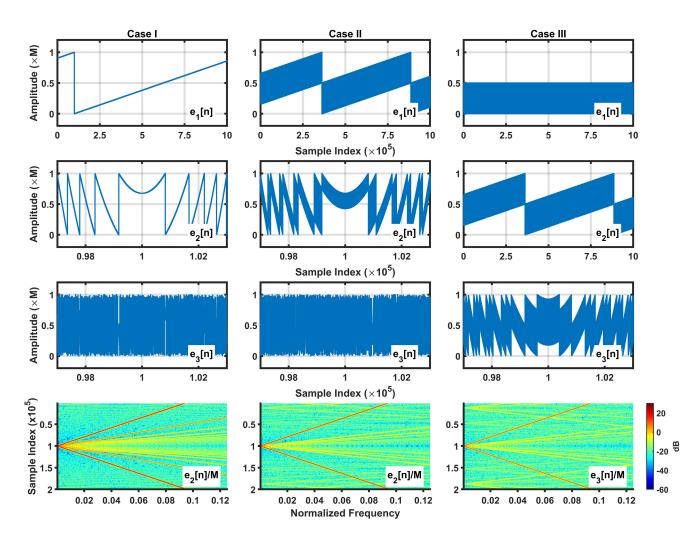

Representative waveforms and spectrograms for the three cases are shown in Fig. 3. The top three rows show the quantization error signals in the first, second, and third stages of the MASH 1-1-1, which are denoted  $e_1[n]$ ,  $e_2[n]$ , and  $e_3[n]$ , respectively. The double accumulation of a constant is the root cause of wandering spurs. It leads to the quantization error signal having the characteristic parabolic structure, which produces the chirp that causes the time-varying spurs that

form the V-shaped patterns in the spectrogram. In Case I and Case II, the  $e_2[n]$  signal contains the parabolic structure. In Case III, the parabolic waveform appears in  $e_3[n]$ .

These signals contain the underlying pattern of the wandering spurs that are eventually manifested at the output of the synthesizer in each corresponding case. According to the classical linear analysis of the MASH 1-1-1 DDSM, the quantization error signal  $e_2[n]$  should be canceled in the error cancellation network and, therefore, is not present explicitly in the output of the divider controller. In practice, the wandering spurs in Cases I and II are caused by interaction between the phase deviation due to the divider controller and nonlinearities within the synthesizer loop, such as those of the PFD and CP [6]. After distortion by the nonlinearity, spectral components associated with  $e_2[n]$  in the divider controller noise cause the most significant pattern in the  $e_2[n]$  spectrogram to appear in the synthesizer output. In these two cases, periodic wandering spur events can be observed. By contrast, wandering spurs that are independent of the nonlinearity, i.e., the spurs are inherent to the synthesizer, are present in Case III [14]. In Case III, the divider controller noise is directly related to the  $e_3[n]$  signal that contains the wandering spur pattern. As the result, numerous wandering spur events are present in the synthesizer output, resulting in complex patterns in the spectrogram.

# III. MITIGATION SOLUTIONS TO WANDERING SPURS

In this section, two wandering spur mitigation techniques based on a MASH 1-1-1 DDSM, namely, a high-amplitude dither solution and a modified MASH solution, are described.

## A. Prior Art: High-Amplitude Dither Solution

The root cause of wandering spurs in a MASH 1-1-1 DDSM-based fractional-N frequency synthesizer is the

Fig. 3. Typical waveforms of the internal error signals in different cases of wandering spurs. Signals  $e_1[n]$ ,  $e_2[n]$ , and  $e_3[n]$  are the quantization error signals from the first stage, the second stage, and the third stage of a MASH 1-1-1, respectively. Spectrograms of the scaled versions of the signals carrying the underlying wandering spur pattern in each case are shown on the bottom row.

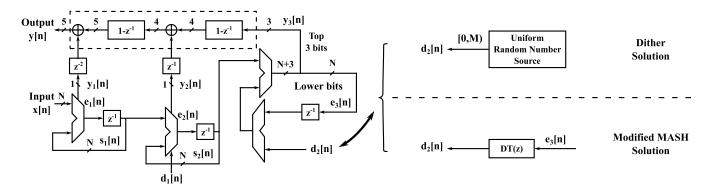

Fig. 4. MASH 1-1-1 DDSM divider controller and wandering spur suppression techniques based on it.

double accumulation of a constant within the MASH divider controller. The analysis reveals that the quantization error of the second stage either contains the underlying pattern itself or causes the underlying pattern to arise in the third-stage quantization error [6], [14].

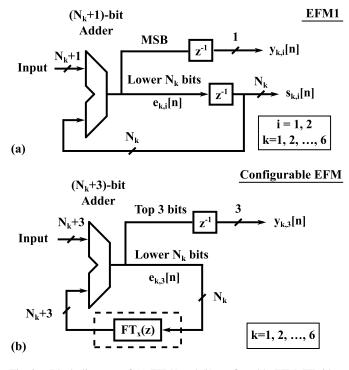

A MASH 1-1-1 DDSM with wandering spur suppression techniques can be represented by the schematic shown in

Fig. 4. A standard MASH 1-1-1 DDSM consists of three stages of first-order error feedback modulator (EFM1), which are essentially digital accumulators. A first-order shaped dither is introduced by injecting uniformly distributed LSB dither  $d_1[n]$  at the input of the second EFM1. This is used to lengthen cycles and randomize  $e_3[n]$  without adding a frequency offset [15].

MAI et al.: WANDERING SPUR SUPPRESSION IN 4.9-GHz FRACTIONAL-N FREQUENCY SYNTHESIZER

Adding high-amplitude dither  $d_2[n]$  at the input to the third-stage EFM in a MASH 1-1-1 introduces noise that is uncorrelated with  $e_2[n]$  and can, thereby, mitigate wandering spurs [8]. As shown in [8], the dither signal  $d_2[n]$  can be effective for mitigating wandering spurs. When dither  $d_2[n]$  is applied, the output of the third-stage EFM is

$$Y_3(z) = \frac{1}{M} \left( E_2(z) - \left(1 - z^{-1}\right) E_3(z) + D_2(z) \right)$$

(3)

and the output of the MASH DDSM controller is

$$Y(z) \approx \frac{1}{M} \left( X - \left(1 - z^{-1}\right)^3 E_3(z) + \left(1 - z^{-1}\right)^2 D_2(z) \right)$$

(4)

where X is the constant input. The LSB dither  $d_1[n]$  is neglected in the expression above. A uniform dither with a range [0, M) can be applied for effective wandering spur mitigation in the presence of an assumed strong piecewise linear PFD/CP nonlinearity [16].

The dither signal  $d_2[n]$  is generated from an on-chip independent source that is external to the MASH DDSM. Since the dither  $d_2[n]$  dominates the quantization noise of the MASH divider controller, care must be taken in order to ensure its spectral performance. Since the required uniform dither has a large number of bits, the complexity of implementation is higher than that of the original MASH 1-1-1 DDSM divider controller.

#### B. Modified MASH Wandering Spur Solution

The required range of the uniform random number source for the uniform dither solution is [0, M). In the theoretical analysis of the quantization noise of a MASH 1-1-1 DDSM, the quantization noise from the third-stage EFM1  $e_3[n]$  is often considered to be uniformly distributed in [0, M) [8].

Therefore, instead of introducing an externally sourced dither signal, a dither transfer function DT(z) can be applied to the error signal  $e_3[n]$  of a MASH 1-1-1 to generate an equivalent dither signal  $d_2[n]$ , as indicated in Fig. 4. Thus,

$$D_2(z) = \mathrm{DT}(z)E_3(z). \tag{5}$$

When the dither transfer function DT(z) is applied, the output of the third-stage modified EFM can be expressed as

$$Y_3(z) = \frac{1}{M} \left( E_2(z) - \left( 1 - z^{-1} - \mathrm{DT}(z) \right) E_3(z) \right).$$

(6)

In [8], several dither transfer functions that are effective in mitigating wandering spurs have been presented. As an equivalent to the uniformly distributed explicit dither, a dither transfer function

$$\mathsf{DT}(z) = z^{-2} \tag{7}$$

can be used.

As mentioned in [8], a first-order shaped equivalent dither can be achieved by choosing a suitable dither transfer function. Therefore, we also consider the dither transfer function

$$DT(z) = 2(1 - z^{-1})z^{-2}.$$

(8)

This yields a third-order shaped quantization error of the MASH divider controller that has identical low-frequency noise to that of the original MASH 1-1-1.

Fig. 5. Block diagram of the implemented fractional-*N* frequency synthesizer.

Fig. 6. Photomicrograph of the implemented synthesizer. The modulator is a MASH divider controller with wandering spur solutions.

Compared to the conventional MASH 1-1-1, a multi-bit quantizer is required in the modified EFM stage, and the buses of the cancellation network (shown in the dashed box in Fig. 4) are wider. The modified MASH has an output range of [-11, 12] versus [-3, 4] for the standard MASH. Attention should be given to the minimum division ratio due to the extended range to prevent consequences of extremely small division ratios [8]. Also, a wider output range leads to a small increase in the in-band phase noise, as we will show.

#### **IV. IMPLEMENTATION DETAILS**

# A. Synthesizer

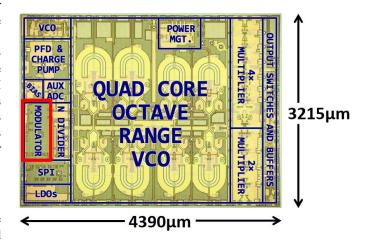

A block diagram of the implemented synthesizer is shown in Fig. 5. A photomicrograph of the synthesizer is shown in Fig. 6. The synthesizer is based on an identical architecture to that described in [17] and [18] and has a similar power consumption. It comprises a type-II CP fractional-N frequency synthesizer implemented in a 180-nm SiGe BiCMOS process [17]. A bipolar CP operating from a 5-V supply is employed. In addition to programmable up and down CP current sources, the synthesizer contains a set of binary-weighted current is used to set the CP operating point at regions of different local linearity in the overall transfer

Fig. 7. (a) Detailed structure of the implemented MASH DDSM. (b) Level k which consists of  $N_k$ -bit EFMs. Modulus  $M_k = 2^{N_k} = 2^6$  for Level 1 to Level 4 and  $M_5 = M_6 = 2$  for Level 5 and Level 6.

characteristic. A quad-core pseudo-differential Colpitts VCO is used to generate output frequencies, which covers the range from 4 to 8 GHz. Furthermore, dividers and multipliers are available at the output of the synthesizer to provide an extended output frequency range. A passive third-order *RC* loop filter is implemented externally using discrete components for the filtering of the phase noise contribution from the divider controller. A closed-loop bandwidth of approximately 100 kHz is chosen to optimize the phase noise performance. The MASH divider controller with selectable wandering spur solutions, which is the emphasis of this work, is implemented on-chip, and it will be detailed next.

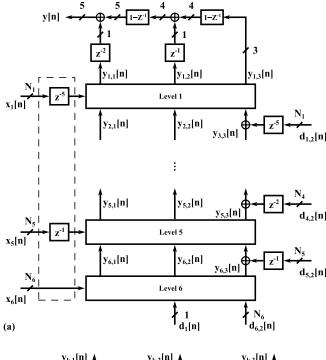

#### B. MASH Divider Controller

The 26-bit (N = 26 and  $M = 2^{26}$ ) MASH divider controller of the synthesizer is implemented over six levels using a nested cascaded structure to maximize the operational clock frequency [19]. Fig. 7(a) shows the implementation of the divider controller. Each level consists of three cascaded EFMs having the same modulus  $M_k$ , as shown in Fig. 7(b). The delayed outputs of the EFMs of each stage of a level are added to the inputs of the corresponding EFMs in its upper level. The outputs from the top level (Level 1) are combined

Fig. 8. Block diagrams of (a) EFM1 and (b) configurable EFM.  $FT_x(z) = DT(z) + z^{-1}$  is the variable transfer function.

Fig. 9. Measurement setup for the fractional-*N* frequency synthesizer with MASH-based wandering spur solutions.

through the error cancellation network to generate the output of the MASH divider controller. Each of the top four levels (Level 1–Level 4) consists of 6-bit EFMs, which is the result of the tradeoff between area and delay [19]. In order to achieve a configurable divider controller modulus, the EFMs are implemented with variable modulus in the two additional levels at the bottom [20]. They function as 1-bit EFMs in the measurements.

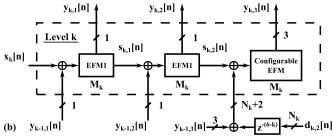

In each level, the first two cascaded stages are identical conventional first-order EFMs, as shown in Fig. 8(a). The high-amplitude dither  $d_2[n]$  is divided into  $d_{k,2}[n]$  and injected into each level based on the bit width of the EFM at that level.

In order to implement the modified MASH solution, the third EFM in each level is designed to be configurable; its structure is shown in Fig. 8(b). The configurable EFM has a

#### MAI et al.: WANDERING SPUR SUPPRESSION IN 4.9-GHz FRACTIONAL-N FREQUENCY SYNTHESIZER

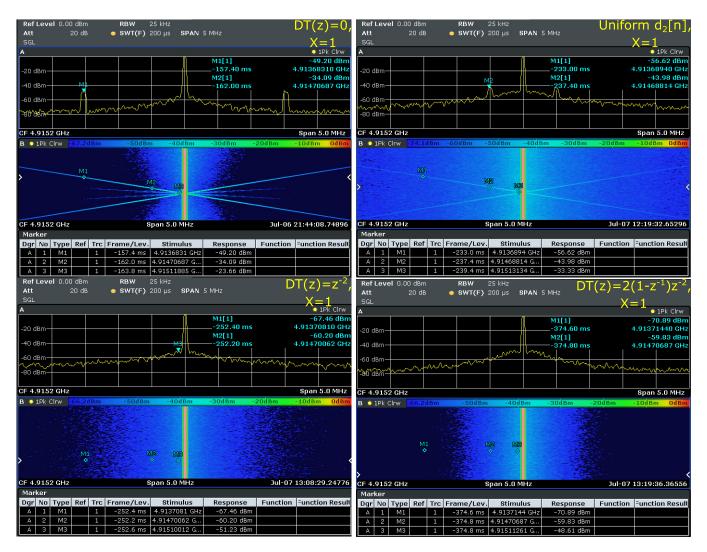

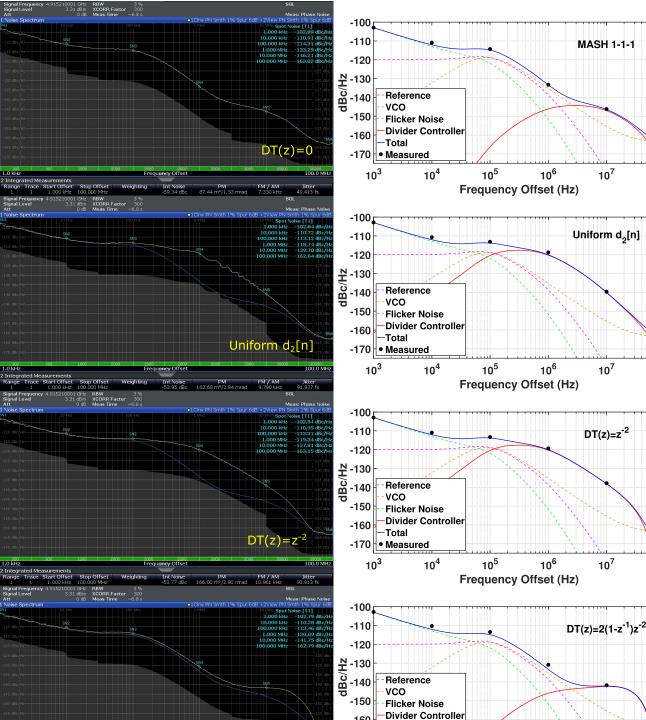

Fig. 10. Representative measured short-term spectra and spectrograms of the output of the synthesizer in Case I. The divider controller is configured as a MASH 1-1-1 DDSM without wandering spur suppression, a MASH 1-1-1 with uniform high-amplitude  $d_2[n]$  applied, a modified MASH implementing  $DT(z) = z^{-2}$ , and a modified MASH with  $DT(z) = 2(1 - z^{-1})z^{-2}$ , respectively. The divider controller input is X = 1.

variable feedback transfer function

$$FT_x(z) = z^{-1} + DT(z).$$

(9)

In the implementation, two options for the dither transfer function are available. When DT(z) = 0, the stage functions as a conventional first-order EFM; this is used as the reference for comparison purposes. When the modified MASH solution is enabled,  $FT_x(z)$  is set such that one of the dither transfer functions  $DT(z) = z^{-2}$  or  $DT(z) = 2(1 - z^{-1})z^{-2}$  is applied. When the dither solution is enabled, the dither transfer function remains DT(z) = 0.

Note that, since the EFM output  $y_{k,i}[n]$  is from the delayed accumulator output, the input  $x_k[n]$  and dither  $d_{k,2}[n]$  to the *k*th level experience corresponding delays; this ensures the correct equivalent initial condition of the first stage EFM1 and dither signal  $d_2[n]$  in a conventional MASH structure. A pseudorandom number generator based on a 61-bit linearfeedback shift register provides the uniform dither  $d_{k,2}[n]$  at each level. Compared to the standard MASH 1-1-1 divider controller, the modified MASH divider controller occupies a negligible additional area of 38  $\mu$ m<sup>2</sup>.

# V. MEASUREMENT RESULTS

# A. Measurement Setup

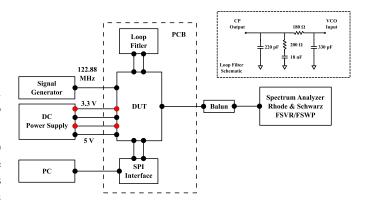

The measurement setup for the implemented frequency synthesizer is shown in Fig. 9. A reference frequency of 122.88 MHz is provided by a signal generator. The integer part of the divide ratio  $N_{\text{int}} = 40$  gives an output frequency of approximately 4.9 GHz.

Four configurations of the MASH divider controller are available: 1) DT(z) = 0, i.e., a standard MASH 1-1-1; 2) a standard MASH 1-1-1 with a uniform high-amplitude dither  $d_2[n]$  with a range [0, M); 3) the modified MASH with wandering spur mitigation having  $DT(z) = z^{-2}$ ; and 4) the modified MASH DDSM implementing  $DT(z) = 2(1 - z^{-1})z^{-2}$ .

In order to observe the potential wandering spur phenomenon, a Rhode & Schwarz FSVR spectrum analyzer with real-time spectrum function is used to generate the output

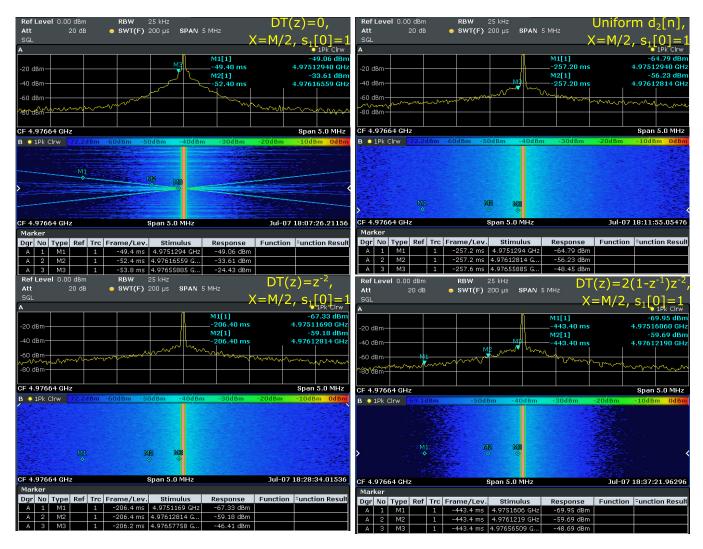

Fig. 11. Representative measured short-term spectra and spectrograms of the output of the synthesizer in Case III. The divider controller is configured as a MASH 1-1-1 DDSM without wandering spur suppression, a MASH 1-1-1 with uniform high-amplitude  $d_2[n]$  applied, a modified MASH implementing  $DT(z) = z^{-2}$ , and a modified MASH with  $DT(z) = 2(1 - z^{-1})z^{-2}$ , respectively. The divider controller input is X = M/2 and  $s_1[0] = 1$ .

spectrogram of the synthesizer. The phase noise profiles and conventional output spectra are measured using a Rhode & Schwarz FSWP spectrum analyzer.

# B. Spectrograms of Output Phase Noise

According to the analysis in [6], the presence of nonlinearity in a synthesizer gives rise to the wandering spurs in Case I and Case II. In Case III, the MASH 1-1-1-based synthesizer would exhibit wandering spurs even if there were no nonlinearity [14]. Therefore, only the results for Case I and Case III are presented due to the qualitatively similar generating mechanism between Case I and Case II. Representative divider controller inputs that lead to prominent wandering spur patterns in a standard MASH 1-1-1-based synthesizer are used. The bleed current is set to zero during the real-time spectrum and spectrogram measurements. This locates the PFD/CP operating point at a nonlinear region and, consequently, causes more prominent wandering spurs. Measured short-term spectra and spectrograms for synthesizer without and with wandering spur suppression are presented in Figs. 10 and 11.

Fig. 10 shows measurement results for Case I when the divider controller constant input is X = 1 (fractional part  $\alpha = 1/M$ ). In each screenshot, the upper part is a conventional short-term spectrum at the corresponding marker position in the synthesizer output spectrogram shown at the bottom. The short-term spectrum when the MASH 1-1-1 DDSM reference design with DT(z) = 0 is employed shows the wandering spurs at offsets of approximately  $\pm 150$  kHz. The spectrogram exhibits characteristic tip-to-tip V-shaped traces. The wandering spur amplitudes at the marker locations are -49.2, -34.09, and -23.6 dBm. When the uniform high-amplitude dither is applied, the wandering spurs have been attenuated by about 10 dB. The bottom row of Fig. 10 shows results when the modified MASH with  $DT(z) = z^{-2}$  and DT(z) = $2(1-z^{-1})z^{-2}$  are used, respectively. No wandering spur is observed in the synthesizer output when these two solutions are enabled.

Case III results are shown in Fig. 11. The divider controller constant input is X = M/2 (fractional part  $\alpha = 1/2$ ), and the first stage initial condition is  $s_1[0] = 1$  in the measurements.

10<sup>8</sup>

10<sup>8</sup>

10<sup>8</sup>

10<sup>8</sup>

Authorized licensed use limited to: UNIVERSITY COLLEGE CORK. Downloaded on April 21,2022 at 08:27:56 UTC from IEEE Xplore. Restrictions apply.

-160

-170

10<sup>3</sup>

Total

Measured

10<sup>4</sup>

The spectrogram in the reference design case shows wandering spurs. Note that the spectrogram exhibits a more complex pattern of wandering spurs than in Case I. The measurement results show that all three suppression techniques eliminate wandering spurs in this case.

DT(z)=2

# C. Long-Term Output Phase Noise Profile

The long-term output phase noise profile is a conventional method for characterizing a synthesizer's performance. Due to averaging, wandering spurs are typically not manifest in the output phase noise measurement. The bleed current is set for a

10<sup>5</sup>

10<sup>6</sup>

10<sup>7</sup>

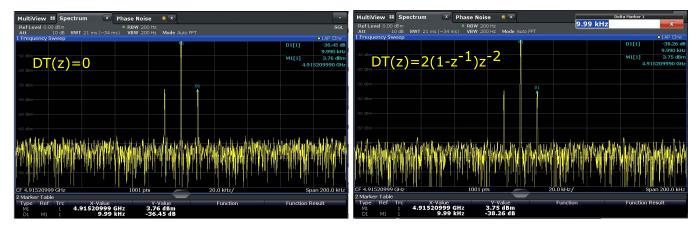

Fig. 13. Measured output spectrum of the output of the synthesizer when the divider controller is configured as a standard MASH 1-1-1 without wandering spur suppression and a modified MASH that implements  $DT(z) = 2(1 - z^{-1})z^{-2}$ . The bleed current is set to zero, giving a PFD/CP operating point at a strongly nonlinear region.

PFD/CP operating point with good local linearity in the phase noise measurements.

Example measured output phase noise profiles of the synthesizer in the conventional and wandering spur suppression modes are shown in the left column of Fig. 12. The output phase noise estimates for each case are presented in the right column. The reference design with the MASH 1-1-1 DDSM divider controller has an output jitter of 49.4 fs. When the uniform additive high-amplitude dither solution is enabled, the phase noise outside the synthesizer loop bandwidth is significantly higher than the reference MASH 1-1-1 DDSM case; this is caused by the second-order shaped quantization noise of the divider controller. As a result, the output jitter when the dither solution is applied is 91.9 fs. Similar to the dither solution, the modified MASH solution with DT(z) = $z^{-2}$  also leads to higher phase noise due to the second-order shaped quantization noise of the divider controller. The synthesizer employing this modified MASH has an output jitter of 93.8 fs.

By contrast, the quantization noise of the modified MASH solution with  $DT(z) = 2(1 - z^{-1})z^{-2}$  is third-order shaped and, thus, provides a phase noise profile that is closer to that when a MASH 1-1-1 is used. However, in comparison to the standard MASH 1-1-1 DDSM, due to the wide range of the output, the in-band noise of the synthesizer increases by approximately 1 dB when the wandering spur mitigation solution is enabled. This, together with additional high-frequency noise introduced by the modified MASH divider controller, causes the output jitter to increase to 56.8 fs compared to the reference MASH 1-1-1 design. A higher order loop filter could be used to attenuate the high-frequency noise contributed by the divider controller for the improvement of the phase noise and jitter performance in this case.

# D. Fixed Spurs

Measurement results of the synthesizer output when the standard MASH 1-1-1 DDSM and the wandering spur solution with  $DT(z) = 2(1 - z^{-1})z^{-2}$  are used are shown in Fig. 13. The bleed current is set to zero during these measurements, placing the PFD/CP operating point in a strongly nonlinear

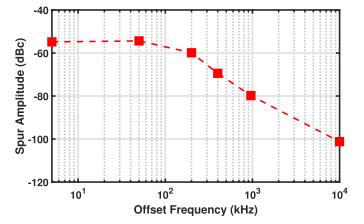

Fig. 14. Measurement results for the worst integer boundary spur amplitudes of the synthesizer.

region. Despite the larger output range of the wandering spur solution with  $DT(z) = 2(1 - z^{-1})z^{-2}$ , no significant difference in the noise floor levels is observed. Also, the two divider controllers have similar performance in terms of integer boundary spur amplitudes in the measurements. This indicates that synthesizer nonlinearity, rather than the divider controller architecture, determines the fixed spur performance.

Fig. 14 shows the results for the worst integer boundary spur amplitudes of the synthesizer at different offsets. The results are measured with the optimum bleed current settings.

# VI. CONCLUSION

Key performance metrics of the synthesizer with its MASH divider controller configured as a standard MASH 1-1-1 DDSM and a modified MASH with wandering spur mitigation are compared in Table II.

When the uniform high-amplitude dither solution is enabled, wandering spurs are attenuated by about 10 dB in Case I in the measurement. The measurements indicate that the uniform high-amplitude additive dither can eliminate wandering spurs for Case III inputs. Due to the second-order shaping of the

| Reference                    | This Work              |                                    |                  |                               |        | JSSC20<br>[22] | ISSCC18<br>[23] |

|------------------------------|------------------------|------------------------------------|------------------|-------------------------------|--------|----------------|-----------------|

| Configuration                | DT(z) = 0 (MASH 1-1-1) | Uniform Dither $d_2[n] \in [0, M)$ | $DT(z) = z^{-2}$ | $DT(z) = 2(1 - z^{-1})z^{-2}$ | N/A    | N/A            | N/A             |

| Technology<br>(nm)           | 180                    |                                    |                  |                               |        | 40             | 65              |

| Supplies<br>(V)              | 1.2/3/5                |                                    |                  |                               |        | 1.1            | N/A             |

| f <sub>PFD</sub><br>(MHz)    | 122.88                 |                                    |                  |                               |        | 50             | 52              |

| f <sub>VCO</sub><br>(GHz)    | $\approx 4.9$          |                                    |                  |                               |        | 1.67-3.12      | 3.7-4.1         |

| Loop BW<br>(kHz)             | 100                    |                                    |                  |                               |        | 2760           | 150             |

| In-Band Noise<br>(dBc/Hz)    | -114                   | -113                               | -113             | -113                          | -117.4 | -100           | -104            |

| Noise at 3 MHz<br>(dBc/Hz)   | -143                   | -128                               | -127             | -139                          | N/A    | N/A            | N/A             |

| Jitter<br>(fs)               | 49.4                   | 91.9                               | 93.8             | 56.8                          | 182    | 2260           | 183             |

| Integrated Range<br>(Hz)     | 1k-100M                |                                    |                  |                               |        | 1k-100M        | 1k-30M          |

| Power<br>Consumption<br>(mW) | 118                    |                                    |                  |                               |        | 4.85           | 5.28            |

| FoM*<br>(dB)                 | -245.4                 | -240.0                             | -239.8           | -244.2                        | -249.4 | -226.1         | -247.5          |

# TABLE II

PERFORMANCE COMPARISON

\* FoM =  $10 \log_{10} \left( (\text{Jitter}/1\text{s})^2 \times (\text{Power}/1\text{mW}) \right)$

quantization noise when the dither solution is applied, the high phase noise outside the loop bandwidth compared to the standard MASH 1-1-1 DDSM-based synthesizer leads to an increase in the output jitter from 49.4 to 91.9 fs.

When the modified MASH with  $DT(z) = z^{-2}$  is used, no wandering spurs are observed in the Case I or Case III measurements. The equivalent uniform dither also gives second-order shaped quantization error of the divider controller, which leads to high output phase noise outside the bandwidth of the synthesizer. For the synthesizer with this modified MASH, the output jitter is 93.8 fs.

When the modified MASH wandering spur solution with  $DT(z) = 2(1 - z^{-1})z^{-2}$  is enabled, the amplitude envelope of the output phase noise short-term spectrum is reduced by more than 20 dB with a jitter penalty of less than 8 fs compared to the synthesizer with the reference MASH 1-1-1 DDSM. No wandering spur pattern is observed when this suppression solution is enabled.

# REFERENCES

- B. Miller and R. J. Conley, "A multiple modulator fractional divider," *IEEE Trans. Instrum. Meas.*, vol. 40, no. 3, pp. 578–583, Jun. 1991.

- [2] D. Butterfield and B. Sun, "Prediction of fractional-N spurs for UHF PLL frequency synthesizers," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Feb. 1999, pp. 29–34.

- [3] B. De Muer and M. S. J. Steyaert, "On the analysis of  $\Delta \Sigma$  fractional-N frequency synthesizers for high-spectral purity," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 50, no. 11, pp. 784–793, Nov. 2003.

- [4] D. Banerjee, PLL Performance, Simulation, and Design. Indianapolis, IN, USA: Dog Ear Publishing, 2017.

- [5] Y. Donnelly and M. P. Kennedy, "Wandering spurs in MASH 1–1 deltasigma modulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 7, pp. 2426–2439, Jul. 2019.

- [6] D. Mai and M. P. Kennedy, "Analysis of wandering spur patterns in a fractional-*N* frequency synthesizer with a MASH-based divider controller," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 3, pp. 729–742, Mar. 2020.

- [7] L. Grimaldi, D. Cherniak, W. Grollitsch, and R. Nonis, "Analysis of spurs impact in PLL-based FMCW radar systems," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Oct. 2020, pp. 1–4.

- [8] D. Mai and M. P. Kennedy, "MASH-based divider controllers for mitigation of wandering spurs in a fractional-N frequency synthesizer," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 1, pp. 126–137, Jan. 2021.

- [9] D. Mai et al., "Experimental verification of wandering spur suppression technique in a 4.9 GHz fractional-N frequency synthesizer," in *Proc. IEEE 47th Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2021, pp. 439–442.

- [10] T. A. D. Riley, M. A. Copeland, and T. A. Kwasniewski, "Delta-sigma modulation in fractional-N frequency synthesis," *IEEE J. Solid-State Circuits*, vol. 28, no. 5, pp. 553–559, May 1993.

- [11] W. Egan, Advanced Frequency Synthesis. New York, NY, USA: Wiley, 2011.

- [12] D. Mai, H. Mo, and M. P. Kennedy, "Observations and analysis of wandering spurs in MASH-based fractional-N frequency synthesizers," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 5, pp. 662–666, May 2018.

- [13] E. Familier and I. Galton, "Second and third-order successive requantizers for spurious tone reduction in low-noise fractional-N PLLs," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2017, pp. 1–4.

- [14] D. Mai and M. P. Kennedy, "Influence of initial condition on wandering spur pattern in a MASH-based fractional-N frequency synthesizer," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 12, pp. 2968–2972, Dec. 2020.

- [15] S. Pamarti and I. Galton, "LSB dithering in MASH delta-sigma D/A converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 4, pp. 779–790, Apr. 2007.

- [16] H. Mo and M. P. Kennedy, "Apparatus for reducing wandering spurs in a fractional-N frequency synthesizer," U.S. Patent 10541707, Jan. 21, 2020.

- [17] M. P. Kennedy *et al.*, "4.48 GHz 0.18 μm SiGe BiCMOS exactfrequency fractional-N frequency synthesizer with spurious-tone suppression yielding a -80dBc in-band fractional spur," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 272–274.

- [18] Y. Donnelly et al., "4.48-GHz fractional-N frequency synthesizer with spurious-tone suppression via probability mass redistribution," *IEEE Solid-State Circuits Letters*, vol. 2, no. 11, pp. 264–267, Nov. 2019.

- [19] Y. Donnelly, H. Mo, and M. P. Kennedy, "High-speed nested cascaded MASH digital delta-sigma modulator-based divider controller," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2018, pp. 1–5.

- [20] M. P. Kennedy, B. Fitzgibbon, A. Harney, H. Shanan, and M. Keaveney, "High speed, high accuracy fractional-N frequency synthesizer using nested mixed-radix digital Δ-Σ modulators," in *Proc. ESSCIRC*, Sep. 2013, pp. 245–248.

- [21] Z. Gao et al., "A 2.6-to-4.1 GHz fractional-N digital PLL based on a time-mode arithmetic unit achieving -249.4 dB FoM and -59 dBc fractional spurs," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2022, pp. 380–382.

- [22] Y. Zhang *et al.*, "A fractional-N with space-time averaging for quantization noise reduction," *IEEE J. Solid-State Circuits*, vol. 55, no. 3, pp. 602–614, Mar. 2020.

- [23] L. Bertulessi, L. Grimaldi, D. Cherniak, C. Samori, and S. Levantino, "A low-phase-noise digital bang-bang PLL with fast lock over a wide lock range," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 252–254.

Michael Peter Kennedy (Fellow, IEEE) received the B.E. degree in electronics from the National University of Ireland, Dublin, Ireland, in 1984, the M.S. and Ph.D. degrees from the University of California at Berkeley (UC Berkeley), Berkeley, CA, USA, in 1987 and 1991, respectively, the D.Eng. degree from the National University of Ireland in 2010, and the D.Sc.Eng. degree (Hons.) from Queen's University Belfast, Belfast, U.K., in 2020.

He was a Design Engineer with Philips Electronics, Dublin, a Post-Doctoral Research Engineer with

the Electronics Research Laboratory, UC Berkeley, and a Professeur Invité with the Swiss Federal Institute of Technology Lausanne (EPFL), Lausanne, Switzerland. From 1992 to 2000, he was on the faculty of the Department of Electronic and Electrical Engineering, University College Dublin (UCD), Dublin. In 2000, he joined University College Cork (UCC), Cork, Ireland, as a Professor and the Head of the Department of Microelectronic Engineering. He was the Founding Director of the Microelectronics Industry Design Association, Cork, in 2001. He was the Dean of the Faculty of Engineering, UCC, from 2003 to 2005, where he was the Vice-President for Research from 2005 to 2010. He returned to UCD as a Professor of microelectronic engineering in 2017. He has been the Scientific Director of the Microelectronic Circuits Centre Ireland, Cork, since 2010. He has over 400 publications in the area of nonlinear circuits and has taught courses on nonlinear dynamics and delta-sigma modulation in China, the U.K., Greece, Hungary, Italy, Korea, Spain, Switzerland, and the USA. His research interests are in the simulation, analysis, and design of nonlinear dynamical systems for applications in communications and signal processing.

Dr. Kennedy was made an IEEE Fellow in 1998 for his contributions to the study of neural networks and nonlinear dynamics. He was a recipient of the 1991 Best Paper Award from the International Journal of Circuit Theory and Applications and the Best Paper Award at the European Conference on Circuit Theory and Design 1999. He was awarded the IEEE Third Millennium Medal, the IEEE Circuits and Systems Society Golden Jubilee Medal in 2000, and the Inaugural Parson's Medal for Engineering Sciences by the Royal Irish Academy (RIA) in 2001. He was the Vice-President for Region 8 of the IEEE Circuits and Systems Society (CASS) from 2005 to 2007, a CASS Distinguished Lecturer from 2012 to 2013 and 2022, and the Chair of the CASS Distinguished Lecturer Program from 2017 to 2020. He was elected to membership of the RIA in 2004. He has served as the RIA Policy and International Relations Secretary from 2012 to 2016 and was the President from 2017 to 2020. He has served as an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS from 1993 to 1995 and 1999 to 2004. He has served on the IEEE Fellows Committee and the IEEE Gustav Robert Kirchhoff Award Committee.

**Dawei Mai** (Member, IEEE) received the B.E. and M.E. degrees in electrical and electronic engineering from University College Cork (UCC), Cork, Ireland, in 2015 and 2018, respectively, and the Ph.D. degree from University College Dublin (UCD), Dublin, Ireland, in 2021.

He is currently a Post-Doctoral Research Fellow with UCD and the Microelectronic Circuits Centre Ireland (MCCI), Cork. His research interests include the design, analysis, and modeling of high-performance frequency synthesizers.

**Stefano Tulisi** was born in Naples, Italy, in 1991. He received the master's degree in electronic engineering from the University of Naples Federico II, Naples, in 2015.

From 2016 to 2017, he was a Researcher Intern with the Tyndall National Institute, Cork, Ireland. Since 2017, he has been an IC Designer with Analog Devices, Limerick, Ireland.

Yann Donnelly (Member, IEEE) received the B.E. degree in electrical and electronic engineering and the Ph.D. degree from University College Cork, Cork, Ireland, in 2014 and 2018, respectively.

He was a Post-Doctoral Research Fellow with University College Dublin, Dublin, Ireland, where his work is focused on techniques for mitigating spurious tones in fractional-*N* phase-locked loops. He is currently with Qualcomm Technologies Ireland, Cork.

James Breslin received the M.Sc. degree in electronic engineering from Queen's University Belfast, Belfast, U.K., in 1996, and the M.Sc. degree in technology management from the National University of Ireland, Dublin, Ireland, in 2014.

He is currently with Analog Devices, Limerick, Ireland. He is focused on the area of low-noise radio-frequency integrated circuit (RFIC)/monolithic microwave integrated circuit (MMIC) design, including ultra-low jitter synthesizer design for frequencymodulated continuous-wave (FMCW) radar, instru-

mentation, and clocking applications.

**Patrick Griffin** was born in Kerry, Ireland, in February 1966. He received the B.Eng. degree in electronic engineering from the University of Limerick, Limerick, Ireland, in 1987.

He joined the Design Engineering Group, Analog Devices, Limerick, in 1987, where he worked on the evaluation/debug of 12-/16-bit A/D converters. From 1990 to 2000, he has worked on the design of high-performance CMOS analog integrated circuits for both servo and partial response maximum likelihood (PRML) read channel products for the

hard disk drive market. From 2000 to 2006, he has worked on the design of laser diode products at data rates up to 10 Gb/s on BiCMOS processes. From 2006 to 2015, he has designed analog mixers and other RF circuits. He is currently working with the Frequency Generation Group, Analog Devices, on the design of high-performance phase-locked loops on SiGe BiCMOS for the instrumentation market. His areas of interest include high-speed analog and mixed-signal IC design.

Michael Connor received the M.Eng. degree in electrical and electronic engineering from Queen's University Belfast, Belfast, U.K., in 2018.

He was an IC Validation Engineer with Analog Devices, Limerick, Ireland. He is currently an RF Systems Development Engineer with Hanwha Phasor, London, U.K.

**Stephen Brookes** received the B.Eng. degree (Hons.) in electronic engineering from the University of Limerick, Limerick, Ireland, in 2011.

He has been an Evaluation Engineer with Analog Devices, Limerick, Ireland, where he has been focusing on RF & microwave phase-locked loop (PLL)/voltage-controlled oscillator (VCO) products.

**Brian Shelly** was born in Cork, Ireland, in 1983. He received the B.E. degree in microelectronic engineering from University College Cork, Cork, in 2006.

Since 2007, he has been an RF Layout Architect with Analog Devices, Inc., Limerick, Ireland.

**Mike Keaveney** (Member, IEEE) received the B.E. degree in electrical and electronics engineering from University College Dublin, Dublin, Ireland, in 1986, and the M.Eng. degree from the University of Limerick, Limerick, Ireland, in 1993.

He has spent most of his career at Analog Devices, Limerick, working on ICs for communications systems from Global System for Mobile Communications (GSM) and other 2G systems all the way to 5G, with the last 20 years specializing in RF and microwave phase-locked loops (PLLs) on CMOS

and SiGe BiCMOS for communications infrastructure and automotive radar. He joined Bosch, Limerick, in 2021, where he leads the Limerick Design Centre, working on SoCs for automotive radar.

Mr. Keaveney became an ADI Fellow in 2012. He has served on the RF Subcommittee of the ISSCC Technical Program Committee from 2009 to 2014. He has been serving on the PLL Subcommittee of the ESSCIRC Technical Program Committee since 2017.