|                             | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title                       | Properties of latent interface-trap buildup in irradiated metaloxide-semiconductor transistors determined by switched bias isothermal annealing experiments                                                                                                                                                                                                                                                                                                                                                                                         |

| Authors                     | Jaksic, Aleksandar B.;Pejovic, M. M.;Ristic, G. S.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Publication date            | 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Original Citation           | Jaksic, A. B., Pejovic, M. M. and Ristic, G. S. (2000) 'Properties of latent interface-trap buildup in irradiated metal-oxide-semiconductor transistors determined by switched bias isothermal annealing experiments', Applied Physics Letters, 77(25), pp. 4220-4222. doi: 10.1063/1.1336159                                                                                                                                                                                                                                                       |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Link to publisher's version | http://aip.scitation.org/doi/abs/10.1063/1.1336159 -<br>10.1063/1.1336159                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Rights                      | © 2000 American Institute of Physics. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in Jaksic, A. B., Pejovic, M. M. and Ristic, G. S. (2000) 'Properties of latent interface-trap buildup in irradiated metaloxide-semiconductor transistors determined by switched bias isothermal annealing experiments', Applied Physics Letters, 77(25), pp. 4220-4222 and may be found at http://aip.scitation.org/doi/abs/10.1063/1.1336159 |

| Download date               | 2024-04-25 16:46:20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Item downloaded from        | https://hdl.handle.net/10468/4408                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## Properties of latent interface-trap buildup in irradiated metal—oxide—semiconductor transistors determined by switched bias isothermal annealing experiments

Aleksandar B. Jaksic, Momcilo M. Pejovic, and Goran S. Ristic

Citation: Appl. Phys. Lett. 77, 4220 (2000); doi: 10.1063/1.1336159

View online: http://dx.doi.org/10.1063/1.1336159

View Table of Contents: http://aip.scitation.org/toc/apl/77/25

Published by the American Institute of Physics

APPLIED PHYSICS LETTERS VOLUME 77, NUMBER 25 18 DECEMBER 2000

## Properties of latent interface-trap buildup in irradiated metal-oxide-semiconductor transistors determined by switched bias isothermal annealing experiments

Aleksandar B. Jaksic, a) Momcilo M. Pejovic, and Goran S. Ristic Faculty of Electronic Engineering, University of Nis, Beogradska 14, 18000 Nis, Yugoslavia

(Received 24 July 2000; accepted for publication 1 November 2000)

Isothermal annealing experiments with switched gate bias have been performed to determine the properties of the latent interface-trap buildup during postirradiation annealing of metal—oxide—semiconductor transistors. It has been found that a bias-independent process occurs until the start of the latent interface-trap buildup. During the buildup itself, oxide-trap charge is not permanently neutralized, but is temporarily compensated. © 2000 American Institute of Physics.

[S0003-6951(01)02601-8]

Regardless of many years of extensive research, there are still gaps in understanding of postirradiation effects in metal-oxide-semiconductor (MOS) devices. One of the most controversial postirradiation phenomena certainly is the so-called latent interface-trap buildup (LITB).<sup>2</sup> The LITB is defined as a large sudden increase in interface traps during postirradiation annealing, after apparent saturation of the interface-trap density immediately following the irradiation.<sup>2</sup> It can have significant implications on performance and long-term reliability of MOS devices in radiation environments. The LITB has been observed in several different MOS device types and previous investigations have clarified some details pertinent to this process. 2-5 Namely, it has a much longer time scale than normal, conventional interface trap buildup,6 which occurs during and immediately following the irradiation (several hours for normal buildup<sup>6</sup> versus several thousand hours for LITB at room temperature).<sup>5</sup> During the LITB, the increase in interface traps is accompanied by the decrease in oxide-trap charge. The LITB is a thermally activated process, with an activation energy of 0.47 eV.2 The LITB is also a radiation-induced effect, enhanced by radiation dose and positive gate bias.<sup>2,5</sup> We have recently performed a detailed study aimed at elucidating additional details of the LITB. Here, we report and discuss the results of switched bias isothermal annealing experiments that have revealed some important properties of this phenomenon.

Commercial n-channel power vertical double-diffused MOS field-effect transistors (VDMOSFETs) EFL1N10,<sup>5</sup> known to exhibit the LITB, were irradiated at room temperature with Co-60 gamma rays to a total dose of 200 Gy at a dose rate of 0.03 Gy(Si)/s. The gate bias ( $V_{\rm GS}$ ) during irradiation was +10 V. Irradiated devices were subjected to isothermal annealing, during which time the gate bias was switched from positive to negative or vice versa at some characteristic points. The first data points in the figures were measured immediately after irradiation, and the second points immediately before annealing. Transistors were characterized for the densities of radiation-induced oxide-trap

charge  $[\Delta N_{\rm ot}({\rm cm}^{-2})]$  and interface traps  $[\Delta N_{\rm it}({\rm cm}^{-2})]$ , us-

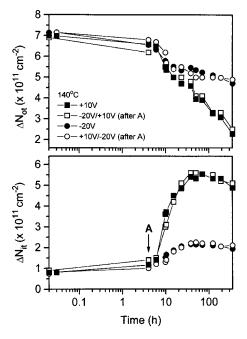

Figure 1 shows  $\Delta N_{\rm ot}$  and  $\Delta N_{\rm it}$  during annealing for the case when the bias switch was made immediately before the start of LITB, i.e., at the end of phase 1 of annealing. It can be concluded that the  $\Delta N_{\rm it}$  and  $\Delta N_{\rm ot}$  behaviors are independent of the bias sign during phase 1. Moreover, the bias sign during this phase does not affect device response at later annealing times. It is the bias sign in the period after the start of the LITB that determines the defects' behavior. The LITB is observed for both positive and negative  $V_{\rm GS}$ , but is largely suppressed in the latter case.

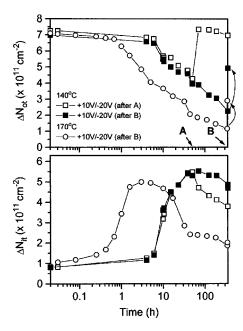

Figure 2 shows the effect of bias switch from positive to negative at some characteristic points during annealing.

FIG. 1.  $\Delta N_{\rm ot}$  and  $\Delta N_{\rm it}$  during switched bias isothermal annealing at 140 °C. The bias was switched at point A (4 h).

ing the midgap (MG) technique of McWhorter and Winokur. The modified charge-pumping (CP) technique for power VDMOSFETs (Ref. 8) was also used. Only MG data will be shown here, CP data in all cases confirm the trends of MG data.

Figure 1 shows  $\Delta N_{\rm eff}$  and  $\Delta N_{\rm eff}$  during annealing for the

a) Now with National Microelectronics Research Centre (NMRC), Lee Maltings, Cork, Republic of Ireland; electronic mail: ajaksic@nmrc.ie

FIG. 2.  $\Delta N_{\rm ot}$  and  $\Delta N_{\rm it}$  during switched bias isothermal annealing at 140 and 170 °C. The bias was switched from positive to negative at point A (50 h) or B (340 h) at 140 °C and at point B (340 h) at 170 °C. Arrows point to  $\Delta N_{\rm ot}$  values after the bias switch at 340 h.

When the switch is made at the point of maximum  $\Delta N_{\rm it}$  (140 °C data),  $\Delta N_{\rm ot}$  "rebounds" to its preannealing value and the  $\Delta N_{\rm it}$  decrease is enhanced. The first postswitch data point in Fig. 2 was measured some 20 h after the switch; however, it takes only several minutes, if not even less, for dramatic changes in  $\Delta N_{\rm ot}$  to occur. These changes are shown to be reversible: switching the bias to positive again leads to  $\Delta N_{\rm ot}$  values close to the values before the first bias switch. 10 It can be concluded that during phase 2 of annealing, the oxide-trap charge is not permanently neutralized, but rather temporarily compensated by the electrons tunneling from Si under the positive bias. 11 When the bias is switched at later annealing times, i.e., at the end of phase 3 (140 and  $170\,^{\circ}\text{C}$  data),  $\Delta N_{\text{ot}}$  also rebounds, but not quite to its preannealing value, while  $\Delta N_{\rm it}$  changes are almost negligible. This implies that at later annealing times there is permanent neutralization of a portion of the oxide-trap charge. Since this portion is more significant in both absolute and relative terms at the higher annealing temperature, the permanent neutralization is most probably caused by thermal emission of electrons from the oxide valence band to traps in the oxide.<sup>12</sup>

The presented experimental results have serious implications for the understanding of processes underlying the LITB, which will be briefly discussed below. It is clear from Fig. 1 that some bias-independent process occurs during phase 1 of annealing. This is inconsistent with the LITB model involving bias-assisted tunneling of electrons from Si and the assumption of a peaked hole-trap distribution further from the Si/SiO<sub>2</sub> interface than is typical.<sup>2</sup>

An interesting possibility is to attribute the LITB to retarded H<sup>+</sup> transport through SiO<sub>2</sub> and Si and its interactions at or near the Si/SiO<sub>2</sub> interface<sup>3</sup> and/or in the Si surface layer.<sup>4</sup> Commercially processed oxides, as is our case, are plausible candidates for retarded H<sup>+</sup> transport, during which the H<sup>+</sup> is captured at traps associated with O vacancies, and released at later annealing times.<sup>3,4</sup> If we take the scenario of

interface-trap formation by H<sup>+</sup> reaction at the interface, we would have essentially the same mechanism as for conventional interface-trap buildup,6 but slowed down. A particularly intriguing possibility is that H<sup>+</sup>-induced passivation of dopants in the Si surface layer may lead to a switch from buried to surface channel conduction.4 In such a case, the latent increase in  $\Delta N_{\rm it}$  would not necessarily have to come as a consequence of the increase in the actual number of interface traps, but as a result of their increased influence on conduction in the p-channel region of our devices, as the current would move closer to the Si/SiO2 interface. The reversible exchange of H<sup>+</sup> between near-interfacial SiO<sub>2</sub> and Si, along with the reversible oxide-trap charge compensation by electrons, 11 may be responsible for rebound in  $\Delta N_{\rm ot}$  after the bias switch in Fig. 2 and also for the reversible  $\Delta N_{\rm ot}$ changes in subsequent bias switches. 10 However, the biasindependent behavior during phase 1 of annealing is more difficult to account for. It might be that the H<sup>+</sup> ions are, during this period, so deeply trapped that the bias sign has no influence on their transport. On the other hand, for the retarded H<sup>+</sup> transport concept to be consistent with experimental data in Fig. 2, almost 45% of  $\Delta N_{\rm ot}$  after irradiation should be due to hydrogen ions, and not due to trapped holes. This is not very likely, since it has been established that the majority of the radiation-induced oxide-trap charge is from holes trapped at E' centers.<sup>13</sup>

The data in Fig. 1 are in accordance with the so-called hydrogen cracking models, <sup>1,4,5</sup> as they assume as a first step diffusion to the Si/SiO<sub>2</sub> interface of radiolytic H<sub>2</sub> released in the gate oxide and/or adjacent structures (poly-Si gate, chemical-vapor-deposited oxide). <sup>14</sup> In addition, these models have been shown to be consistent with other previously known details of the LITB as well. <sup>5</sup> The crucial step in these models is the H<sub>2</sub> cracking reaction at the positive charge centers in the vicinity of the interface. <sup>14</sup> However, the cracking reaction would lead to permanent neutralization of the oxide-trap charge during the LITB, i.e., phase 2 of annealing, which is in contrast to the data in Fig. 2.

It is clear that additional work is required to elucidate all the details of the LITB. It might be that an explanation should be sought in non- $P_b$  like nature of most of electrically observable interface traps. <sup>15</sup> This assumption is in contrast to the vast majority of work on radiation effects<sup>1</sup> and is still to be verified. <sup>16</sup> Finally, within the context of the  $P_h$  approach, and not necessarily in direct connection with the LITB, we would like to stress the importance of taking into account the concurrent running of interface-trap formation and passivation processes.<sup>5</sup> This fact has often been neglected in analysis of the postirradiation response of MOSFETs. It depends on experimental conditions, such as gate bias and temperature, which process (formation or passivation of interface traps) will dominate; and it is the balance between formation and passivation kinetics that determines  $\Delta N_{it}$  postirradiation behavior.<sup>5,10</sup> Data in Fig. 2 reinforce this approach. Passivation of interface traps during long-term postirradiation annealing has been attributed to the reaction of slowly diffusing H<sub>2</sub>O at the interface and is bias independent and enhanced by temperature,<sup>5</sup> while the formation is largely enhanced by positive bias.<sup>5,6</sup> Thus, suppression of interface-trap formation by negative bias during phase 3 of annealing leads to predominant passivation at earlier times than in the case when both processes are enabled to occur ( $140\,^{\circ}\text{C}$  data). On the other hand, increased temperature also leads to predominant passivation at earlier times ( $140\,^{\circ}\text{C}$  vs  $170\,^{\circ}\text{C}$  data).

- <sup>1</sup>T. P. Ma and P. V. Dressendorfer, *Ionizing Radiation Effects in MOS Devices and Circuits* (Wiley, New York, 1989).

- <sup>2</sup>J. R. Schwank, D. M. Fleetwood, M. R. Shaneyfelt, and P. S. Winokur, IEEE Electron Device Lett. **13**, 203 (1992); J. R. Schwank, D. M. Fleetwood, M. R. Shaneyfelt, P. S. Winokur, C. L. Axness, and L. C. Riewe, IEEE Trans. Nucl. Sci. **39**, 1953 (1992).

- <sup>3</sup>D. M. Fleetwood, W. L. Warren, J. R. Schwank, P. S. Winokur, M. R. Shaneyfelt, and L. C. Riewe, IEEE Trans. Nucl. Sci. 42, 1698 (1995).

- <sup>4</sup>M. J. Johnson and D. M. Fleetwood, Appl. Phys. Lett. **70**, 1158 (1997); D. M. Fleetwood, M. J. Johnson, T. L. Meisenheimer, P. S. Winokur, W. L. Warren, and S. C. Witczak, IEEE Trans. Nucl. Sci. **44**, 1810 (1997).

- <sup>5</sup>M. Pejovic and G. Ristic, Solid-State Electron. **41**, 715 (1997); G. S. Ristic, M. M. Pejovic, and A. B. Jaksic, J. Appl. Phys. **83**, 2994 (1998); A. Jaksic, M. Pejovic, G. Ristic, and S. Rakovic, IEEE Trans. Nucl. Sci. **45**, 1365 (1998); G. S. Ristic, M. M. Pejovic, and A. B. Jaksic, J. Appl. Phys. **87**, 3468 (2000).

- <sup>6</sup>D. B. Brown and N. S. Saks, J. Appl. Phys. **70**, 3734 (1991), and references therein.

- <sup>7</sup>P. J. McWhorter and P. S. Winokur, Appl. Phys. Lett. 48, 133 (1986).

- <sup>8</sup> A. Jaksic and P. Igic, Electron. Lett. 32, 2183 (1996), and references therein.

- <sup>9</sup>We will divide postirradiation annealing into three phases, according to different patterns of  $\Delta N_{\rm it}$  behavior observed: phase 1, from immediately after irradiation to the beginning of the rapid increase in  $\Delta N_{\rm it}$  ( $\Delta N_{\rm it}$  is approximately constant); phase 2, from the end of phase 1 to the moment when  $\Delta N_{\rm it}$  reaches its maximum value ( $\Delta N_{\rm it}$  increases rapidly); and phase 3, from the end of phase 2 to the end of the experiment ( $\Delta N_{\rm it}$  decreases).

- <sup>10</sup> A. B. Jaksic, M. M. Pejovic, and G. S. Ristic, IEEE Trans. Nucl. Sci. 47, 659 (2000); A. B. Jaksic, G. S. Ristic, and M. M. Pejovic, *ibid.* 47, 580 (2000).

- <sup>11</sup> A. J. Lelis and T. R. Oldham, IEEE Trans. Nucl. Sci. 41, 1835 (1994), and references therein.

- <sup>12</sup> P. J. McWhorter, S. L. Miller, and W. M. Miller, IEEE Trans. Nucl. Sci. 37, 1682 (1990).

- <sup>13</sup>P. M. Lenahan and P. V. Dressendorfer, J. Appl. Phys. **55**, 3495 (1984).

- <sup>14</sup> R. E. Stahlbush, A. H. Edwards, D. L. Griscom, and B. J. Mrstik, J. Appl. Phys. **73**, 658 (1993); J. F. Conley, Jr. and P. M. Lenehan, IEEE Trans. Nucl. Sci. **40**, 1335 (1993).

- <sup>15</sup> R. E. Stahlbush, in *The Physics and Chemistry of SiO<sub>2</sub> and the Si-SiO<sub>2</sub> interface—3*, edited by H. Z. Massoud, E. H. Poindexter, and C. R. Helms (Plenum, New York, 1996); p. 525, and references therein.

- <sup>16</sup>P. M. Lenahan, J. J. Mele, J. F. Conley, Jr., R. K. Lowry, and D. Woodbury, IEEE Trans. Nucl. Sci. 46, 1534 (1999).