# Ollscoil na hÉireann, Corcaigh National University of Ireland, Cork

### **GeSn semiconductor for micro nanoelectronic applications**

Thesis presented by

Emmanuele Galluccio

for the degree of

**Doctor of Philosophy**

## University College Cork Department of Electrical and Electronic Engineering

Head of School: Dr. Jorge Oliveira

Supervisor: Dr. Ray Duffy

Co-supervisor: Prof. Justin Holmes

April 2020

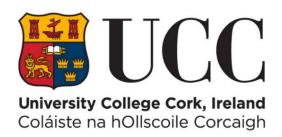

## GeSn semiconductor for micro nanoelectronic applications

Emmanuele Galluccio,

Tyndall national Institute & University College Cork

### **Declaration**

I Emmanuele Galluccio certify that the work I am submitting is my own and has not been submitted for another degree, either at University College Cork or elsewhere. All external references and sources are clearly acknowledged and identified within the contents.

Emmanuele Galluccio

### Acknowledgements

This project was not realizable without the help and the contributions of many individuals that I would like to genuinely express my gratitude.

First of all I want to express my sincere appreciation and deepest gratitude to my supervisor Dr. Ray Duffy for his priceless support and guidance throughout the course of my PhD. The fortune of having found more than an expert guide an invaluable friend allowed me to face the difficult moments without never giving up.

I would also like to give my thanks to prof. Justin Holmes who allowed me to work on this topic and the whole UCC chemistry group with whom I had the pleasure of collaborate during this amazing experience. Especially I would like to thank dr. Subhajit Biswas and prof. Nikolay Petkov for their support and discussion in device fabrication process.

I am thankful in many former to my colleagues in Tyndall where I had unforgettable moments Gioele Mirabelli, Enrico Caruso prof. Paul Hurley, dr. Farzan Gity, Shane Garvey, Noel Kennedy, Andrea Bocchino, Davide Alfieri, Pasquale Torchia, Marco Sica, Juan Morales, Krimo Khalifi, Simone Iadanza, Francesco Floris, Luca Zagaglia. I am very grateful also to all of my friends outside the work with which I spent 4 years in fun and stress-free moments.

I also wish to show my gratitude to the AMAT group in Gloucester where I spent 4 months of my PhD and I had the opportunity to work with a great team on the state of the art tools. I would like to thanks for the immeasurable experience, their encouragements and guidance during the internship period.

Lastly but not least I wish to acknowledge the support and great love of my family. Finally I am grateful to my wife that has always believed and encouraged me to give my best; she kept me going on and this work would not have been possible without her input and support, I dedicate this thesis to her.

#### **List of Publications**

#### **Based on results presented in this thesis**

- (1) **Galluccio E.**, Petkov N., Mirabelli G., Doherty J., Shih-Va L., Fang-Liang L., Chee Wee L., Holmes J., Duffy R., *Formation and characterization of Ni*, *Pt*, and *Ti stanogermanide contacts on Ge0*. *92Sn0*. *08*. Thin Solid Films, 2019. **690**: p. 137568.

- (2) Galluccio E., Petkov N., Mirabelli G., Doherty J., Shih-Va L., Fang-Liang L., Chee Wee L., Holmes J., Duffy R..., Ni, Pt, and Ti stanogermanide formation on Ge0.92Sn0.08, 2019 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Grenoble, France, 2019, pp. 1-4

- (3) Doherty J., Biswas S., Galluccio E., Broderick C., Garcia A., Duffy R., O'Reilly E., Holmes J., *Progress on Germanium-tin Nanoscale Alloys, ACS Chem. Mater.* 2020, 32, 11, 4383–4408

- (4) **Galluccio E.**, Doherty J., Biswas S., Holmes J., Duffy R., *Field-Effect Transistor Figures of merit for VLS grown Ge*<sub>1-x</sub>*Sn*<sub>x</sub> (x=0.03-0.09) *Nanowire devices*, ACS Applied Electronic Materials doi.org/10.1021/acsaelm.0c00036. 2020.

- (5) Galluccio E., Mirabelli G., Harvey A., Conroy M., Napolitani, E., Duffy, R., *Cell formation in stanogermanides using pulsed laser thermal annealing on Ge*<sub>0.91</sub>Sn<sub>0.09</sub>. Materials Science in Semiconductor Processing, 105399,2020

#### Conference contributions and talks

- **E. Galluccio**, J. Holmes, R. Duffy., *Modelling Ge(1-x)Sn(x) junctionless nanowire transistors through the study of the bandgap and effective mass in the alloy*. E-MRS fall meeting, September 18-21, 2017, Symposium L, Warsaw, Poland.

- E. Galluccio; Petkov, N., Mirabelli, G., Doherty, J., Shih-Va, L., Fang-Liang, L., Chee Wee, L., Holmes, J., Duffy, R..., Ni, Pt, and Ti stanogermanide formation on Ge0.92Sn0.08, 2019, EUROSOIULIS 2019, Grenoble, France.

#### Other contributions that are not discussed in this thesis

- (6) Duffy R., Kennedy N., Mirabelli G., **Galluccio E.**, Hurley P.K., Holmes J.D. and Long B., 2018, March. *Monolayer doping and other strategies in high surface-to-volume ratio silicon devices*. In 2018 18th International Workshop on Junction Technology (IWJT) (pp. 1-6). IEEE.

- (7) Duffy R., Thomas K., **Galluccio E.**, Mirabelli G., Sultan M., Kennedy N., Petkov N., Maxwell G., Hydes A., O'Connell D. and Lyons C., 2018. *AsH3 gas-phase ex situ doping 3D silicon structures*. Journal of Applied Physics, 124(4), p.045703.

- (8) Duffy R., Meaney F. and **Galluccio E.**, 2020. *Doping Considerations for Finfet, Gate-All-Around, and Nanosheet Based Devices*. 237th ECS Meeting with the 18th International Meeting on Chemical Sensors (IMCS 2020) (May 10-14, 2020)

- (9) Biswas S., Doherty J., **Galluccio E.**, Manning H., Conroy M., Bangert U., Duffy R., Boland J. and Holmes J. D., *Stretching the Equilibrium limit of Sn Incorporation* (x > 0.3) in Ge1-xSnx nanowires under High Pressure. (inpreparation).

## Table of Contents

| Declarat   | ion                                                           | ii         |

|------------|---------------------------------------------------------------|------------|

| Acknowl    | edgements                                                     | iv         |

| List of P  | ublications                                                   | v          |

| List of al | bbreviations                                                  | X          |

| Abstract   | ••••••                                                        | xiv        |

|            | uction                                                        |            |

| •          | e Scaling of CMOS technology                                  |            |

| 1.1.1      | Transistor shrinking challenges                               |            |

| 1.1.2      | New device architecture                                       | 7          |

| 1.1.3      | New semiconductor materials                                   | 9          |

| 1.2 Ge     | $x_{1-x}Sn_x$ alloy challenge and opportunities               | 11         |

| 1.2.1      | Theoretical perspective of $Ge_{1-x}Sn_x$ Band structure      |            |

| 1.2.2      | Growth and challenges of $Ge_{1-x}Sn_x$ material              | 14         |

| 1.2.3      | Field effect transistor and optoelectronic applications       | 15         |

| 1.3 Th     | esis structure                                                | 17         |

| 2 TCAD     | analysis and simulation on GeSn semiconductor d               | levices 20 |

|            | roduction                                                     |            |

|            | CAD Potential                                                 |            |

|            | ATERIAL BACKGROUND                                            |            |

|            | <sub>1-x</sub> Sn <sub>x</sub> physical features              |            |

| 2.4 Ge     | Crystal structure                                             |            |

| 2.4.2      | Empirical pseudo-potential methodology                        |            |

| 2.4.3      |                                                               |            |

| 2.4.4      | Mass extraction                                               |            |

|            | vice physics of Junctionless transistor (JNT)                 |            |

|            | nulation of Ge <sub>1-x</sub> Sn <sub>x</sub> JNT             |            |

| 2.6.1      |                                                               |            |

|            | Electrical characterisation before mobility calibration       |            |

| 2.6.3      | Mobility calibration                                          |            |

| 2.6.4      | Electrical characterisation after calibration                 |            |

|            | nclusion                                                      |            |

| 2   Contac | ets on Ge <sub>1-x</sub> Sn <sub>x</sub> devices              | 10         |

|            | troduction                                                    |            |

|            |                                                               |            |

|            | eory                                                          |            |

|            | ate-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> contacts |            |

|            | ontacts made by Rapid Thermal Annealing                       |            |

| 3.4.1      | Experimental procedure                                        |            |

| 3.4.2      | Results and discussion                                        |            |

| 5.5 Co     | ntacts made by Laser Thermal Annealing                        | 66         |

| 3.5.1                                                                                                                                                          | Experimental procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 3.5.2                                                                                                                                                          | Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                                                 |

| 3.5.2.                                                                                                                                                         | Electrical characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67                                                                 |

| 3.5.2.2                                                                                                                                                        | 2 Morphological analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69                                                                 |

| 3.6 Co                                                                                                                                                         | nclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75                                                                 |

|                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

|                                                                                                                                                                | g on Ge <sub>1-x</sub> Sn <sub>x</sub> devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

|                                                                                                                                                                | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

| 4.2 Th                                                                                                                                                         | eory/Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77                                                                 |

| 4.3 Do                                                                                                                                                         | ping and annealing methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79                                                                 |

| 4.4 Sta                                                                                                                                                        | te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80                                                                 |

| 4.5 SR                                                                                                                                                         | IM simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82                                                                 |

| 4.5.1                                                                                                                                                          | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82                                                                 |

| 4.5.2                                                                                                                                                          | Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 85                                                                 |

| 4.6 Do                                                                                                                                                         | ping investigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86                                                                 |

| 4.6.1                                                                                                                                                          | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

| 4.6.2                                                                                                                                                          | Ion beam approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 89                                                                 |

| 4.6.3                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

| 47 Co                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 100                                                                |

| 5  <b>Ge</b> <sub>1-x</sub> <b>S</b> :                                                                                                                         | nclusion $\mathbf{n}_{\mathbf{x}}$ Nanowires device: fabrication and characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 102                                                                |

| 5  Ge <sub>1-x</sub> Si<br>5.1 Int                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 102<br>102                                                         |

| 5  Ge <sub>1-x</sub> Si<br>5.1 Int<br>5.2 Sta                                                                                                                  | n <sub>x</sub> Nanowires device: fabrication and characterization<br>croduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 102<br>102<br>103                                                  |

| 5  Ge <sub>1-x</sub> Si<br>5.1 Int<br>5.2 Sta<br>5.3 Mo                                                                                                        | n <sub>x</sub> Nanowires device: fabrication and characterization<br>croductionte-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102<br>102<br>103<br>105                                           |

| 5  Ge <sub>1-x</sub> Si<br>5.1 Int<br>5.2 Sta<br>5.3 Mo                                                                                                        | n <sub>x</sub> Nanowires device: fabrication and characterization roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102<br>102<br>103<br>105<br>108                                    |

| 5  Ge <sub>1-x</sub> Si<br>5.1 Int<br>5.2 Sta<br>5.3 Me<br>5.4 Bo                                                                                              | n <sub>x</sub> Nanowires device: fabrication and characterization<br>croduction<br>hte-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device<br>oving from planar to 1D nanostructure devices<br>ttom up process                                                                                                                                                                                                                                                                                                                                                          | 102<br>102<br>103<br>105<br>108                                    |

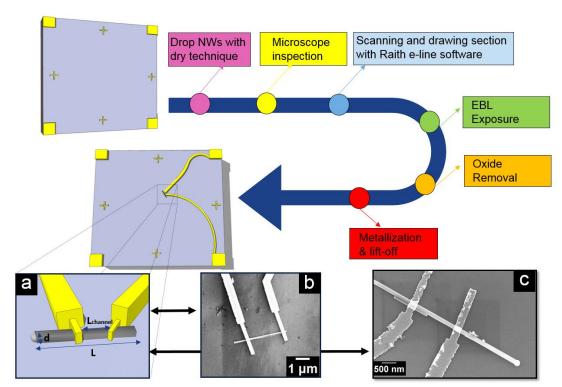

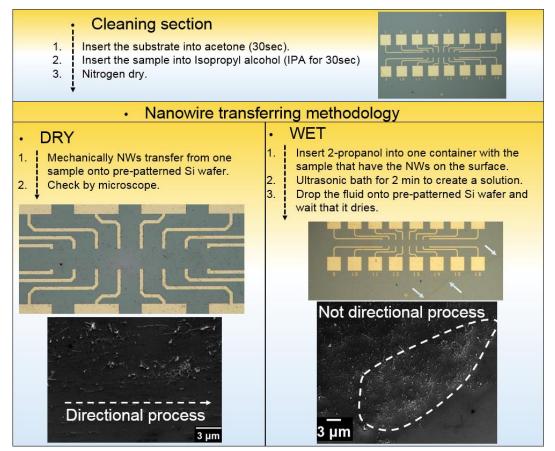

| 5  Ge <sub>1-x</sub> Si<br>5.1 Int<br>5.2 Sta<br>5.3 Me<br>5.4 Bo<br>5.4.1                                                                                     | n <sub>x</sub> Nanowires device: fabrication and characterization roduction  te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  oving from planar to 1D nanostructure devices  ttom up process  Experimental procedure and process optimization                                                                                                                                                                                                                                                                                                                    | 102<br>102<br>103<br>105<br>108<br>109                             |

| 5  Ge <sub>1-x</sub> Si<br>5.1 Int<br>5.2 Sta<br>5.3 Mo<br>5.4 Bo<br>5.4.1<br>5.4.2<br>5.4.3                                                                   | n <sub>x</sub> Nanowires device: fabrication and characterization croduction  te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  oving from planar to 1D nanostructure devices  ttom up process  Experimental procedure and process optimization  Results and discussion un-doped NWs                                                                                                                                                                                                                                                                              | 102<br>103<br>105<br>108<br>109<br>113                             |

| 5  Ge <sub>1-x</sub> Si<br>5.1 Int<br>5.2 Sta<br>5.3 Mo<br>5.4 Bo<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5 Co                                                         | n <sub>x</sub> Nanowires device: fabrication and characterization croduction  te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  oving from planar to 1D nanostructure devices  ttom up process  Experimental procedure and process optimization  Results and discussion un-doped NWs  Results and discussion doped NWs  nclusion                                                                                                                                                                                                                                  | 102<br>103<br>105<br>108<br>109<br>113<br>125                      |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co                                                                                 | n <sub>x</sub> Nanowires device: fabrication and characterization croduction  te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  oving from planar to 1D nanostructure devices  ttom up process  Experimental procedure and process optimization  Results and discussion un-doped NWs  Results and discussion doped NWs  nclusion  own Patterned Gate-All-Around devices                                                                                                                                                                                           | 102<br>103<br>105<br>108<br>109<br>125<br>128                      |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-Do 6.1 Int                                                                | n <sub>x</sub> Nanowires device: fabrication and characterization croduction nte-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device oving from planar to 1D nanostructure devices ttom up process  Experimental procedure and process optimization Results and discussion un-doped NWs Results and discussion doped NWs nclusion  own Patterned Gate-All-Around devices croduction                                                                                                                                                                                     | 102<br>103<br>105<br>108<br>109<br>125<br>128                      |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-Do 6.1 Int 6.2 Sta                                                        | n <sub>x</sub> Nanowires device: fabrication and characterization croduction  te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  oving from planar to 1D nanostructure devices  ttom up process  Experimental procedure and process optimization  Results and discussion un-doped NWs  Results and discussion doped NWs  nclusion  own Patterned Gate-All-Around devices  croduction  ate-of-the-art: nanometric multigate Ge <sub>1-x</sub> Sn <sub>x</sub> devices                                                                                               | 102<br>103<br>105<br>108<br>109<br>125<br>128<br>131<br>131        |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-Do 6.1 Int 6.2 Sta                                                        | n <sub>x</sub> Nanowires device: fabrication and characterization croduction  te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  oving from planar to 1D nanostructure devices  ttom up process  Experimental procedure and process optimization  Results and discussion un-doped NWs  Results and discussion doped NWs  nclusion  own Patterned Gate-All-Around devices  croduction  ate-of-the-art: nanometric multigate Ge <sub>1-x</sub> Sn <sub>x</sub> devices  p down Device processes                                                                      | 102<br>103<br>105<br>108<br>125<br>128<br>131<br>131<br>132        |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-Do 6.1 Int 6.2 Sta                                                        | n <sub>x</sub> Nanowires device: fabrication and characterization croduction  Ite-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  Oving from planar to 1D nanostructure devices  Experimental procedure and process optimization  Results and discussion un-doped NWs  Results and discussion doped NWs  nclusion  Own Patterned Gate-All-Around devices  croduction  Ite-of-the-art: nanometric multigate Ge <sub>1-x</sub> Sn <sub>x</sub> devices  p down Device processes  Experimental procedure                                                              | 102<br>103<br>105<br>108<br>125<br>128<br>131<br>131<br>132<br>133 |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-Do 6.1 Int 6.2 Sta 6.3 To                                                 | n <sub>x</sub> Nanowires device: fabrication and characterization croduction  Ite-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  Oving from planar to 1D nanostructure devices  Itom up process  Experimental procedure and process optimization  Results and discussion un-doped NWs  Results and discussion doped NWs  nclusion  Own Patterned Gate-All-Around devices  croduction  Ite-of-the-art: nanometric multigate Ge <sub>1-x</sub> Sn <sub>x</sub> devices  p down Device processes  Experimental procedure                                             | 102<br>103<br>105<br>108<br>125<br>128<br>131<br>131<br>132<br>133 |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-Do 6.1 Int 6.2 Sta 6.3 To 6.3.1 6.3.2                                     | n <sub>x</sub> Nanowires device: fabrication and characterization croduction  Ite-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device  Oving from planar to 1D nanostructure devices  Experimental procedure and process optimization  Results and discussion un-doped NWs  Results and discussion doped NWs  nclusion  Own Patterned Gate-All-Around devices  croduction  Ite-of-the-art: nanometric multigate Ge <sub>1-x</sub> Sn <sub>x</sub> devices  p down Device processes  Experimental procedure                                                              | 102 103 105 108 109 125 128 131 131 132 133 134                    |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Me 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-De 6.1 Int 6.2 Sta 6.3 To 6.3.1 6.3.2 6.4 Co                              | n <sub>x</sub> Nanowires device: fabrication and characterization croduction te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device oving from planar to 1D nanostructure devices ttom up process  Experimental procedure and process optimization Results and discussion un-doped NWs Results and discussion doped NWs nclusion  own Patterned Gate-All-Around devices croduction te-of-the-art: nanometric multigate Ge <sub>1-x</sub> Sn <sub>x</sub> devices p down Device processes  Experimental procedure Preliminary electrical results and discussion nclusion | 102 103 105 108 109 125 128 131 131 132 134 134 144                |

| 5  Ge <sub>1-x</sub> Si 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-Do 6.1 Int 6.2 Sta 6.3 To 6.3.1 6.3.2 6.4 Co 7  Conclu                    | n <sub>x</sub> Nanowires device: fabrication and characterization croduction te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device oving from planar to 1D nanostructure devices ttom up process  Experimental procedure and process optimization Results and discussion un-doped NWs Results and discussion doped NWs nclusion  own Patterned Gate-All-Around devices croduction te-of-the-art: nanometric multigate Ge <sub>1-x</sub> Sn <sub>x</sub> devices p down Device processes  Experimental procedure Preliminary electrical results and discussion nclusion | 102 103 105 108 109 125 128 131 131 132 134 144 144                |

| 5  Ge <sub>1-x</sub> S <sub>2</sub> 5.1 Int 5.2 Sta 5.3 Mc 5.4 Bo 5.4.1 5.4.2 5.4.3 5.5 Co 6 Top-Do 6.1 Int 6.2 Sta 6.3 To 6.3.1 6.3.2 6.4 Co 7  Conclu 7.1 Su | n <sub>x</sub> Nanowires device: fabrication and characterization croduction te-of-the-art for Ge <sub>1-x</sub> Sn <sub>x</sub> device oving from planar to 1D nanostructure devices ttom up process  Experimental procedure and process optimization Results and discussion un-doped NWs Results and discussion doped NWs nclusion  own Patterned Gate-All-Around devices croduction te-of-the-art: nanometric multigate Ge <sub>1-x</sub> Sn <sub>x</sub> devices p down Device processes  Experimental procedure Preliminary electrical results and discussion nclusion | 102 103 105 108 109 113 125 128 131 131 134 134 144 144 146        |

#### List of abbreviations

**α-Sn** Gray-Tin

$\beta$ -Sn White-Tin

$\mathcal{E}_{ox}$  Dielectric constant oxide **Esi** Dielectric constant Silicon

**ρ**<sub>C</sub> Contact Resistivity

**4PP** Four Point Probe

**AFM** Atomic Force Microscopy

**ALD** Atomic Layer Deposition

$Al_2O_3$  Aluminum oxide

**AMAT** Applied Materials

**As** Arsenic

Au Gold

**B** Boron

**BCC** Body Centre Cubic

$\mathbf{B_g}$  Bandgap

**BOE** Buffered oxide etching

**BTBT** Band to Band Tunneling

C Carbon

C<sub>B</sub> Conduction Band

**CMOS** Complementary Metal Oxide Semiconductor

**CVD** Chemical vapour deposition

**DFT** Density Functional Theory

**DI** Deionised

**DIBL** Drain Induced Barrier Lowering

**DOS** Density Of State

**EBL** Electron beam lithography

**EDX** Electron Dispersive X-ray

**Ed** Energy Displacement

**EF** Energy Fermi level

**Eg** Energy gap

**EPM** Empirical pseudopotential method

E<sub>VAC</sub> Vacuum Energy level

eSBH electron Schottky Barrier Height

**F** Fluorine

**FA** Furnace Annealing

FCC Face-Centered Cubic

**FET** Filed Effect Transistor

**FFT** Fast-Fourier-Transformation

**FLA** Flash Lamp Annealing

**GAA** Gate all around

**Ga** Gallium

**Ge** Germanium

$Ge_{1-x}Sn_x$  Germanium-Tin alloy

**HAADF** High Angle Annular Dark Filed

**HCl** Hydrogen chloride

**HF** Hydrogen fluoride

**HFO**<sub>2</sub> Hafnium dioxide

**high-K** high dielectric constant

**hSBH** hole Schottky Barrier Height

**HSQ** Hydrogen Silsesquioxane

IC Integrated Circuit

**ICP** Inductive Coupled Plasma

ICT Information & communication technology

I<sub>leak</sub> Leakage current

$I_{off}$  Off current

**I**<sub>on</sub> On current

**IPA** Isopropyl Alcohol

**IRDS** International Roadmap Device and System

ITRS International Technology Roadmap for Semiconductors

**JNT** Junctionless transistor

LN<sub>2</sub>T Liquid nitrogen temperature

**LTA** Laser Thermal annealing

MBE Molecular Beam Epitaxy

MLD Molecular Monolayer Deposition

MLDA Modified-Local-Density-Approximation

**MOSFET** Metal Oxide Semiconductor Field Effect Transistor

**MUGFET** Multiple Gate Field Effect Transistor

MS Metal-semiconductor

MWA Microwave Annealing

N Nitrogen

N<sub>2</sub> Di-Nitrogen

Ni Nickel

NiGe Nickel-Germanide

NiGeSn Nickel-Stanogermanide

NiSi Nickel-Silicide

NMOS Negative channel Metal Oxide Semiconductor

**NWs** Nanowires

O Oxygen

**PECVD** Plasma Enhanced Chemical Vapour Deposition

**PMMA** Poly Methyl Methacrylate

**PMOS** Positive channel Metal Oxide Semiconductor

**PLM** Pulsed laser melting

Pt Platinum

**PtGe** Platinum-Germanide

**PtGeSn** Platinum-Stanogermanide

**PVD** Physical Vapour Deposition

**R**<sub>C</sub> Contact Resistance

**RIE** Reactive Ion Etching

**RMS** Root Mean Square

**Rp** Projected Range

**R**<sub>sh</sub> Sheet Resistance

**RT** Room Temperature

**RTA** Rapid Thermal annealing

**SCE** Short Channel Effects

S/D Source/Drain

**SEM** Scanning Electron Microscopy

Si Silicon

**SIMS** Secondary ion mass spectroscopy

**SiN** Silicon Nitride

Sn Tin

SiO<sub>2</sub> Silicon Oxide

**SOI** Silicon on Insulator

**SPER** Solid Phase Epitaxial Regrowth

**SRIM** Stopping and Range of Ions in Matter

SS Subthreshold Slope

T Temperature

**TCAD** Technology Computer Aided Design

**TEM** Transmission Electron Microscopy

**TFET** Tunnel field effect transistor

**TLM** Transfer Length Methodology

**Ti** Titanium

**TiGe** Titanium-Germanide

**TiGeSn** Titanium-Stanogermanide

**TiSi** Titanium-Silicide

**TMD** Transition Metal Dichalcogenides

**TRIM** Transport of Ions In Matter

tox Thickness oxide

**ULSI** Ultra Large Scale Integration

$V_B$  Valence Band

VCA Virtual Crystal Approximation

V<sub>ds</sub> Drain-Source Voltage

V<sub>th</sub> Threshold Voltage

VLS Vapor-Liquid-Solid

VS Virtual Substrate

**WF** Work Function

**XTEM** Cross-sectional Transmission Electron Microscopy

#### **Abstract**

Within the last few years the steady electronic evolution lead the semiconductor world to study innovative device architectures and new materials able to replace Si platforms. In this scenario  $Ge_{1-x}Sn_x$  alloy attracts the interest of the scientific community due to its ability to tune the material bandgap as a function of Sn content and its extreme compatibility with Si processing. Although the enhanced optical properties of  $Ge_{1-x}Sn_x$  are evident, the augmented electrical properties such as the higher electron and holes mobility are also beneficial for metal oxide semiconductor. Therefore the alloy is expected to be a potential solution to integrate both electrical and optical devices.

On one hand, several theoretical and experimental works depict the  $Ge_{1-x}Sn_x$  alloy as a novel and fascinating solution to replace Si; on the other hand the material novelty forces us to enhance the knowledge of its fundamental physical and chemical properties, re-adapting the processing steps necessary to develop electronic and optical devices.

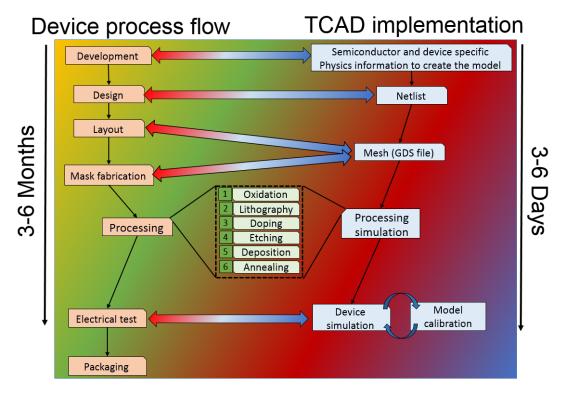

In this dissertation a comprehensive study on  $Ge_{1-x}Sn_x$  has been undertaken and discussed analysing a wide range of topics. The first chapter provides a detailed theoretical study on the electronic properties of the GeSn performed using first principle methods; subsequently the data obtained have been inserted into a TCAD software in order to create and calibrate a library used to simulate electrical devices. It is important to note, that at the beginning of this PhD GeSn was not an available material in the Synopsys device software, and thus it had to be defined from scratch

As a next point, since the ever decreasing device size push toward the definition of Ohmic contacts, different stanogermanide films have been thoroughly analysed using various metals (Ni, Pt and Ti) annealed with two distinct methodologies (Rapid Thermal Annealing and Laser Thermal Annealing).

Subsequently, considering the material limitation such as the limited thermal budget and the Sn segregation, an exhaustive study on the material doping has been firstly discussed theoretically and after experimentally characterized using both classical ion implantation and layer deposition techniques.

The different building blocks of Field Effect Transistors have been investigated and tuned individually with the aim to develop FET devices with bottom up approach. Then, Field Effect Transistor devices using GeSn NWs grown by a VLS methodology with Sn composition ranging from (0.03-0.09 at.%) have been developed and extensively characterized with the state of the art present in literature.

Finally the analysis of highly selective etch recipes lead to the development of sub-nm device configuration such as Gate-All-Around (GAA) structure obtained using classical top down lithography approach. The innovative structure was electrically characterized highlighting the possibility to obtain decananometer device architecture with this innovative alloy.

Lastly thesis summary and final outlooks were reported with the aim to outline the thesis contribution and the future material investigations.

## 1 | Introduction

#### Contents

| 1   Intro           | duction                                                             | 2  |

|---------------------|---------------------------------------------------------------------|----|

| •                   | Scaling of CMOS technology                                          |    |

|                     | Transistor shrinking challenges                                     |    |

| 1.1.2               | New device architecture                                             | 7  |

| 1.1.3               | New semiconductor materials                                         | 9  |

| 1.2 Ge <sub>1</sub> | <sub>x</sub> Sn <sub>x</sub> alloy challenge and opportunities      | 11 |

| 1.2.1               | Theoretical perspective of $Ge_{1-x}Sn_x$ Band structure            | 12 |

|                     | Growth and challenges of Ge <sub>1-x</sub> Sn <sub>x</sub> material |    |

|                     | Field effect transistor and optoelectronic applications             |    |

| 1.3 The             | sis structure                                                       | 17 |

#### This chapter is adapted from the following publication:

(1) Doherty, J.; Biswas, S.; **Galluccio, E**.; Broderick, C.; Garcia, A.; Duffy, R.; O'Reilly, E.; Holmes, J. *Progress on Germanium-tin Nanoscale Alloys ACS Chem. Mater.* 2020, 32, 11, 4383–4408

#### 1 | Introduction

In this section the conventional CMOS scaling process is extensively discussed pointing out the importance of using new semiconductor materials and alternative device architectures to overcome the technology limits. In the first part the miniaturization process is broadly debated focusing mostly on the challenges and the opportunities in relation to scaled dimensions. Thereafter, a brief literature review of the Ge<sub>1-x</sub>Sn<sub>x</sub> alloy is made focusing on three key points: modelling work to estimate the material features, the creation of reliable substrates with high enough Sn content, and lastly on the development of electronic and optical devices. Finally, a manuscript overview has been outlined to introduce the reader into this dissertation.

#### 1.1 The Scaling of CMOS technology

Down the years the disruptive semiconductor innovations set the pace for the steady progress of the *Information & Communication Technology (ICT)*. Considering the growing number of electronic devices in daily life, the transistor device had a breakthrough impact on modern society in several sectors such as telecommunication, medical, financial and environmental. *Germanium (Ge)* had always played an active and important role in the outstanding electronics history; as a matter of fact the first transistor was manufactured with Ge in the Bell labs on 1947 by W. Shockley, W. Brattain and J. Bardeen [1].

Nevertheless, the difficulty in handling Ge, in conjunction with superb *Silicon oxide* (SiO<sub>2</sub>), favoured *Silicon* (Si) development over the years [2]. From the birth of the first functional *Metal-Oxide-Semiconductor-Field-Effect-Transistor MOSFET* (1959, D. Kang and J. Atalla) up to the modern microprocessors, giant steps have been made in circuitry manufacturing [3]. The scientific proposal described by G. Moore in 1965 has been followed for generations by semiconductor companies as the driving force for endless innovations.

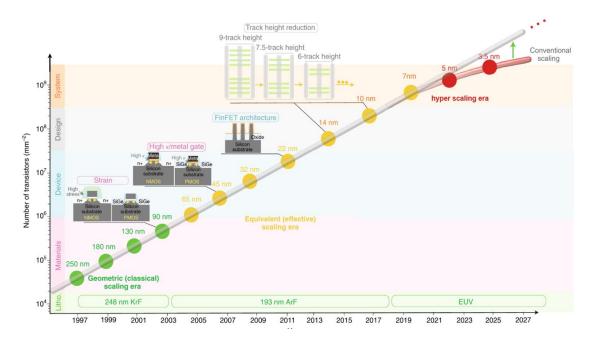

For a long period scaling followed the Dennard scaling rules [4] even though considerable efforts have been made to meet the Moore's law criteria. In the last 50 years the semiconductor companies focused relentless on Moore's law [5] to reduce the transistor device size passing from 10  $\mu$ m channel length to 7 nm nowadays. Indeed Fig. 1.1 shows both the actual status and the predicted miniaturization

process according to the IRDS international roadmap and *International Technology Roadmap for Semiconductors (ITRS)* [6].

| YEAR OF PRODUCTION                        | 2018   | 2020   | 2022           | 2025  | 2028         | 2031            | 2034            |

|-------------------------------------------|--------|--------|----------------|-------|--------------|-----------------|-----------------|

| Logic industry "Node Range" Labeling (nm) | "7"    | "5"    | "3"            | "2.1" | "1.5"        | "1.0 eq"        | "0.7 eq"        |

| Logic device structure options            | FinFET | finFET | finFET<br>LGAA | LGAA  | LGAA<br>VGAA | LGAA-3D<br>VGAA | LGAA-3D<br>VGAA |

|                                           | Oxide  | Oxode  | Oxeds          | Oxide | Oxide        | oxide 1         | Section 1       |

**Figure 1.1:** Evolution of MOSFET gate length in integrated circuit where area listed the "node range", the architecture used and the representative device image. (adapted from [7]).

Nowadays the electrical scaling trend has become a significant challenge to sustain for the semiconductor companies due to the onset of physical restrictions and bottlenecks [8]. Essentially for a long time the scaling rules were based on the constant electrical field paradigm, in order that only the gate was able to control the current flow. Nevertheless, the continuous device reduction led to a constant gate oxide thickness (tox) thinning, with the inset of high dielectric constant materials (high-k), used to reduce the tunneling effects and gate leakage current. Nonetheless as the technology node passed 130 nm, CMOS scaling had to think of alternative solutions to improve the device performance. In the beginning, the introduction of tensile or compressive strain respectively in negative channel MOS (N-MOS) and in positive channel MOS (P-MOS) allowed the continuation of the conventional scaling route. Although the application of stress lead to performance boosting [9-12], the progressive device reduction induced to a steady electrical degradation due to two bottlenecks; namely short channel effects (SCE) and the increment of the leakage current  $(I_{leak})$ . Therefore to go beyond the 32 nm technology node the multiple gate (MUGFETs) device architecture has been proposed [13, 14]. The main idea was to make the transistor more efficient against SCE by improving the gate electrostatic control. For many years numerous studies on physical properties [15-17] and process variability [16, 17] have been performed, while new devices architectures with channel lengths in the decananometer range have already been manufactured and commercially used [18-21].

However as the logic device scaling approached 10 nm the semiconductor companies had to address both the historical scaling challenges (SCE, mobility) as

well as new demands associated with the extreme gate length shrinkage (quantum effects).

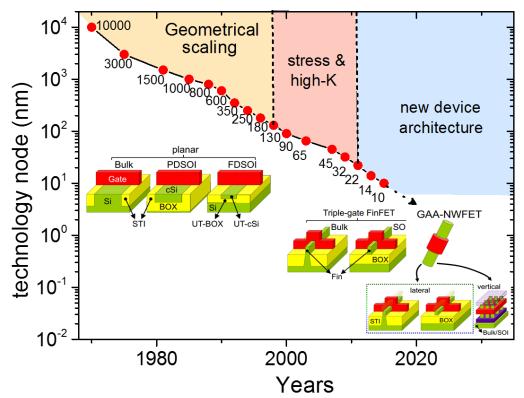

Figure 1.2 summarizes all the insights used to overcome the scaling limits as a function of the technology node released. Each area highlighted with a different colour emphasizes the intuition used to address the challenges. According to the *International Roadmap Device and System* (IRDS) [7] and Nereid roadmaps [22] the next steps would be the development of vertical hybrid structure.

Therefore new technology and alternative materials are required to go beyond the limits. Then in this scenario, Ge and its alloy seems to show the potentiality to replace Si due to the higher carrier mobility, the ability to tune the *bandgap* (B<sub>g</sub>), and the extreme compatibility with existing Si manufacturing processes.

**Figure 1.2:** Generic overview on the scaling evolution divided into three different scaling areas: geometrical equivalent and hyper scaling, adapted from [23].

#### 1.1.1 Transistor shrinking challenges

The main driving force that lead the semiconductor company to reduce the transistor size was increasing device speed coupled with reduced manufacture costs. Indeed, smaller circuits in the same time increased operating speed, while allowing more die in one wafer, cutting the total cost.

However to have a comprehensive view, before exploring the major challenges faced by the scaling process, it is important review some basic MOSFET equations and performance benchmark parameters.

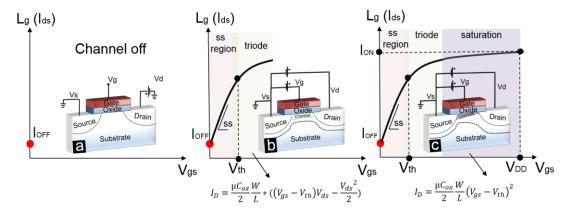

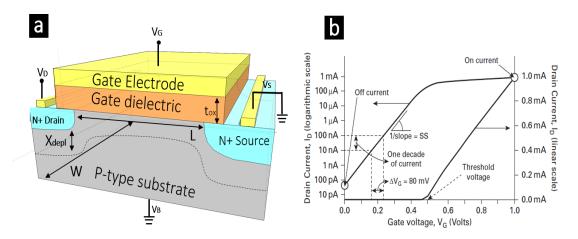

Figure 1.3 shows the typical planar MOSFET  $I_{ds}$ - $V_{gs}$  characteristics in its different region of operation. Starting from off status ( $I_{off}$ ), where no voltage is applied on the gate, the drain current is equal to zero, see Fig. 1.3.(a). Increasing the gate voltage the device reaches the threshold voltage ( $V_{th}$ ) condition, defined as the point where the minority carriers start to be attracted from the channel forming an inversion layer underneath the gate. At this stage as the drain voltage increases the device enters in triode mode, see Fig. 1.3.(b).

Furthermore, increasing  $V_{ds}$  the channel starts to saturate due to the enhancement of the depletion regions. In this situation the channel is partially truncated, but the strong electrical field around the drain region allow the carrier to pass the truncated region, see Fig. 1.3.(c). In saturation regime, as pointed out by the equation, the current is almost independent of the drain voltage, it is primarily controlled by the gate source voltage. [24]

**Figure 1.3:** *Id-Vg* characteristics in log scale for a MOSFET transistor with the representative device schematic. (a) shows the device when it is off, while (b) and (c) show respectively the characteristics in triode and saturation region with the current output equation.

Beside the typical working region of MOSFETs other important parameters to take into account for the evaluation of the fundamental transistor performance are the intrinsic speed (3); namely the time required for the input to be propagated to the output to drive a second similar inverter; the switching energy (4), composed by two parameters;  $P_{ACTIVE}$  and  $P_{PASSIVE}$  respectively related to the charging and the discharging of capacitance and to the power dissipation when the device is in sleep mode. Finally the *subthreshold slope SS* (5) that express the velocity transition between  $I_{off}$  and  $I_{on}$ .

$$\tau = C_{GATE} * V_{DD}/I_d \tag{3}$$

$$P_{TOT} = P_{ACTIVE} + P_{PASSIVE} = C * V_{DD}^{2} f + I_{leakage} * V_{DD}$$

(4)

$$SS = \left(\frac{KT}{q}\right) * \ln 10 * \left(1 + \frac{C_{bulk}}{C_{gate}}\right)$$

(5)

where f denotes the frequency, K the Boltzmann constant, T the temperature, q the electron charge,  $V_{DD}$  is the supply voltage,  $I_d$  the drain current and  $I_{leakage}$  represent the leakage current; while  $C_{bulk} = \varepsilon_{Si}/W_d$  and  $C_{gate} = \varepsilon_{ox}/t_{ox}$  are respectively bulk and gate capacitances. Looking at all the equations, the basic ideology that drove MOS device scaling was to keep  $I_d$  as large as possible while  $V_{DD}$  and  $I_{leakage}$  as small as possible in order to have fast switching without energy waste.

Nevertheless, as the device size pushed towards nanodecanometer technological nodes, numerous issues, revealed in the form of unwanted side effects, started to be considered.

As a regards of Short Channel Effects (SCEs) [15] several aspects have to be contemplated due to the strong influence on the electrical device performance.

- 1. Drain Induced Barrier Lowering (DIBL) leads to undermine the gate control due to the channel potential barrier reduction. As the gate size decreases the current into the device tends to be strongly influenced by the drain depletion region extension leading to a degradation of SS and V<sub>th</sub> [8].

- 2. Punchthrough occurs if the drain and source are enough close, the formation of a unique depletion region may happen under the gate due to the junction depletion regions spreading. This is essentially equivalent to reducing the transistor threshold voltage  $V_{th}$  roll-off because the drain is able to partially control the channel [8].

- 3. Velocity saturation caused by the strong electrical field in the channel that leads to increase the level of interaction with the lattice encouraging scattering [8].

Another relevant aspect to scrutinize is the tunneling current evolution as scaling increases. Basically by reducing the channel size two tunneling effects might contribute in Ioff degradation. Band to Band Tunneling (BTBT) occurs when the potential barriers between the drain and the gate are thin enough that the carriers

Overall the major outcome, coming from the SCE and tunneling effects, is the high leakage current in the SS region. As a matter of the fact, increasing the scaling the P<sub>PASSIVE</sub>, SS and the gate overdrive worsen dramatically [25, 26] then the only way to potentially reduce the negative effects is the use of novel semiconductor with higher mobility, new high-k materials and the formation of new multigate device architectures with higher electrostatic control [13, 17, 27].

Moreover, as MOS technology scales further, processing aspects also have to be taken into account because the reliability drastically impacts on the device accuracy [28]. Then the processing variations can be categorized in two classes [29]; the first one, historically regrouped patterning effects [30], line edge and line width roughness [31], variations in gate dielectric (thickness variations [32], defects and traps [33]). While the second one includes variations that have emerged according to the scaling pace; such as the random dopant fluctuations [34, 35] or the innovative doping technologies as the *molecular monolayer doping* (MLD) [36] through the optimization of the annealing recipes [37] or finally variations associated with the strain in the material [38].

Therefore to push beyond the nanometer nodes it is essential to face all the challenges that have arisen over the years to continue the astonishing electronics progress toward atomistic scale.

#### 1.1.2 New device architecture

The necessity of developing a new disruptive device architecture able to replace the planar configuration came from the bottlenecks that arose during the continuous transistor scaling. Fig. 1.4 shows the transistor evolution according to the technology node. Basically, the transformation process can be grouped in three main areas according to the technology booster carried out to follow the scaling paradigm (classical scaling, stress and high-k introduction and finally new device architectures).

The first refinement for the planar structure was the introduction of the Silicon

on insulator (SOI) substrate. It is well established that SOI improved the SCE control compared with traditional bulk transistor architecture because it enabled smaller source/drain to substrate capacitance, faster switching and the ability to run at lower voltages [17]. However the necessity to fabricate very thin semiconductor layers generates process variability and physical problems such as thickness targeting and quantum confinement.

As the device reduction approached the 130 nm technological node the necessity to improve the electrical behaviour due to ever worsening SCE control lead to the debut of the strain concept to boost the channel mobility (tensile for n-type and compressive for p-type). The strain technique, extensively studied in literature [39-41], relies on the equilibrium lattice constant alteration resulting in superior electrical properties. In addition, the continuous device reduction caused severe current limitations; then, both the necessity to decrease the gate leakage and to increase the electrical performance motivated to use high-k material in the 45 nm technology node [42].

Although the application of strain and high-k material did not result in a substantial MOS configuration diversity, it established the emergence of new concepts that motivated the research of new materials and ingenious device architectures. According to the idea to restrict the SCE, the multigate structure has been used for the first time in the 22 nm technology node. The definitive switch from new device architecture enabled the industry to address the SCE and go beyond what was possible with the conventional miniaturization process.[17]

Though new processing challenges emerged, with the switch to new device architectures (fabrication of high aspect ratio structures) the integration of multigate structures enabled advantages both from the electrical point of view, achieving higher performance, that from the topology, decreasing the device area [43-45]. The extraordinary electrostatic advantage over the conventional planar structure achieved led towards a reduction of SCE due to the development of device with more than two gates such as TriGate architectures [46, 47] that provide higher performance considering the similar processing challenges.

The ultimate CMOS device is likely to be a nanowire channel with surrounded gate. The *gate all around (GAA)*- FET geometry was designed with the aim of reducing SCE, however scaling has a massive effect on electrical performance.

**Figure 1.4:** Electronic device evolution as a function of the technology node, and device architecture used to enable CMOS scaling starting from the planar device up to the extremely scaled GAA-NWFET which can be implemented both in lateral and in vertical orientation (adapted from [48] and [49]).

The last exotic architecture predicted sees the development of vertical structure (skyscraper approach) interconnected through specific vias to go beyond the physical restriction (shorter wires with lower latency problems) and increase the device density [50].

Therefore in this context, the need to research and study new materials to improve the performance of these new fascinating architectures, seems to be a key point to address the new challenges proposed by the device scaling.

#### 1.1.3 New semiconductor materials

Over the last few decades new concepts as the material strain [51, 52], high-k adoption [10, 53] and new device configuration [54-57] (FinFET, GAA, *Junctionless transistor (JNT)*) have been extensively researched to continue the scaling process. The most intriguing challenge to improve the electrical device performance and go beyond physical limits consist of emerging semiconductor materials [7].

Actually to enhance the device performance there is the argument to replace Si with higher carrier mobility semiconductors such as III-V compounds [58], Ge and

its alloy [59, 60], Graphene [61], and *transition metal dichalcogenides* (TMDs) [62]. Table 1.1 details all the major semiconductor materials investigated to date. Among all the materials inspected, III-V semiconductors provide the higher electron mobility exploitable for n-MOS while Ge has superior hole mobility usable for p-MOS. In addition, Group IV semiconductors, such as Ge and its alloys, seems to be the most favourable candidates to replace Si in the future CMOS devices due to the extreme process compatibility. Beyond the compatibility with Si, Ge looks to be interesting opportunity because it exhibits several benefits as higher carrier mobility (electron (2×), hole (4×)), lower lattice constant mismatch with Si substrate and the extreme compatibility with Si processing.

Although the several advantages offered by Ge and its application as a channel booster, the semiconductor is still under research. Recent investigations on  $Ge_{1-x}Sn_x$  gained a lot of interest due to its distinctiveness. Semiconducting GeSn alloys offer higher carrier mobility, high compatibility with the already well-established Si processing and last but not least the possibility to tune the  $B_g$  as a function of the Sn content [63, 64]. Nevertheless, even considering the remarkable properties of  $Ge_{1-x}Sn_x$  alloy and the unequivocal straightforward integration with the well-established Si platform, all the steps needed to fabricate  $Ge_{1-x}Sn_x$  circuitry need to be further optimized. Nonetheless, the introduction of alternative materials into FET architectures is fraught with several difficulties such as the fabrication of high quality substrates without defects, the lattice mismatch with the substrate, the processing and fabrication challenge due to the possible contamination; therefore it is essential to re-adapt the fabrication line of the well-established Si process.

|                                            | Grou                                         | ıp IV                                         | Group III-V           |                       |               |                       |

|--------------------------------------------|----------------------------------------------|-----------------------------------------------|-----------------------|-----------------------|---------------|-----------------------|

| Semiconductors                             | Si                                           | Ge                                            | GaAs                  | InP                   | InAs          | InSb                  |

| Electron mobility (cm <sup>2</sup> /Vs)    | 1600                                         | 3900                                          | 9200                  | 5400                  | 40000         | 77000                 |

| Hole mobility (cm <sup>2</sup> /Vs)        | 430                                          | 1900                                          | 400                   | 200                   | 500           | 850                   |

| Bandgap (eV)                               | 1.12                                         | 0.66                                          | 1.42                  | 1.34                  | 0.36          | 0.14                  |

| Electron effective mass (/m <sub>0</sub> ) | m <sub>t</sub> :0.19<br>m <sub>l</sub> :0.91 | m <sub>t</sub> :0.082<br>m <sub>l</sub> :1.46 | 0.067                 | 0.08                  | 0.026         | 0.013                 |

| Hole effective                             | m <sub>HH</sub> :0.49                        | m <sub>HH</sub> :0.28                         | m <sub>HH</sub> :0.45 | m <sub>HH</sub> :0.45 | $m_{HH}:0.57$ | m <sub>HH</sub> :0.44 |

| mass(/m <sub>0</sub> )                     | $m_{LH}$ :0.16                               | $m_{LH}$ :0.04                                | $m_{LH}$ :0.08        | $m_{LH}:0.12$         | $m_{LH}:0.35$ | $m_{LH}$ :0.01        |

**Table 1.1:** Semiconductor material properties categorized as a function of group belongs adapted from [65].

Therefore, despite several challenges have to be addressed to make the transition possible, undoubtedly  $Ge_{1-x}Sn_x$  represents a valid alternative to the integration and to the scaling of both optoelectronics and logic device in one chip.

#### 1.2 Ge<sub>1-x</sub>Sn<sub>x</sub> alloy challenge and opportunities

Over the years the continual evolution of *ICT* lead to an enhancement of networked devices and data traffic in modern society [66]. Nowadays electronics apparatus are everywhere and they are part of our daily routine. Nevertheless, the conventional CMOS transistor miniaturization approach has arrived at the point where dramatic power consumption triggers materials and device architecture innovations.

Intriguing alternatives to settle the miniaturization problem includes the application of massless photons instead of electrons for the data transfer, or the usage of new semiconductors material that enables both higher speed and less power consumption devices. Therefore, for the scientific community, the ultimate insight to reduce the power consumption might be represented by the adoption of one semiconductor material able to integrate both electronic and photonic devices.

According to outstanding manuscripts by Cohen and Sau [67] and other fundamental works [68-71], the  $Ge_{1-x}Sn_x$  alloy platform exhibits higher mobility channel and direct  $B_g$  nature. Hence the material characteristics turn in set the route for MOSFET performance enhancement by merging photonics with Si-CMOS technology.

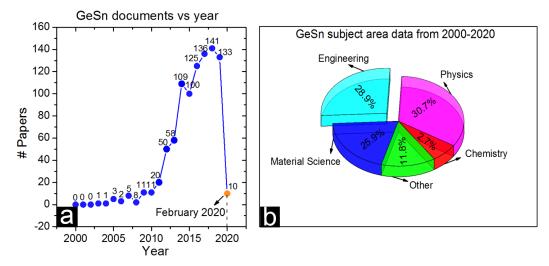

Figure 1.5 shows the increasing interest in the material according to data found on [72]; Fig 1.5.(a) reports the popularity increase in the last 20 years while Fig.1.5.(b) outlines the relative area of interest.

**Figure 1.5:** (a). GeSn manuscript evolution in scientific community with its relative areas of interest (b). Data extracted from [72].

Although the material represents a valid alternative to Silicon, the implementation route is still full of obstacles because many processing aspects need to be addressed. Hence to have a comprehensive vision about  $Ge_{1-x}Sn_x$  a literature review on three key points listed below have been made:

- (1)  $Ge_{1-x}Sn_x$  band structure.

- (2) Thin film formation and growth challenges.

- (3) Transistor and optoelectronic applications.

The three milestones chronologically represent the most important advances for the material obtained in research. The coming sections detail, as far as our knowledge in literature, challenges tackled and the future perspectives.

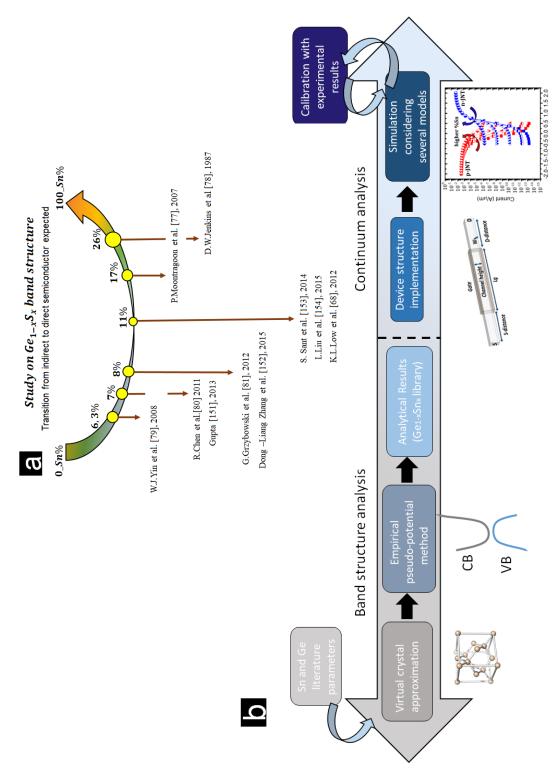

#### 1.2.1 Theoretical perspective of $Ge_{1-x}Sn_x$ Band structure

$Ge_{1-x}Sn_x$  alloy investigation started more than three decades ago with the aim to improve Ge device electrical performance. The first studies [73, 74] predicted large electron and hole mobility and the  $B_g$  modification considering a very large Sn atomic percentage (at. %) window (26%<Sn<74%). Then, for long time, the transition point between a direct  $B_g$  and indirect  $B_g$  material was not determined experimentally due to the fabrication process challenges. Nonetheless, according to more elaborate simulation models to calculate the band structure, a remarkable reduction in the Sn composition has been proposed attracting the interest of the scientific community.

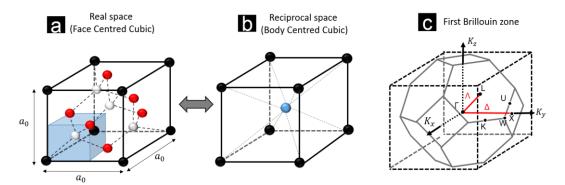

Basically Sn is an element belonging to group IV of the periodic table and in nature it exists in two allotropic forms.  $\alpha$ -Sn, also known as grey tin, with diamond

cubic lattice structure and  $\beta$ -Sn, known as white tin, which has body centred lattice structure. Then the vision to alter the Ge band structure was born from the fact that Ge shows an indirect  $B_g$  of 0.66 eV while  $\alpha$ -Sn has a negative direct  $B_g$  of -0.41eV[75]; therefore merging the two materials in an alloy was expected to create the indirect to direct bandgap transition.

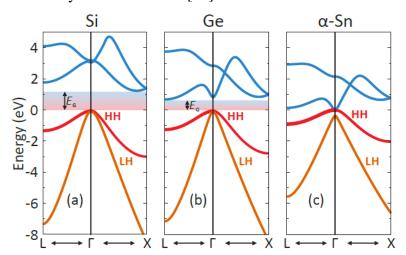

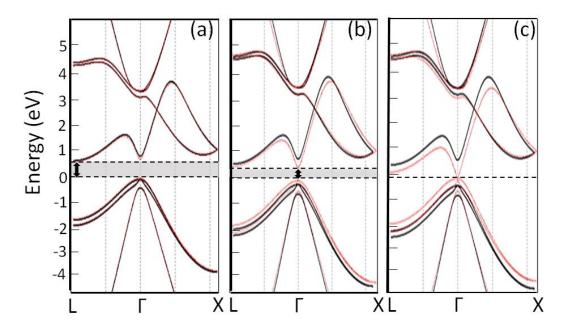

Figure 1.6 shows the band structure of Si, Ge and  $\alpha$ -Sn. Essentially Ge is an indirect semiconductor with its lowest conduction band at the L point while  $\alpha$ -Sn is a semi-metal with direct and negative  $B_g$ . Then mixing the two materials it is possible tune the  $B_g$  as a function of the Sn content because the  $\Gamma$ - valley is going to decrease faster than the L-valley, transforming the material into a direct semiconductor.

In addition, due to the large lattice mismatch between the materials, many theoretical works also include the strain influence in the calculations showing how this effect might influence electrical and optical performance. Gupta et al. [69] demonstrated that compressive strain, obtained by alloying Ge and Sn, lead to a remarkable shift of the direct B<sub>g</sub> transition towards higher Sn content. Then the stronger the compressive strain the higher Sn content is needed to the onset of direct gap, as experimentally demonstrated in [76].

**Figure 1.6:** (a-c) Band structure of Si, Ge and  $\alpha$ -Sn reprinted from [77]. Whereas Si and Ge shows indirect  $B_g$ ,  $\alpha$ -Sn exhibits a negative and direct gap.

Historically, the Sn content required to obtain the direct B<sub>g</sub> drastically reduced due to the different strategies used to extract the data. In 1987 Jenkins et al. [78] predicted using the *virtual crystal approximation (VCA)* the direct B<sub>g</sub> onset with > 20% Sn content; after that, in 2007, Moontragoon et al. [77] exploiting the atomistic

methodology (super cell mixing) to foresee the direct indirect to direct transition with 17% of Sn. Subsequently in 2008 Yin et al. [79] used *density functional theory* (*DFT*) to predict the transition at 6.3% of Sn.

Although most of the early theoretical reports return quite a wide Sn range to achieve the  $B_g$  transition; recent experimental studies [80, 81], based on photoluminescence investigations, suggest the onset of a direct gap around 7-8% of Sn. Once the Sn window has been defined atomistic analysis to explore and predict the band mixing effects influence were made [82, 83]. Recent works show the prominent effects of band mixing for  $Ge_{1-x}Sn_x$  alloy with Sn content lower than 10% due to the small Ge  $B_g$  and the hybridized mixture of L and  $\Gamma$  states.

As the material knowledge evolves,  $Ge_{1-x}Sn_x$  turns into a reality for future electric and photons devices, therefore it becomes essential take into account secondary effects as the band mixing or the Sn atom position within the lattice, to understand and predict electrical and optical features.

#### 1.2.2 Growth and challenges of $Ge_{1-x}Sn_x$ material

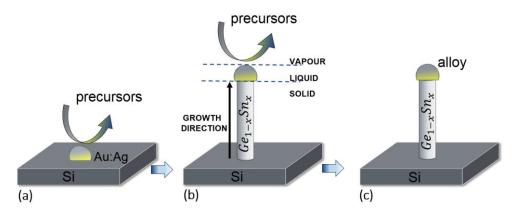

$Ge_{1-x}Sn_x$  growth established new perspectives in the semiconductor sector and the material knowledge has been improved over the year. From the first reported growth of microcrystalline  $Ge_{1-x}Sn_x$  [84] a lot of challenges have been addressed. Essentially two reasons hampered and delayed the material growth; (1) the low solid solubility of Sn into Ge (2) the high compressive strain.

According to Olesinki et al [85] the maximum solid solubility of Sn in Ge is 1.1% at 400 °C; in addition it tends to degrade as the temperature reduces expecting it to be 0.52% at room temperature. Therefore basing on theoretical and experimental previsions, listed above in the previous paragraph, the Sn content necessary to obtain the direct transition was bigger compared to the equilibrium limit. Then to obtain higher Sn integration, optimized non-equilibrium and low temperature techniques have been developed.

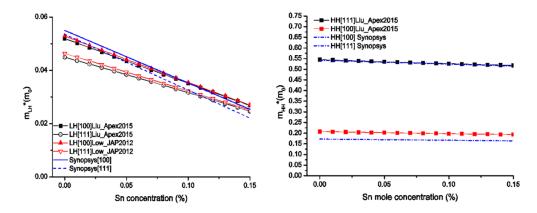

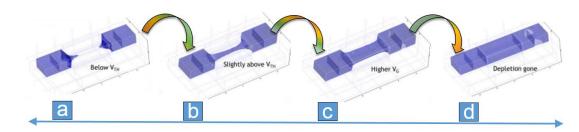

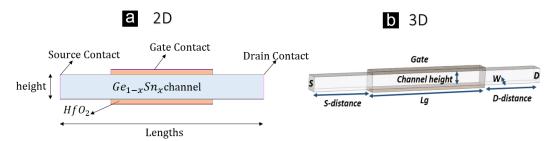

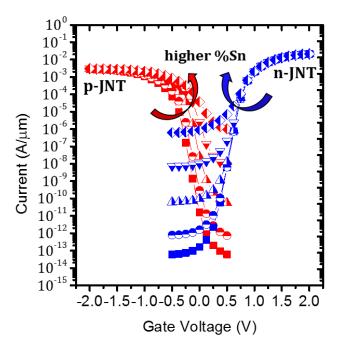

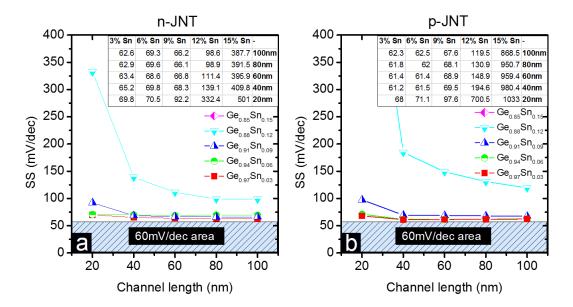

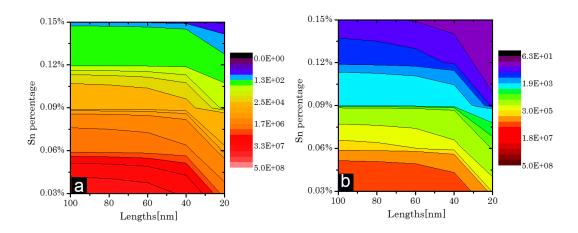

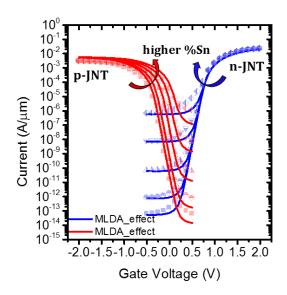

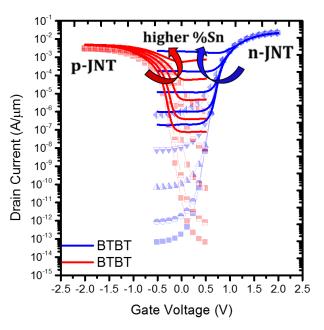

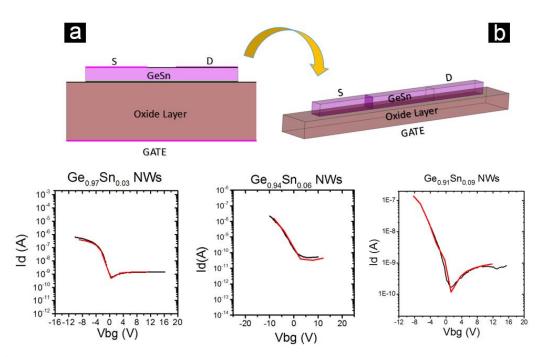

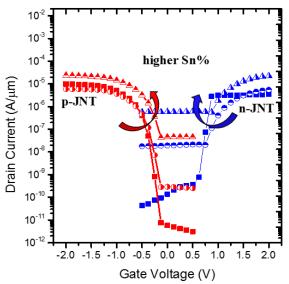

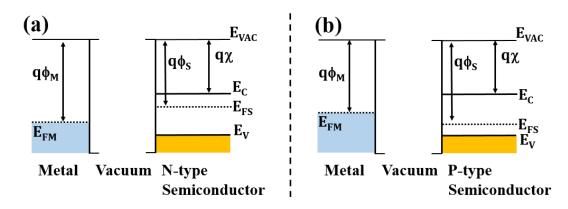

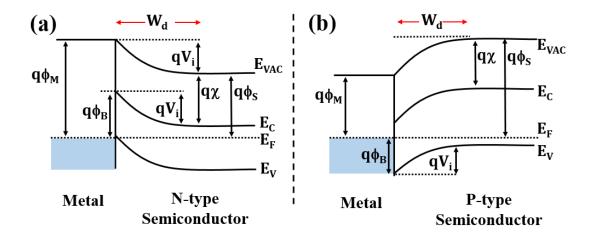

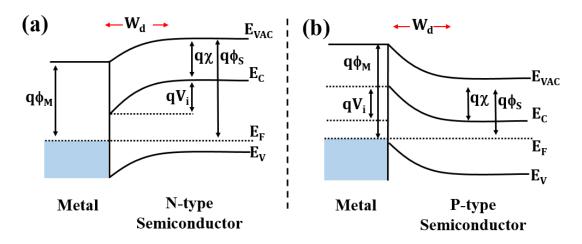

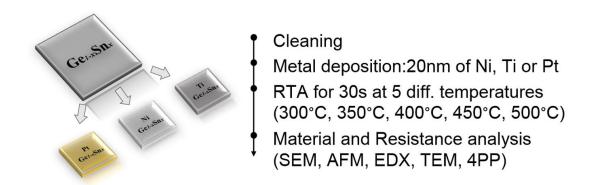

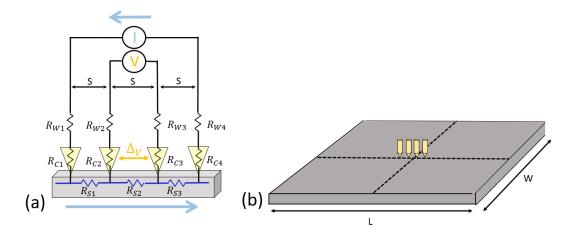

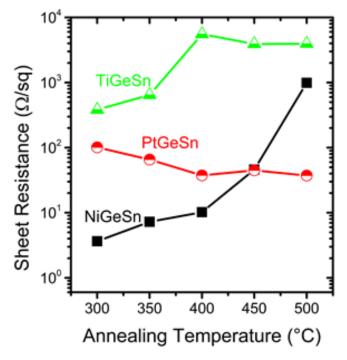

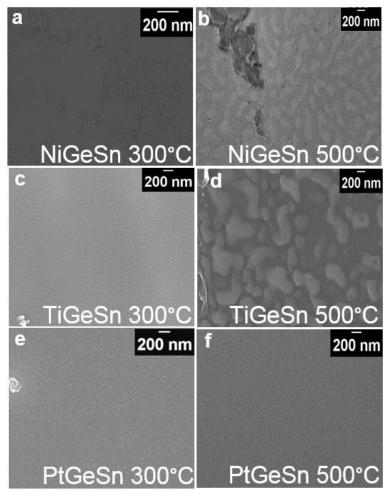

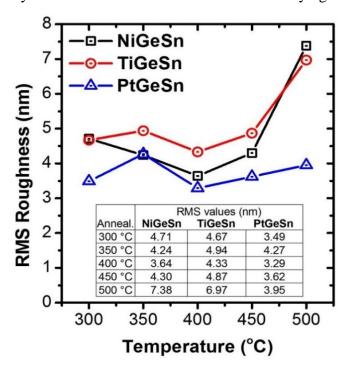

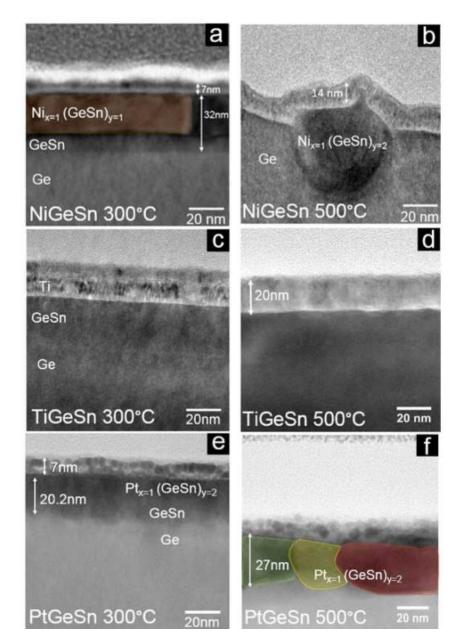

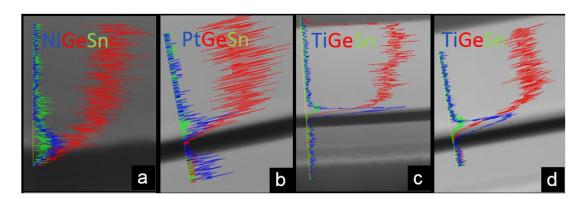

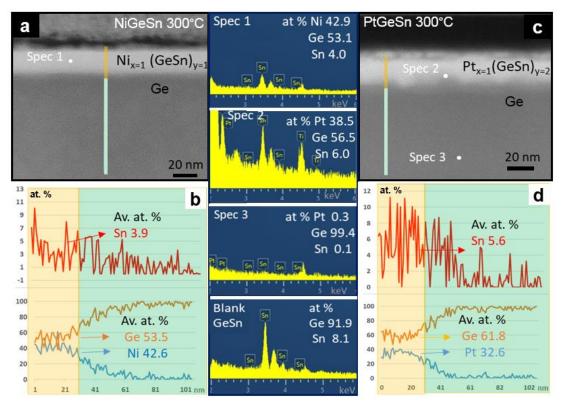

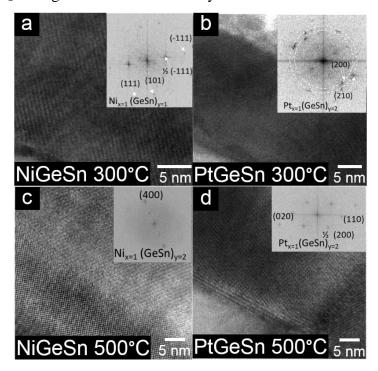

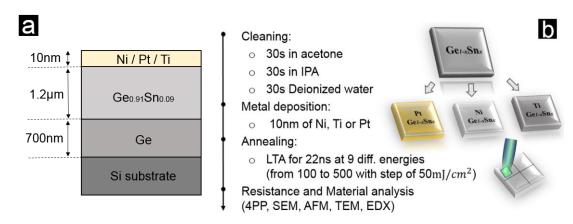

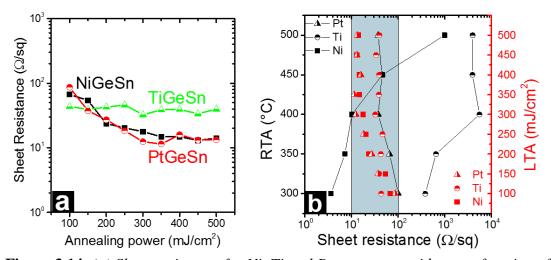

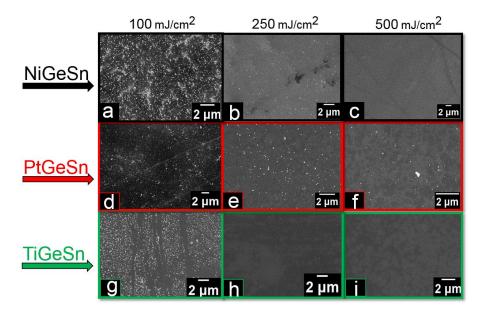

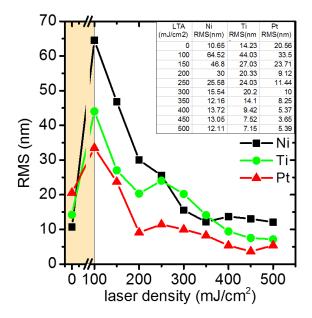

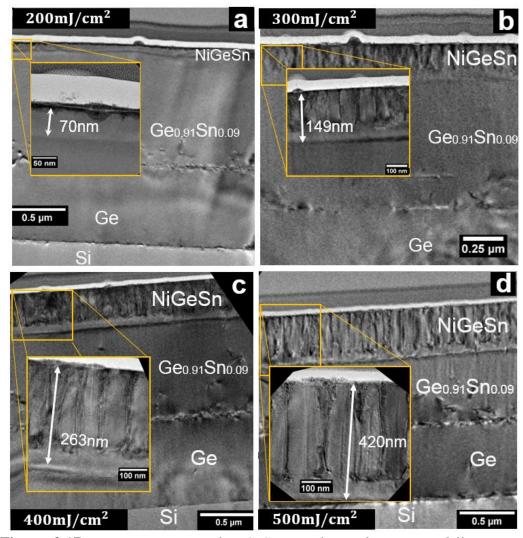

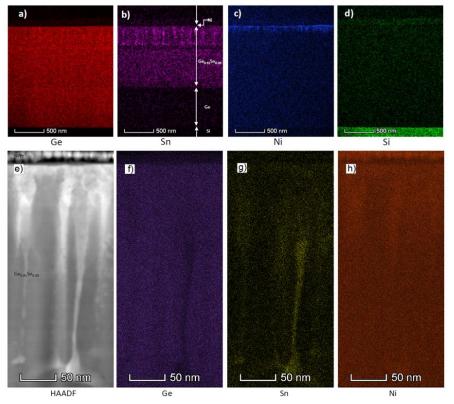

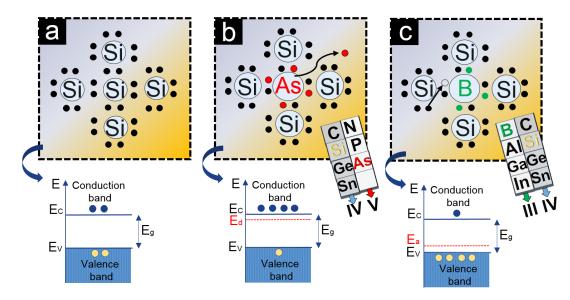

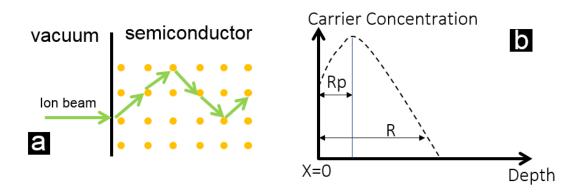

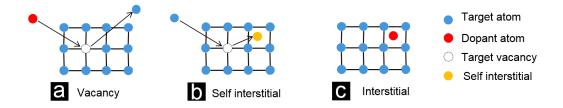

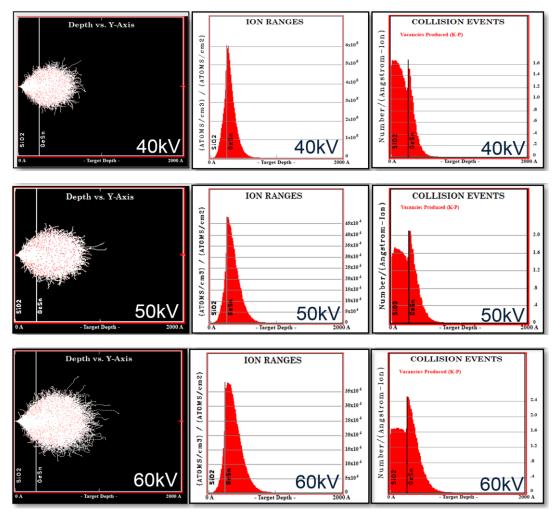

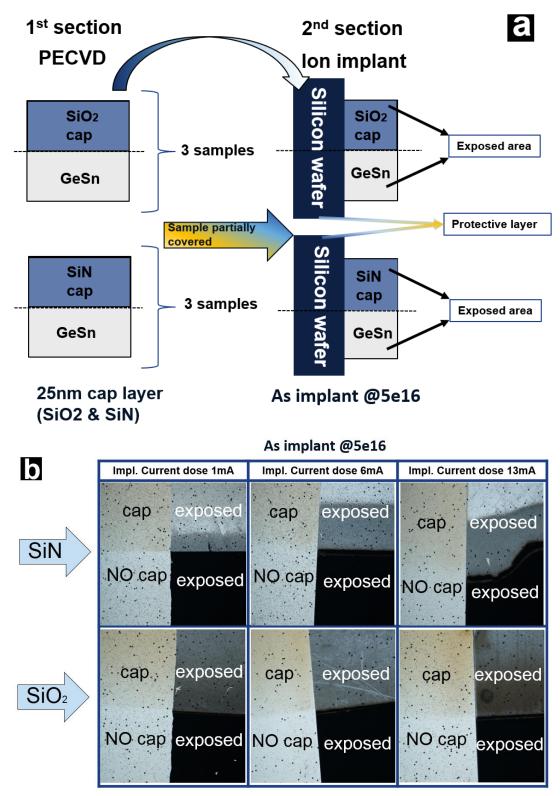

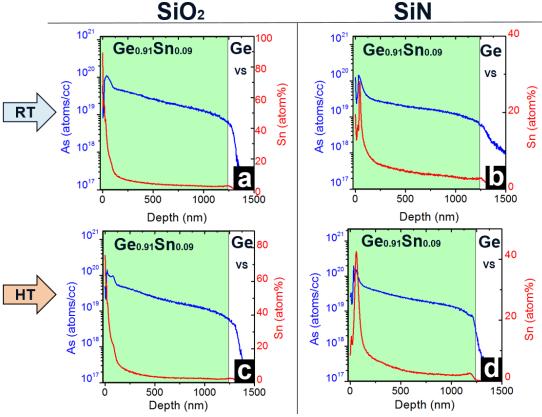

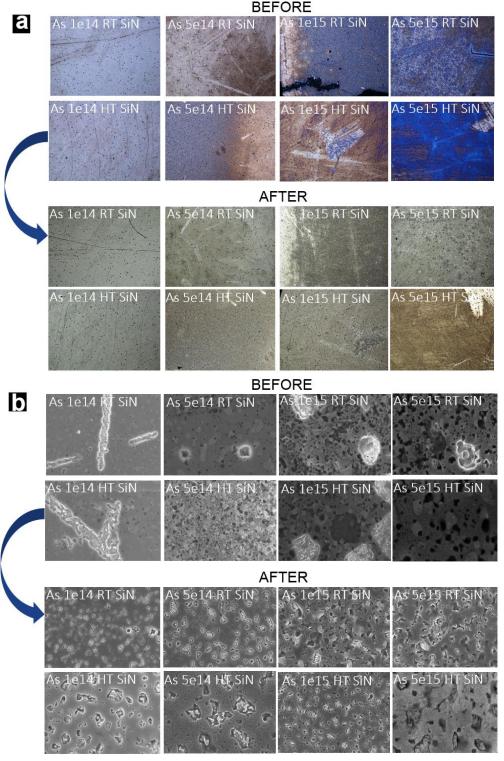

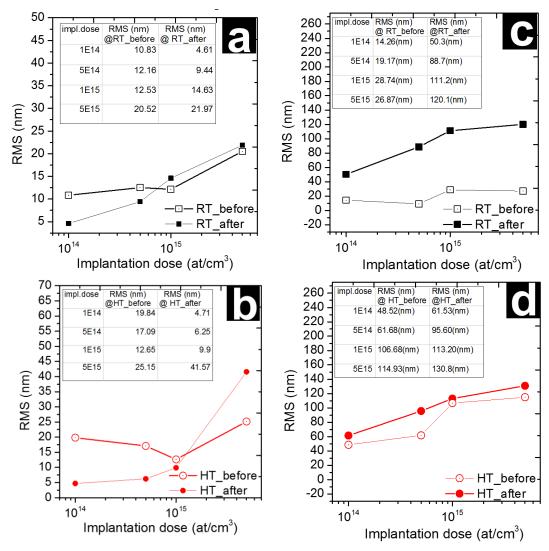

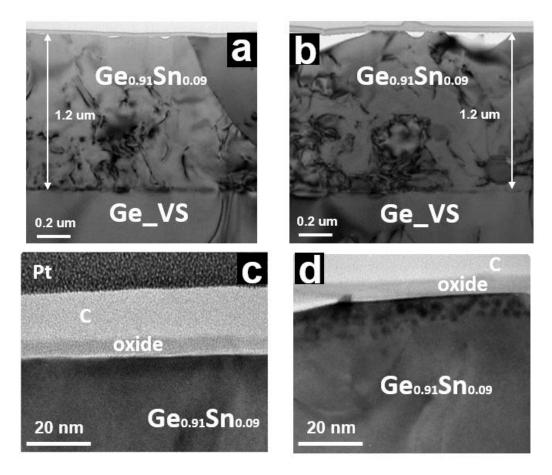

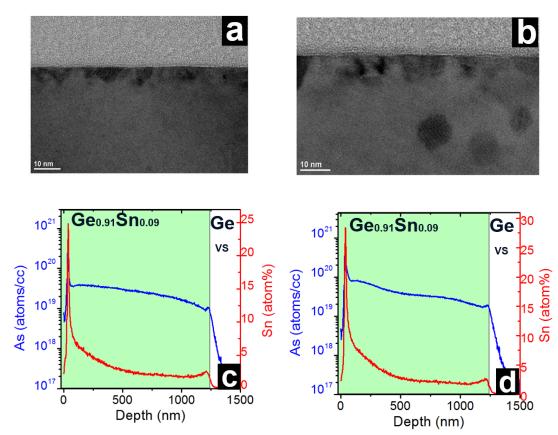

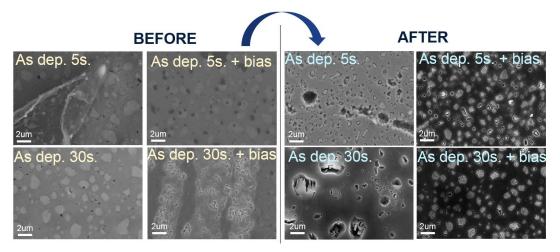

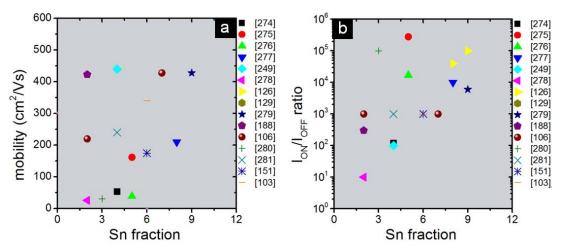

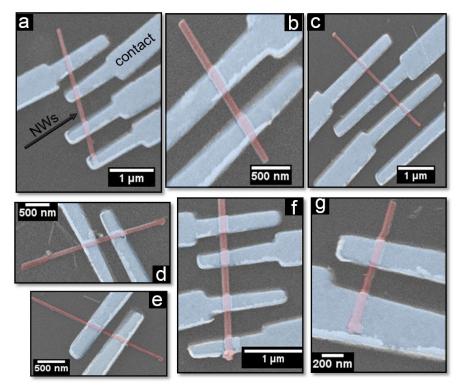

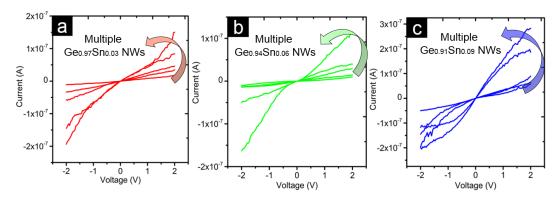

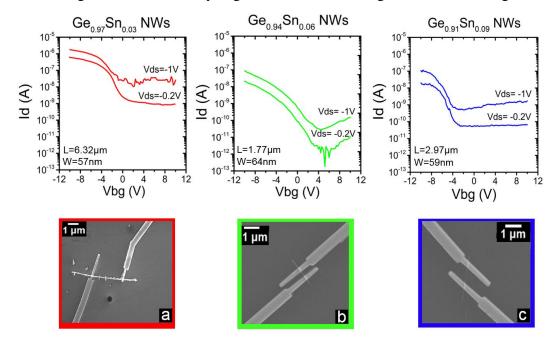

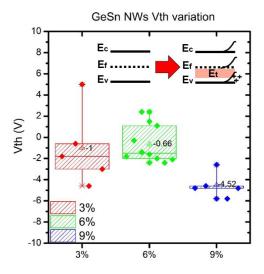

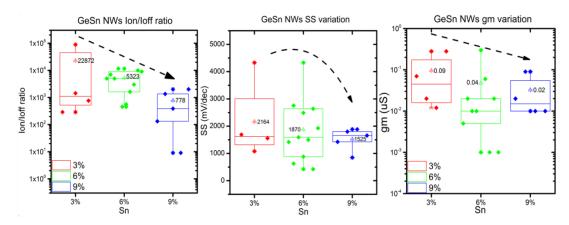

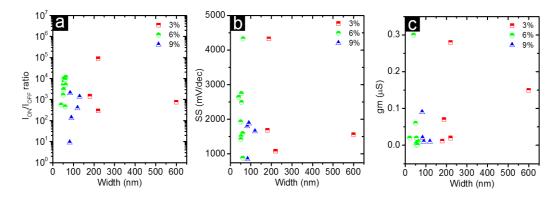

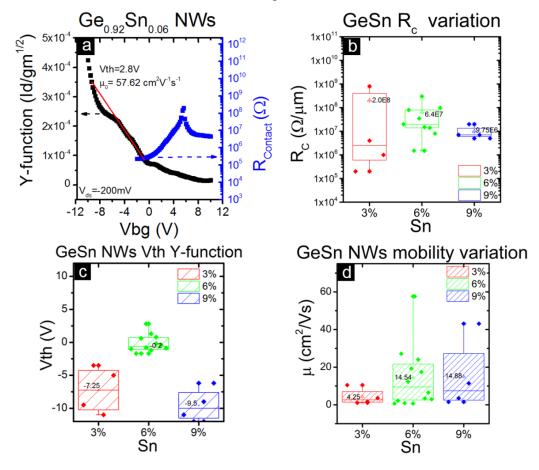

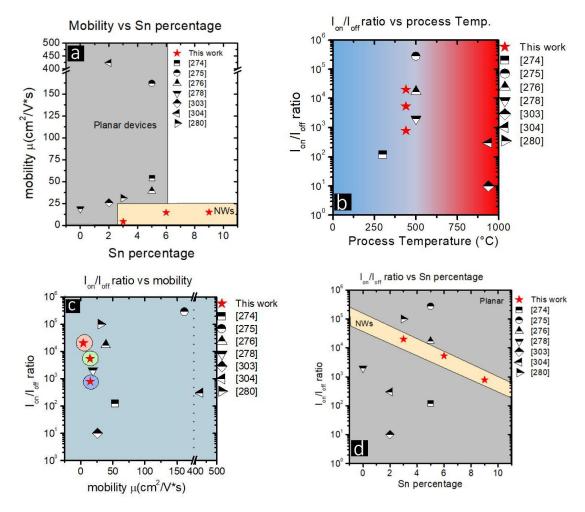

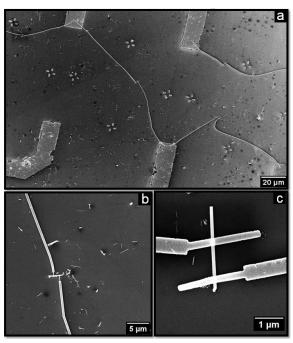

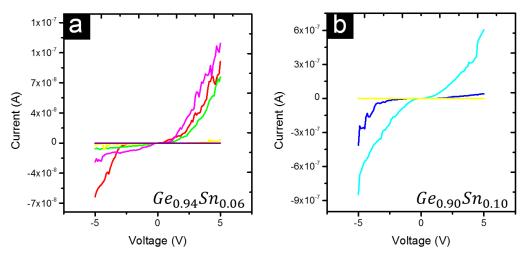

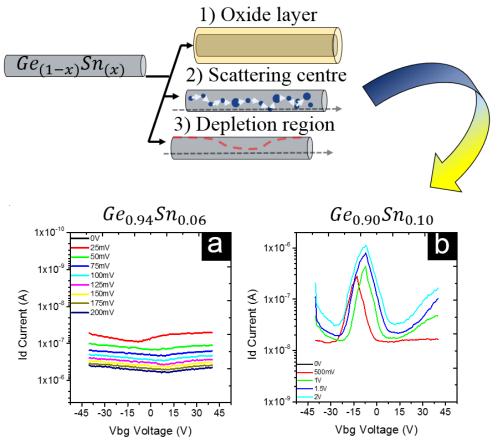

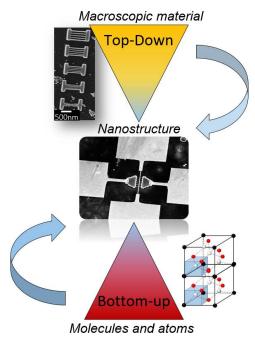

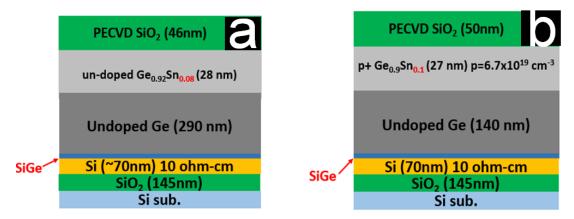

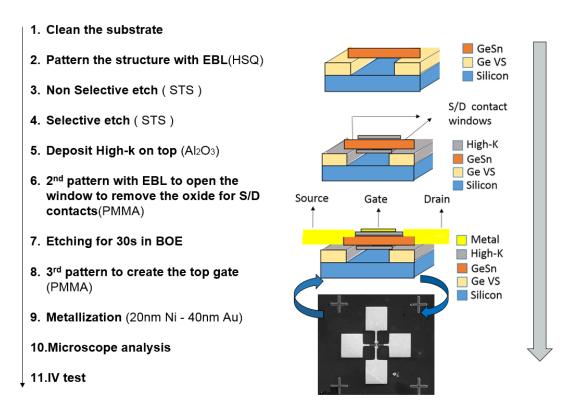

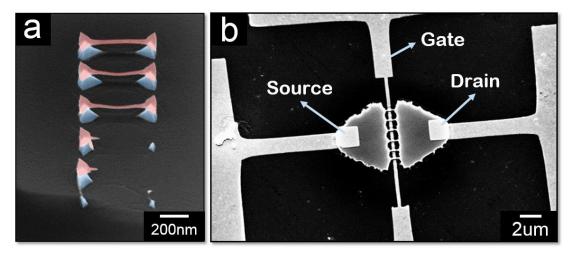

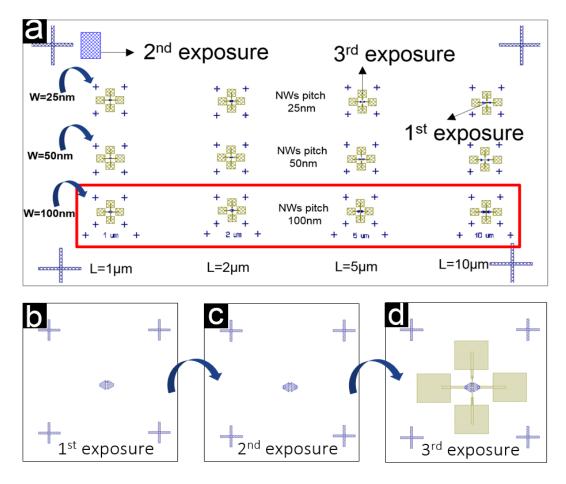

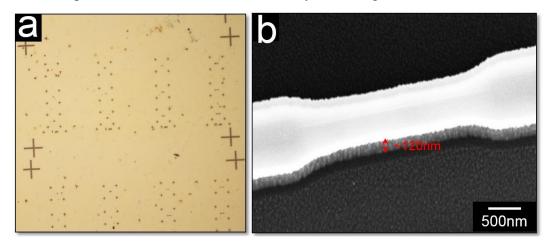

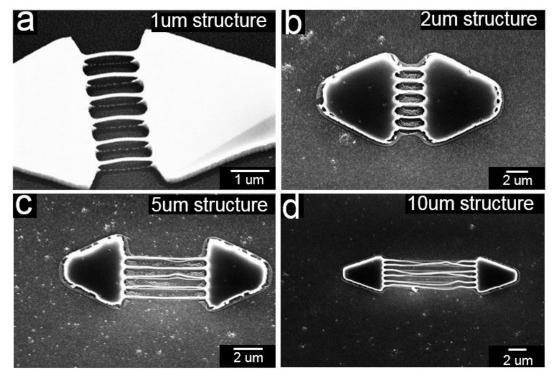

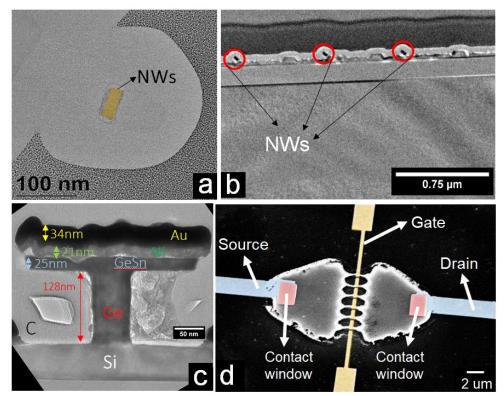

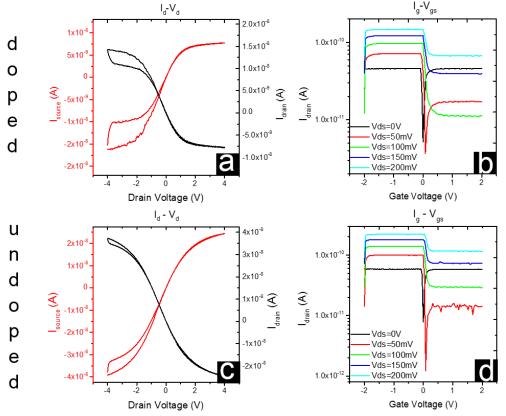

Secondly, the Ge<sub>1-x</sub>Sn<sub>x</sub> alloy has to be grown on Si or Ge substrate that both present higher lattice mismatch. Therefore the high difference among the materials lattice constant leads to large amounts of compressive strain and in some cases, to the formation of defects, such as threading dislocations, in the lattice due to partial relaxation [86]. Therefore to tackle the two aforementioned issues several techniques with different substrates, Ge [87] and In<sub>y</sub>Ga<sub>1-y</sub>P [88] have been investigated.