| Title                       | Influence of initial conditions on the fundamental periods of LFSR-dithered MASH digital delta-sigma modulators with constant inputs                                                                                                                                                                                                                                                             |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Authors                     | Mo, Hongjia;Kennedy, M. Peter                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Publication date            | 2016-05-12                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Original Citation           | Mo, H. and Kennedy, M. P. (2016) 'Influence of initial conditions on the fundamental periods of LFSR-dithered MASH digital deltasigma modulators with constant inputs', IEEE Transactions on Circuits and Systems II: Express Briefs, 64(4), pp. 372-376. doi: 10.1109/TCSII.2016.2567480                                                                                                        |  |  |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Link to publisher's version | https://ieeexplore.ieee.org/document/7469364/ - 10.1109/<br>TCSII.2016.2567480                                                                                                                                                                                                                                                                                                                   |  |  |

| Rights                      | © 2016, IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. |  |  |

| Download date               | 2025-07-08 06:01:49                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Item downloaded from        | https://hdl.handle.net/10468/11766                                                                                                                                                                                                                                                                                                                                                               |  |  |

# Influence of Initial Conditions on the Fundamental Periods of LFSR-Dithered MASH Digital Delta-Sigma Modulators with Constant Inputs

Hongjia Mo, Student Member, IEEE and Michael Peter Kennedy, Fellow, IEEE.

Abstract—A digital delta-sigma modulator (DDSM) with a constant input may produce a periodic output with a small fundamental period, resulting in strong tonal output behavior instead of the expected shaped white quantization noise. In practice, the problem is alleviated by dithering the DDSM. Pseudorandom dither generators based on linear feedback shift registers (LFSRs) are widely used to "break up" periodic cycles in DDSMs with constant inputs. Pseudorandom dither signals are themselves periodic and can lead to relatively short output sequences from dithered DDSMs. It is known that the fundamental period of the output signal depends not only on the input and initial condition of the DDSM but also on the initial state of the LFSR. This work shows that bad LFSR initial conditions can lead to ineffective dithering, producing short cycles and strong tonal behavior. Furthermore, it explains how to set the inital state of the DDSM, as a function of the initial state of the LFSR, in order to obtain a maximum length dithered output.

# I. INTRODUCTION

Digital delta-sigma modulators (DDSMs) are widely used in oversampled digital-to-analog converters and fractional-N frequency synthesizers [1]–[3]. In the synthesizer application, the input to the DDSM is typically constant.

A DDSM is a nonlinear finite state machine. When its input is held constant, it produces a periodic output. It has been proven that the fundamental period of the output depends on the input and the initial state of the DDSM [4]–[6].

For some constant inputs, the fundamental period may be very small, resulting in strong tonal behavior in the output spectrum. A number of ways have been suggested to increase the fundamental period. One popular (deterministic) solution is to set the initial state of the DDSM [6]. A more common (stochastic) alternative is to apply an additive dither signal [7].

Ideally the dither signal should be random. In practice, it is produced by a linear feedback shift register (LFSR) which is itself a finite state machine. The output of the LFSR is pseudorandom, meaning that it is periodic, albeit usually with a very large period.

We have shown previously that the output of a DDSM driven by a periodic input is itself periodic [8]. In particular, a MASH 1-1-1 with a modulus M and a constant input x—as well as additive LSB dither produced by a b-bit LFSR with

Rev. R1.rev1 of manuscript dated May 11, 2016.

This work has been funded in part by Science Foundation Ireland and Enterprise Ireland under grants 13/IA/1979 and CC-2009-05, respectively.

H. Mo and M.P. Kennedy are with the School of Engineering—Electrical and Electronic Engineering and Tyndall National Institute, University College Cork, Cork, Ireland (e-mail: hongjia.mo@tyndall.ie; peter.kennedy@ucc.ie).

fundamental period  $L_{sd}=(2^b-1)$ —has a fundamental period  $L_{\mbox{DDSM}}.$

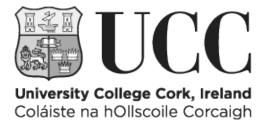

Qualitatively, the larger the value of  $L_{\rm DDSM}$ , the closer the DDSM's output spectrum should approximate shaped white noise. While one might be tempted to achieve this by making  $L_{sd}$  large, the downside of this approach is that it causes the shaped dither signal to dominate the noise performance at low frequencies. This is illustrated in Fig. 1(a), which simulates an 8-bit MASH 1-1 architecture that has been used to drive the DCO in an ADPLL [9].

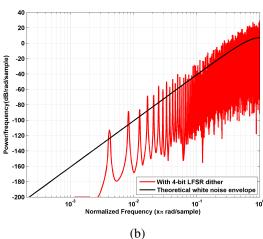

If  $L_{sd}$  is smaller, it may result in spurs due to feedthrough of the dither signal [10], [11]. Guaranteeing no feedthrough spurs imposes an upper bound on the value of  $L_{sd}$  [12]. This in turn puts a lower bound on the possible value of  $L_{\rm DDSM}$ , which could be as low as  $L_{sd}$ . Fig. 1(b) shows the case where b is small and  $L_{\rm DDSM}$  is large: dithering is effective; the low frequency noise is highpass filtered. Fig. 1(c) shows the case where b is small and  $L_{\rm DDSM}$  is also small; in this case, dithering is ineffective in the sense that the spectrum is tonal. The difference between Figs. 1(b) and (c) is only the initial state of the LFSR. This dependence on the initial state of the LFSR, and how to overcome the problem, is the focus of this manuscript.

We focus on MASH DDSMs comprising a cascade of first-order error feedback modulators. We show how to choose the initial state of the DDSM as a function of the initial state of the LFSR in order to maximize  $L_{\mbox{DDSM}}$  and present empirical formulae for the worst case value of  $L_{\mbox{DDSM}}$  in terms of  $L_{sd}$  when the necessary conditions are satisfied.

This paper is organized as follows. In Section II, we review the LFSR architecture and show spectra of an effectively dithered MASH DDSM [12]. In Sec. III, we consider a MASH 1-1-1 DDSM with additive first-order shaped LSB dither. We present general results for various modulator and dither filter orders in Sec. IV. These empirical results are based on extensive simulations; we hope that they will inspire other researchers to solve the problem analytically. We summarize our observations and hypotheses in Sec. V.

### II. DITHERED MASH DDSM

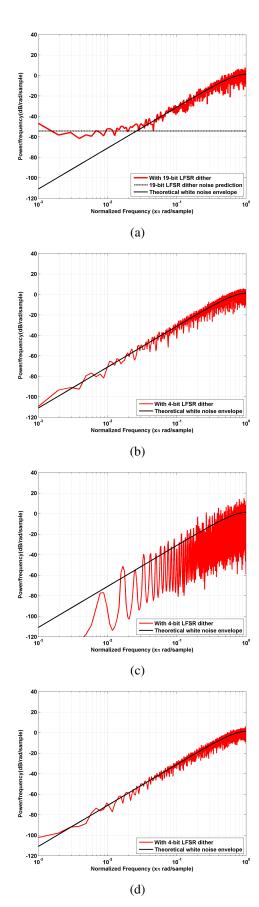

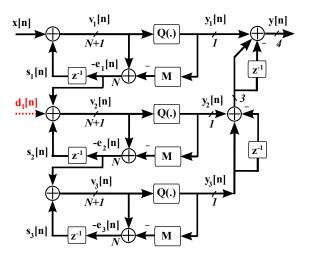

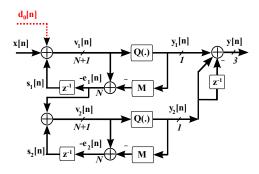

We consider in this work MASH DDSMs with additive LSB dither [7], [10], [12]. A block diagram of the architecture is shown in Fig. 2. The lth order DDSM comprises l first-order error feedback modulators (denoted EFM1) and an error cancellation network. The binary dither signal d[n] is filtered by a

Fig. 2. MASH DDSM with additive filtered dither

discrete-time filter with transfer function  $V(z) = (1 - z^{-1})^{l_d}$ . The dither generator is a so-called "internal feedback" LFSR.

To illustrate the problem we address in this work, let us consider a third-order MASH 1-1-1 DDSM with additive first-order shaped dither. This structure is often used in commercial fractional-N frequency synthesizers [13]. A commercial DDSM might have 24 bits per stage and a 20-bit LFSR. For illustrative purposes, the EFM1 stages in our example DDSM are 8 bits wide.

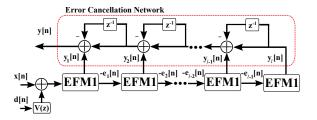

A simulated power spectrum is shown red in Fig. 3(a). The idealized spectral envelope, assuming white quantization noise, is defined by

$$S_3(f) = \frac{1}{12} \left( 2 \sin\left(\frac{\pi f}{f_s}\right) \right)^6. \tag{1}$$

This is shown black in Fig. 3.

The spectra in Figs. 3(a) and (b) are qualitatively different: one is smooth, while the other is comprised of discrete tones (spurs). The difference between Figs. 3(a) and (b) is that the LFSR has been initialized to 0100 in (a) and 1001 in (b).

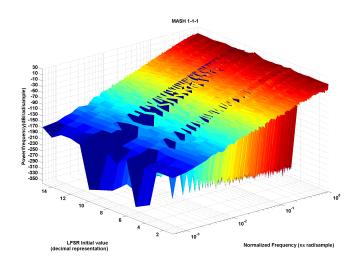

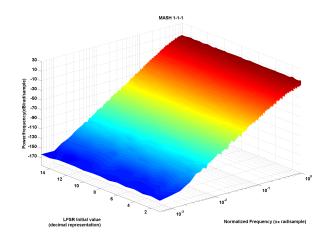

Fig. 4 presents brute force simulations of the power spectral density of our 8-bit third-order MASH DDSM with first-order shaped dither from a 4-bit LFSR for all possible initial states of the LFSR. The input is x=M/2 and the initial state of the DDSM is  $s_1[0]=s_2[0]=s_3[0]=0$ .

If the quantization noise were white, one would expect to see a smooth surface. Instead, for some "bad" LFSR initial conditions, the dithered MASH 1-1-1 DDSM has a small fundamental period, resulting in strong tonal behavior such as that seen in Fig. 3(b). This confirms that the cycle length of a dithered MASH 1-1-1 DDSM depends not only on the input and initial condition of the DDSM but *also* on the initial condition of the LFSR [14].

We previously proved how to set the initial condition of an *undithered* DDSM to ensure that the fundamental period is maximized, independently of the value of a constant input [6]. In this paper, we will show how to set the initial condition of the DDSM so that the fundamental period of the *dithered* DDSM is maximized, independently of *both* the value of the constant input and the initial state of the LFSR.

We will illustrate the method in detail for a third-order MASH with first-order shaped additive dither. A similar approach can be taken for other DDSM and LFSR architectures.

# III. EXAMPLE: MASH 1-1-1 DDSM WITH ADDITIVE FIRST-ORDER SHAPED LSB DITHER

The block diagram of the first-order dithered MASH 1-1-1 DDSM we consider is shown in Fig. 5. The LFSR-derived LSB

Fig. 3. Simulated power spectrum of an 8-bit MASH 1-1-1 DDSM with input x=M/2 and additive zeroth-order LSB dither produced by a 4-bit LFSR. The smooth black curve shows the expected behavior assuming that the quantization noise is white and the dither is effective. (a)  $s_1[0]=1, s_2[0]=s_3[0]=0$ , and  $s_d[0]=1001_2$  yields a "good" output with a fundamental period of  $512 \times L_{sd}$ . (b)  $s_1[0]=s_2[0]=s_3[0]=0$  and  $s_d[0]=1001_2$  yields a "bad" output with a fundamental period of  $32 \times L_{sd}$ .

dither is added to the second stage of the MASH, resulting in first-order shaping; this is equivalent to  $V(z)=(1-z^{-1})$  in Fig. 2.

The fundamental period of the output y of a MASH DDSM depends

on the cycle length of the last stage. If the third stage is started from state  $s_3[0]$  then, after  $L_{s3}$  iterations, we have that [14]:

$$\begin{split} s_3[L_{s3}] &= \left(s_3[0] + \sum_{k_3=0}^{L_{s3}-1} s_2[k_3]\right) \bmod M \\ &= \left(s_3[0] + L_{s3}s_2[0] + \frac{L_{s3}(L_{s3}-1)}{2} s_1[0] \right. \\ &+ \sum_{k_3=0}^{L_{s3}-1} \sum_{k_2=0}^{k_3-1} \sum_{k_1=0}^{k_2-1} x[k_1] + \sum_{k_3=0}^{L_{s3}-1} \sum_{k_2=0}^{k_3-1} d[k_2]\right) \bmod M, \end{split}$$

where x is the input,  $s_i$  is the state of stage i, and M is the modulus.

Fig. 4. Power spectral density of first-order shaped 4-bit dither dithered MASH 1-1-1 8-bit DDSM with x=M/2. Spurs (and troughs) associated with short cycle lengths correspond to "bad" LFSR initial conditions.

Fig. 5. Block diagram of a MASH 1-1-1 DDSM with first-order shaped dither.

Note that  $s_3$  is periodic with period  $L_{s3}$  if  $s_3[L_{s3}] = s_3[0]$ . For a constant input  $x[n] = x \forall n$ , we obtain [14]:

$$\left(L_{s3}s_{2}[0] + \frac{L_{s3}(L_{s3} - 1)}{2}s_{1}[0] + \frac{L_{s3}(L_{s3} - 1)(L_{s3} - 2)}{6}x + \sum_{k_{3}=0}^{L_{s3}-1} \sum_{k_{2}=0}^{k_{3}-1} d[k_{2}]\right) \bmod M = 0.$$

Note that the period of  $s_3$  depends explicitly on the input, the initial state  $s_1[0]$  of the first stage, and the initial state  $s_d[0]$  of the dither generator (which determines the double sum of the samples d[k]).

The LFSR has the property that  $\sum_{k=0}^{L_{sd}-1} d[k] = 2^{b-1}$ , where b is the number of bits in the LFSR, which is an even number. Recall that, in the undithered case, the maximum cycle length can be achieved by setting  $s_1[0]$  to an arbitrary odd number in the range of [1, M-1] [6].

#### A. Simulations

The fundamental period of an 8-bit MASH 1-1-1 DDSM with first-order dither produced by a 4-bit LFSR was determined by brute force simulation of all possible combinations of inputs (0 through 255) and initial states (1 through 15) of the LFSR. Two cases were considered: (a) the initial state of the DDSM was set to all zeroes, i.e.  $s_1[0] = s_2[0] = s_3[0]$ , and (b) the initial state of the first EFM1 in the DDSM was set to 1, with  $s_2[0] = s_3[0] = 0$ .

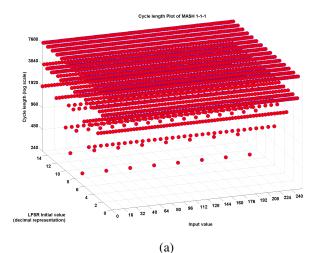

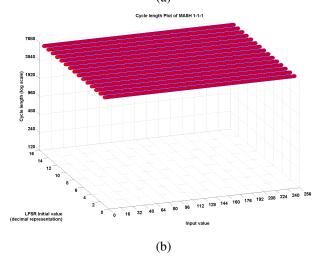

Consider Fig. 6, which shows the simulated fundamental period (cycle length) of the dithered DDSM as a function of the (constant) input value and the initial condition of the LFSR. Fig. 6(a) shows what happens when the DDSM is initialized to

Fig. 6. Simulated fundamental period of an 8-bit MASH DDSM with first-order dither from a 4-bit LFSR for all possible constant values x of the input. The initial states  $s_2[0]$  and  $s_3[0]=0$ . (a) With  $s_1[0]=0$ , both "bad" short and "good" long cycles can occur; (b) when  $s_1[0]=1$ , all initial states lead to maximum length cycles.

the zero state. In the worst case, the output period is as small as  $16 \times L_{sd}$ ; in the best case, it is  $2M \times L_{sd}$ . By contrast, setting  $s_1[0]$  to the opposite parity as the initial state of the LFSR always leads to maximum length cycles, as shown in Fig. 6(b).

# B. Output spectra

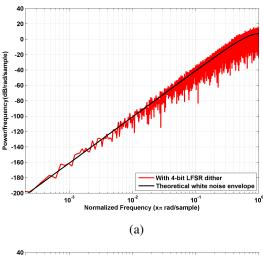

Fig. 7 shows the output spectra of our 8-bit third-order MASH 1-1-1 DDSM with first-order dither produced by a 4-bit LFSR, constant input x = M/2 and initial states  $s_2[0] = s_3[0] = 0$ .

By contrast with Fig. 4, in which  $s_1[0] = 0$ , the smooth spectra in Fig. 7, corresponding to maximum length cycles, result from setting  $s_1[0]$  to 1.

Fig. 7. Output spectra of a 8-bit third-order MASH DDSM with first-order dither produced by a 4-bit LFSR. The initial states are  $s_2[0]$  and  $s_3[0]=0$  and  $s_1[0]=1$ . All cycles are maximum length; all spectra are smooth.

# IV. GENERAL RESULTS

The observations in Sec. III also apply to higher order modulators and dither filters. Our empirical results are summarized in Tables I and II for MASH modulators (comprising cascaded first order stages) up to fifth order and filters  $(1-z^{-1})^{l_d}$  up to third order.

| Dither      | MASH    | Initial                      |  |

|-------------|---------|------------------------------|--|

| Order $l_d$ | Order l | Condition                    |  |

| No dither   | 2–5     | s <sub>1</sub> [0] odd [6]   |  |

| 0           | 2–5     | set $s_1[0]$ opposite parity |  |

|             |         | to initial state of the LFSR |  |

| 1           | 3–5     | $s_1[0]$ odd                 |  |

| 2           | 4–5     | $s_1[0]$ odd                 |  |

| 3           | 5       | $s_1[0]$ odd                 |  |

Referring to Table I, note that making  $s_1[0]$  odd, as already recommended for the undithered case [6], is sufficient to guarantee maximum length cycles for dither filters of order one or more. The problem of tonal behavior associated with short cycles arises mainly when zeroth-order dither is used. It can be alleviated by choosing the initial condition  $s_1[0]$  opposite to the parity of the initial state of the LFSR.

Figs. 1(b) and (c) show spectra of an 8-bit MASH 1-1 DDSM with additive zeroth-order LSB dither produced by a 4-bit LFSR, the block diagram of which is shown in Fig. 8.

Fig. 8. Block diagram of a MASH 1-1 DDSM with zeroth-order shaped dither.

A "bad" initial condition yields a fundamental period of  $16 \times L_{sd} = 240$  and a tonal spectrum, as shown in Fig. 1(b). By contrast, satisfying the criterion in Table I by setting  $s_1[0]$  opposite to the parity of the inital state of the "internal feedback" LFSR produces a significantly smoother spectrum which more closely approximates idealized shaped white quantization noise, as shown in Fig. 1(c). Finally, we show in Fig. 1(d) the case of  $s_1[0] = 0$  and an odd parity initial condition in the "internal feedback" LFSR.

Table II summarizes the maximum possible and guaranteed minimum cycle lengths when the conditions on  $s_1[0]$  specified in Table I are satisfied.

TABLE II WORST AND BEST CASE CYCLE LENGTHS  $L_{\mbox{DDSM}}$  for MASH DDSM with power-of-2 quantizer modulus M and dither period  $L_{sd}$  when the conditions in Table I are satisfied.

|             |           | Guaranteed          | Maximum            |

|-------------|-----------|---------------------|--------------------|

| Dither      | MASH      | Minimum             | Possible           |

| Order $l_d$ | Order $l$ | Cycle Length        | Cycle Length       |

| No dither   | 2         | M/2                 | 2M                 |

|             | 3         | 2M                  | 2M                 |

|             | 4         | 2M                  | 4M                 |

|             | 5         | 4M                  | 4M                 |

| 0           | 2         | $M/2 \times L_{sd}$ | $2M \times L_{sd}$ |

|             | 3         | $2M \times L_{sd}$  | $2M \times L_{sd}$ |

|             | 4         | $2M \times L_{sd}$  | $4M \times L_{sd}$ |

|             | 5         | $4M \times L_{sd}$  | $4M \times L_{sd}$ |

| 1           | 3         | $2M \times L_{sd}$  | $2M \times L_{sd}$ |

|             | 4         | $2M \times L_{sd}$  | $4M \times L_{sd}$ |

|             | 5         | $4M \times L_{sd}$  | $4M \times L_{sd}$ |

| 2           | 4         | $2M \times L_{sd}$  | $4M \times L_{sd}$ |

|             | 5         | $4M \times L_{sd}$  | $4M \times L_{sd}$ |

| 3           | 5         | $4M \times L_{sd}$  | $4M \times L_{sd}$ |

The maximum possible fundamental period of the output is either 2 or 4 times  $M \times L_{sd}$ , depending on the order of the modulator. When the corresponding initial condition for the "internal feedback" LFSR in Table I is satisfied, the minimum cycle length is guaranteed to be at least  $M/2 \times L_{sd}$ .

Note that a third-order modulator with zeroth- or first-order dither always produces maximum length sequences when the condition in Table I is satisfied. Furthermore, for dither orders greater than zero, the "make  $s_1[0]$  odd" recommendation is

the same as for the undithered case [6].

## V. CONCLUSION

A pseudorandom dither generator based on an "internal feedback" LFSR produces a periodic output. When this signal is used to dither a DDSM with a constant input, the overall system has a periodic output. The harmonic components of the output spectrum, the so-called spurious tones, are influenced by the length of the "internal feedback" LFSR's output sequence, the initial condition of the "internal feedback" LFSR, and the input, initial conditions and modulus of the DDSM.

The output spectrum can be made to approximate shaped white noise by maximizing the fundamental period of the dithered DDSM. We have shown by simulation that it is possible to control the output sequence length by initializing the DDSM appropriately. The required sets of initial conditions are defined in Table I for modulators of order up to five and dither filters up to third order. When the DDSM is started from the initial state specified in Table I, the guaranteed sequence length depends only on the DDSM's modulus M and the size of the "internal feedback" LFSR; it is independent of the value of the (constant) input.

#### REFERENCES

- T. A. D. Riley, M. A. Copeland, and T. A. Kwasniewski, "Delta-Sigma modulation in fractional-N frequency synthesis," *IEEE J. Solid-State Circuits*, vol. 28, no. 5, pp. 553–559, May 1993.

- [2] M. Kozak and I. Kale, Oversampled Delta-Sigma Modulators, Analysis, Applications and Novel Topologies. Boston: Kluwer Academic Publishers, 2003.

- [3] R. Schreier and G. C. Temes, Understanding Delta-Sigma Data Converters. New York: Wiley, 2005.

- [4] M. J. Borkowski, T. A. D. Riley, J. Hakkinen, and J. Kostamovaara, "A practical  $\Delta\Sigma$  modulator design method based on periodical behavior analysis," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 52, pp. 626–630, Oct. 2005.

- [5] K. Hosseini, M. P. Kennedy, and C. McCarthy, "Calculation of sequence lengths in mash 1-1-1 digital delta sigma modulators with a constant input," in *Research in Microelectronics and Electronics Conference*, 2007. PRIME 2007. Ph.D., July 2007, pp. 13–16.

- [6] K. Hosseini and M. P. Kennedy, Minimizing Spurious Tones in Digital Delta-Sigma Modulators. New York: Springer, 2011.

- [7] S. Pamarti and I. Galton, "LSB dithering in MASH delta-sigma D/A converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 4, pp. 779–790, April 2007.

- [8] M. Kennedy, B. Fitzgibbon, and K. Dobmeier, "Spurious tones in digital delta sigma modulators with pseudorandom dither," in *Circuits* and Systems (ISCAS), 2013 IEEE International Symposium on, Beijing, China, May 2013, pp. 2747–2750.

- [9] J. Zhuang, K. Waheed, and R. B. Staszewski, "Design of spur-free σδ frequency tuning interface for digitally controlled oscillators," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 62, no. 1, pp. 46–50, Jan 2015.

- [10] V. R. Gonzalez-Diaz, M. A. Garcia-Andrade, G. E. Flores-Verdad, and F. Maloberti, "Efficient dithering in MASH sigma-delta modulators for fractional frequency synthesizers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 9, pp. 2394–2403, Sep. 2010.

- [11] H. Mo and M. P. Kennedy, "Comments on efficient dithering in digital delta-sigma modulator," in *Proc. IEEE Int. Conf. Electron. Circuits Syst.*, Marseille, France, Dec. 2014, pp. 88–91.

- [12] —, "Effective (spur-free) dithering of digital delta-sigma modulators with pseudorandom dither," in *Proc. Eur. Conf. Circuit Theory Des.*, Aug. 2015, pp. 627–630.

- [13] ADF4155: Integer-N/Fractional-N PLL Synthesizer, Analog Devices. [Online]. Available: http://www.analog.com/media/en/ technical-documentation/data-sheets/ADF4155.pdf

- [14] M. P. Kennedy, H. Mo, and B. Fitzgibbon, "Spurious tones in digital delta-sigma modulators resulting from pseudorandom dither," *Journal of the Franklin Institute*, vol. 352, no. 8, pp. 3325–3344, August 2015.