| Title                | Average-case analysis of power consumption in embedded systems                                                               |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| Authors              | Zeinolabedini, Nasim                                                                                                         |

| Publication date     | 2015                                                                                                                         |

| Original Citation    | Zeinolabedini, N. 2015. Average-case analysis of power consumption in embedded systems. PhD Thesis, University College Cork. |

| Type of publication  | Doctoral thesis                                                                                                              |

| Rights               | © 2015. Nasim Zeinolabedini http://creativecommons.org/<br>licenses/by-nc-nd/3.0/                                            |

| Download date        | 2025-06-30 16:27:30                                                                                                          |

| Item downloaded from | https://hdl.handle.net/10468/3375                                                                                            |

## Average-Case Analysis of Power Consumption in Embedded Systems

## Nasim Zeinolabedini

# Thesis submitted for the degree of Doctor of Philosophy

#### NATIONAL UNIVERSITY OF IRELAND, CORK

# School of Engineering Department of Electrical and Electronic Engineering

August 2015

Head of Department: Prof Nabeel Riza

Supervisors: Dr Emanuel Popovici

Research supported by Science Foundation Ireland

## Contents

|          |      | of Figures                                                  | i        |

|----------|------|-------------------------------------------------------------|----------|

|          | List | of Tables in                                                |          |

|          | Ack  | nowledgements                                               | i        |

|          | Abs  | tract                                                       | i        |

| 1        | Intr | roduction                                                   | 1        |

|          | 1.1  |                                                             | 1        |

|          | 1.2  |                                                             | 3        |

|          | 1.3  |                                                             | 6        |

|          | 1.4  |                                                             | 8        |

| <b>2</b> | Pro  | cessor Power Estimation Techniques 10                       | )        |

|          | 2.1  | Methods Based on Program Execution Profile                  | 1        |

|          |      | 2.1.1 Instruction-Level Methods                             |          |

|          |      | 2.1.1.1 Data Independent Approaches                         |          |

|          |      | 2.1.1.2 Semi-Data Dependent Approaches                      |          |

|          |      | 2.1.1.3 Data Dependent Approaches                           |          |

|          |      | 2.1.2 Function-Level Methods                                |          |

|          |      | 2.1.2 Function-Level Methods                                |          |

|          | 2.2  |                                                             |          |

|          | 2.2  | Methods Based on Architectural Parameters                   |          |

|          | 2.3  | Methods Based on System-Level Models                        |          |

|          |      | 2.3.1 Kernel Based Approaches                               |          |

|          |      | 2.3.2 API Based Approaches                                  |          |

|          |      | 2.3.3 Other Approaches                                      |          |

|          | 2.4  | Performance Counter Based Methods                           |          |

|          | 2.5  | Thermal Profile Based Methods                               | 4        |

|          | 2.6  | Summary                                                     | 4        |

| 3        | Asy  | rnchronous Charge Sharing Logic (ACSL) 20                   | 3        |

|          | 3.1  | Background                                                  | 7        |

|          |      | 3.1.1 Asynchronous vs. Synchronous Logic                    | 7        |

|          |      | 3.1.2 Dynamic vs. Static Logic                              | 3        |

|          |      | 3.1.3 Adiabatic Dynamic Differential Logic                  | Э        |

|          | 3.2  | Asynchronous Charge Sharing Logic                           | 2        |

|          |      | 3.2.1 General Operation of ACSL                             |          |

|          |      | 3.2.2 ACSL Circuit Design                                   |          |

|          |      | 3.2.3 Latch-Less ACSL                                       |          |

|          |      | 3.2.4 Summary                                               |          |

| 4        | Imr  | blementation of 8051 Arithmetic Logic Unit (ALU) in ACSL 39 | <b>)</b> |

| •        | 4.1  | ACSL Design Flow                                            |          |

|          | 4.1  | 8051 ALU Operations                                         |          |

|          | 4.3  | Implementation of the ALU Operations in ACSL                |          |

|          | 4.0  | 4.3.1 Addition and Subtraction Operations                   |          |

|          |      | 1                                                           |          |

|          |      | 4.3.2 Multiplication Operation                              | J        |

|   |      | 4.3.3 Division Operation                                    |

|---|------|-------------------------------------------------------------|

|   |      | 4.3.4 Logic Operations                                      |

|   |      | 4.3.5 Shift Operations                                      |

|   |      | 4.3.6 Exchange Operation                                    |

|   |      | 4.3.7 Decimal Adjust Operation                              |

|   |      | 4.3.8 No Operation                                          |

|   | 4.4  | The ALU Structure                                           |

|   | 4.5  | Functional Verification of the ACSL ALU                     |

|   | 4.6  | Performance Analysis of the ACSL ALU                        |

|   | 4.7  | Summary                                                     |

| 5 | Pov  | ver Prediction Method for The 8051 ALU 64                   |

|   | 5.1  | Analysis of Power, Delay and Area for the 8051 ACSL ALU Op- |

|   |      | erations                                                    |

|   | 5.2  | Power Prediction Method                                     |

|   |      | 5.2.1 The 8051 ALU related Instructions                     |

|   |      | 5.2.2 Steps to Predict the ALU Power                        |

|   | 5.3  | Results and Analysis                                        |

|   | 5.4  | Summary                                                     |

| 6 | Stat | tic Average-Case Power Analysis of a Sorting Algorithm 81   |

|   | 6.1  | MOdular Quantitative Analysis (MOQA)                        |

|   | 6.2  | MOQA Average-Case Analysis for The Insertion Sort 84        |

|   |      | 6.2.1 Insertion Sort Algorithm                              |

|   |      | 6.2.2 MOQA Analysis                                         |

|   | 6.3  | SPARC LEON3 Processor                                       |

|   | 6.4  | Experimental Method                                         |

|   |      | 6.4.1 Random Number Generation                              |

|   |      | 6.4.2 Power Measurement Flow                                |

|   |      | 6.4.2.1 Compiling The Code                                  |

|   |      | 6.4.2.2 RTL-Level Simulation                                |

|   |      | 6.4.2.3 Synthesis                                           |

|   |      | 6.4.2.4 Timing Analysis                                     |

|   |      | 6.4.2.5 Gate-Level Simulation 96                            |

|   |      | 6.4.2.6 Power Analysis                                      |

|   |      | 6.4.3 Automation of The Flow                                |

|   | 6.5  | Processor Energy Model For the Insertion Sort Algorithm 99  |

|   | 6.6  | Results and Analysis                                        |

|   |      | 6.6.1 Energy Model Parameters                               |

|   |      | 6.6.2 Validation of The Energy Model                        |

|   | 6.7  | Summary                                                     |

| 7 | Cor  | iclusion 107                                                |

|   |      | 7.0.1 Future Work                                           |

## List of Figures

| 2.1        | The basic FLPA principle                                                                 | 17              |

|------------|------------------------------------------------------------------------------------------|-----------------|

| 3.1<br>3.2 | Synchronous Architecture versus Asynchronous Architecture Static Logic vs. Dynamic Logic | 28<br>29        |

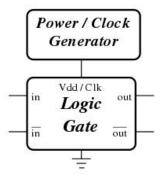

| 3.3        | Basic Blocks of Adiabatic Logic System                                                   | $\frac{20}{31}$ |

| 3.4        | Three Main Styles in Adiabatic Logic Family                                              | 32              |

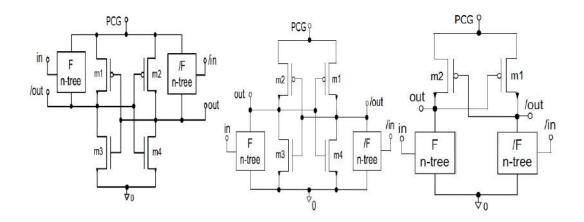

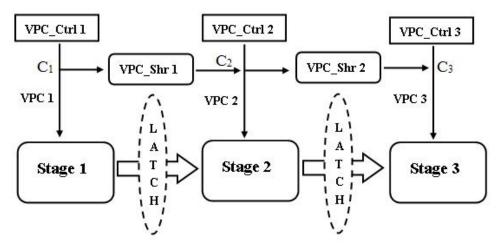

| 3.5        | General Architecture of ACSL                                                             | 33              |

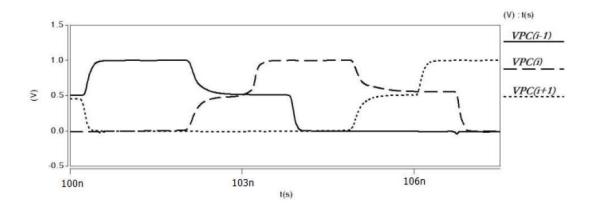

| 3.6        | VPC Signals Waveform                                                                     | 34              |

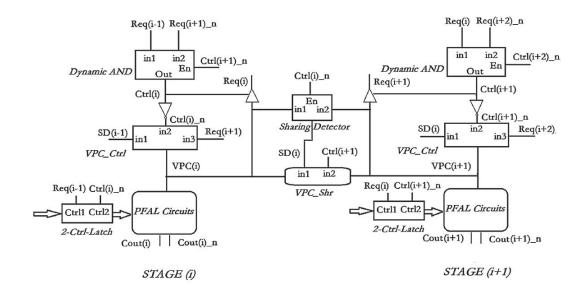

| 3.7        | 2-Stage Architecture of The ACSL circuit                                                 | 35              |

| 3.8        | ACSL Handshaking Protocol                                                                | 35              |

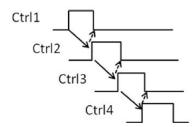

| 3.9        | Schematic for ACSL Circuit Basic Blocks                                                  | 36              |

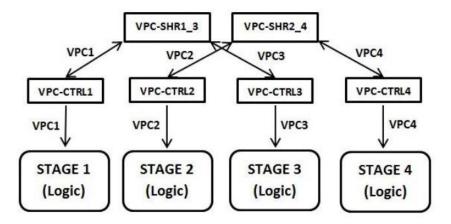

| 3.10       | Block Diagram of Latch-Less ACSL                                                         | 37              |

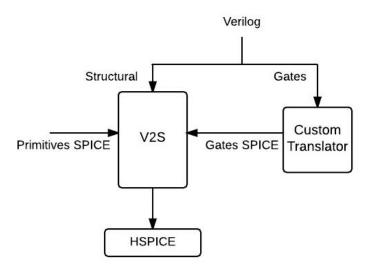

| 4.1        | ACSL Design Flow                                                                         | 42              |

| 4.1        | ACSL Besign Flow                                                                         | 46              |

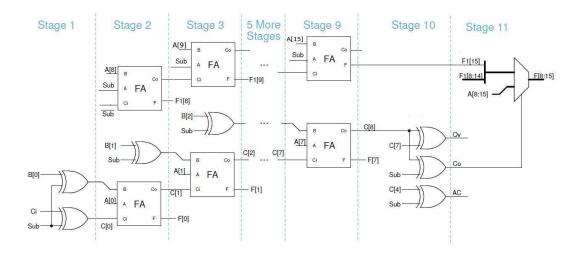

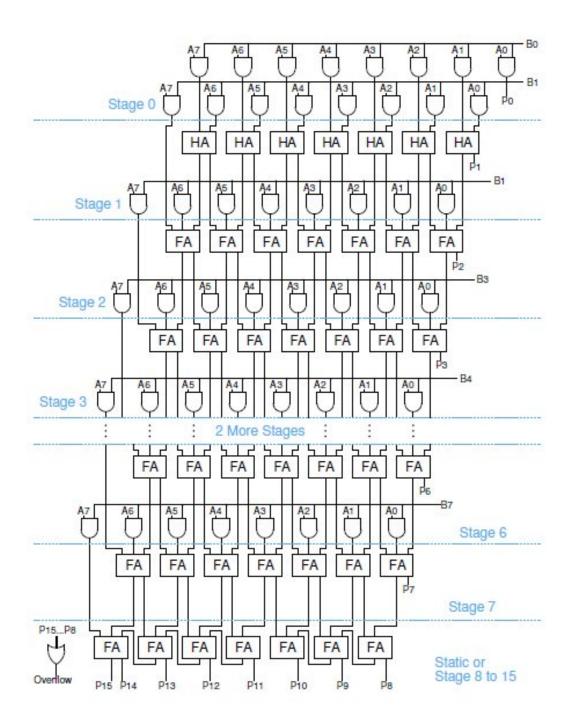

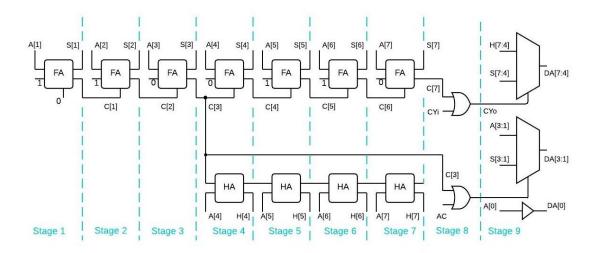

| 4.3        | ACSL 8051 Multiplier Circuit                                                             | 47              |

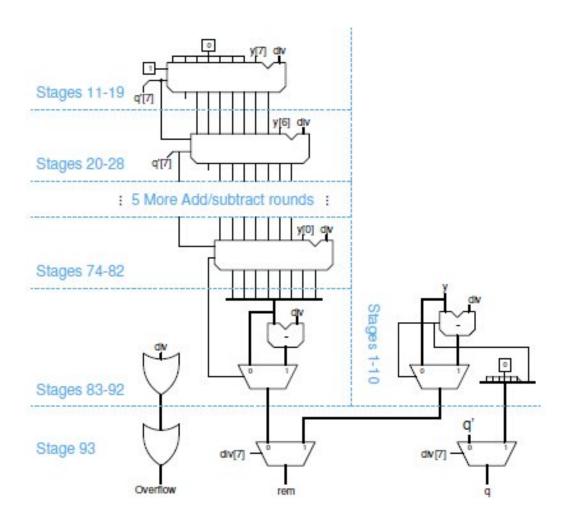

| 4.4        | ACSL 8051 Division Circuit                                                               | 49              |

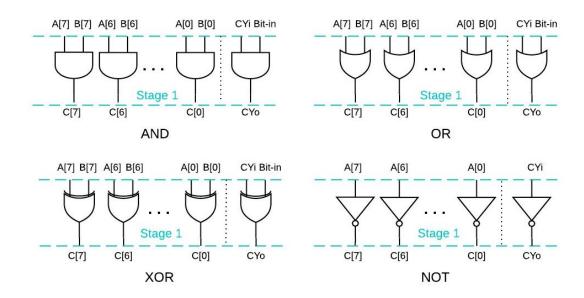

| 4.5        | ACSL 8051 Logic Operations Circuits                                                      | 51              |

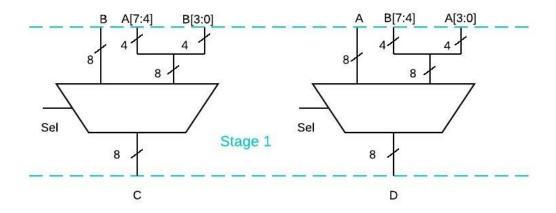

| 4.6        | ACSL 8051 Shift Operations Circuits                                                      | 52              |

| 4.7        | ACSL 8051 Exchange Operation Circuit                                                     | 53              |

| 4.8        | ACSL 8051 Decima Adjust Operation Circuit                                                | 55              |

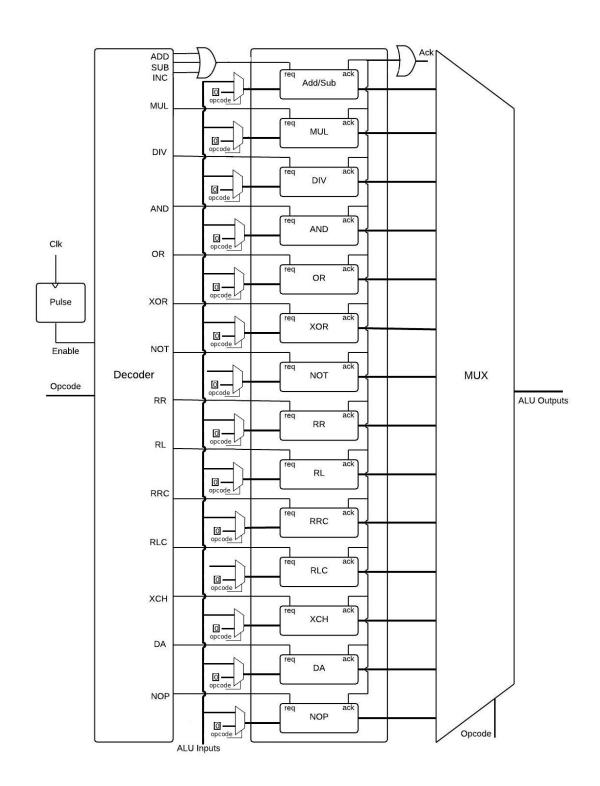

| 4.9        | The ALU Structure                                                                        | 57              |

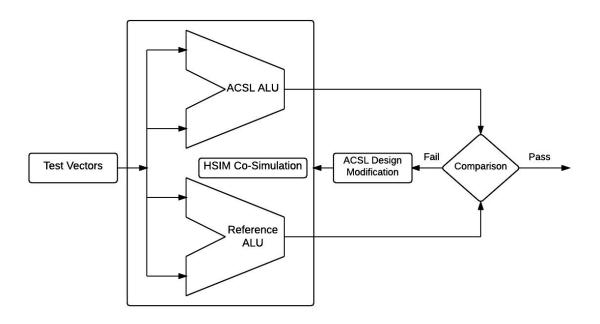

| 4.10       | Verification Method for ACSL 8051 ALU                                                    | 59              |

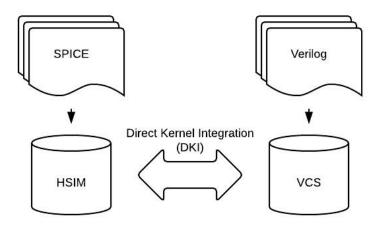

|            | HSIMplus Co-Simulation Environment                                                       | 60              |

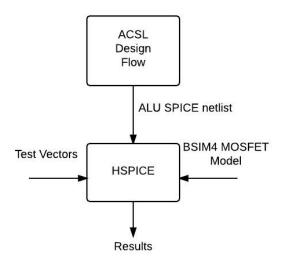

| 4.12       | HSPICE Simulation of the ACSL ALU                                                        | 60              |

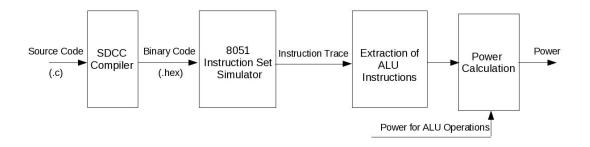

| 5.1        | Power Prediction Flow                                                                    | 72              |

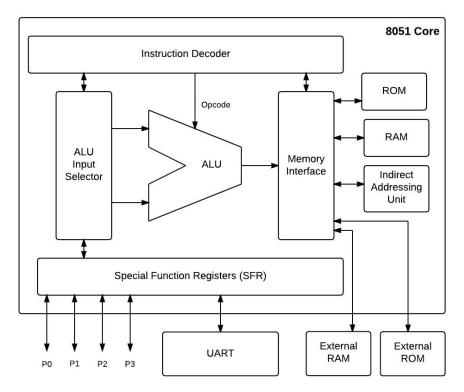

| 5.2        | The 8051 Microcontroller Structure                                                       | 76              |

| 0.2        |                                                                                          |                 |

| 6.1        | Insertion Sort Pseudocode                                                                | 85              |

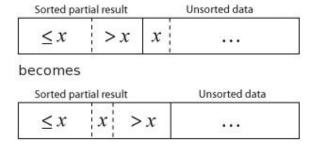

| 6.2        | Insertion of an element into the sorted part of the list                                 | 86              |

| 6.3        | MOQA Code for Insertion Sort                                                             | 86              |

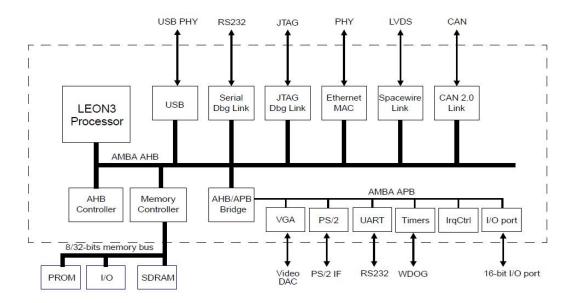

| 6.4        | Leon3 Design Platform                                                                    | 88              |

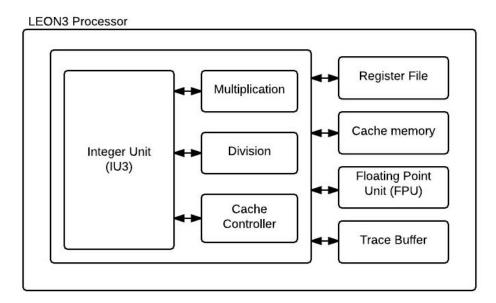

| 6.5        | LEON3 Processor Core Structure                                                           | 88              |

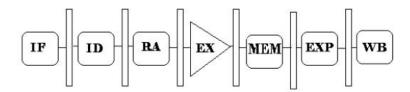

| 6.6        | Pipelined Stages of LEON3 Integer Unit                                                   | 89              |

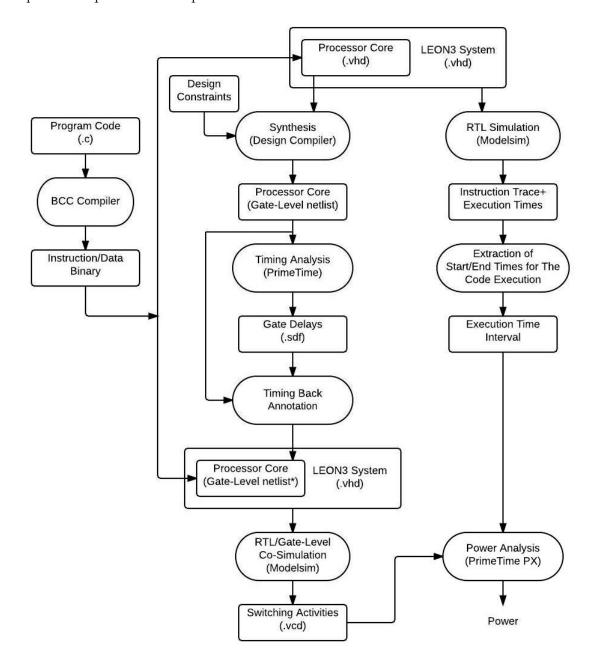

| 6.7        | Power Measurement Flow                                                                   | 92              |

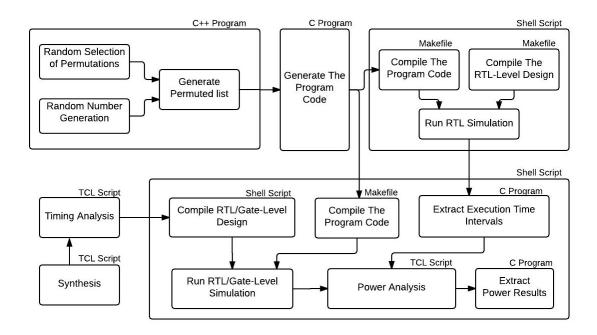

| 6.8        | Programs and Scripts to Automate the Power Measurement Flow                              | 98              |

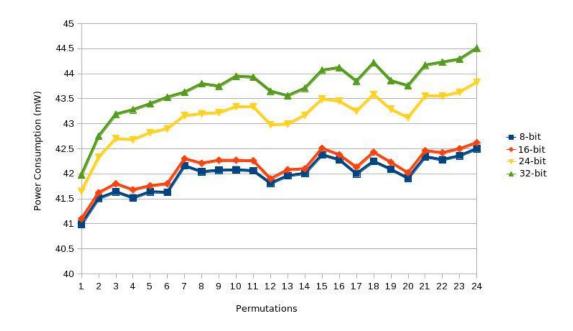

| 6.9        | LEON3 Processor Power Consumption For The Insertion Sort with                            | 100             |

|            | Input List Size $-4$                                                                     | 103             |

## List of Tables

| 4.1 | ACSL Gates and Primitive Modules                                    | 41  |

|-----|---------------------------------------------------------------------|-----|

| 4.2 | 8051 ALU Operations                                                 | 43  |

| 4.3 | Technology Parameters and Operating Conditions                      | 61  |

| 4.4 | Power, Delay and Area for ACSL 8051 ALU                             | 62  |

| 5.1 | Power of the ALU operations in operative and non-operative modes    | 66  |

| 5.2 | Power of Multiplication and Division Operations over 4 Clock Cycles | 67  |

| 5.3 | Delay and Area of the ACSL ALU operations                           | 67  |

| 5.4 | The 8051 Instructions Using ALU operations                          | 69  |

| 5.5 | Number of Times the ALU Operations Used by Benchmark Pro-           |     |

|     | grams                                                               | 75  |

| 5.6 | Predicted Power and Measured Power for The Benchmark Programs       | 75  |

| 5.7 | Speedup of The Power Prediction Method                              | 78  |

| 6.1 | Area and Delay for the LEON3 Processor Core                         | 96  |

| 6.2 | Partitioning of the code for the Insertion Sort Program             | 100 |

| 6.3 |                                                                     | 103 |

| 6.4 | Measured Energy and Estimated Energy for LEON3 Processor for        |     |

|     | the Insertion Sort Program                                          | 104 |

| 6.5 | Input Data and Processor Power Measurement Time for The In-         |     |

|     | sertion Sort Program                                                | 104 |

| 6.6 | Percentage of The Energy Consumption in Each Submodule of The       |     |

|     | LEON3 Processor                                                     | 105 |

| sim Zeinolabe |  | work and has not been or elsewhere. | n   |

|---------------|--|-------------------------------------|-----|

|               |  |                                     |     |

|               |  | <br>Nacion Zain alahadin            | -   |

|               |  | <br>Nasim Zeinolabedin              | -i  |

|               |  | Nasim Zeinolabedin                  | -i  |

|               |  | Nasim Zeinolabedin                  | -ii |

|               |  | Nasim Zeinolabedin                  | -i  |

## Acknowledgements

I would like to thank my supervisor, Dr. Emanuel Popovici, and all of my colleagues for having me as a part of the Embedded System Group through these years.

I am very thankful to my family for giving me the chance to continue my education away from them and away from my country. Specially I would like to thank my sister, Shamim, for being always encouraging and supportive to me. I am sorry for not being by her side during the difficulties she experienced through these years.

I would like also to thank all of my friends for their company, their advises and their supports that helped me to handle the hard situations.

Finally, I give my most sincere and heartfelt thanks to Prof. Nabeel Riza that completion of this work was never possible without his kind support.

#### Abstract

Power efficiency is one of the most important constraints in the design of embedded systems since such systems are generally driven by batteries with limited energy budget or restricted power supply. In every embedded system, there are one or more processor cores to run the software and interact with the other hardware components of the system. The power consumption of the processor core(s) has an important impact on the total power dissipated in the system. Hence, the processor power optimization is crucial in satisfying the power consumption constraints, and developing low-power embedded systems.

A key aspect of research in processor power optimization and management is "power estimation". Having a fast and accurate method for processor power estimation at design time helps the designer to explore a large space of design possibilities, to make the optimal choices for developing a power efficient processor. Likewise, understanding the processor power dissipation behaviour of a specific software/application is the key for choosing appropriate algorithms in order to write power efficient software.

Simulation-based methods for measuring the processor power achieve very high accuracy, but are available only late in the design process, and are often quite slow. Therefore, the need has arisen for faster, higher-level power prediction methods that allow the system designer to explore many alternatives for developing power-efficient hardware and software.

The aim of this thesis is to present fast and high-level power models for the prediction of processor power consumption. Power predictability in this work is achieved in two ways: first, using a design method to develop power predictable circuits; second, analysing the power of the functions in the code which repeat during execution, then building the power model based on average number of

repetitions.

In the first case, a design method called Asynchronous Charge Sharing Logic (ACSL) is used to implement the Arithmetic Logic Unit (ALU) for the 8051 microcontroller. The ACSL circuits are power predictable due to the independency of their power consumption to the input data. Based on this property, a fast prediction method is presented to estimate the power of ALU by analysing the software program, and extracting the number of ALU-related instructions. This method achieves less than 1% error in power estimation and more than 100 times speedup in comparison to conventional simulation-based methods.

In the second case, an average-case processor energy model is developed for the Insertion sort algorithm based on the number of comparisons that take place in the execution of the algorithm. The average number of comparisons is calculated using a high level methodology called MOdular Quantitative Analysis (MOQA). The parameters of the energy model are measured for the LEON3 processor core, but the model is general and can be used for any processor. The model has been validated through the power measurement experiments, and offers high accuracy and orders of magnitude speedup over the simulation-based method.

## Chapter 1

## Introduction

#### 1.1 Motivation

In the past decade, the use of embedded systems has grown in almost every aspect of our daily lives, including simple household appliances, transportation systems, and many communication, recreation and entertainment products. As a result, the design and implementation of efficient embedded software and hardware systems have gained utmost importance.

In the design of embedded systems, in addition to the need that the system has to produce the desired outputs for the given inputs, there are a number of other requirements which must be satisfied. These requirements could be imposed by user expectations or resource constraints. Some examples of these types of requirements are limits on the response time, memory space, battery capacity or channel bandwidth. These requirements are integral to the correct operation of the system. For instance, the response time of the electronic braking system in automobiles, or the power consumption of remote sensor nodes that scavenge their energy from the environment are critical for the correct functionality of these systems [1].

1. Introduction 1.1 Motivation

Power efficiency is one of the most important requirements in the design of embedded systems since such systems are generally driven by batteries with limited energy budget or have a restricted power supply. The power consumption becomes a more critical element in the design of highly integrated systems with a constant increase in the number of transistors per die, smaller chip area, and a higher operating frequency from older to newer technology nodes.

In every embedded system, there are one or more processor cores to run the software and interact with the other hardware components of the system. The power consumption of the processor core(s) has an important impact on the total power dissipated in the system. Hence, the processor power optimization is crucial in satisfying the power consumption constraints, and developing low-power embedded systems.

A key aspect of research in processor power optimization and management is "power estimation". Power estimation is important for several technical and commercial reasons. Having a fast and accurate method for processor power estimation at design time helps the designer to explore a large space of design possibilities to make the optimal choices for developing a power efficient processor. This can be done well before the actual processor is designed, fabricated and tested. Likewise, understanding the processor power dissipation behaviour of a specific software/application is key for choosing appropriate algorithms in order to write power efficient software [2]. From a commercial point of view, accurate power estimation at the design stage avoids costly re-design cycles, and leads to a product with better power consumption characteristics, and thus ensures higher profitability.

The simulation-based methods for measuring the processor power achieve very high accuracy, but they are available only late in the design process, and are often quite slow. Thus, it is difficult to exploit these methods in order to measure the 1. Introduction 1.2 Prior Work

power consumption of the processor for a large number of hardware or software design alternatives. For this reason, the need has arisen for the faster, higher-level power prediction methods that allow the system designer to explore different alternatives for development of power-efficient hardware and software.

The motivation of this work is taking a step toward building a framework to estimate the processor power consumption with high speed and accuracy early in the design flow of embedded systems. The work presented in this thesis is mostly focused on the estimation of the processor power for a given program code which can help software developers in writing power optimized embedded software code. In the rest of this chapter, the previous work in this area is outlined, and the contribution of the thesis is explained.

#### 1.2 Prior Work

The proposed methods in the area of processor power estimation can be classified into five categories: methods based on architectural simulation, system-level models, hardware performance counters, on-chip temperature profile and program execution profile. The first two categories (architectural-level models and system-level models) are the only methods available at the design stage which are useful to avoid re-design cycles and reduce the time to market in the processor design. Three other categories are available at runtime to estimate the power consumption of the software application. In the following, each of these categories are concisely described. In Chapter 2, more detail of the methods proposed in the literature in each category is presented.

Architectural-level models for power estimation are based on calculation of the load capacitance of each functional unit inside the processor using circuit simulation, analytic equations or empirical data. The activity factor of each functional

1. Introduction 1.2 Prior Work

unit during the execution of the test programs is generated through simulation, and is applied to the processor model to compute the power/energy consumption. The most famous work in this category is a power estimation framework called Wattch [3]. In this framework, the instruction cache, branch predictor, wakeup logic, register file, instruction window and the global clock are modeled at architectural-level, and the access counts for functional units are calculated using SimpleScalar [4] simulator. Other examples of architectural-level power estimation are the works presented in [5, 6, 7].

System-level models are communication-oriented models which describe a system of processing elements and the interactions between them. An important subset of such kind of models are Transaction Level Models (TLMs) [8]. TLMs model each message or event between processing blocks as a basic transaction. Most of the works with system-level models are presented to estimate power consumption for SystemC-based designs. In these works, the events relevant to power consumption are captured by modifying the SystemC kernel or using additional custom Application Program Interface (API). Some examples of this type of approach are presented in [9, 10, 11, 12, 13, 14].

Hardware performance counters are a set of special-purpose registers built into modern microprocessors to store statistics about the activity of different subsystems in the processor. These registers are typically readable by kernel-level or user-level software entities. For the processor power estimation, the performance counters that have a good correlation with the measured power are selected, and the power model is built as a function (F) of their sampled values. Different techniques are used in the literature for determining function F. Some of the approaches [15, 16] are purely mathematical and use regression based methods to solve the problem. Some approaches [17, 18, 19] use micro-benchmarks to generate events in a specific performance counter to determine the impact of

1. Introduction 1.2 Prior Work

each counter on the total power. There are some other approaches [20, 21, 22] which combine mathematical methods with micro-benchmark-based methods.

In on-chip temperature profile techniques, the power estimation is based on the link between the power consumption and the temperature of a die. The problem of finding the power consumption map of a die, given the temperature map is known as the Inverse Heat Conduction Probem (IHCP) [23]. To collect the temperature data either the InfraRed (IR) photograph of a die or embedded performance counter based thermal sensors can be used. Some approaches [24, 25, 26] in this category solve the IHCP problem assuming that temperature values are exact, and some other approaches [27, 28] consider some thermal noise.

The last category of approaches for processor power estimation is based on program execution profile. The work in this thesis also fits in this category. The approaches in this category can be divided into three groups: instruction-level methods, function-level methods and functional unit based methods.

In instruction-level methods, first the processor energy consumption of each instruction is characterized, and then the program code is analysed to get the instruction counts. The total energy consumption is obtained by multiplying the number of executed instructions of each type by their corresponding energy values. Some of the works [29, 30] based on instruction-level power characterization are data independent. It means that the power models are built without taking the impact of the instruction operands into account. Some other works [31, 32] in this area are semi-data dependent. In these works, some parameters like the inter-instruction effects, circuit state, pipeline stalls and cache misses are also considered in building the power model. The last set of works [33, 34] are data dependent which take the effect of program input data on the power consumption into account.

Function-level power estimation approaches are based on the processor power

characterization at the level of functions and library calls. In these approaches, the number of executions for the frequently invoked functions are counted, and total power is estimated by multiplying this number by the corresponding energy values. The examples of Function-level power estimation are presented in [35, 36, 37].

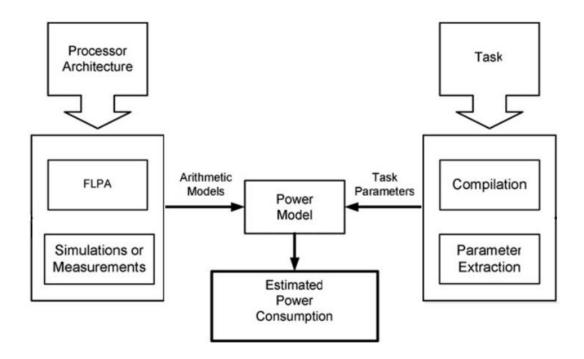

In functional unit based methods, the activity of the relevant functional units in the processor during the execution of the code is extracted as task parameters by analysing the program code. The total energy is computed by applying these task parameters to arithmetic models developed for the functional units. This method is also known as Functional Level Power Analysis (FLPA). In [38, 39, 40], this method is used for processor power estimation.

#### 1.3 Contributions of the Thesis

The work presented in this thesis is comprised of two main parts. The first part of the thesis can be classified as an instruction-level approach in the category of program execution profile based methods for processor power estimation. The second part represents a function-level approach in the same category.

In the first part of the thesis, a power estimation method is proposed which is based on a power predictable design methodology. This methodology that is called Asynchronous Charge Sharing Logic (ACSL) is a dynamic design style which offers two main properties. The first property is that it has lower power when compared with the other dynamic circuits, and the second property is that its power usage is almost constant and independent from the input patterns. This second property makes the ACSL circuits power predictable.

In this work, the Arithmetic Logic Unit (ALU) of 8051 microcontroller is implemented in ACSL. The power consumption of the arithmetic and logic operations

#### 1. Introduction

of this ALU has a very small variability, and is independent from the input data. This makes it possible to estimate the power usage for the ALU only by knowing the number and type of the operations it performs. The 8051 microcontroller is chosen in this work since it is a common microcontroller in embedded systems applications due to being widely available, and having many variants with different peripherals.

The power prediction method for the ACSL ALU is based on using an 8051 Instruction Set Simulator (ISS) to run the programs, and analysing their instruction trace to extract the number of ALU related instructions. This also provides the information on the number of times each ALU operation is used by the instructions during the execution of the program on the 8051. The average power of the ALU is then calculated by multiplying this number by the power consumption associated with each operation. This method can estimate the power with less than 1% error, and over 100 times faster than the gate-level simulation. Considering that the ALU is quite a small component in the processor core, when this method is applied to the entire core the speedup will be much higher.

The novelty of this work lies in the fact that in other methods the processor hardware is designed and implemented without considering the power predictability of the final circuit. The accuracy of these methods is affected by the fact that there is a high dependency of the power consumption on the input data profile which is often unknown at design time. As a result, it is hard to capture the behaviour of these circuits in terms of power to develop accurate power models.

In the second part of the thesis, an average-case processor energy model for the Insertion sort algorithm is proposed. This model is based on the average number of comparisons in the sorting algorithm that is calculated using MOdular Quantitative Analysis (MOQA).

MOQA is a high level methodology for static average-case analysis of the program

codes. This methodology enables the prediction of the average number of basic steps during the execution of a program which facilitates the estimation of the complexity measures such as average time or average power consumption.

The average-case analysis of the design metrics in embedded systems is important because it provides useful insight about the typical behaviour of the system, and complements the worst-case information to help the designer in taking better strategies in implementing an efficient system.

The energy model is built based on the average number of times that each part of the program code is repeated during the execution on the processor core, and the energy consumption of each part. In this work, the parameters of the energy model are determined for the LEON3 processor core, but the model is general and can be used for any processor.

This energy model enables the static estimation of the average-case processor energy consumption for the Insertion sort program for any given size of the input list. The accuracy and speedup of the model has been evaluated for the LEON3 processor through the power meaurement experiments. The model achieves high accuracy, and estimates the average energy in a fraction of a second in compare with gate-level simulation method which can take days or weeks to be run for a reasonable number of input samples.

#### 1.4 Structure of the Thesis

The structure of the chapters in this thesis is as follows: In Chapter 2, the previous work in processor power estimation area presented in the literature is reviewed. In Chapter 3, the design concept of the Asynchronous Charge Sharing Logic (ACSL) is introduced, and the structure and general operation of the ACSL circuits are described. In Chapter 4, the implementation of the 8051 Arithmetic

#### 1. Introduction

Logic Unit in ACSL is explained. In Chapter 5, the power prediction method for the 8051 ACSL ALU is presented. Finally in Chapter 6, the average-case processor energy model for the Insertion sort algorithm is described.

## Chapter 2

## Processor Power Estimation

## **Techniques**

In this chapter, different methods proposed in the literature for processor power estimation are explored. In general, every processor power estimation method is composed of two parts: model and input. The model is independent from the program code, and can be built in different levels of abstraction. The input is derived from the execution of the program code. The energy or power is estimated by applying the input to the model.

The power estimation methods described in this chapter are classified in five categories: methods based on program execution profile, architectural simulation, system-level models, hardware performance counters and on-chip temperature profile. Some of these methods work at design time, and are suitable for early stage architectural exploration. Some other methods work at runtime, and are useful for developing power efficient application software. The most prominent works presented in the literature in each category are explained.

The structure of this chapter is as follows: In Section 2.1, the methods based on program execution profile are described. In Section 2.2, the methods based

2. Processor Power Estimation TECHNIQUES

on architectural parameters are presented. In Section 2.3, the methods using system-level models are investigated. The performance counter based methods and thermal profile based methods are introduced in Section 2.4 and Section 2.5 respectively.

### Methods Based on Program Execution Pro-2.1file

Processor power estimation methods based on the program execution profile use a group of instructions as the basic atomic unit. The generic approach is to characterize the energy consumption of each instruction, and then analyse the code to get the instruction counts. It is also possible to do the characterization and profling at a higher level of granularity e.g. functions or traces. Some approaches predict the functional unit access counts by using program analysis or from instruction access counts. Subsequently, they compute the total energy by multiplying the access counts with pre-characterized energy values. In the following, each of these approaches are explained in more detail.

#### 2.1.1Instruction-Level Methods

All instruction-level approaches have a similar structure. In the first phase of these approaches, a profling run performs which executes different pieces of code repeatedly, and measures their energy usage. This allows the estimation of the energy associated with the set of instructions. In the second phase, some counters are embedded in the software that gives the execution frequency of each basic block. In the final phase, the total energy consumption is obtained by multiplying the number of executed instructions of each type by their corresponding energy

2. Processor Power Estimation Techniques

values. The estimated energy is divided by the execution time to yield the average

power.

2.1.1.1 Data Independent Approaches

In [29], a tool called Jouletrack is proposed to estimate the processor power at

the basic block/instruction level. This tool also calculates the processor leakage

power. In [41] a similar approach is taken but the leakage power is not modeled

explicitly. Their model considers all sources of power that cannot be classified as

dynamic power as a lumped constant.

In [42], the instruction-level profiling method is extended to VLIW processors.

These processors execute a group of instructions as a bundle, therefore, the pro-

cessor power is characterized at the level of each bundle of instructions. In

this way, the power consumed by an instruction depends on three factors: op-

code/operands of the instruction, the pipeline/circuit state, and the other instruc-

tions in the bundle. In [43], a simpler approach is taken for VLIW processors. In

this approach, the instruction trace is passed to an architectural power simulator

which is calibrated with RTL models.

In [30], a very low level method for modeling the timing and power of C programs

is proposed. In the proposed method, every statement in the C language is

broken to a set of micro-instructions which resembles a very primitive RISC

ISA. The power consumption is characterized for each such micro-instruction.

Subsequently, the software counters are embedded in a block of C statements for

each high level construct such as a switch case or a loop statement. The total

power is estimated based on the access counts.

## 2. Processor Power Estimation

#### 2.1.1.2Semi-Data Dependent Approaches

For the first time, a systematic approach for the estimation of the processor power during the execution of the instructions, with accounting for the interinstruction effects, was proposed in [32, 44, 31]. In these works, three types of inter-instruction effects are considered: pipeline stalls, change in circuit state and cache misses. The average number of switching bits for every consecutive pair of instructions are measured through the extensive simulations. The other effects are modeled by adding a constant to the total instruction power/energy. Considering all the above parameters, an instruction-level power model is presented to estimate the total energy for the processor  $(E_P)$  during the execution of a given program (P).

$$E_P = \sum_{i} (B_i * N_i) + \sum_{i,j} (O_{i,j} * N_{i,j}) + \sum_{k} E_k$$

(2.1)

where for each instruction i,  $B_i$  is the base cost, and  $N_i$  is the number of times it is executed. For each pair of consecutive instructions (i, j),  $O_{i,j}$  is the circuit state overhead, and  $N_{i,j}$  is the number of times the pair is executed.  $E_k$  is the energy contribution of the other inter-instruction effects, k (stalls and cache misses), that occures during the execution of the program.

In [45], this energy model is slightly simplified by using a constant power dissipation per instruction. This includes the effect of some of the inter-instruction factors. In [46], the impact of instructions inter-dependency on energy is accounted for based on characterizing the energy for pairs of instructions, and building a fine-grain 2-instruction-based model.

#### 2.1.1.3**Data Dependent Approaches**

In [33], the work of [31] has been extended by introducing a new instruction model able to consider the influence of the operands distribution on the processor power consumption. This model tries to relate the instruction power usage to the internal switching activity induced by operands. The power model in this work (given in Equation 2.2) is developed for the execution unit (EX+MEM stage) which is the main source of the power consumption in the processor, but it is extensible to the entire microprocessor.

$$Power = K_1 n_1 + K_2 n_2 + \dots + K_n n_n + K_0 + C_{ij}$$

(2.2)

In this model, coefficients  $K_i$  and variables  $n_i$  are respectively the weights and the number of transitions of the activity indices. Activity indices are the elements inside the processor that have a strong impact on the power consumption. The activity indices used in this work are the data write bus, address bus, and ALU bus.  $K_i$  and  $n_i$  parameters represent the average effect of the operands on the power, and are determined using uniformly distributed operands.  $K_0$  is the power cost for null switching activity on activity indices. It is the minimum cost for the particular instruction.  $C_{ij}$  is the changing-instruction cost between instructions i and j. That is a fixed cost due to the changing in the datapath configuration because of changing instruction.  $C_{ij}$  must be added to j instruction when it is preceded by i instruction.

In [34], an automated method is proposed for characterizing the energy usage of the instructions. In this work, the energy per cycle is decomposed into four parts: instruction-dependent energy dissipation, data-dependent energy dissipation, energy dissipation of the cache system and the dissipation of all external components including the bus system, memories, and peripherals. Since a complete character-

Profile

2. PROCESSOR POWER ESTIMATION TECHNIQUES

ization of the whole range of values of the operands is only theoretically possible, the data-dependent energy consumption is modeled in this work by means of linear regression.

In [47], a multi-granularity power model is proposed at functional, architectural and cycle-accurate micro-architectural stages of the design flow. These models offer a designer the flexibility to trade off estimation accuracy with estimation/simulation effort. A 3-D power contribution LUT is created that holds the power dissipation for each instruction, at each pipeline stage, for every functional unit in the processor. For improved accuracy, a set of three such 3-D LUTs is created, corresponding to average power, minimum power and maximum power depending on the operands values.

#### 2.1.2 Function-Level Methods

Function-level power estimation approaches are based on the processor power characterization at the level of functions and library calls. In these approaches, number of executions for the frequently invoked functions are counted by putting software counters at their entry point.

In [35, 48], a "power data bank" is built which stores the power information of the built-in library functions and basic instructions. In this work, the machine code is decomposed into library functions and user-defined functions. Then program profiling/tracing tools are used to get the execution information of the target software. Next, the total energy consumption and execution time is evaluated based on the "power data bank", and their ratio is taken as the average power.

In [36], two kinds of macro-modeling techniques for high-level energy estimation for software functions are proposed: Complexity-based macro-modeling and profiling-based macro-modeling. Both of the techniques are based on linear regression models. Complexity-based macro-modeling uses the algorithmic complexity of the functions to determine the macro-model template. For example, for an algorithm which has an average-case complexity of  $O(n^2)$ , the energy macromodel is:

$$E = c_1 + c_2 n + c_3 n^2 (2.3)$$

where n is the input size. The regression analysis is used along with low-level software power measurements to obtain the unknown coefficients  $c_i$ s.

In profiling-based macro-modeling, internal profiling statistics for the functions are used as parameters in the energy macro-models. Several variants of profiling-based macro-modeling is proposed, starting from simple basic-block profiling, to different lengths of basic-block correlation profiling and Ball-Larus path [49] correlation profiling.

[37] presents a systematic automated methodology for macro-model generation for frequently used functions/libraries. This work is based on the observation that large embedded software programs are rarely written from scratch, and a large fraction of the execution time is due to the reused software components (including embedded-operating systems, middleware, run-time libraries, domain-specific algorithm libraries, etc.). The energy consumption macro-models for these functions/libraries is generated by determining the right set of parameters, collecting data through simulation, and building the models using symbolic regression.

#### 2.1.3 Functional Unit Based Methods

In this type of approach, the activity of the relevant functional units in the processor (e.g. fetch unit, processing unit, clock network, internal memory and others) during the execution of the code is extracted as task parameters by analysing

the program code. The total energy is computed by applying these task parameters to arithmetic models developed for the functional units. This method is also known as Functional Level Power Analysis (FLPA). Figure 2.1 depicts the principal of this approach.

In the work presented in [50, 38, 51, 52], a tool called SoftExplorer is developed to perform power and energy estimation of generic C programs for DSP applications at both assembly level and C level. This work is based on three models: a processor model, an algorithm model and a compiler model. To perform estimation from the assembly code, only the two former models are needed. The model for the processor represents the way the processor's power consumption varies with its activity. The model for the algorithm links the algorithm with the activity it induces in the processor. To perform estimation at the algorithmic level (C level), a model for the compiler is also needed to take the effect of compiler behavior on the assembly code into account.

Figure 2.1: The basic FLPA principle

2. Processor Power Estimation Techniques

The processor model is built by identifying the functional units, and characterizing the energy consumption of each unit through the physical measurements. The algorithm model extracts the values of a few parameters from the code. These values are injected in the processor model to estimate the power consumption. The compiler model represents the behavior of the compiler, and how it will allow the algorithm to use the processor's resources.

Two sets of parameters are defined in this work: architectural and algorithmic parameters. The architectural parameter values depend on the processor configuration settled by the designer. This includes: clock frequency (F), memory mode (MM), data mapping (DM) and data width (W) during Direct Memory Access (DMA). The algorithmic parameters depend on the code execution, and represent the activity rate of the functional units and their interactions. Five algorithmic parameters are identified: fetch rate  $(\alpha)$ , execution rate  $(\beta)$ , cache miss rate  $(\gamma)$ , activity rate between the data memory controller and the DMA  $(\varepsilon)$  and Pipeline Stall Rate (PSR).

In [39, 53], an Energy-Aware Compilation (EAC) framework is presented that estimates and optimizes energy consumption of a given code, taking as input the energy/performance constraints, architectural and technological parameters and energy models. The energy consumption in this work has been modeled for datapath, clock network, buses, caches, and main memory. Some of the application-dependent parameters extracted from the code using the compiler are: data-path accesses, number of execution cycles, bus transactions, cache misses and memory transactions.

In [54], the power consumption of the processor functional blocks has been modeled in terms of parameterized arithmetic model functions. A parser which allows to analyze automatically the assembler codes has been implemented. This parser yields the input parameters of the arithmetic functions, e.g. the achieved degree

of parallelism or the kind and number of memory accesses.

In [40], a hybrid method for processor power estimation is presented which combines FLPA and instruction-level modeling approaches. In this work, an instruction dependent part is added to the FLPA in order to achieve high estimation accuracy.

# 2.2 Methods Based on Architectural Parameters

The generic approach for power estimation at architectural-level consists of the following steps: First, the load capacitance for each functional unit in the processor is calculated using either circuit simulation, analytic equations or empirical data. Next, the functional unit activity factor  $(\alpha)$  is generated through simulation. Finally, the total power is computed using Equation 2.4.

$$P = \alpha C V^2 f \tag{2.4}$$

In [3], a framework called Wattch is presented for architectural-level power analysis and optimization. In this framework different blocks are classified by their structure and functionality. A suit of parameterized power models for different hardware structures and on per-cycle resource usage counts is generated through cycle-level simulation. Some of these hardware structures include instruction cache, branch predictor, wakeup logic, register file, instruction window and the global clock. Wattch calculates the access counts for functional units using SimpleScalar simulator.

In [7], a new power, area, and timing modeling framework called McPAT (Multicore Power, Area, and Timing) is introduced which advances the state of the art in several directions in compared to Wattch. First, McPAT enables architects to use new metrics combining performance with both power and area such as energy-delay-area $^2$  product  $(EDA^2P)$  and energy-delay-area product (EDAP), which are useful to quantify the cost of new architectural ideas. Second, McPAT models more than just dynamic power, which is critical in deep-submicron technologies since static power has become comparable to dynamic power. All three types of power dissipation (dynamic, static, and short-circuit power) are modeled to give a complete view of the power envelope of multicore processors. Third, McPAT provides a complete, integrated solution for multithreaded and multicore/manycore processor power. Fourth, McPAT handles technologies that can no longer be modeled by the linear scaling assumptions used by Wattch.

In [55, 6], an architecture-level power estimation framework called SimplePower is presented which also takes the impact of input values on power consumption into account in compare with previously mentioned architecture-level models that only consider the number of accesses to the functional units.

## 2.3 Methods Based on System-Level Models

System-level models are communication-oriented models which describe a system of processing elements and the interactions between them. An important subset of such kind of models are Transaction Level Models (TLMs) [8]. TLMs model each message or event between processing blocks as a basic transaction. SystemC [56] is one of the most common TLM-based languages for high-level modeling which contains a basic event-driven simulation engine (kernel), and provides an interface for modeling system-level designs.

Most of the works with system-level models are presented to estimate power consumption for SystemC-based designs. The first set of approaches modify the SystemC kernel. These approaches are more generic and user-friendly, but they are not very flexible. The second set of approaches use additional custom Application Program Interfaces (APIs) to capture events relevant to power consumption. These approaches make no modification to the kernel.

#### 2.3.1 Kernel Based Approaches

In [11, 10], a framework is presented for the estimation of area, power and delay characteristics of hardware systems modeled at the Register-Transfer Level (RTL) using the SystemC modeling language. The framework also allows for dynamic power profiling and analysis based on the state of the modeled circuit. In this work, SystemC kernel is modified to calculate the number of 0-to-1 transitions at input and output ports of each component. The power consumption is then calculated using the number of input and output transitions and the type of the component.

[12] introduces a modeling and simulation technique that extends TLM method and modifies the SystemC kernel to support multi-accuracy models and power estimation. This allows the designer to trade off between simulation accuracy and speed at runtime. Another work in this area is presented in [57] for designs that have voltage scaling. [58] propose a tool called PowerSim on the same line. PowerSC [59] is a commercial tool that supports power estimation for SystemC, and PowerKernel [60] is one of the prominent open source tools in this domain.

### 2.3.2 API Based Approaches

In [13], a high-level power estimation methodology based on SystemC and Aspect Oriented Programming (AOP) is proposed. AspectC++ [61] is used to define special power-aware aspects. These aspects can be viewed as configuration files to

link the power aware APIs and SystemC functionality model. This methodology supports multi-macro-models and multi-accuracy power estimation.

In [62, 14], a VHDL to SystemC translator is described which can insert power simulation routines in the SystemC code. In contrast to previous approaches, the API calls in this work do not need input values, and estimate the average number of transitions per operation using the stochastic methods. For this reason, they are significantly faster.

#### 2.3.3 Other Approaches

In [63, 64, 65, 66], a system-level methodology for energy and performance estimation of System-on-Chip (SOC) architectures is proposed. This methodology operates at a very high abstraction level, namely the functional untimed level. For this reason it has been called Funtime. Funtime approach achieves more speed in compare to TLM methods since it needs no architectural-level simulation, and all information is inferred from functional level.

Funtime consists of three layers. The bottom layer relies on building a library of IP energy and performance models, where each IP's functionality is precharacterized through gate-level simulation. At the intermediate layer, applications are run and profiled on a development host (a common PC). This allows to create a trace of the executed source code, which is then mapped to the assembly code of the target architecture. Once the target trace is inferred, energy and performance figures can be extracted by using the IP models from the bottom layer. The top layer is a refinement layer that accounts for the presence of caches and for the fact that multiple applications normally run concurrently, share the same resources and are controlled by an operating system. Statistical models are built to account for the impact of each of these components.

#### 2.4 Performance Counter Based Methods

Hardware performance counters are a set of special-purpose registers built into modern microprocessors to store statistics about the activity of different subsystems in the processor. These registers are typically readable by kernel-level or user-level software entities.

Assuming that vector V represents the sampled values of performance counters, the total power can be computed using Equation 2.5.

$$P = F(V) = VW + P_{idle} \tag{2.5}$$

In this equation, the power (P) is a function (F) of the sampled performance counter values. W is a vector of weights, where  $W_i$  represents the weight associated with  $i^{th}$  performance counter.  $P_{idle}$  represents the static power.

Three different approaches are proposed in the literature for determining function F. The first set of approaches are purely mathematical. They view the problem as an optimization problem, and try to find a least squares based estimate. The works presented in [15, 67, 68] are in this category. In the second set of approaches, the  $W_i$  coefficients are determined by measuring the total power dissipated by a micro-benchmark that exclusively generates events for the  $i^{th}$  performance counter. The examples of using this approach is presented in [17, 18, 19]. The third approach combines purely mathematical approaches with with micro-benchmark based approaches. In this type of approach, additional constraints are enforced in the optimization process by taking inputs from micro-benchmark based methods or data from architectural simulators. [20, 21, 22] are in this group.

#### 2.5 Thermal Profile Based Methods

In this type of method, the power estimation is based on the link between the power consumption and the temperature of a die. The problem of finding the power consumption map of a die, given the temperature map is known as the Inverse Heat Conduction Probem (IHCP) [23]. This problem can be formulated according to Equation 2.6.

$$P = AT + C\frac{dT}{dt} \tag{2.6}$$

Where P and T are column vectors representing the power and temperature of each core, and C is a diagonal matrix which contains the thermal capacitance of each node. The challenge is to estimate the matrix A which is called the conductance matrix.

The first step to solve the IHCP problem is to collect the temperature data. This can be done either through an IR (InfraRed) photograph of a die [24, 25, 27], or using embedded performance counter based thermal sensors [26]. In either case, the same mathematical techniques need to be used. The first set of approaches try to solve the Equation 2.6 by assuming that the temperature values are exact. The work presented in [24, 25] is based on this approach. The second set of approaches consider some thermal noise which can arise due to the limits of heat transfer or measurement error. [27, 28] are in this category.

## 2.6 Summary

In this chapter, the most important processor power estimation methods proposed in the literature are investigated. Some of these methods work at design time, and are useful for early stage architectural exploration. Some other methods work at runtime, and are suitable for developing power efficient application software. The methods are classified in five categories, and the most prominent works in each category are described. The methods in these categories are based on program execution profile, architectural simulation, system-level models, hardware performance counters and on-chip temperature profile.

#### Chapter 3

## Asynchronous Charge Sharing Logic (ACSL)

In this chapter, the design concept of the Asynchronous Charge Sharing Logic (ACSL) is introduced. ACSL is a dynamic design style which is proposed in [69] as an ultra-low power methodology. ACSL circuits have two main properties. The first property is that they consume lower power in comparison with the other dynamic circuits, and the second property is that their power usage is almost constant and independent from the input patterns. This second property makes the ACSL circuits desirable in terms of power prediction. This property is the base of the power prediction method that is proposed in Chapter 5.

The structure of this chapter is as follows: in Section 3.1, the background information that is needed for understanding the ACSL design concept is presented. This information includes the description of the asynchronous logic, dynamic logic, and adiabatic differential logic family. In Section 3.2, the structure, general operation and circuit design of the ACSL is described. ACSL has been developed by combining an adiabatic differential logic with charge sharing technology. A modified version of ACSL called Latch-less ACSL (LACSL) is also introduced that

provides extremly low variation in the power consumption for the applications that data independency of power is crucial for their operation.

#### 3.1 Background

#### 3.1.1 Asynchronous vs. Synchronous Logic

It is widely accepted that a single clock (global clock) scheme would not adjust to the nano-scaled Very Large Scale Integration (VLSI) circuits and, thus asynchronous architectures (or hybrid) emerge as potential alternatives [70]. In largely conventional systems such as modern system-on-chip designs, global clock distribution has become such a challenge that some systems have separate clocks for each processor and exchange data asynchronously between them, referred to as Globally Asynchronous Locally Synchronous (GALS) [71].

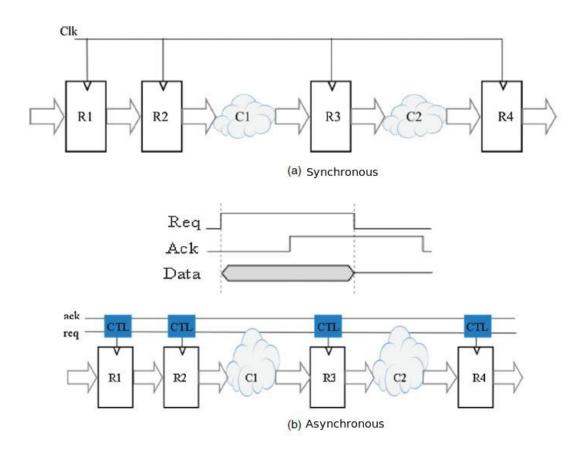

As shown in Figure 3.1 (a), the synchronous design consists of the several stages of the combinational logic which are separated by the memory blocks (registers) that transfer signals from one stage to the next. Each memory block is controlled by the clock signal (CLK) which is distributed through the clock tree. The whole system is under the control of this global clock. However, the essential clock tree results in large overhead in the area and the power consumption [72]. Other than this, the speed of the system is constrained by the the worst-case delay of the critical path.

Rather than using the global clock signal, the asynchronous circuits use a protocol called handshaking [73]. The basic structure of an asynchronous circuit is exhibited in Figure 3.1 (b). In this circuit, the flow of the data is controlled by the pipeline controllers (CTL) through the handshaking signals represented by ack and req. The controllers detect the completion of each stage, and produce

Figure 3.1: Synchronous Architecture vs. Asynchronous Architecture [69]

the ack signal which is used to trigger the operation of the next stage.

Unlike the conventional synchronous logic whose operation speed is determined by global worst-case latency, in asynchronous designs the speed depends on the actual local latencies. In other words, an asynchronous circuit has the potential to run at the highest possible speed. Moreover, not having to distribute a global clock leads to power savings, since the effective distribution of such a clock can cost 40% to 50% of the power in a modern digital system [74].

#### 3.1.2 Dynamic vs. Static Logic

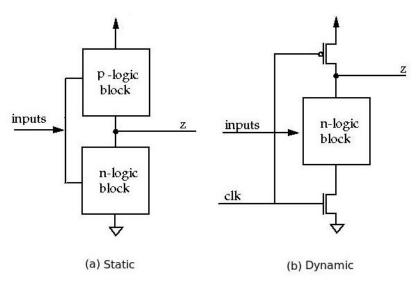

Most digital logic circuits are implemented using static CMOS logic gates for the combinational functions. Static gates always provide a definite output based on the current input, and update that output as soon as the input changes. As shown in Figure 3.2 (a), the static circuits are made of NMOS and PMOS logic blocks. These blocks are dual, and for any given input only one of them creates a path between output to either the power source or the ground [75].

Figure 3.2: Static Logic vs. Dynamic Logic

Dynamic logic refers to the logic gates where the gate does not drive the output constantly. Instead, the output value is stored temporarily in stray and gate capacitances. As shown in Figure 3.2 (b), a simple dynamic gate has just the NMOS pull-down network in series with an evaluate NMOS transistor to ground. There is no pull-up logic function, and just a single PMOS pre-charge transistor connects the output to the power supply. The execution of these gates is governed by a clock. When the clock goes low, the circuit goes to pre-charging phase. In this phase, the pre-charge PMOS transistor pulls the output of the gate high. When the clock goes high, the gate evaluates. In the evaluation phase, if the NMOS pull-down network is satisfied, in series with the pull-down NMOS transistor pulls the output low. If it is not satisfied, the output remains high due to the gate capacitances [76].

Dynamic logic circuits are usually faster than static counterparts, and require less surface area, but are more difficult to design. Static logic is slower because it has twice the capacitive loading, higher thresholds, and uses slow PMOS transistors

for logic. Dynamic logic can be harder to work with, but it may be the only choice when increased processing speed is needed [77]. Dynamic logic has a higher toggle rate than static logic [78] but the capacitative loads being toggled are smaller [79], so the overall power consumption of dynamic logic may be higher or lower depending on various tradeoffs.

#### 3.1.3 Adiabatic Dynamic Differential Logic

Dynamic logic gates cannot directly be cascaded. The reason is that for the correct operation of the dynamic gates the inputs need to be monotonically rising during the evaluation phase [80]. Considering the case where two gates are connected directly, and the final output should take value '1', the pre-charged '1' on the intermediate node can partially discharge the output of the second gate before the intermediate node takes its correct value.

Various designs are available to address this problem. Domino logic is one design where each dynamic gate is followed by a static inverter. However this means that all the intermediate nodes must be non-inverting, limiting the range of functions that can be implemented. Thus dynamic logic families are often differential (dualrail), that is each signal is computed in both true and complemented form. There are several dynamic differential CMOS logic types such as Dual-rail Domino logic [81], DDCVSL (Dynamic Differential Cascode Voltage Switch Logic) [82], SABL (Sense Amplifier Based Logic) [83], etc.

Dynamic differential logic is well-known for its high speed property. However, its drawaback is inevitably high energy dissipation. Adiabatic logic [84] is a new type of low power differential logic which has drawn a lot of attention in recent years. The term, adiabatic (meaning no heat transfer), comes from the fact that an adiabatic process is one in which the total heat or energy in the system remains constant.

Adiabatic circuits recycle the energy after the evaluation through the Power Clock Generator (PCG) which usually is a LC resonant circuit [85] or a switch capacitor tank [86]. Power Clock Generator (PCG) is a replacement for DC supply (VDD) that is used in the standard CMOS circuits. The general structure of the adiabatic logic circuits is shown in Figure 3.3. The special design of the gate, and the use of the Power Clock Generator (PCG) satisfies two fundamental rules that leads to energy saving in the adiabatic logic. The first rule is never to turn on a transistor when there is a voltage difference between the drain and source. The second rule is never to turn off a transistor that has current flowing through it [84].

Figure 3.3: Basic Blocks of Adiabatic Logic System [85]

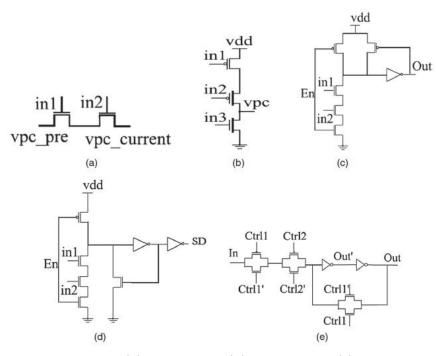

Figure 3.4 depicts three main styles in adiabatic logic family, which are Positive Feedback Adiabatic Logic (PFAL) [87], 2N-2N2P [88] and Efficient Charge Recovery Logic (ECRL) [89]. All three structures are charged and discharged through the Power Clock Generator (PCG).

Each PCG cycle consists of four intervals: evaluate, hold, recovery and wait. In the evaluate interval, PCG is charged up to a certain value, usually VDD, and the differential outputs are set as '1' or '0' depending on the function of the n-tree. During the hold interval, outputs are kept stable for supplying the subsequent gate with a stable input signal. In the recovery interval, PCG recycles the energy stored in the circuit by discharging itself to zero. For symmetry resons, a wait interval is also inserted [90].

Figure 3.4: (a)General Schematic for PFAL, (b)General Schematic for 2N-2N2P, (c)General Schematic for ECRL

PFAL has the lowest power dissipation and the best consistency of voltage scaling in contrast to 2N-2N2P and ECRL [91]. However, the efficiency and performance of adiabatic circuits is restricted by PCG. Sometimes it even minimizes the savings achieved by adiabatic circuits itself. Also the area overhead due to resonant LC circuits for PCG is high.

To avoid the effort of designing power clock generator for adiabatic circuits, a new logic called Asynchronous Charge Sharing Logic (ACSL) is proposed in [69]. This new logic achieves reduced power consumption as well as low power variability. The ACSL design structure and general operation is explained in the next section.

#### 3.2 Asynchronous Charge Sharing Logic

The main methodology of Asynchronous Charge Sharing Logic (ACSL) is to combine PFAL adiabatic logic with charge sharing technology. The main body of the PFAL is inherited by the ACSL, but the Power CLock Generator (PCG) is replaced by the charge sharing mechanism.

#### 3.2.1 General Operation of ACSL

Figure 3.5: General Structure of ACSL [92]

The general architecture of the ACSL circuit is shown in Figure 3.5. The ACSL circuit consists of some stages of logic which are controlled by an asynchronous handshake. The internal structure of each stage is the same as the PFAL circuit shown in Figure 3.4 (a). The charging, discharging and sharing are performed by a power control block called  $VPC\_Ctrl$  and a power sharing block called  $VPC\_Shr$ . The  $VPC\_Ctrl$  enables the evaluation and discharging of the ACSL circuit while the  $VPC\_Shr$  is used to share the energy between two neighboring stages [69].

In Figure 3.5,  $C_1$  is the capacitance load at VPC1, and  $C_2$  is the capacitance load at VPC2. Before the charge sharing happens, the voltage of VPC1 is at VDD, and the voltage of VPC2 is at zero. At the end of the charge sharing process between VPC1 and VPC2, the voltage of both nodes equals to VDD/2 assuming that  $C_1$  is the same as  $C_2$ . After the charge sharing, VPC1 is discharged to zero, and VPC2 is charged to full VDD. The waveforms for VPC signals are shown in Figure 3.6 [69].

The stages of the ACSL circuit shown in Figure 3.5 make an asynchronous system, and the *VPC\_Ctrl* units control the flow of data between the stages. Firstly,

Figure 3.6: VPC Signals Waveform [92]

$VPC\_Ctrl1$  evaluates the logic block of stage 1 by charging the VPC1 to VDD. The output of the stage 1 is latched to be available as the input to the stage 2. Then the  $VPC\_Shr1$  placed between stage 1 and stage 2 is switched on to start the charge sharing process. Once VPC1 and VPC2 reach almost the same level, nearly VDD/2, a Sharing Detector (SD) unit turns off the  $VPC\_Shr1$ .  $VPC\_Ctrl2$  is then activated to charge VPC2 from VDD/2 to full VDD. Meanwhile, VPC1 is discharged to zero by  $VPC\_Ctrl1$ . This process repeats for the following stages [69].

#### 3.2.2 ACSL Circuit Design

Figure 3.7 shows the detailed architecture of a two stage ACSL circuit. The evaluation and charge sharing in this circuit is controlled by an asynchronous handshake. This handshake is based on the stage power clock, VPC(i) and three other signals, Ctrl(i), Req(i) and SD(i). Ctrl(i) puts the gate logic in the evaluation mode, and Req(i) indicates the completion of the stage. SD(i) triggers the charge sharing between the stages.

A dynamic AND is used to generate Ctrl(i). Using the dynamic AND leads to Ctrl(i) switching to low voltage immediately once Ctrl(i+1)\_n becomes low. In this way, activation of the next stage leads to the deactivation of the current stage.

Figure 3.7: 2-Stage Architecture of The ACSL circuit [69]

A dynamic buffer which is controlled by the Ctrl(i) signal is used to accomplish the completion detection. This buffer senses the VPC signal, and generates the Req(i) signal. The completion of each stage triggers the activation of the next stage. The signal transition diagram of the ACSL handshaking protocol is exhibited in Figure 3.8. As seen in the figure, the control signal of an indivisual stage is only valid when the control signal of two adjacent stages are low.

When the Ctrl(i) becomes low, the Sharing Detector (SD) gets active, and starts the charge sharing between the stages. When both VPCs are higher than the threshold voltage of the NMOS transistor, the signal SD becomes low. It indicates that sharing operation can be stopped by switching off  $VPC\_Shr$ .

The two-controlled latch placed between the stages is crucial for the correct op-

Figure 3.8: ACSL Handshaking Protocol [69]

Figure 3.9: Schematic for (a) VPC\_Shr, (b) VPC\_Ctrl, (c) Dynamic AND, (d) Sharing Detector, and (e) Two-controlled Latch [69]

eration of the ACSL. It assures that all the data from previous stage is loaded before the sharing happens. The latch is accessed only when the signal Req(i) is high and the signal Ctrl(i+1) is low, and it enters into hold mode as soon as Ctrl(i+1) becomes high. In this way, the output is stored when the evaluation of the current stage is complete, and stays unchanged when the next stage is in the evaluation mode. The circuits of  $VPC\_Shr$ ,  $VPC\_Ctrl$ , Dynamic AND, Sharing Detector and two-controlled latch are all shown in Figure 3.9.

#### 3.2.3 Latch-Less ACSL

Asynchronous Charge Sharing Logic (ACSL) has good power constancy, due to the symmetry of the gates and the fact that the gates are completely discharged in between executions. However, the latches which are necessary for the complete discharge of the gates consume different amounts of power depending on whether they are rewritten with the same or opposite value. In some applications like

Figure 3.10: Block Diagram of Latch-Less ACSL [93]

cryptography, it is very important for the system to have extremly low power variation to avoid power attacks [93]. In such cases, it is desirable to design the circuit without the latches, since they are the only ACSL component with intrinsic data dependence.

It is not practical to exclude the storage elements directly from ACSL, doing so reduces the stability of the gates. without data retention devices, once the charge sharing finishes, the input data for the next stage might not be valid (only at half VDD), the consequent unequal voltage distribution not only slowing down the evaluation speed but also leading to possible error occurrences like the write error in SRAM cells [93].

To tackle this problem, interleaved charge sharing is considered, because it could intuitively solve the voltage unbalance situation discussed above. The block diagram of the Latch-less ACSL (LACSL) is shown in Figure 3.10. It can be seen that charge sharing occurs between the Voltage Power Clocks (*VPCi*, i=1..4) which are one stage apart instead of the adjacent stages. By doing this, input data for each stage is always fully charged during the computation. Moreover, it is found to be generally efficient in terms of performance, power consumption and area. The main adjustment needed in LACSL is to re-design the *VPC\_Ctrl* circuit to maintain the power-up situation across the stages. LACSL offers extremly

low power variation, and thus very high predictability. In [93], a Montgomery modular multiplier is developed using LACSL for cryptography applications.

#### 3.2.4 Summary

The Asynchronous Charge Sharing Logic (ACSL) is a dynamic design style that combines PFAL adiabatic logic family with charge sharing technology. The ACSL has low power usage, and exhibits strong power predictability that is a useful feature for high level power analysis.

In this chapter, the background information for understanding the ACSL design concept is presented, and the structure and operation of the ACSL circuits are explained. A variant of ACSL is also introduced that offers even more constant power usage by excluding the latches from the ACSL structure.

In next chapter, the implementation of the Arithmetic Logic Unit (ALU) of 8051 microcontroller in ACSL is described. A power prediction method for this ALU is proposed in Chapter 5. The prediction method is based on the data independency of power consumption which is one of the main properties of ACSL circuits.

#### Chapter 4

# Implementation of 8051 Arithmetic Logic Unit (ALU) in ACSL

In this chapter, the implementation of the 8051 Arithmetic Logic Unit (ALU) in Asynchronous Charge Sharing Logic (ACSL) is described. The aim of this implementation is using the property of ACSL in providing power predictibility for the circuits. The ALU operations in ACSL show almost constant power usage independent from the inputs. This property makes it possible to estimate the power usage for the ALU only by knowing the number and type of the operations it performs.