| Title                       | Synthesis and electrical and mechanical properties of silicon and germanium nanowires                                                                                                                                                                                                                                                                          |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Authors                     | Wu, Xueyan;Kulkarni, Jaideep S.;Collins, Gillian;Petkov,<br>Nikolay;Almecija, Dorothee;Boland, John J.;Erts, Donats;Holmes,<br>Justin D.                                                                                                                                                                                                                       |  |  |

| Publication date            | 2008-08-13                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Original Citation           | Wu, X., Kulkarni, J. S., Collins, G., Petkov, N., Almécija, D., Boland, J. J., Erts, D. and Holmes, J. D. (2008) 'Synthesis and Electrical and Mechanical Properties of Silicon and Germanium Nanowires', Chemistry of Materials, 20(19), pp. 5954-5967. doi: 10.1021/cm801104s                                                                                |  |  |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                        |  |  |

| Link to publisher's version | https://pubs.acs.org/doi/abs/10.1021/cm801104s - 10.1021/<br>cm801104s                                                                                                                                                                                                                                                                                         |  |  |

| Rights                      | © 2008 American Chemical Society. This document is the Accepted Manuscript version of a Published Work that appeared in final form in Chemistry of Materials, copyright © American Chemical Society after peer review and technical editing by the publisher. To access the final edited and published work see https://pubs.acs.org/doi/abs/10.1021/cm801104s |  |  |

| Download date               | 2025-08-17 20:09:55                                                                                                                                                                                                                                                                                                                                            |  |  |

| Item downloaded from        | https://hdl.handle.net/10468/8151                                                                                                                                                                                                                                                                                                                              |  |  |

The Synthesis and Electrical and Mechanical

Properties of Silicon and Germanium Nanowires

Xueyan  $Wu^{1,2}$ , Jaideep S. Kulkarni<sup>1,2</sup>, Gillian Collins<sup>1,2</sup>, Nikolay Petkov<sup>1,2</sup>, Dorothée Almécija<sup>1,3</sup>, John J. Boland<sup>1,3</sup>, Donats Erts<sup>1,4</sup> and Justin D. Holmes<sup>1,2</sup>\*

<sup>1</sup>Centre for Research on Adaptive Nanostructures and Nanodevices (CRANN) Trinity College Dublin, Dublin 2, Ireland

<sup>2</sup>Department of Chemistry and the Tyndall National Institute, University College Cork, Cork, Ireland

<sup>3</sup>School of Chemistry, Trinity College Dublin, Dublin 2, Ireland

<sup>4</sup>Institute of Chemical Physics, University of Latvia, LV-1586 Riga, Latvia

\* Author to whom correspondence should be addressed. E-mail: j.holmes@ucc.ie

Tel: +353 (0)21 4903608

Fax: +353 (0)21 4274097

#### **Abstract**

The development of semiconductor nanowires has recently been the focus of extensive research as these structures may play an important role in the next generation of nanoscale devices. Using semiconductor nanowires as building blocks, a number of high performance electronic devices have been fabricated. In this review, we discuss synthetic methodologies and electrical characteristics of Si, Ge and Ge/Si core/shell nanowires. In particular the fabrication and electrical properties of a variety of nanowire-based field effect transistors (FETs) are discussed. Although the bottom-up approach has the potential to go far beyond the limits of top-down technology, new techniques need to be developed to realize precise control of structural parameters, such as size uniformity, growth direction and dopant distribution within nanowires to produce nanowire-based electronics on a large scale.

#### 1. Introduction

1 D semiconducting nanowires possess some very unique properties such as quantum confinement effects, surface sensitivity and low leakage currents which make them attractive as building blocks for functional nanosystems and next generation electronics. Chemically synthesized semiconductor nanowires have attracted much attention as key parameters, such as diameter, length, growth direction, chemical composition and doping levels can be rationally and predictably controlled during the synthesis process, which may enable their integration in a wide range of devices <sup>1-6</sup>. Semiconductor nanowires have been used for the assembly of FET devices with either a top, bottom or surround gate architecture <sup>7-12</sup>. Low-temperature bottom—up assembly methods offer unique opportunities and alternatives for the design and fabrication of single- and multi-nanowire device structures on a range of substrates without the need for lithography, which currently dominates many top-down technologies.

Si transistor technology, in particular CMOS, has played a pivotal role in allowing a decrease in feature sizes by a factor of 0.7 every 3 years as predicted by Moore's law <sup>13</sup>. Currently Intel has started production at the 45 nm technology node using an all dry process with other chipmakers in-step or close behind. However, to improve device performance, increase device density and reduce power consumption, further downscaling will be greatly desirable. Great attention has been paid to the 32 nm and 22 nm nodes although it is highly challenging according to the International Technology Roadmap for Semiconductors (ITRS):2007 <sup>14</sup>. ITRS 2007 expects that by 2018, the metal oxide semiconductor

field-effect transistor (MOSFETs) node will be scaled down to 18 nm and beyond, with the gate length down to 7 nm (Table 1). However planar bulk Si MOSFETs are unlikely to meet the ITRS roadmap requirements in the long-term and hence new structural, material and fabrication technology solutions, that are generally compatible with current and Si manufacturing, have to be exploited to maintain the historical CMOS performance trend.

Compared with bulk semiconductors, semiconductor nanowires have attracted considerable attention because of their unique electrical properties and intrinsically miniaturized dimensions <sup>15-17</sup>. Semiconductor nanowires can have an on/off current ratio which varies by many orders of magnitude for small changes in gate voltage. They also offer the possibility of ballistic transport since electron scattering in 1 D is much reduced <sup>18</sup>. In general, the performance characteristics of nanowire-based electronic devices often rivals devices constructed from the best bulk and epitaxial single-crystal semiconductors. Semiconductor nanowires are looked upon as a potential solution to some of the most daunting challenges in the painstaking effort to shrink CMOS FET devices deeply into the nanometre regime. Ge and Si nanowires offer a performance enhancement of FETs without jeopardizing device reliability. FETs based on boron and phosphorus-doped Si and Ge nanowires have been actively studied during the past several years as these two materials offer great compatibility with the industrial chip technology <sup>18-22</sup>. Devices based on Si and Ge nanowires display performances that are comparable to the best reported for corresponding planar devices. 23, 24

In this article, we review the synthesis, electronic and mechanical properties of Si, Ge and

core/shell Ge/Si nanowires as well as the performance of nanowire-based FET devices.

#### 2. Silicon Nanowires

## 2.1 Si Nanowire Synthesis

Various methods have been employed to synthesize Si nanowires including electron beam lithography <sup>25</sup>, reactive ion etching <sup>26</sup> and laser ablation <sup>27</sup>. Among the lithography approaches, special attention should be given to the method developed by Heath and co-workers for depositing aligned arrays of Si nanowires by the supperlatice nanowire pattern transfer (SNAP) technique, since very small and uniform diameter structures were obtained<sup>28</sup>. Most Si nanowires have been synthesised by the classical metal catalyzed vapor-liquid-solid (VLS) growth process using gold nanoparticles as catalytic seeds. In the VLS process, the Si precursor decomposes on the surface of the catalyst and Si diffuses into the metal forming a liquid alloy. Upon reaching supersaturation, a Si nanowire is precipitated and the liquid alloy drop remains at the end of the nanowire as it grows in length <sup>29</sup>. The diameter of each Si nanowire is largely determined by the size of the catalyst particle and growth conditions. It has been demonstrated that Si nanowires with specific dimensions can be obtained by controlling the diameter of gold particles, which can be formed by metal deposition, photolithography, laser ablation, evaporation or nanocluster formation <sup>8, 23, 24, 30-34</sup>. The VLS process has also been used to grow doped Si nanowires using boron sources such as trimethylboron (TMB) and diborane  $(B_2H_6)^{35}$ . At the specific growth conditions used, B-doped Si nanowires grown using B<sub>2</sub>H<sub>6</sub> consisted of a crystalline core with a thick amorphous Si coating, while the B-doped Si nanowires grown from TMB were predominantly single crystalline even at high boron concentrations.

The authors suggested that the difference in the crystallinity can be attributed to the higher thermal stability and reduced reactivity of TMB compared to B<sub>2</sub>H<sub>6</sub>. Nevertheless a detailed mechanistic study is still necessary to uniquely identify the conditions responsible for the difference in the crystalinity of the doped Si nanowires obtained.

Nanoporous templates have been employed to synthesize Si nanowires. High-density, free-standing, vertical Si nanowires with well-defined diameter and spacing were synthesized by Lombardi et al. using a non-lithographic technique (Figure 1) <sup>36</sup>. An anodized aluminium oxide (AAO) membrane was first transferred onto a Si (111) substrate, followed by the evaporation of Au through the AAO pores. The AAO was then removed and Si nanowires were grown from the patterned substrate by the VLS technique. method enables the fabrication of Si nanowires with a high packing density, up to 60 wires/ $\mu$ m<sup>2</sup> and is the highest reported density of vertical Si nanowires on a Si substrate without lithographic means. Additionally Redwing et al. have combined template-directed synthesis and VLS growth techniques to produced Si nanowires ranging from 45 to 200 nm <sup>37-39</sup>. These Si nanowires were single crystals with a [110], [111], or [100] growth direction, or bicrystalline containing a single (111) twin boundary along the [112] growth axis. It was noted that when longer reaction times were employed larger diameter nanowires grew on the surface of the membranes. The authors speculate that the size difference between these nanowires is likely due to a change in the shape of the Au tip from cylindrical to hemispherical, which occurs when the Au-Si liquid alloy is no longer constrained by the pore walls. Nevertheless a detailed investigation and observation of the Si nanowires within the AAO channels to assess loading factors and their distribution along the length of the membrane was not discussed. Investigation of the Si nanowire growth characteristics showed that the length of the Si nanowires was linearly dependent on the growth time over a temperature range from 400 to 600 °C, and over a SiH<sub>4</sub> partial pressure range from 0.13 to 0.65 Torr. This approach also provided a method for contact formation as the AAO membrane could be used as a support structure based on the work by Erts *et al* 40

#### 2.2 Silicon Nanowire Field Effect Transistors

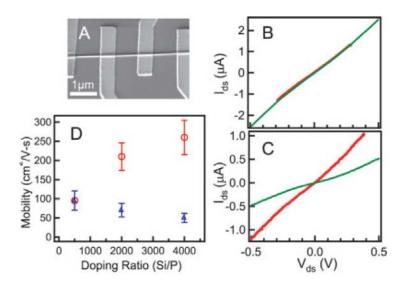

Lieber et al have been extremely successful in fabricating and electrical characterizing Si nanowire-based FET devices. They have demonstrated that carrier type (electrons, n-type; holes, p-type) and carrier concentrations in single-crystal Si nanowires can be controlled during the growth process using phosphorus and boron dopants <sup>24</sup>. Back-gated n-type FETs were fabricated based on p-doped 20 nm Si nanowires grown with a gold nanocluster mediated VLS technique. It was reported that these FETs have an electron mobility 100 times higher than those prepared in a laser-assisted catalytic growth process and are comparable to high-performance planar Si FETs. While investigating the electrical properties of P-doped devices with different dopant concentration, it was found that the transconductance values and mobility values decreased with decreasing dopant concentration, which contrasts the behavior in bulk silicon. This fact still leads to number of discussions in the literature and definitely requires further investigation. Bv determining the intrinsic transconductance values with data obtained from two and four-probe transport measurements, it was concluded that this behavior was due to dopant concentration dependent contact resistances between the Si nanowires and source/drain

electrodes. In other words the contact resistance is negligible for the measurement of transconductance in heavily doped Si nanowire devices, while it makes a substantial contribution in the lightly doped Si nanowires devices. The intrinsic transconductance value was four times larger for the heavily doped nanowires as compared to the lightly doped Si nanowires (Figure 2). The mobility after correction of the contact resistance effects decreased from 260 to 95 cm $^2$  /Vs as the phosphorous doping level increased from Si:P = 4000 to Si:P = 500 and is in agreement with the values reported for bulk silicon.

As compared with n-type Si nanowire FETs, p-type Si nanowire FETs have attracted greater interest 8, 11, 24, 30, 31, 41-43. High- performance p-type Si nanowire FETs have been fabricated using 10-20 nm diameter single-crystal VLS grown Si nanowires and Ti as a source/drain (S/D) contact 8. It was observed that not only was the hole mobility of Si nanowire FETs an order magnitude larger than that of planar Si devices, but the average transconductance was also approximately 10 times larger. However, value of mobility obtained was an estimated field effect mobility based on a measured transconductance. Significantly, it has been observed that the average sub-threshold slope approaches the theoretical limit. Importantly, it has been observed that both the transconductance and mobility increase by an order of magnitude after surface modification, suggesting that many of the electrical properties of the nanowire-based devices are determined by the large number of surface states. These characteristics suggest that Si nanowires have better device characteristics than state-of-the-art silicon-on insulator (SOI) FETs. Si nanowire-based devices thus have the potential to substantially exceed the performance of conventional devices. Nevertheless we should not exclude the fact that such devices lack the possibility of large scale processability, integration and reliability in their performance. In order to explore the possibility of utilizing Si nanowire-based FETs in the area of multifunctional electronics and display applications the characteristics of single-crystal Si nanowire FETs assembled on non-conducting glass and plastic substrates have been studied <sup>32</sup>. It was demonstrated that ohmic contacts to Si nanowires are possible on both glass and plastic substrates using post-synthesis processing performed entirely at room temperature. These Si nanowire FETs assembled on both plastic and glass substrates displayed device performances which exceeded those of state-of-the-art amorphous Si and organic transistors currently used for flexible electronics on plastic substrates. Moreover, the high-performance characteristics of Si nanowire FETs assembled on plastic substrates were relatively unaffected by operation in a bent configuration or by repeated bending. The robust nature of Si nanowire FETs on plastic substrates enhances their potential for high performance flexible devices. These studies on Si nanowire FETs on non-crystalline substrates have opened up a new direction for nanoelectronics.

Nanowire FET device performance is affected by the contact properties to a large degree <sup>44-48</sup>. Studies of thermal annealing effects on the transport characteristics of single B-doped Si nanowire FETs with Ti S/D contacts have revealed that both the transconductance and the mobility increase after annealing <sup>8</sup>. Based on measurements carried out on over 50 devices it was concluded that the above observation can be partially attributed to better metal-Si nanowire contacts. Redwing *et al.* have carried out four-point resistance measurements and gate-dependent conductance on individual B- and P-doped Si nanowires grown on the surface of AAO membranes using TMB and PH<sub>3</sub> as the source of

boron and phosphorus, respectively <sup>35, 49</sup>. The results showed a clear trend of decreasing nanowire resistivity for increasing dopant:Si ratio. For P-doped Si nanowires, it was observed that the resistivity decreased by approximately 3 orders of magnitude as the P:Si ratio was increased from 2  $\times 10^{-5}$  to 2  $\times$  10<sup>-3</sup>. A P:Si ratio greater than 2  $\times$  10<sup>-5</sup> was required to compensate the unintentional p-type background doping (most probably created by the surface states) of the Si nanowires and transition from p- to n-type conduction. A method for extracting Si nanowire resistivity from measurements carried out on B- and P-doped Si nanowire array formed within the pores of an AAO template has recently been developed <sup>50, 51</sup>. This method utilizes the magnitude of the array resistance as a function of nanowire length in order to extract the resistivity parameter. As expected it was found that the resistivity of a nanowire embedded within the AAO membrane decreases with increasing dopant/source gas ratio. Siginificantly, it was observed that the resistivity of these nanowires compared favorably with resistivity data obtained on individual Si nanowires grown under identical conditions. Nevertheless such a relationship is not clear since the structural properties of the free-standing Si nanowires can differ significantly from those deposited within the confined environment of an AAO template.

Silicides can be potentially used as device contacts, gate electrodes, and local interconnects. Self-aligned-silicide technology which offers a possible way to reduce parasitic resistances has been applied for the fabrication of advanced logic devices. This technology may provide a way for the rapid and successful miniaturization of device dimensions for MOSFETs in pace with Moore's law <sup>52-57</sup>. The current focus of silicide technology is centered on contact resistivity in the S/D regions of a MOSFET. The primary challenge

for metallic-S/D technology is achieving a sufficiently low Schottky barrier height to meet the Roadmap I<sub>on</sub> specifications. Mohney *et al.* have recently described the fabrication of cobalt silicide contacts to Si nanowires within AAO arrays <sup>39</sup>. Cobalt silicide was formed by the reaction of cobalt deposited within the AAO pores and the growing of Si NWs during the VLS process. The interface between the cobalt silicide and Si was formed along the cross section of the wire. However this method may lead to doping of the Si nanowires with Co atoms.

Due to the superior nature of nickel mono-silicide (NiSi) over TiSi<sub>2</sub> and CoSi<sub>2</sub>, such as the elimination of adverse narrow line effects on sheet resistance, lower contact resistance and lower temperature of formation, NiSi is a better candidate to replace TiSi2 and CoSi2 as the silicide material for contact metallization for sub-100 nm CMOS technology <sup>58, 59</sup>. NiSi technology was first developed by Morimoto et al with the demonstration of a 0.4 µm NiSi silicide-based CMOS structure <sup>57, 59</sup>. NiSi can be formed by rapid thermal annealing of a nickel film sputtered onto Si substrates at relatively low temperatures (400-600 °C). The current drivability of both n- and p- MOSFETs with the NiSi technology is higher than the conventional titanium silicide process due to the lower contact resistance and sheet resistance of polysilicon and single-silicon layers. The metal-gate approach is especially crucial for smaller devices with thinner gate dielectrics in advanced CMOS technologies. NiSi used as a metal gate with dual work functions in state-of-the-art thin-body double-gate FINFET structures has been demonstrated. Such MOSFETs with a metal gate are free from the gate poly-Si depletion problem and thus characterized with an enhanced gate control over the channel <sup>56</sup>. Studies on NiSi sub-100 nm gate length CMOS or MOSFETs have shown that these devices exhibit excellent electrical characteristics <sup>58, 60</sup>.

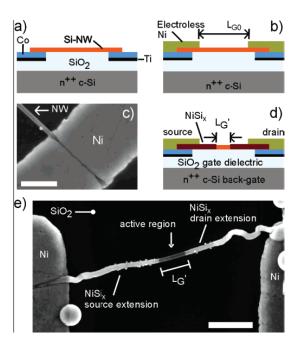

Lieber *et al* have reported the selective transformation of Si nanowires into NiSi nanowires  $^{61}$ . These single crystal NiSi nanowire heterostructures have ideal resistivities of about 10  $\mu\Omega$  cm and remarkably high failure-current with atomically sharp metal–semiconductor interfaces. Spatially and electronically well-defined metal–semiconductor FETs fabricated based on these heterostructures exhibited a relatively high hole mobility of 325 cm<sup>2</sup> Vs, but lower than previously reported by the same group for doped Si nanowires. The formation of nikel-silicide source and drain segments along the nanowire have allowed the reduction of the physical gate length in Si nanowire FETs (Figure 3)  $^{62}$ . Si nanowire FETs fabricated using this approach exhibit on/off ratios of up to  $10^7$ , which are the highest reported for catalytically grown and nominally undoped Si NWs.

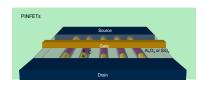

A surround gate architecture allows better electrostatic gate control of the conducting channel and offers the potential to drive more current per device area than is possible in a conventional planar architecture<sup>63</sup>. With surround gate architecture, FETs offer greater scalability due to the superior control of short-channel effects and leakage, providing the ideal device architecture for sub-10 nm CMOS. The epitaxial growth of vertical nanowires enables the fabrication of surround-gate FETs. The first generation device of vertically integrated nanowire FETs (VINFETs) based on Si nanowires was reported by both Yang and Schmidt in 2006 <sup>63, 64</sup>. The Si wafers on which the Si nanowires were grown served as the common bottom contact. The vertical Si nanowire cores were used as the active channels. The gate length was defined by etching of the gate material. Ti, Ni

or Ni/Pt was fabricated to form the top gate (Figures 4 and 5). No chemical or mechanical polishing step was involved in the fabrication process. This novel concept represents a platform for the fabrication of high-performance Si nanowire electrical devices. undoped <sup>7</sup> and B-doped <sup>64</sup> Si VINFETs were fabricated using this technique. The undoped devices functioned as regular FETs having an inverse sub-threshold slope of 250 mV/ decade for small V<sub>DS</sub>. Under reverse bias, these devices functioned as impact ionization FETs with a I<sub>on/off</sub> as high as four orders of magnitude. The minimum value recorded was an order of magnitude below the theoretical room temperature limit. Initial first generation un-optimized B-doped Si VINFETs also exhibited excellent electronic properties. The transconductance and hole mobility of these devices was comparable to reported values for high-performance SOI MOSFETs. The sub-threshold slope was much smaller than typical values obtained for nanowire devices with back-gate or top-gate geometries. The authors claim that a Si nanowire channel as thin as 6.5 nm was fabricated, demonstrating the ability to further scale down the device dimensions. Nevertheless, detailed structural characterization demonstrating the very small dimensions of these device were not presented.

#### 3. Germanium Nanowires

Recently Ge has attracted considerable interest as a channel material for FETs due to its lower resisitivity and higher hole carrier mobility compared to Si. These characteristics suggest that Ge nanowires could be utilized in the fabrication of high performance transistors with nanoscale gate lengths, especially for faster switching and higher frequency devices <sup>65, 66</sup>.

### 3.1 Germanium Nanowire Synthesis

The first Ge nanowire synthesis was reported by Heath and coworkers in 1993 using a solvothermal reaction <sup>67</sup>. Other synthetic methods including laser ablation, supercritical fluid-liquid-solid (SFLS) synthesis <sup>68</sup>, vapor transport <sup>69</sup> and supercritical fluid (SCF) deposition <sup>40</sup>. Lieber and co-workers have successfully combined the VLS approach with laser ablation techniques for the synthesis of Ge nanowires <sup>70a</sup>. Although single-crystal Ge nanowires with diameters as small as 3 nm have been synthesized using this method the mean diameter obtained is typically around 80 nm. Recently, in-situ high temperature TEM measurements were employed to observe Au-Ge alloy drops at the tips of VLS grown Ge nanowires. It was observed that the phase diagram of the nanoscale drop deviates significantly from that of the bulk alloy, which may explain various discrepancies between actual growth results and predictions made on the basis of the bulk-phase equilibria 70b. Korgel et al have developed high tempertature (375 °C) supercritical fuild-liquid-solid (SFLS) growth approach to grow Ge nanowires ranging from 5 to 30 nm in diameter utilizing organic-monolayer-protected gold nanocrystals as catalysts <sup>68</sup>. co-workers have reported a relatively low temperature (275 °C) growth of high-quality single-crystal Ge nanowires via chemical vapour deposition (CVD) under atmospheric pressure <sup>71</sup>. A low-pressure CVD method has also been developed to achieve deterministic one-to-one synthesis of Ge nanowires in near-quantitative yields from gold-seeded particles <sup>72</sup>. Tutuc *et al* have studied the morphology of Ge nanowires grown in the presence of B<sub>2</sub>H<sub>6</sub>. Undoped Ge nanowires wrapped by a conformal B-doped Ge shell were fabricated by a two- stage growth process. The undoped Ge core served as the transistor's channel while the doped Ge shell acted as the gate. The above example opens

up the possibility of a Ge nanowire-based core/dielectric/gate *in-situ* FET growth if a dielectric growth can be introduced before the growth of doped Ge nanowires <sup>73</sup>.

Unfortunately, the Ge nanowires synthesized by techniques discussed above are randomly oriented and if nanowires are to be integrated into useful devices it would be highly advantageous to have an organised and aligned array of nanowires. A Langmuir-Blodgett (LB) technique has been used to obtain LB films of high quality single-crystal Ge nanowires with close packing and excellent alignment <sup>74</sup>. These Ge nanowires were synthesized using a CVD approach. The surface of the Ge nanowires was then functionalized and passivated to enhance the solubility of Ge nanowires in organic solvents. Ge nanowire suspension were then added drop wise to a sub-phase of ethanol/water. Floating Ge nanowires were left on the water surface after the evaporation of the organic solvent. The close-packed Langmuir-Blodgett films were then obtained upon compression. Unfortunately, these nanowire arrays lack full directional alignment with controlled pitch and length. Nevertheless isolated nanowires were used for nanowire FET device fabrication <sup>74</sup>. Another approach to form aligned nanowire assemblies was developed by Chidsey and co-workers who grew vertically oriented Ge nanowires of uniform length and diameter <sup>75</sup>. Homogenously-sized gold catalysts from acidified gold colloid solutions were deposited onto oxide-free silicon substrates, followed by a two-step temperature process to grow predominantly vertically-oriented Ge nanowires. Figure 6a shows the cross-section SEM image of vertically-oriented Ge nanowires on Si(111) substrates. 94 % of nanowires were observed to grow in the vertical direction while 6 % of the nanowires were oriented in other non-vertical directions, which appear at 120° from each other. All nanowires were of the same length. Moreover, it was possible to remove the gold catalysts from the nanowires with aqueous triiodide and HCl while preventing substantial etching of the nanowires. A two-furnace thermal evaporation system where the nanowire growth temperature and source evaporation temperature are separately controlled was developed by Yu et al to synthesize large quantities of single crystalline Ge nanowires using Ge powder as a source <sup>4</sup>. A systematic study of the effect of temperature on the Ge nanowire synthesis showed that a high yield of straight nanowires, with relatively good diameter uniformity, were obtained in the temperature range between 450 and 600 °C. Compared to other methods such as laser ablation, metalorganic CVD, and CVD, the two-furnace thermal evaporation system uses a much simpler reaction setup and non-hazardous materials and gases. It was observed that In-catalyzed Ge nanowires prefer [111] growth direction on SiO<sub>2</sub> substrates while [110] direction on Si (111) substrates at the same growth temperature. It was speculated that the low melting point of In and surface interaction between the molten In and different substrates play a key role in determining the growth direction of the Ge nanowires. Nevertheless, a deeper mechanistic study would be necessary to fully identify the growth conditions leading to such deterministic growth directions. High-density, vertical, free-standing Ge nanowires with smooth surfaces and uniform diameters on doped and undoped Ge substrates were produced using a similar approach (Figure 7) <sup>66</sup>. The typical morphology of the Ge nanowires consisted of a hemispherical gold catalyst head on top of a Ge receptacle, followed by the Ge nanowire stem. Ge nanowires synthesized using this method were observed to be coated with a thin Ge oxide layer. This approach offers the possibility of integrating nanowires into electronic devices such as VINFETs by avoiding the laborious positioning of

randomly-oriented nanowires, but requires extensive and sometimes limited processability integration steps. Template encapsulation synthesis too offers a viable method to form high density arrays of ordered, crystalline nanowires.

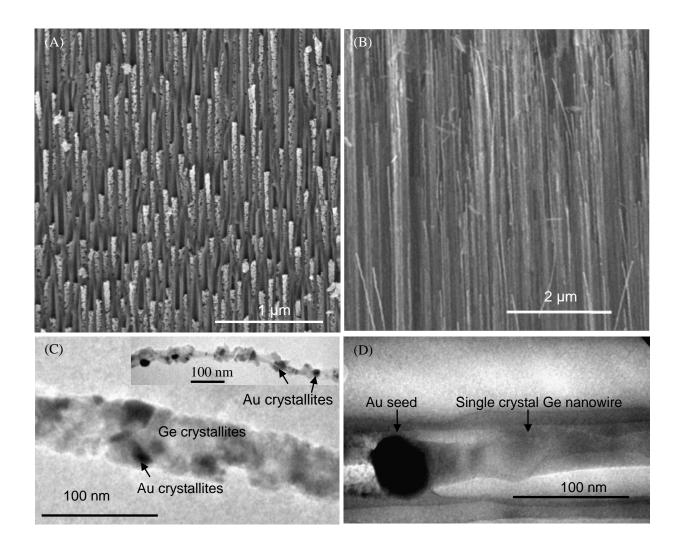

Within CRANN we have developed SCF deposition methods to form high-density, vertically aligned Ge nanowires with controlled diameters. Our synthetic approach for growing Ge nanowires relies on the selective modification of channelled alumina surfaces with Au-seeds that guide the growth of 1 D nanostructures by the SFLS mechanism. The nanostructures were obtained with tuneable and controllable crystallinity, grain size and domain boundaries, ranging from chains of Au-nanoparticles connected through semiconductor Ge crystallites to Au-seeded Ge single crystalline nanowires (see Figure 8). The conditions that control the type of Ge nanostructures produced were: (i) the distribution and size of the Au-seeds across the alumina surfaces, (ii) the type of SCF deposition, *e.g.* batch *vs* flow-through deposition and (iii) the confining environment of the AAO channels.

The synthesis of vertically-aligned Ge nanowires by combining a low temperature nanowire synthesis with the self-assembly of block co-polymer-templated nanoporous films has been reported by Jagannathan *et al* <sup>76</sup>. A 3 nm Au catalyst film was first deposited using electron beam evaporation onto a silicon wafer having 100 nm of thermal oxide. A mesoporous organosilicate film of ~330 nm in thickness was then self-assembled on top of the Au film. The nanowire growth was performed at a partial pressure of 1.8 Torr of germane using a source gas of 10 % germane diluted in hydrogen. All wires in the pores of the organosilicate film were observed to be polycrystalline and the Au catalyst was

found to be present at the tip of the nanowires. The density of the nanowires was found to increase with an increase in growth temperature resulting in close to 100 % filling of pores at 380 °C. Nevertheless the lack of well defined crystallinity and possible integration problems within such a high density nanowire array may hinder further implementation in future electronic devices.

#### 3.2 Germanium Nanowire Field Effect Transistors

Traditional CMOS manufacturing methods for gate electrode formation are not compatible with Ge-based devices as Ge does not grow a stable oxide which is critical for gate electode formation. However the fabrication of Ge-based devices has been made possible by the use of high-k dielectrics films such as hafnium oxide and zirconium oxide <sup>77,78</sup> which have been used to fabricate Ge nanowire FETs. Significantly this approach improves device performance to a certain degree. Using SiO<sub>2</sub> or ALD deposited high-k HfO<sub>2</sub> as gate dielectrics, p-Ge nanowire FETs have been fabricated by Dai et al using a low-temperature CVD method for both back- and top-gated structures 77, 78. The back-gated p-type Ge nanowire FETs showed high  $I_{on}/I_{off}$  ( $\geq 10^3$ ) and low resistances ( $\sim 500 \text{ k}\Omega$ ). The hole carrier mobility was higher than 600cm<sup>2</sup>/Vs, which is close to the highest reported value for Ge MOSFETs built on Ge wafers (~700cm<sup>2</sup>/Vs). As compared to back-gated Ge nanowire FETs, top-gated structures exhibited lower mobility due to the interface states between the HfO<sub>2</sub> and Ge nanowires. Lieber and co-workers have also fabricated p-type Ge nanowire FET 79 which exhibits high currents and transconductances similar to those reported by Dai et al. although the mobility in this case was much smaller because of the

unpassivated surfaces of the Ge nanowires. The above examples suggest that a precise control of the doping procedure and surface passivation may possibly provide a solution towards further improving the performance of Ge nanowire FETs.

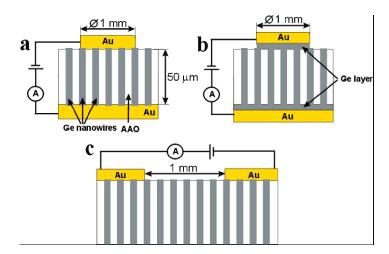

To date, the bulk of electrical transport measurements reported in the literature have focused on individual nanowires. However there are very few reports on the electrical properties of ordered arrays of nanowires. Within CRANN we have investigated the electrical properties of vertically aligned Ge nanowires within AAO and MTF templates <sup>40,80</sup> Conductive atomic force microscopy (C-AFM) was used to measure the electrical transport properties of individual nanowires within the arrays, while macrocontacts were used to measure the mean current-voltage characteristics of groups of nanowires (Figure 9). Contact resistance between the nanowires and metal macrocontacts was minimized by polishing and gradual etching the AAO surface, to expose the nanowires, prior to the deposition of the contacts. The C-AFM and macrocontact measurement methods provided approximately the same electrical resistivity results.

# 3.3 Surface Chemistry of Germanium Nanowire FETs

As mentioned above <sup>65-67</sup>, the electrical properties of Ge nanowire FETs are affected by the nature of the surface of the nanowire and hence it is reasonable to expect that passivation and functionalisation of the surface of Ge nanowires before deposition of the dielectric layer would be key step towards fabricating a high-performance device. Korgel *et al* and Dai *et al* have investigated the influence of surface states on the electron transport through both p-type and n-type Ge nanowire FETs <sup>65, 74, 77, 81, 82</sup>. They observed that

hysteresis behaviours in Ge nanowire FETs are caused by water molecules which are absorbed onto the surface oxides of the nanowires due to the electric dipole of the absorbed species. As compared to p-type Ge nanowire FETs, n-type Ge nanowire FETs were observed to be more susceptible to hysteresis behaviour due to Fermi level pining by interface states between Ge and surface oxides. A number of approaches have been utilised to prevent the oxidation of Ge nanowires. For example passivation via self-assembled crystalline monolayers of long chain alkanethiols ( $\geq$  12 carbons) has been used to protect Ge nanowires against oxidation in ambient air  $^{61}$ .. ALD grown high–k HfO<sub>2</sub> films could also be applied as the first layer of surface passivation. Thermal annealing in vacuum is also an efficient way to remove the germanium oxides from Ge surfaces and eliminate or reduce the hysteresis for Ge nanowire FETs.

Photoemission studies of the passivation of Ge nanowires grown by cold-wall CVD has revealed that as grown Ge nanowires are initially free of oxide and appear to be hydrogen passivated <sup>83</sup>. The nanowires were observed to progressively oxidize with time when exposed to air. HCl exposure after nanowire CVD growth appeared to produce a Cl passivation which was observed to be more stable than putative hydrogen passivation achieved by aqueous HF treatment.

#### 4. Ge/Si Core/Shell Nanowire FETs

Coaxial heterostructures of two single-crystalline semiconductor materials have significant technological potential. Heterostructured nanowires can serve as building blocks in directed assembled schemes. The interest in the electronic properties in Ge/Si core/shell nanowires is due to the indirect band gaps of Si and Ge <sup>84</sup>. In Ge/Si core/shell

heterostructures, free holes accumulate in the Ge channel when the Fermi level lies below the valance band edge of the Ge core. With this band structure design, it is possible to get high-performance Ge/Si core/shell heterostructure-based FETs.

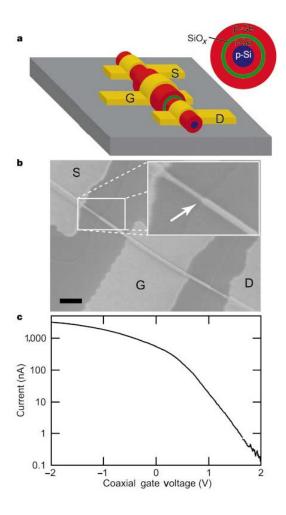

In 2002, Lauhon et al first published their results on the synthesis of core—multi-shell Si/Ge nanowires by a CVD-based epitaxial shell-growth method <sup>85</sup>. A high-performance coaxially gated FET consisted of a core-multi-shell structure: p-Si/ i-Ge/SiOx/p-Ge was successfully fabricated, where the active channel was the Si-Ge shell. This unoptimized device showed a maximum transconductance of 1.5 µA/V, which was comparable to results reported for carbon-nanotube FETs at that time. The coaxial geometry offers advantages for nano-FETs, such as a capacitance enhancements compared to standard planar gates used in nanowire FETs. The most significant success of this geometry is that some key parameters, such as gate dielectric thickness that control the device electrical properties, can be controlled during the initial synthesis stage. All this requires sub-nanometer control during the synthetic steps which in many cases is difficult to achieve and lacks necessary large scale reliability. Nevertheless conceptually these new core-multi-shell structures open up a new platform to study low-dimensional transport phenomena and show the general potential of radial heterostructure growth for the development of high-performance nanowire-based FETs. (Figure 10)

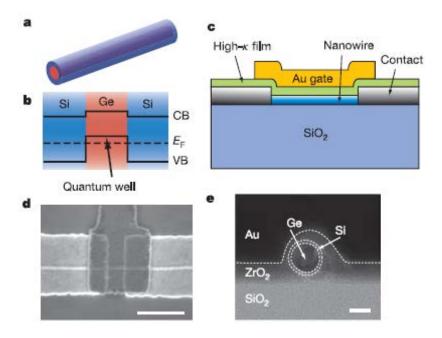

Top-gated single heterostructured nanowire FETs have been fabricated at cryogenic temperatures employing high-k dielectrics with a top gate geometry <sup>10, 84, 86, 87</sup>, with Au as the top gate and HfO<sub>2</sub> as the dielectric film (Figure 11). Devices with gate length of 190

nm have exhibited the best performance achieved to date in nanowire FET devices at room temperature. The on current ( $I_{on}$ ) and transconductance ( $g_m$ ) were three to four times greater than state-of-the-art Si p-MOSFETs. The sub-threshold slope (S) was superior to the best value reported for nanowire FETs while the hole mobility was much greater than the Si p-MOSFET, Ge and strained SiGe heterostructure PMOS devices. Furthermore, calculated intrinsic delay as a function of gate length for these nanowire FETs showed a significant speed advantage over Si p-MOSFETs. These results have demonstrated that there is great potential for such nanowire devices. The ability to prepare high-performance nanowire FETs with close to 100 % yield could find use in high-frequency electronics on plastic substrates, nanosensors with greater sensitivity, and even extend the roadmap for high-performance logic.

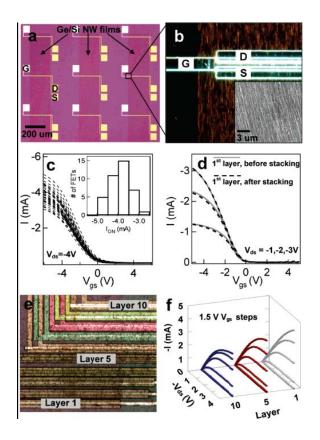

Using Ge/Si core/shell nanowires as building blocks, 3 D, multifunctional electronics can be developed <sup>88</sup>. Both five-layer top-gated single-nanowire FET and ten-layer top-gated multi-nanowire FET have been fabricated based on the layer-by-layer assembly (Figure 12). These devices have exhibited reproducible high-performance. Uniform characteristics and performance has been achieved in sequential layers.

A relative simple method has been developed to fabricate surround-gate (SG) core-shell Ge nanowire FETs based on individual and parallel arrays <sup>9</sup>. The individual SG nanowire FETs have exhibited more desirable on/off ratios and sub-threshold swings than Ge nanowire FETs with planar gate stacks. SG FETs with various numbers of wires, up to 50 in parallel in each transistor, have been fabricated and the electrical properties of such

devices were consistent with that of individual SG Ge NW FETs (Figure 13). It should be mentioned that major difficulties appear to be in the alignment and integration steps that hinder the demonstration of high performance and density of functional nanowire devices.

# 5. Mechanical Properties of Nanowires

In the drive to implement semiconducting nanowires into devices, their electronic properties have been extensively studied. Nevertheless, mechanical behaviour has received much less attention particularly due to the difficulty in handling these materials which makes manipulation and especially mechanical measurements a considerable challenge. However, the mechanical properties of semiconductor nanowires are of paramount importance in device processing as these building blocks undergo changes in temperature, induced strain and external stress. These stimuli can generate dislocations inside the wire and hence change its electrical conductivity. The processing of VLSI (very large scale integration) induces compressive and tensile stresses via deposition of different materials which can cause failure mainly due to delamination and electro-migration.

One dimensional systems are expected to have interesting mechanical properties due to their high ratio of surface to bulk atoms and the reduced number of defects per unit length. The *Young's modulus* is defined as the ratio of stress over strain, and the *stress* is defined as the ratio of force applied over the area onto which this force is acting. For homogenous materials, simple elastic theory shows that the Young's modulus, E, reflects the average binding forces between the atoms <sup>89</sup>. Therefore, at reduced dimensions, the modulus should become sensitive to the increased fraction of surface atoms and to possible surface tension effects <sup>90, 91</sup>. Different fracture behaviour, enhanced Young's modulii and

strengths or improved elastic properties are expected from nanowires. Many research groups have performed mechanical measurements on individual nanowires, adopting different approaches; predominantly using either an AFM or home-built system incorporated within a TEM.

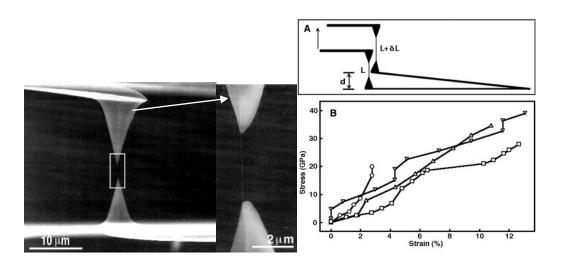

In 1997, Wong et al <sup>92</sup>studied the elastic strength and toughness of silicon carbide nanorods and multi-walled carbon nanotubes (MWNT) using an AFM based technique. nanomaterials were first dispersed on a flat surface, and pinned to it by lithographically patterned arrays of SiO<sub>2</sub> squares. An AFM tip was then used to directly measure the force-displacement (F-d) characteristics at different distances from the pinning points and hence the Young's modulus and the bending strength were determined. In addition, a lower boundary for stored strain energy was calculated and showed to be about 10 times higher in MWNTs than in SiC nanorods. This experiment highlighted the potential applications of MWNTs and carbide rods as reinforcement in ceramics or polymer composites. Later, Poncharal and co-workers 93 reported a method involving electrical excitations of MWNTs at their resonance frequency in-situ in a TEM and simultaneously measured the induced dynamic deflection of the tube. The Young's modulus was calculated from the resonant frequency and the dimensions of the wire and was found to decrease sharply with increasing diameter. This was accounted for by the wavelike distortions occurring on the inner arc of bent nanotubes. This method was also applied to a Kelvin probe based on nanotubes and a nanobalance able to measure in the picogram to femtogram range. Yu et al 94 used a nano-stressing stage inside a SEM and recorded the entire experiment on video, enabling real-time characterization of the deformation. In

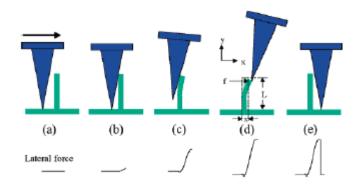

these experiments, individual MWNTs were picked up and attached onto the opposing tips of AFM cantilever probes, as seen in Figure 14. This experiment mimics quite accurately a classical macroscale tensile load experiment and hence allows the calculation of a wide range of mechanical properties, such as the force at fracture, the Young's modulus and the tensile strength. These were found to range from 270 to 950 GPa and from 11 to 63 GPa, respectively. TEM imaging also revealed different fracture patterns such as wavelike structures, ribbon-like distortions and radial collapses <sup>95</sup>. An AFM-based technique was developed by Song et al 96 in 2005 and has the key advantage of being non destructive towards the nanowire. An AFM in contact mode scans the surface which is covered with vertically aligned nanowires. The elastic modulus was determined by simultaneously recording the topography and lateral force when the tip scans across the aligned arrays, as shown in Figure 15. Prior to touching a nanowire, a small lateral force is observed (Figure 15(a)). When the tip comes in contact with the wire, the force increases almost linearly as the nanowire is elastically bent from its equilibrium position (Figure 15(b), (c)). At the largest deflection (Figure 15(d)), the tip crosses the top of the wire and the nanowire is then released (Figure 15(e)). However, since no F-d curves were recorded, the behaviour of the wire during manipulation is unknown; it was assumed to be due to bending forces only. This technique was recently improved by Hoffmann and co-workers <sup>97</sup> by setting up an AFM inside an SEM. The AFM tip was used to bend standing silicon nanowires until The maximum stress before fracture was then calculated and found to be 12 GPa. A correlation between strength and length was also reported, such that shorter nanowires tend to have greater fracture strength than longer ones. In addition, a simulation of the stress showed that the maximum stress appeared at the pinning point of the wire.

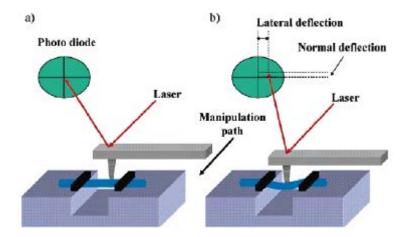

An advancement in this AFM technique was developed by Wu et al <sup>98</sup> who overcame the friction issues caused by the nanowires being deposited on a flat surface (Figure 16). method is very reproducible and provides a wide range of mechanical properties such as Young's modulus, yield strength, plastic deformation and force at failure. Nanowires, pinned on either side of a trench, are laterally loaded by an AFM tip while the F-d curves are recorded. Thanks to a x-y-z closed loop scanner, the tip can be positioned extremely accurately at the loading point (centre of spanning nanowire) and deep enough into the trench to avoid slipping. By imaging the wire before and after manipulation, one can ensure the wire failed at the load point (and not at the pinning points) and that slippage at the pinning lines does not occur. Therefore, the signal recorded is only due to wire deformation. In this manner, the Young's modulus of silicon and germanium nanowires and the maximum strength of germanium nanowires were determined and a generalized model was established 99, 100 for this double-clamped beam configuration. The latter provides a comprehensive description of F-d curves and enables the mechanical properties to be determined. The key advantage of this model is that it accounts for both bending and stretching of the wire, therefore reflecting both linear and non-linear behaviour.

Table 2 presents the values for the Young's modulus (which depends on the crystal orientation) and the fracture strength for bulk silicon and bulk germanium <sup>101, 102</sup>. Table 3 displays the same constants for silicon and germanium nanowires <sup>97, 99, 103-106</sup>. For all the different techniques, the wire systems exhibit elastic behaviour leading to brittle fracture. To date, quite large nanowires have been characterized (over 20 nm in radius), therefore the

elastic constants are close to the bulk values. However, the smallest wires (20 nm in radius) are remarkably flexible as they can be elastically deformed up to 15 times their radii <sup>100</sup>. This ability to store elastic energy suggests potential applications in the field of sensors and nano electromechanical systems (NEMS).

# 6. Summary and Perspective

1 D nanostructures exhibit critical device function, and thus can be exploited as device elements in future architectures for nanosystems. Semiconductor nanowires are expected to play an important role as building blocks for novel nanoscale electronics assembled without the need for complex and costly fabrication facilities. Several performance requirements outlined in the ITRS roadmap have been demonstrated (such as nanowire length and maximum saturation current density) or are very close to meeting the specification, such as a diameter of 3 nm (< 5nm demonstrated <sup>107</sup>), doping of 10<sup>18</sup>-10<sup>19</sup> cm<sup>-3</sup> (2 x  $10^{18}$  cm<sup>-3</sup> demonstrated  $^{108}$ ) and resistivity of 5000 - 40,000  $\mu\Omega$  cm (30,000  $\mu\Omega$ cm demonstrated <sup>109</sup>), as shown in Table 4. However, some key challenges remain. Progress has been made towards controlling placement of nanowire devices using various approaches such as block copolymer patterning 109. However reliable angular placement accuracy, specified as 0.6 deg by the ITRS remains to be demonstrated. Nanowire devices typically utilise metal contacts, which can result in ambipolar conduction <sup>110</sup> While the ITRS calls for a contact resistance of less than 10 % of the nanowire resistance, a key challenge will be to achieve this using conventional implanted or diffused p-n junctions. The ITRS also calls for non Au catalysts for nanowire growth for reasons of CMOS compatibility. Additionally, most of the research so far has mainly focused on the growth, placement and electrical contacting of nanowires but the mechanical robustness of these structures when they are processed into devices needs to be studied in more detail.

# 6. Acknowledgement

The authors acknowledge CRANN, SFI, IRCSET and the ERAF for financial support. JDH especially wishes to thank Peter Gleeson for his valuable input into this paper.

## **References**

- (1) Huang, Y.; Lieber, C. M. Pure Appl. Chem. 2004, 76, 2051.

- (2) Lieber, C. M.; Wang, Z. L. MRS Bull. 2007, 32, 99.

- (3) Dai, H. J. Accounts Chem. Res. 2002, 35, 1035.

- (4) Yu, B.; X. Sun, X. H.; Calebotta, G. A.; Dholakia, G. R.; Meyyappan, M. J. Clust. Sci. 2006, 17, 579.

- (5) Agarwal, P.; Vijayaraghavan, M. N.; Neuilly, F.; Hijzen, E.; Hurkx, G. A. M. Nano Lett. 2007, 7, 896.

- (6) Chan, C. K.; Peng, H.; Lui, G.; McIlwrath, K.; Zhang, X. F.; Huggins, R. A.; Cui, Y. *Nature Nanotech.* **2008**, *3*, 31.

- (7) Bjork, M. T.; Hayden, O.; Schmid, H.; Riel, H.; Riess; W. Appl. Phys. Lett. 2007, 90.

- (8) Cui, Y.; Zhong, Z. H.; Wang, D. L.; Wang, W. U.; Lieber, C. M. Nano Lett. 2003, 3, 149.

- (9) Zhang, L.; Tu, R.; Dai, H. J. Nano Lett. 2006, 6, 2785.

- (10) Li, Y.; Qian, F.; Xiang, J.; Lieber, C. M. *Mater. Today* **2006**, *9*, 18.

- (11) Wang, D. W. B. A. Sheriff, J. R. Heath, *Nano Lett.* **2006**, *6*, 1096.

- (12) Saraswat, K. C.; Chui, C. O.; Krishnamohan, T.; Nayfeh, A.; McIntyre, P. *Microelectron. Eng.* **2005**, 80, 15.

- (13) Moore, G. E. *Electronics* **1965**, *38*, 84.

- (14) The International Technology Roadmap for Semiconductors Edition Report, 2005, http://www.itrs.net/Links/2007ITRS/Home2007.htm.

- (15) Khanal, D. R.; Yim, J. W. L.; Walukiewicz, W.; Wu, J. Nano Lett. 2007, 7, 1186.

- (16) Andersen, S. E. S.; Brenner, R.; Wellard, C. J.; Yang, C.; Hopf, T.; Escott, C. C.; Clark, R. G.; Dzurak, A. S.; Jamieson, D. N.; Hollenberg, C. L. *Nano Lett.* **2007**, *7*, 2000.

- (17) Tilke, A. T.; Simmel, F. C.; Lorenz, H.; Blick, R. H.; Kotthaus, J. P. *Phys.l Rev. B* **2003**, *68*, 075311.

- (18) Wong, H. S. P. Solid-State Electron. 2005, 49, 755.

- (19) Buin, A. K.; Verma, A.; Svizhenko, A.; MAnantram, M. P. Nano Lett. 2008, 8, 760.

- (20) Whang, S. J.; Lee, S. J.; Yang, W. F.; Cho, B. J. Appl. Phys. Lett. **2007**, 91, 072105.

- (21) Chaudhry, A.; Ramamurthi, V.; Fong, E.; Islam, M. S. *Nano Lett.* **2007**, *7*, 1536.

- (22) Ma, D. D.; Lee, C. S.; Lee, S. T. Appl. Phys. Lett. 2001, 79, 2468.

- (23) Jin, S.; Whang, D. M.; McAlpine, M. C.; Friedman, R. S.; Wu, Y.; Lieber, C. M. *Nano Lett.* **2004**, *4*, 915.

- (24) Zheng, G. F.; Lu, W.; Jin, S.; Lieber, C. M. Adv. Mater. 2004, 16, 1890.

- (25) Giovine, E.; Notargiacomo, A.; Di Gaspare, L.; Palange, E.; Evangelisti, F.; Leoni, R.; Castellano, G.; Torrioli, G.; Foglietti, V. *Nanotech.* **2001**, *12*, 132.

- (26) Liu, J. L. Lu, Y.; Shi, Y.; Gu, S. L.; Jiang, R. L.; Wang, F.; Bu, H. M.; Zheng, Y. D. *Phys. Status Solidi A-Appl. Res.* **1998**, *168*, 441.

- (27) Tang, Y. H.; Zhang, Y. F.; Wang, N.; Shi, W. S.; Lee, C. S.; Bello, I.; Lee, S. T.; *J. Vac. Sci. Technol. B* **2001**, *19*, 317.

- (28) Beckman, R. A.; Johnston-Halperin, E.; Melosh, N. A.; Luo, Y.; Green, J. E.; Heath, J. R. *J. Appl. Phys.* **2004**, *96*, 5921.

- (29) Bogart, T. E.; Dey, S.; Lew, K. K. Mohney, S. E.; Redwing, J. M. Adv. Mater. 2005, 17, 114.

- (30) Cui, Y.; Lauhon, L. J.; Gudiksen, M. S.; Wang, J. F.; Lieber, C. M. Appl. Phys. Lett. 2001, 78, 2214.

- (31) Wu, Y.; Cui, Y.; Huynh, L.; Barrelet, C. J.; Bell, D. C.; Lieber, C. M. Nano Lett. 2004, 4, 433.

- (32) McAlpine, M. C.; Friedman, R. S.; Jin, S.; Lin, K. H.; Wang, W. U.; Lieber, C. M. *Nano Lett.* **2003**, *3*, 1531.

- (33) Whang, D.; Jin, S.; Lieber, C. M. *Jpn. J. Appl. Phys. Part 1 Regul. Pap. Short Notes Rev. Pap.* **2004**, 43 4465

- (34) Whang, D.; Jin, S.; Wu, Y.; Lieber, C. M. *Nano Lett.* **2003**, *3*, 1255.

- (35) Lew, K. K.; Pan, L.; Bogart, T. E.; Dilts, S. M.; Dickey, E. C.; Redwing, J. M.; Wang, Y. F.; Cabassi, M.; Mayer, T. S.; Novak, S. W. *Appl. Phys. Lett.* **2004**, *85*, 3101.

- (36) Lombardi, I.; Hochbaum, A. I.; Yang, P. D.; Carraro, C.; Maboudian, C. R. *Chem. Mater.* **2006**, *18*, 988.

- (37) Lew, K. K.; Reuther, C.; Carim, A. H.; Redwing, J. M.; Martin, B. R. J. Vac. Sci. Technol. B 2002, 20, 389.

- (38) Lew, K. K.; Redwing, J. M. J. Cryst. Growth 2003, 254, 14.

- (39) Mohammad, A. M.; Dey, S.; Lew, K. K.; Redwing, J. M.; Mohney, S. E. J. Electrochem. Soc. 2003, 150, G577.

- (40) Erts, D.; Polyakov, B.; Daly, B.; Morris, M. A.; Ellingboe, S.; Boland, J. D. Holmes, J. D. J. Phys. Chem. B 2006, 110, 820.

- (41) Cui, Y.; Lieber, C. M. Science **2001**, 291, 851.

- (42) Yu, J. Y.; Chung, S. W.; Heath, J. R. J. Phys. Chem. B 2000, 104, 11864.

- (43) Cui, Y.; Duan, X. F.; Hu, J. T.; Lieber, C. M. J. Phys. Chem. B 2000, 104, 5213.

- (44) Lu, W.; Lieber, C. M. J. Phys. D-Appl. Phys. 2006, 39, R387.

- (45) Chen, Z. H.; Appenzeller, J.; Knoch, J.; Lin, Y. M.; Avouris, P. *Nano Lett.* **2005**, *5*, 1497.

- (46) Zhong, Z. H.; Fang, Y.; Lu, W.; Lieber, C. M. Nano Lett. 2005, 5, 1143.

- (47) Landman, U.; Barnett, R. N.; Scherbakov, A. G.; Avouris, P. Physical Review Letters 2000, 85, 1958.

- (48) Mohney, S. E.; Wang, Y. F.; Cabassi, M. A.; Lew, K. K.; Dey, S.; Redwing, J. M.; Mayer, T. S. *Solid-State Electron.* **2005**, *49*, 227.

- (49) Wang, Y. F.; Lew, K. K.; Ho, T. T.; Pan, L.; Novak, S. W.; Dickey, E. C.; Redwing, J. M.; Mayer, T. S. *Nano Lett.* **2005**, *5*, 2139.

- (50) Eichfeld, S. M.; Ho, T.-T.; Eichfeld, C. M.; Cranmer, A.; Mohney, S. E.; Mayer, T. S.; Redwing, J. M. Nanotech. 2007, 18, 315201.

- (51) Dilts, S. M.; Mohammad, A.; Lew, K.-K.; Redwing, J. M.; Mohney, S.E. "Fabrication and Electrical Characterization of Silicon Nanowire Arrays", Warrendale, **2005**.

- (52) Lasky, J. B.; Nakos, J. S.; Cain, O. J.; P. J. Geiss, P. J. IEEE Trans. Electron Devices 1991, 38, 262.

- (53) Taur, Y.; Sun, J. Y. C.; Moy, D.; Wang, L. K.; Davari, B.; Klepner, S. P.; Ting, C. Y. *IEEE Trans. Electron Devices* **1987**, *34*, 575.

- (54) Jeon, H.; Sukow, C. A.; Honeycutt, J. W.; Rozgonyi, G. A.; Nemanich, R. J. J. Appl. Phys. 1992, 71, 4269.

- (55) Kunishima, I.; Suguro, K.; Aoyama, T.; Matsunaga, J. Jpn. J. Appl. Phys. Part 2 Lett. 1990, 29, L2329.

- (56) Zhang, S. L.; Smith, U.; J. Vac. Sci. Technol. A **2004**, 22, 1361.

- (57) Morimoto, T.; Momose, H. S.; Iinuma, T.; Kunishima, I.; Suguro, K.; Okano, H.; Katakabe, I.; Nakajima, H.; Tsuchiaki, M.; Ono, M.; Katsumata, Y.; Iwai, H. *IEDM Tech. Dig.* **1991**, 653.

- (58) Iwai, H.; Ohguro, T.; Ohmi, S.; Microelectron. Eng. 2002, 60, 157.

- (59) Morimoto, T.; Ohguro, T.; Momose, H. S.; Iinuma, T.; Kunishima, I.; Suguro, K.; Katakabe, I.; Nakajima, H.; Tsuchiaki, M.; Ono, M.; Katsumata, Y.; Iwai, H. *IEEE Trans. Electron Devices* **1995**, 42, 915.

- (60) Inaba, S.; Okano, K.; Matsuda, S.; Fujiwara, M.; Hokazono, A.; Adachi, K.; Ohuchi, K.; Suto, H.; Fukui, H.; Shimizu, T.; Mori, S.; Oguma, H.; Murakoshi, A.; Itani, T.; Iinuma, T.; Kudo, T.; Shibata, H.; Taniguchi, S.; Takayanagi, M.; Azuma, A.; Oyamatsu, H.; Suguro, K; Katsumata, Y.; Toyoshima, Y.; Ishiuchi, H. IEEE Trans. Electron Devices 2002, 49, 2263.

- (61) Wu, Y.; Xiang, J.; Yang, C.; Lu, W.; Lieber, C. M. *Nature* **2004**, *430*, 61.

- (62) Weber, W. M.; Geelhaar, L.; Graham, A. P.; Unger, E.; Duesberg, G. S.; Liebau, M.; Pamler, W.; Cheze, C.; Riechert, H.; Lugli, P.; Kreupl, F. *Nano Lett.* **2006**, *6*, 2660.

- (63) Schmidt, V.; Riel, H.; Senz, S.; Karg, S.; Riess, W.; Gosele, U. Small 2006, 2, 85.

- (64) Goldberger, J.; Hochbaum, A. I.; Fan, R.; Yang, P. D. *Nano Lett.* **2006**, *6*, 973.

- (65) Hanrath, T.; Korgel, B. A. J. Phys. Chem. B 2005, 109, 5518.

- (66) Nguyen, P.; Ng, H. T.; Meyyappan, M. Adv. Mater. 2005, 17, 549.

- (67) Heath, J. R.; Legoues, F. K. Chem. Phys. Lett. 1993, 208, 263.

- (68) Schricker, A. D.; Joshi, S. V.; Hanrath, T.; Banerjee, S. K.; Korgel, B. A. J. Phys. Chem. B 2006, 110, 6816.

- (69) Gu, G.; Burghard, M.; Kim, G. T.; Duesberg, G. S.; Chui, P. W.; Krstic, V.; Roth, S. J. Appl. Phys. **2001**, 90, 5747.

- (70) (a) A. M. Morales, C. M. Lieber, *Science* **1998**, 279, 208. Sutter E.; Sutter, P. *Nano Lett.* **2008**, 8,

- (71) Wang, D. W.; Dai, H. J.; Angew. Chem.-Int. Edit. 2002, 41, 4783.

- (72) Wang, D. W.; Tu, R.; Zhang, L.; Dai, H. J. Angew. Chem.-Int. Edit. 2005, 44, 2925.

- (73) Tutuc, E.; Guha, S.; Chu, J. O. Appl. Phys. Lett. 2006, 88.

- (74) Wang, D. W.; Chang, Y. L.; Liu, Z.; Dai, H. J. J. Am. Chem. Soc. 2005, 127, 11871.

- (75) Woodruff, J. H.; Ratchford, J. B.; Goldthorpe, I. A.; McIntyre, P. C.; Chidsey, C. E. D. *Nano Lett.* **2007**, 7, 1637.

- (76) Jagannathan, H.; Deal, M.; Nishi, Y.; Kim, H. C.; Freer, E. M.; Sundstrom, L.; Topuria, T.; Rice, P. M. *J. Vac. Sci. Technol. B* **2006**, *24*, 2220.

- (77) Wang, D.; Dai, H. Appl. Phys. A-Mater. Sci. Process. 2006, 85, 217.

- (78) Wang, D. W.; Wang, Q.; Javey, A.; Tu, R.; Dai, H. J.; Kim, H.; McIntyre, P. C.; Krishnamohan, T.; Saraswat, K. C. *Appl. Phys. Lett.* **2003**, *83*, 2432.

- (79) Greytak, A. B.; Lauhon, L. J.; Gudiksen, M. S.; Lieber, C. M. Appl. Phys. Lett. 2004, 84, 4176.

- (80) Ziegler, K. J.; Polyakov, B.; Kulkarni, J. S.; Crowley, T. A.; Ryan, K. M.; Morris, M. A.; Erts, D.; Holmes, J. D. *J. Mater. Chem.* **2004**, *14*, 585.

- (81) Wang, D. W.; Y. L. Chang, Y. L.; Wang, Q.; Cao, J.; Farmer, D. B.; Gordon, R. G.; Dai, H. J. J. Am. Chem. Soc. 2004, 126, 11602.

- (82) Hanrath, T.; Korgel, B. A. J. Am. Chem. Soc. 2004, 126, 15466.

- (83) Adhikari, H.; McIntyre, P. C.; Sun, S. Y.; Pianetta, P.; Chidsey, C. E. D. Appl. Phys. Lett. 2005, 87.

- (84) Lu, W.; Xiang, J.; Timko, B. P.; Wu, Y.; Lieber, C. M. Proc. Natl. Acad. Sci. U. S. A. 2005, 102, 10046.

- (85) Lauhon, L. J.; Gudiksen, M. S.; Wang, C. L.; Lieber, C. M. *Nature* **2002**, 420, 57.

- (86) Xiang, J.; Lu, W.; Hu, Y. J.; Wu, Y.; Yan, H.; Lieber, C. M. *Nature* **2006**, *441*, 489.

- (87) Liang, G. C.; Xiang, J.; Kharche, N.; Klimeck, G.; C. Lieber, C. M.; Lundstrom, M. *Nano Lett.* **2007**, 7, 642.

- (88) Javey, A.; Nam, S.; Friedman, R. S.; Yan, H.; Lieber, C. M. Nano Lett. 2007, 7, 773.

- (89) Wooster, W. A. Reports on Progress in Physics 1953, 16, 62.

- (90) Cammarata, R. C. Phys. Rev. Lett. 1989, 62, 2005.

- (91) Chen, C. Q.; Zhang, Y. S.; Zhhu, J.; Yan, Y. J. Phys. Rev. Lett. 2006, 96, 075505.

- (92) Eric, W.; Wong, P. E. Science **1997**, 277, 1971.

- (93) Poncharal, P.; Ugarte, D.; de Heer, W. A. Science **1999**, 283, 1513.

- (94) Yu, M.-F.; Dyer, M. J.; Moloni, K.; Kelly, T. F.; Ruoff, R. S. Science 2000, 287, 637.

- (95) Ruoff, R. S.; Lorent, D. C.; Subramani, S.; Chan, B. *Nature* **1993**, *364*, 514.

- (96) Song, J.; Riedo, E.; Wang, Z. L. *Nano Lett.* **2005**, *5*, 1954.

- (97) Hoffmann, S.; Moser, B.; Michler, J.; Christiansen, S. H.; Schmidt, V.; Senz, S.; Werner, P.; Gosele, U.; Ballif, C. *Nano Lett.* **2006**, *6*, 622.

- (98) Wu, B.; Heidlelberg, A.; Boland, J. J. Nature Mater. 2005, 4, 525.

- (99) Heidlelberg, A.; Ngo, L. T.; Wu, B.; Phillips, M. A.; Sharma, S.; Kamins, T. I.; Sader, J. E.; Boland, J. J. *Nano Lett.* **2006**, *6*, 1101.

- (100) Ngo, L. T.; Almecija, D. A.; Sader, J. E.; Daly, B.; Petkov, N.; Holmes, J. D.; Erts, D.; Boland, J. J. *Nano Lett.* **2006**, *6*, 2964.

- (101) Roundy, D. Phys. Rev. B 2001, 64, 212103.

- (102) Wortman, J. J. J. Appl. Phys. 1965, 36, 153.

- (103) Kang, K. Philosophical Magazine 2007, 87, 2169.

- (104) Menon, M.; Srivastava, D.; Ponomareva, I.; Chernozatonskii, L. A. Phys. Rev. B. 2004, 70, 125313.

- (105) San Paulo, A.; Howe, R. T.; He, R.; Yang, P.; Gao, D.; Carraro, C.; Maboudian, R. *Appl. Phys. Lett.* **2005**, 87, 053111.

- (106) Tabib-Azar, M.; Wang, R.; Sharma, S.; Kamins, T. I.; Islam, M. S.; Williams, R. S. *Appl. Phys. Lett.* **2005**, 87, 113102.

- (107) Singh, N.; Agarwal, A.; Bera, L. K.; Liow, T. Y.; Yang, R.; Rstagi, S. C.; Tung, C. H.; Kumar, R.; Lo, G. Q.; Balasubramanian, N.; Kwong, D.-L. *IEEE Elec. Dev. lett.* **2006**, *27*, 5.

- (108) Seo, K.; Sharma, S.; Yasseri, A. A.; Stewart, D. R.; Kamins, T. I. Electrochem. Sol. Staate Lett. 2006, 9, G69.

- (109) Black, C. T. Appl. Phys. lett. 2005, 87, 163116.

- (110) Chau, R.; datta, S.; Doczy, M.; Doyle, B.; Jin, B.; Kavalieros, J.; Majumdar, A.; Metz, M.; Radosavlijevic, M. *IEEE Trans. Nanotech.* **2005**, *4*, 2.

- (111) Yeo, K. H.; Suk, Y. S.; Li, M.; Yeoh, Y.-Y.; Cho, K. H.; Hong, K.-H.; Yun, S. K.; Lee, M. S.; Cho, N.; Lee, K.; Hwang, D.; Park, B.; Kim, D.-W.; Park, D.; Ryu, B.-I. *IEDM Tech. Digest* **2006**, paper 20.2

**Table 1.** ITRS2007 Long-term Technology Requirements—Double-gate MOSFETs (HP: high performance; LSTP: low standby power; LOP: low operation power) <sup>14</sup>.

| Year                            |      | 2016     | 2017     | 2018     | 2019     | 2020     | 2021     | 2022     |

|---------------------------------|------|----------|----------|----------|----------|----------|----------|----------|

| Node(nm)                        |      | 22       | 20       | 18       | 16       | 14       | 13       | 11       |

| Lg(nm)                          | HP   | 9        | 8        | 7        | 6        | 5.6      | 5.0      | 4.5      |

|                                 | LSTP | 14       | 13       | 12       | 11       | 10       | 9        | 8        |

|                                 | LOP  | 11       | 10       | 9        | 8        | 7        | 6.5      | 6        |

| $V_{dd}(V) \\$                  | HP   | 0.8      | 0.7      | 0.7      | 0.7      | 0.65     | 0.65     | 0.65     |

|                                 | LSTP | 0.8      | 0.8      | 0.8      | 0.75     | 0.75     | 0.7      | 0.7      |

|                                 | LOP  | 0.6      | 0.5      | 0.5      | 0.5      | 0.5      | 0.45     | 0.45     |

| $V_{t,\;sat}(mV)$               | HP   | 110      | 109      | 114      | 119      | 123      | 115      | 118      |

|                                 | LSTP | 366      | 371      | 365      | 374      | 378      | 369      | 376      |

|                                 | LOP  | 202      | 188      | 194      | 190      | 195      | 190      | 201      |

| $I_{off}(DG)$ ( $\mu A/\mu m$ ) | НР   | 0.44     | 0.48     | 0.45     | 0.47     | 0.43     | 0.62     | 0.60     |

|                                 | LSTP | 2.97E-05 | 2.55E-05 | 3.38E-05 | 2.62E-05 | 2.39E-05 | 3.38E-05 | 2.89E-05 |

|                                 | LOP  | 1.31E-02 | 2.23E-02 | 1.94E-02 | 2.55E-02 | 2.41E-02 | 3.26E-02 | 2.40E-02 |

| $I_{on}(DG)$ $(\mu A/\mu m)$    | НР   | 2627     | 2533     | 2804     | 2768     | 2677     | 2799     | 2786     |

|                                 | LSTP | 738      | 839      | 889      | 895      | 935      | 934      | 946      |

|                                 | LOP  | 916      | 808      | 850      | 900      | 919      | 874      | 876      |

| E <sub>OT</sub> (DG)<br>(Å)     | НР   | 5.5      | 5.5      | 5.5      | 5        | 5        | 5        | 5        |

|                                 | LSTP | 11       | 10       | 10       | 9        | 9        | 8        | 8        |

|                                 | LOP  | 8        | 7        | 7        | 7        | 7        | 6        | 6        |

Table 2. Young's modulus (E) and fracture strength ( $\sigma$ ) for bulk Si and Ge

|           | E(GPa)      | σ (GPa)           |

|-----------|-------------|-------------------|

| Silicon   | 135-190 102 | 22 101            |

| Germanium | 103-150 102 | 14 <sup>101</sup> |

**Table 3.** Young's modulus (E), fracture strength  $(\sigma)$  and bending strength  $(\sigma_b)$  for Si and Ge nanowires acquired by AFM techniques and theoretical calculations.

|                                     | Si                                                                                              | Ge nanowires                            |                                                 |                                       |                                       |

|-------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------|---------------------------------------|---------------------------------------|

|                                     | E (GPa)                                                                                         | σ (GPa)                                 | σ <sub>b</sub> (GPa)                            | E (GPa)                               | σ (GPa)                               |

| AFM<br>techniques                   | 210 <sup>106</sup> , 158 <sup>99</sup> , 186 <sup>105</sup>                                     | 12 <sup>97</sup>                        | 0.3-0.85 <sup>106</sup> ,<br>17.5 <sup>97</sup> | 112 100                               | 15 <sup>100</sup>                     |

| Calculations only: brittle behavior | 147.3 <sup>104</sup> (t)<br>94.43 <sup>104</sup> (c)<br>165 <sup>103</sup> , 139 <sup>103</sup> | 22.7 <sup>103</sup> 13.2 <sup>103</sup> |                                                 | 160 <sup>103</sup> 125 <sup>103</sup> | 19 <sup>103</sup> 11.1 <sup>103</sup> |

t = tetrahedral nanowire, c = cage-like nanowire

**Table 3.** From ITRS 2007 Table ERM4 Emerging Research Materials - Demonstrated and Projected Parameters <sup>14</sup>.

| Parameter                                        | Requirement  |                                                        |  |  |

|--------------------------------------------------|--------------|--------------------------------------------------------|--|--|

| Diameter (nm)                                    | Goal         | 3-200                                                  |  |  |

|                                                  | Demonstrated | < 5 <sup>107</sup> - 200 <sup>108</sup>                |  |  |

| Angular placement accuracy                       | Goal         | ~10 <sup>-2</sup> radians (0.6 deg)                    |  |  |

|                                                  | Demonstrated | -                                                      |  |  |

| Length (µm)                                      | Goal         | 2                                                      |  |  |

|                                                  | Demonstrated | Si >20 (12 nm diameter)                                |  |  |

| Doping [electrically active] (cm <sup>-3</sup> ) | Goal         | ~10 <sup>18</sup> - 10 <sup>19</sup>                   |  |  |

|                                                  | Demonstrated | Si ~2x10 <sup>18 (108)</sup>                           |  |  |

| Resistivity (μΩ cm)                              | Goal         | 5000 - 40,000                                          |  |  |

|                                                  | Demonstrated | 30,000 108                                             |  |  |

| Contact resistance                               | Goal         | < 10 % nanowire resistance                             |  |  |

|                                                  | Demonstrated | Ohmic                                                  |  |  |

| Maximum current density (A/cm <sup>2</sup> )     | Goal         | Bulk                                                   |  |  |

|                                                  | Demonstrated | $I_{Dsat} = 1.94 \text{mA/} \mu \text{m (pFET)}^{111}$ |  |  |

|                                                  |              | $I_{Dsat} = 1.44$ mA/ $\mu$ m (nFET) $^{111}$          |  |  |

**Figure 1.** (a) Low magnification and (b) high magnification SEM images of vertically aligned, diameter-controlled Si nanowires grown from ordered Au dots on Si(111) substrates: the average diameter of the wires is 72 nm <sup>36</sup>.

**Figure 2.** (a) SEM image of a typical Si nanowire device with four contacts used for four-probe transport measurements. (b)  $I_{ds}$  versus  $V_{ds}$  data recorded on a Si nanowire using two-probe (green) and four-probe (red) contact geometries; the Si/P ratio was 500:1, (c)  $I_{ds}$  versus  $V_{ds}$  data recorded on a Si nanowire using two-probe (green) and four-probe (red) contact geometries; the Si/P ratio was 4000:1 and (d) measured (blue triangles) and intrinsic (red circles) mobility values, where the intrinsic values were obtained after correcting for contact resistance  $^{41}$ .

**Figure 3.** Fabrication of Si nanowire SBFETs with shortened active region: (a) n++-Si substrate (common back gate) is covered with a 300 nm thick SiO<sub>2</sub> gate dielectric. Recessed Co/Ti contacts are patterned by photolithography prior to the dispersion of the Si nanowires on top of the substrate, (b) conformal and selective electroless deposition of Ni on Co, embedding the Si nanowires as seen in the SEM top view (c). Annealing leads to Ni silicide segments along the nanowires adjacent to the Ni pads, shortening the length of the active region from LG0 to LG' (d) as shown in the SEM top view (e). The scalebars in (c) and (e) are 200 nm  $^{41}$ .

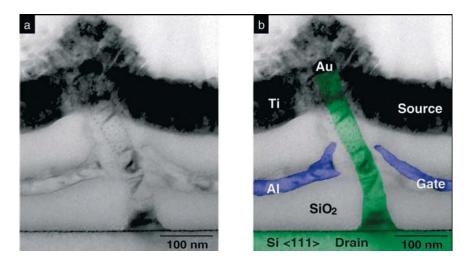

**Figure 4.** (a) TEM image of a silicon nanowire VS-FET (exclusively produced for TEM study) and (b) colored TEM image (green: silicon, blue: aluminum) <sup>63</sup>.

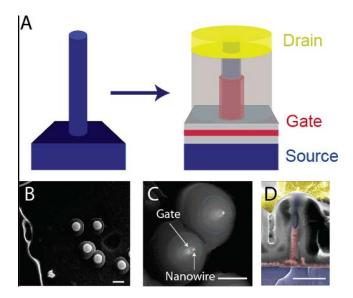

**Figure 5.** VINFET device configuration: (a) cartoon schematic of a VINFET device (right) fabricated from vertical silicon nanowires (left), (b) top-view SEM image of a completed VINFET device, scale bar is  $2 \mu m$ , (c) top-view SEM image of the midsection of the VINFET device, highlighting the conformal gate surrounding the nanowire channel, scale bar is  $1\mu m$ . SEM images (b) and (c) are obtained with a  $30^{\circ}$  tilt. (d) cross-sectional SEM image of a VINFET device. Scale bar is 500 nm. False color is added to image (d), for clarity. In (a) and (d), blue corresponds to the Si source and the nanowire, gray corresponds to the SiO<sub>2</sub> dielectric, red corresponds to the gate material and yellow corresponds to the drain metal  $^{64}$ .

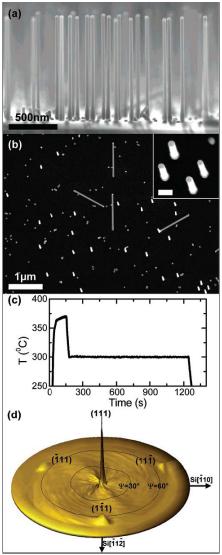

**Figure 6.** (a) Cross-section SEM of Ge nanowires grown epitaxially on Si(111) substrates from 40 nm gold colloids deposited using the HF-addition method, showing predominantly vertically oriented Ge nanowires of uniform diameter and length, (b) plan-view SEM of the sample in (a) showing the other three  $\langle 111 \rangle$  growth directions and (b) inset magnified view of vertical Ge nanowires (scale bar is 100 nm), (c) two-step temperature profile used to grow the Ge nanowires in (a) and (b). (d) XRD pole figure of Ge{111} diffraction from the sample shown in (a) and (b) <sup>75</sup>.

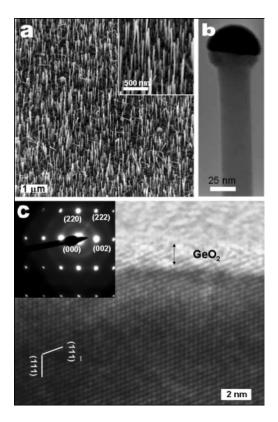

**Figure 7.** FEG-SEM and high-resolution TEM images of vertical Ge nanowires on Ge substrates: (a) A  $30^{\circ}$  perspective of high-density vertical Ge nanowires on a (111) Ge substrate. The inset shows a higher magnification of the nanowires, (b) typical nanowires as viewed by TEM, showing a hemispherical alloy catalyst head, a Ge receptacle, and a Ge body with uniform diameter and a smooth surface and (c) a TEM image of the nanowires, showing the (111) lattice friges with an interplanar distance of 3.26 Å, a smooth and distinct boundary between the Ge and the GeO<sub>2</sub> and a GeO<sub>2</sub> sheath of 1-2 nm. The inset shows the electron diffraction pattern suggesting high crystallinity. The spots are resolved to the (300) and (330) families  $^{66}$ .

**Figure 8.** SEM images of (a) polycrystalline and (b) single crystalline arrays of Ge nanowires grown within 80 nm AAO membranes, and (c) and (d) the corresponding TEM images.

**Figure 9.** Representation of the macrocontact setup: (a) averaged conductivity through nanowires with Au-Ge nanowire contact interface, (b) same as (a) but with a Ge-Ge nanowire interface and (c) surface conductivity measurement <sup>40</sup>.

**Figure 10.** Coaxially-gated nanowire transistors: (a) device schematic showing transistor structure. The inset shows the cross-section of the as-grown nanowire, starting with a pdoped Si core (blue, 10 nm) with subsequent layers of i-Ge (red, 10 nm), SiO<sub>x</sub> (green, 4 nm), and p-Ge (5 nm). The source (S) and drain (D) electrodes are contacted to the inner i-Ge core, while the gate electrode (G) is in contact with the outer p-Ge shell and electrically isolated from the core by the SiO<sub>x</sub> layer. (b) SEM image of a coaxial transistor. Source and drain electrodes were deposited after etching the Ge (30 % H<sub>2</sub>O<sub>2</sub>, 20 s) and SiO<sub>x</sub> layers (buffered HF, 10 s) to expose the core layers. The etching of these outer layers is shown clearly in the inset and is indicated by the arrow. The gate electrodes were defined in a second step without any etching before contact deposition. Scale bar is 500 nm. (c) Gate response of the coaxial transistor at V SD =1 V, showing a maximum transconductance of 1.500 nA V<sup>-1</sup>. Charge transfer from the p-Si core to the i-Ge shell produces a highly conductive and gateable channel.