| Title                       | The impact of forming gas annealing on the electrical characteristics of sulfur passivated Al2O3/In0.53Ga0.47As (110) metal-oxide-semiconductor capacitors                                                                                                                                                                                                               |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Fu, Yen-Chun;Peralagu, Uthayasankaran;Millar, David A. J.;Lin,<br>Jun;Povey, Ian M.;Li, Xu;Monaghan, Scott;Droopad, Ravi;Hurley,<br>Paul K.;Thayne, Iain G.                                                                                                                                                                                                              |

| Publication date            | 2017-04-06                                                                                                                                                                                                                                                                                                                                                               |

| Original Citation           | Fu, YC., Peralagu, U., Millar, D. A. J., Lin, J., Povey, I., Li, X., Monaghan, S., Droopad, R., Hurley, P. K. and Thayne, I. G. (2017) 'The impact of forming gas annealing on the electrical characteristics of sulfur passivated Al203/In0.53Ga0.47As (110) metal-oxide-semiconductor capacitors', Applied Physics Letters, 110(14), pp. 142905. doi:10.1063/1.4980012 |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                  |

| Link to publisher's version | 10.1063/1.4980012                                                                                                                                                                                                                                                                                                                                                        |

| Rights                      | © 2017, AIP Publishing. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in: Appl. Phys. Lett. 110, 142905 (2017) and may be found at http://aip.scitation.org/doi/pdf/10.1063/1.4980012                                                                   |

| Download date               | 2025-04-28 06:21:12                                                                                                                                                                                                                                                                                                                                                      |

| Item downloaded from        | https://hdl.handle.net/10468/3948                                                                                                                                                                                                                                                                                                                                        |

## The impact of forming gas annealing on the electrical characteristics of sulfur passivated Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As (110) metal-oxide-semiconductor capacitors

Yen-Chun Fu, Uthayasankaran Peralagu, David A. J. Millar, Jun Lin, Ian Povey, Xu Li, Scott Monaghan, Ravi Droopad, Paul K. Hurley, and Iain G. Thayne

Citation: Appl. Phys. Lett. **110**, 142905 (2017); doi: 10.1063/1.4980012

View online: http://dx.doi.org/10.1063/1.4980012

View Table of Contents: http://aip.scitation.org/toc/apl/110/14

Published by the American Institute of Physics

## Articles you may be interested in

Oxidation induced stress in SiO2/SiC structures

Appl. Phys. Lett. 110, 141604141604 (2017); 10.1063/1.4979544

High pulsed current density  $\beta$ -Ga2O3 MOSFETs verified by an analytical model corrected for interface charge Appl. Phys. Lett. **110**, 143505143505 (2017); 10.1063/1.4979789

Thermodynamic understanding and analytical modeling of interfacial SiO2 scavenging in HfO2 gate stacks on Si, SiGe, and SiC

Appl. Phys. Lett. 110, 142903142903 (2017); 10.1063/1.4979711

Control of pn-junction turn-on voltage in 4H-SiC merged PiN Schottky diode

Appl. Phys. Lett. 110, 142103142103 (2017); 10.1063/1.4979790

1-kV vertical Ga2O3 field-plated Schottky barrier diodes

Appl. Phys. Lett. 110, 103506103506 (2017); 10.1063/1.4977857

Inductively coupled plasma etch damage in (-201) Ga2O3 Schottky diodes

Appl. Phys. Lett. 110, 142101142101 (2017); 10.1063/1.4979592

## The impact of forming gas annealing on the electrical characteristics of sulfur passivated Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As (110) metal-oxide-semiconductor capacitors

Yen-Chun Fu,<sup>1,a)</sup> Uthayasankaran Peralagu,<sup>1</sup> David A. J. Millar,<sup>1</sup> Jun Lin,<sup>2</sup> Ian Povey,<sup>2</sup> Xu Li,<sup>1</sup> Scott Monaghan,<sup>2</sup> Ravi Droopad,<sup>3</sup> Paul K. Hurley,<sup>2</sup> and Iain G. Thayne<sup>1</sup> School of Engineering, University of Glasgow, Glasgow, G12 8LT, United Kingdom <sup>2</sup>Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland <sup>3</sup>Ingram School of Engineering, Texas State University, San Marcos, Texas 78666, USA

(Received 8 December 2016; accepted 27 March 2017; published online 6 April 2017)

This study reports the impact of forming gas annealing (FGA) on the electrical characteristics of sulfur passivated, atomic layer deposited  $Al_2O_3$  gate dielectrics deposited on (110) oriented n- and p-doped In<sub>0.53</sub>Ga<sub>0.47</sub>As layers metal-oxide-semiconductor capacitors (MOSCAPs). In combination, these approaches enable significant Fermi level movement through the bandgap of both n- and p-doped  $In_{0.53}Ga_{0.47}As$  (110) MOSCAPs. A midgap interface trap density ( $D_{it}$ ) value in the range  $0.87 - 1.8 \times 10^{12} \, \text{cm}^{-2} \text{eV}^{-1}$  is observed from the samples studied. Close to the conduction band edge, a  $D_{it}$  value of  $3.1 \times 10^{11}\,\mathrm{cm^{-2}eV^{-1}}$  is obtained. These data indicate the combination of sulfur pre-treatment and FGA is advantageous in passivating trap states in the upper half of the bandgap of (110) oriented In<sub>0.53</sub>Ga<sub>0.47</sub>As. This is further demonstrated by a reduction in border trap density in the n-type  $In_{0.53}Ga_{0.47}As$  (110) MOSCAPs from 1.8 ×  $10^{12}\,\mathrm{cm^{-2}}$  to  $5.3\times10^{11}\,\mathrm{cm^{-2}}$  as a result of the FGA process. This is in contrast to the observed increase in border trap density after FGA from  $7.3 \times 10^{11} \,\mathrm{cm}^{-2}$  to  $1.4 \times 10^{12} \,\mathrm{cm}^{-2}$  in p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As (110) MOSCAPs, which suggest FGA is not as effective in passsivating states close to the valence band edge. Published by AIP Publishing.

[http://dx.doi.org/10.1063/1.4980012]

Due to the fundamental scaling limits of Si complementary-metal-oxide-semiconductor (CMOS), innovations based around new materials and device architectures are required to facilitate improvements in transistor performance, and extend the logic device and more than Moore roadmaps. The first of these innovations has seen the device architecture evolving to become non-planar in the form of tri-gate metal-oxidesemiconductor field-effect-transistors (MOSFETs) and fin field-effect-transistors (FinFETs), which have become the mainstream in CMOS since the 22 nm technology node. Future scaling, beyond critical geometries of 10 nm, will require the introduction of high-mobility channels to sustain performance at reduced supply voltages.<sup>3</sup> III-V compound semiconductors have garnered significant interest due to their superior electron transport properties in this regard.<sup>3</sup> This has led to a number of non-planar device demonstrations, including InGaAs FinFETs and nanowire MOSFETs, on (100)-oriented substrates. 4-6 In these devices, the gate stack is formed over both the top and sidewalls of the fin/wire, with the latter having (110) or (111) surface orientations. As such, passivation techniques to engineer a high quality gate stack on a variety of surface orientations are essential to realising high performance non-planar InGaAs-channel devices.

Numerous approaches including sulfur-based chemical cleans, 7,8 As<sub>2</sub> capping and decapping, 9 trimethylaluminum (TMA) pre-dosing,  $^{10}$  cyclic plasma (H<sub>2</sub> or N<sub>2</sub>) and TMA exposures,  $^{11,12}$  and AlN interface control layer  $^{13}$  have been explored to passivate InGaAs (100) surfaces prior to atomic

Wafers comprising of p-type Be-doped  $(4 \times 10^{17} \text{ cm}^{-3})$ and *n*-type Si-doped  $(4 \times 10^{17} \text{ cm}^{-3}) \text{ In}_{0.53} \text{Ga}_{0.47} \text{As}$  (110) layers with a thickness of 200 nm grown by molecular beam epitaxy (MBE) on  $p^+$  and  $n^+$  InP (110) substrates, respectively, were used in this study. Samples from both wafers were initially degreased for 1 min each in acetone, methanol, and isopropanol. Following treatment in (NH<sub>4</sub>)<sub>2</sub>S (10% in deionised  $H_2O$ ) for 20 min at room temperature ( $\sim$ 295 K), samples were transferred to the ALD chamber within  $\sim$ 3 min after removal from the sulfur solution. Films of Al<sub>2</sub>O<sub>3</sub>, with a nominal thickness of 8 nm, were grown by

layer deposition (ALD) of high-k gate dielectrics. Of these surface preparation methods, ammonium sulfide ((NH<sub>4</sub>)<sub>2</sub>S), a wet chemical treatment, has demonstrated interface trap density  $(D_{it})$  below  $10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> around the mid-gap energy. <sup>14</sup> Wet sulfur treatment has also been reported to be an effective passivation technique on InGaAs (111) surfaces, resulting in an interface quality comparable to that achieved on sulfurtreated InGaAs (100) surfaces. 15 In the case of InGaAs (110) surfaces,  $D_{it}$  in the order of  $2-4\times10^{12}\,\mathrm{cm}^{-2}\mathrm{eV}^{-1}$  was achieved for surfaces prepared by means of cyclic atomic H cleaning and TMA pre-dosing. 16 However, as yet, there has been no exploration into the effectiveness of wet sulfur treatments on InGaAs (110) surfaces. It is therefore timely to observe the impact of this sulfur-based approach to the interface between Al<sub>2</sub>O<sub>3</sub> grown by ALD and (110)-oriented n- and p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As and in addition to evaluate the role of forming gas annealing (FGA), which has been widely used to lower  $D_{it}$  in both  $SiO_2/Si^{17}$  and high-k/InGaAs (100)<sup>18</sup> systems.

a)Electronic mail: y.fu.2@research.gla.ac.uk

ALD at 300 °C using alternating pulses of TMA and H<sub>2</sub>O precursors, with TMA being the first pulse in the process. Metal-oxide-semiconductor capacitors (MOSCAPs) were fabricated by electron-beam evaporation of Pt/Au through a shadow mask for gate contacts, and completed with Au/Zn/Au or Au/Ge/Ni/Au ohmic contacts to the back of the *p*- and *n*-type samples, respectively. Post-metallisation FGA was performed in a H<sub>2</sub>/N<sub>2</sub> (5%/95%) ambient for 30 min at 350 °C. Electrical measurements were performed on-wafer in a microchamber probe station (Cascade, Summit 12971B) in a dark, electrically shielded environment using an impedance analyser (Agilent E4980A).

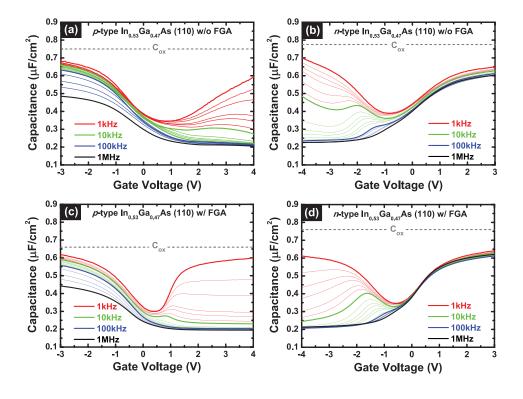

Fig. 1 shows the room temperature frequency-dependent (1 kHz to 1 MHz) capacitance-voltage (CV) characteristics of sulfur passivated p- and n-type  $In_{0.53}Ga_{0.47}As$  (110) MOSCAPs before and after FGA. A qualitative assessment of the samples prior to FGA reveals a larger frequency dispersion in the accumulation region of the p-type (110) MOSCAP, akin to that observed in In<sub>0.53</sub>Ga<sub>0.47</sub>As (100) MOSCAPs. The observed dispersion is ascribed to the tunnelling of carriers into electrically active, near interface border traps in the oxide, <sup>19–21</sup> and fast interface states. <sup>22,23</sup> The larger frequency dispersion in the depletion region of the p-type MOSCAP also suggests a higher density of interface traps in the lower half of the bandgap. Following FGA, the frequency dispersion in accumulation and depletion is marginally improved for the p-type MOSCAP. Notably though the CV response is seen to plateau as the gate bias is increased to more positive voltages as shown in Fig. 1(c). This behaviour is consistent with a genuine minority carrier response in inversion as opposed to a defect-dominated response.<sup>24</sup> The transition frequency, defined as the capacitance in inversion that is half way between the highest capacitance measured at low frequency and the lowest capacitance measured at high frequency, and for which the frequency scaled measured conductance  $(G_m/\omega)$  is also a maximum, provides a measure of the minority carrier response time  $(\tau_R)$ .<sup>24</sup> For the p-type MOSCAP after FGA,  $G_{\rm m}/\omega$  (not shown) is at a maximum at a transition frequency of 3 kHz, from which  $\tau_R$  is estimated as 0.25 ms. This value is comparable with a  $\tau_R$  of  $\sim$ 1 ms reported on MBE grown InGaAs (100), for which inversion was observed.<sup>25,26</sup> In the case of the n-type MOSCAP, the frequency dispersion in accumulation and depletion and the CV stretch-out are noticeably reduced following the FGA treatment. These observations can be interpreted as reduced  $D_{\rm it}$  in the bandgap as a consequence of the FGA process.

For quantitative analysis,  $D_{it}$  distributions of the MOSCAPs pre- and post-FGA were determined using a temperature modified version<sup>7</sup> of the combined high-low frequency CV method.<sup>24</sup> In this approach, the low-frequency capacitance measurement was obtained at 100 Hz at room temperature while the high frequency measurement of 1 MHz was obtained at a reduced temperature of -50 °C to minimise the interface defect response to allow for a more accurate estimation of Dit. It is further crucial to obtain an accurate estimate of the oxide capacitance  $(C_{ox})$  as this has a direct bearing on the accuracy of the extracted  $D_{it}$ . Often  $C_{ox}$ is deduced from the maximum accumulation capacitance, which is prone to error due to the effects of density of states and charge quantisation in the semiconductor<sup>27</sup> which is compounded by interface states and border traps. 14,22,23 An alternative is to calculate  $C_{ox}$  based on the dielectric constant (k) and physical dielectric thickness obtained from transmission electron microscopy. This can also be erroneous given the uncertainty of the k-value of Al<sub>2</sub>O<sub>3</sub>, reported to be between 7 and 9 in literature, resulting in an assumed value of the dielectric constant to be used in the calculation. In addition, there could be an interfacial transition region between the InGaAs and the Al<sub>2</sub>O<sub>3</sub>, whose dielectric constant is not known. Instead, here we derived the value of  $C_{ox}$ for each sample by comparing the experimental and modelled CV curves. The modelling was based on the work of

FIG. 1. Multifrequency (1 kHz to 1 MHz) room temperature CV responses of  $Au/Pt/Al_2O_3/In_{0.53}Ga_{0.47}As$  (110) MOSCAPs: (a) p-type and (b) n-type before FGA, and (c) p-type and (d) n-type after FGA. The  $C_{\rm ox}$  values derived from a comparison between experimental and modelled CV curves are indicated as horizontal lines.

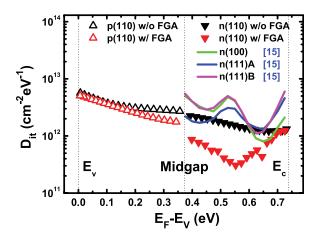

FIG. 2. Extracted  $D_{\rm it}$  profiles of p- and n-type  ${\rm In_{0.53}Ga_{0.47}As}$  (110) MOSCAPs before and after FGA. For comparison, the  $D_{\rm it}$  distributions of sulfur passivated n-type  ${\rm In_{0.53}Ga_{0.47}As}$  (100), (111) A and (111B) surfaces from Ref. 15 are shown.

Engel-Herbert et al.,  $^{28}$  and the obtained  $C_{ox}$  values are indicated as horizontal lines in Fig. 1. Fig. 2 shows the  $D_{it}$  distributions of the p- and n-type MOSCAPs before and after FGA as a function of the surface potential  $(\psi)$  determined from the Berglund integral.<sup>29</sup> As the surface potential for the flatband voltage  $(V_{\rm fb})$  is known, i.e.,  $\psi(V_{\rm fb}) = 0$ , the integral was split into two parts: one integrating from flatband to accumulation and the other from flatband to weak inversion. The flatband voltage used in the integral, and in subsequent analysis, was based on the flatband capacitance calculated using the value of  $C_{ox}$  derived from the aforementioned technique. From the extracted profiles, the midgap  $D_{it}$  of the p- and n-type (110) samples before (and after) FGA are estimated to be  $2.7 \times 10^{12} \, (1.8 \times 10^{12}) \, \text{cm}^{-2} \text{eV}^{-1}$  and  $2.2 \times 10^{12} \, \text{cm}^{-2}$  $10^{12} (8.7 \times 10^{11}) \,\mathrm{cm}^{-2} \mathrm{eV}^{-1}$  respectively. Furthermore, the trap density close to the conduction band is reduced by almost an order of magnitude after the FGA treatment, resulting in a  $D_{\rm it}$  of  $3.1 \times 10^{11} \, {\rm cm}^{-2} {\rm eV}^{-1}$ . For comparison, the  $D_{\rm it}$  profiles of sulfur passivated n-type  ${\rm In}_{0.53}{\rm Ga}_{0.47}{\rm As}$ (100) and (111) MOSCAPs<sup>15</sup> are plotted in Fig. 2. It is notable that  $D_{it}$  distributions in the upper half of the bandgap are comparable between the different surface orientations of  $In_{0.53}Ga_{0.47}As.$

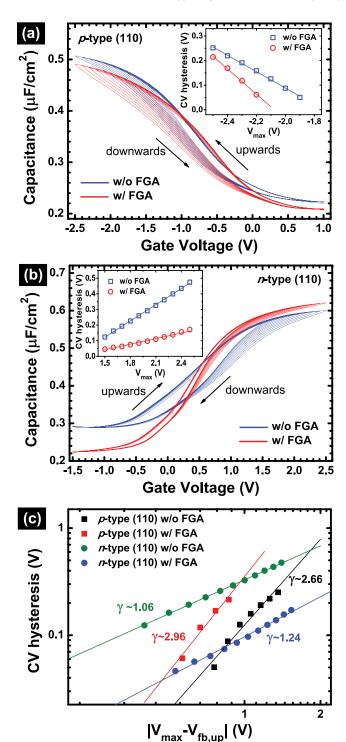

In addition to  $D_{it}$ , the impact of FGA on the border trap response of samples was analysed by means of hysteresis exhibited in the CV characteristics.<sup>30</sup> The CV hysteresis responses were measured at room temperature starting from inversion and sweeping towards accumulation, followed by sweeping back towards inversion. To minimise the contribution of  $D_{it}$  to the CV responses, the bi-directional sweeps were performed at a high frequency measurement of 1 MHz.<sup>7</sup> Shown in Fig. 3(a) and 3(b) are the bi-directional CV sweeps for the p- and n-type  $In_{0.53}Ga_{0.47}As$  (110) MOSCAPs, respectively, obtained under increasing maximum gate bias in accumulation  $(V_{\text{max}})$  before and after FGA. The CV hysteresis is derived from the difference in  $V_{\rm fb}$ between the upward and downward sweep of a measurement. A linear increase in the CV hysteresis with increasing  $V_{\text{max}}$  is noted from the insets of the figures, suggesting an increase in the trapped charge density as the Fermi level is moved

FIG. 3. Bi-directional 1 MHz CV sweeps recorded at room temperature for (a) p-type and (b) n-type  $In_{0.53}Ga_{0.47}As$  (110) MOSCAPs, before and after FGA, using the same starting gate bias in inversion and increasing maximum gate bias in accumulation ( $V_{\rm max}$ ), with plots of CV hysteresis as a function of  $V_{\rm max}$  shown in the insets, and (c) CV hysteresis as a function of  $|V_{\rm max} - V_{\rm fb,up}|$  plotted in log-log scale for p- and n-type  $In_{0.53}Ga_{0.47}As$  (110) samples, before and after FGA.

towards the band edges. For both p- and n-type samples, the FGA treatment results in a reduction in the CV hysteresis. In the case of the p-type sample, the reduction in hysteresis after the FGA treatment becomes more pronounced with decreasing  $V_{\rm max}$ . This is in marked contrast to the n-type sample for which the FGA treatment results in a significant reduction in CV hysteresis with increasing  $V_{\rm max}$ . From the

log-log scale plot of Fig. 3(c), it is further observed the CV hysteresis follows a power-law of  $|V_{\rm max}-V_{\rm fb,up}|$  (where  $V_{\rm fb,up}$  is the flatband voltage of the upward measurement sweep) for all samples. The voltage acceleration factor  $(\gamma)$ , marked in the plot, is given by the exponent of the power-law dependence and is found to improve for both p- and n-type  $I_{10.53}Ga_{0.47}As$  (110) MOSCAPs after FGA. The steeper voltage acceleration is indicative of a narrower border trap distribution (assuming a normal distribution), which can be seen as a projection of improved reliability at lower operating voltages. The level of charge trapping in the samples can be quantified as

$$N_{\rm t} = \frac{C_{\rm ox} \times \Delta V}{q},\tag{1}$$

where  $N_t$  is the trapped charge density (cm<sup>-2</sup>),  $\Delta V$  is the CVhysteresis, and q is the electronic charge. For a valid comparison between the samples,  $N_t$  must be obtained under the same electric field across the oxide.<sup>30</sup> This means  $\Delta V$  in Eq. (1) should be evaluated at the same value of  $|V_{\text{max}} - V_{\text{fb,up}}|$ . If  $|V_{\text{max}} - V_{\text{fb,up}}|$  is taken as 1.1 V, the trapped charge density before (and after) FGA is estimated to be  $7.3 \times 10^{11} \, (1.4 \times$  $10^{12}$ ) cm<sup>-2</sup> for the p-type MOSCAP and  $1.8 \times 10^{12}$  (5.3 ×  $10^{11}$ ) cm<sup>-2</sup> for the *n*-type MOSCAP. It is noted that CV hysteresis measured at 1 MHz does not capture all border traps, as in practical devices, border traps exist into the oxide, and the density can vary with depth into the oxide, as well as with energy.  $^{32}$  In a CV sweep, the fast traps, which can respond at frequencies up to the low GHz range, would have emitted the trapped charge just as the reverse sweep is initiated. In addition, a significant quantity of charge is lost during the reverse CV sweep. As a consequence, the trapped charge measured from CV hysteresis only samples a certain portion from the total population of border traps, whose time constants are comparable to, or longer than, the time associated with the CV sweep. However, it remains a useful approach to explore how the border traps with long time constants vary with FGA.

This study shows that in combination, a wet sulfur pretreatment prior to atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> together with a post-metal deposition FGA, enables significant Fermi level movement through the bandgap of (110) oriented nand p-doped In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSCAPs. Quantitatively, a midgap  $D_{it}$  value in the range  $0.87 - 1.8 \times 10^{12} \,\mathrm{cm}^{-2} \mathrm{eV}^{-1}$ is obtained from both the p- and n-type samples studied. Close to the conduction band edge, a  $D_{\rm it}$  value of 3.1 × 10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup> is obtained. These data are in agreement with previous reports from (100) and (111) oriented *n*-doped In<sub>0.53</sub>Ga<sub>0.47</sub> As MOSCAPs, indicating the combination of sulfur pre-treatment and FGA is advantageous in passivating trap states in the upper half of the bandgap. This is further demonstrated by a reduction in border trap density in the *n*-type  $In_{0.53}Ga_{0.47}$  As (110) MOSCAPs from 1.8 ×  $10^{12}$  cm<sup>-2</sup> to  $5.3 \times 10^{11}$  cm<sup>-2</sup> as a result of the FGA process, as determined from CV hysteresis trapped charge at a bias of 1.1 V beyond the flatband voltage. This is in contrast to the observed increase in border trap density after FGA from  $7.3 \times 10^{11} \,\mathrm{cm^{-2}}$  to  $1.4 \times 10^{12} \,\mathrm{cm^{-2}}$  for similar bias stress conditions in p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As (110) MOSCAPs, which suggest FGA is not as effective in passsivating states close to the valence band edge.

This work was supported by Tokyo Electron Limited custom funding from the Semiconductor Research Corporation through DS Digital CMOS Technologies (Task ID: 2188.002) and funding from the European Union 7th Framework Program COMPOSE3 (FP7-ICT-2013–11-619325). The authors acknowledge technical support from the central fabrication facility at Tyndall National Institute, University College Cork, and the James Watt Nanofabrication Centre, University of Glasgow.

<sup>1</sup>Y. Taur, IBM J. Res. Develop. **46**, 213 (2002).

<sup>2</sup>K. Kuhn, M. Giles, D. Becher, P. Kolar, A. Kornfeld, R. Kotlyar, S. Ma, A. Maheshwari, and S. Mudanai, IEEE Trans. Electron Devices 58, 2197 (2011).

<sup>3</sup>H. Riel, L.-E. Wernersson, M. Hong, and J. A. del Alamo, MRS Bull. **39**, 668 (2014).

<sup>4</sup>C. Hock-Chun Chin, X. Gong, L. Wang, H. K. Lee, L. Shi, and Y.-C. Yeo, IEEE Electron Device Lett. **32**, 146 (2011).

<sup>5</sup>J. J. Gu, O. Koybasi, Y. Q. Wu, and P. D. Ye, Appl. Phys. Lett. **99**, 112113 (2011).

<sup>6</sup>X. Zhao and J. Del Alamo, IEEE Electron Device Lett. **35**, 521 (2014).

<sup>7</sup>E. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, J. Appl. Phys. **109**, 024101 (2011).

<sup>8</sup>E. O'Connor, R. D. Long, K. Cherkaoui, K. K. Thomas, F. Chalvet, I. M. Povey, M. E. Pemble, P. K. Hurley, B. Brennan, G. Hughes, and S. B. Newcomb, Appl. Phys. Lett. **92**, 022902 (2008).

<sup>9</sup>E. J. Kim, E. Chagarov, J. Cagnon, Y. Yuan, A. C. Kummel, P. M. Asbeck, S. Stemmer, K. C. Saraswat, and P. C. McIntyre, J. Appl. Phys. 106, 124508 (2009).

<sup>10</sup>J. Ahn, T. Kent, E. Chagarov, K. Tang, A. C. Kummel, and P. C. McIntyre, Appl. Phys. Lett. **103**, 071602 (2013).

<sup>11</sup>A. D. Carter, W. J. Mitchell, B. J. Thibeault, J. J. M. Law, and M. J. W. Rodwell, Appl. Phys. Express 4, 091102 (2011).

<sup>12</sup>V. Chobpattana, J. Son, J. J. M. Law, R. Engel-Herbert, C.-Y. Huang, and S. Stemmer, Appl. Phys. Lett. **102**, 022907 (2013).

<sup>13</sup>Q. H. Luc, E. Chang, H. D. Trinh, Y. C. Lin, H. Q. Nguyen, Y. Y. Wong, H. B. Do, S. Salahuddin, and C. Hu, IEEE Trans. Electron Devices 61, 2774 (2014).

<sup>14</sup>P. Hurley, E. O'Connor, V. Djara, S. Monaghan, I. Povey, R. Long, B. Sheehan, J. Lin, P. McIntyre, B. Brennan, R. Wallace, M. Pemble, and K. Cherkaoui, IEEE Trans. Device Mater. Reliab. 13, 429 (2013).

<sup>15</sup>M. Yokoyama, N. Taoka, R. Suzuki, O. Ichikawa, H. Yamada, N. Fukuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, and S. Takagi, in *Indium Phosphide and Related Materials (IPRM)* (IEEE, 2012), pp. 167–170.

<sup>16</sup>T. Kent, K. Tang, V. Chobpattana, M. A. Negara, M. Edmonds, W. Mitchell, B. Sahu, R. Galatage, R. Droopad, P. McIntyre, and A. C. Kummel, J. Chem. Phys. 143, 164711 (2015).

<sup>17</sup>A. Stesmans, J. Appl. Phys. **88**, 489 (2000).

<sup>18</sup>Y. Hwang, R. Engel-Herbert, N. G. Rudawski, and S. Stemmer, J. Appl. Phys. **108**, 034111 (2010).

<sup>19</sup>E. J. Kim, L. Wang, P. M. Asbeck, K. C. Saraswat, and P. C. McIntyre, Appl. Phys. Lett. **96**, 012906 (2010).

<sup>20</sup>S. Yoshida, S. Taniguchi, H. Minari, D. Lin, T. Ivanov, H. Watanabe, M. Nakazawa, N. Collaert, and A. Thean, Jpn. J. Appl. Phys., Part 1 55, 08PC01 (2016).

Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P. C. McIntyre, P. M. Asbeck,

M. J. W. Rodwell, and Y. Taur, IEEE Electron Device Lett. 32, 485 (2011)

<sup>22</sup>N. Taoka, M. Yokoyama, S. H. Kim, R. Suzuki, T. Hoshii, R. Iida, S. Lee, Y. Urabe, N. Miyata, T. Yasuda, H. Yamada, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, Microelectron. Eng. 88, 1087 (2011).

<sup>23</sup>G. Brammertz, H.-C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, Appl. Phys. Lett. 95, 202109 (2009).

<sup>24</sup>E. Nicollian and J. Brews, MOS Physics and Technology (Wiley, New Jersey, 2002).

- <sup>25</sup>H. D. Trinh, E. Y. Chang, P. W. Wu, Y. Y. Wong, C. T. Chang, Y. F. Hsieh, C. C. Yu, H. Q. Nguyen, Y. C. Lin, K. L. Lin, and M. K. Hudait, Appl. Phys. Lett. **97**, 042903 (2010).

- Appl. Phys. Lett. 97, 042903 (2010).

<sup>26</sup>Y. C. Chang, M. L. Huang, K. Y. Lee, Y. J. Lee, T. D. Lin, M. Hong, J. Kwo, T. S. Lay, C. C. Liao, and K. Y. Cheng, Appl. Phys. Lett. 92, 072901 (2008).

- <sup>27</sup>P. K. Hurley, R. Long, T. O'Regan, E. O'Connor, S. Monaghan, V. Djara, M. A. Negara, A. O'Mahony, I. Povey, A. Blake, R. Nagle, D. O'Connell, M. Pemble, and K. Cherkaoui, ECS Trans. 33, 433 (2010).

- <sup>28</sup>R. Engel-Herbert, Y. Hwang, and S. Stemmer, Appl. Phys. Lett. 97, 062905 (2010).

- <sup>29</sup>C. N. Berglund, IEEE Trans. Electron Devices **13**, 701 (1966).

- <sup>30</sup>J. Lin, Y. Y. Gomeniuk, S. Monaghan, I. M. Povey, K. Cherkaoui, E. O'Connor, M. Power, and P. K. Hurley, J. Appl. Phys. 114, 144105 (2013).

- <sup>31</sup>J. Franco, A. Alian, B. Kaczer, D. Lin, T. Ivanov, A. Pourghaderi, K. Martens, Y. Mols, D. Zhou, N. Waldron, S. Sioncke, T. Kauerauf, N. Collaert, A. Thean, M. Heyns, and G. Groeseneken, in *International Reliability Physics Symposium (IRPS)* (IEEE, 2014), pp. 6A.2.1–6A.2.6.

- <sup>32</sup>S. Johansson, M. Berg, K. M. Persson, and E. Lind, IEEE Trans. Electron Devices 60, 776 (2013).