| Title                       | Diagnosis of phosphorus monolayer doping in silicon based on nanowire electrical characterisation                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Authors                     | Duffy, Ray;Ricchio, Alessio;Murphy, Ruaidhrí;Maxwell,<br>Graeme;Murphy, Richard;Piaszenski, Guido;Petkov,<br>Nikolay;Hydes, Alan;O'Connell, Dan;Lyons, Colin;Kennedy,<br>Noel;Sheehan, Brendan;Schmidt, Michael;Crupi, Felice;Holmes,<br>Justin D.;Hurley, Paul K.;Connolly, James;Hatem, Chris;Long,<br>Brenda                                                                                                                           |

| Publication date            | 2018-03-23                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Original Citation           | Duffy, R., Ricchio, A., Murphy, R., Maxwell, G., Murphy, R., Piaszenski, G., Petkov, N., Hydes, A., O'Connell, D., Lyons, C., Kennedy, N., Sheehan, B., Schmidt, M., Crupi, F., Holmes, J. D., Hurley, P. K., Connolly, J., Hatem, C. and Long, B. (2018) 'Diagnosis of phosphorus monolayer doping in silicon based on nanowire electrical characterisation', Journal of Applied Physics, 123(12), 125701 (14pp). doi: 10.1063/1.5019470 |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Link to publisher's version | https://aip.scitation.org/doi/full/10.1063/1.5019470 -<br>10.1063/1.5019470                                                                                                                                                                                                                                                                                                                                                               |

| Rights                      | © 2018, AIP Publishing. This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. The following article appeared in Journal of Applied Physics 123, 125701 (2018) and may be found at https://aip.scitation.org/doi/full/10.1063/1.5019470                                                                                                                          |

| Download date               | 2025-06-20 04:48:43                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Item downloaded from        | https://hdl.handle.net/10468/5724                                                                                                                                                                                                                                                                                                                                                                                                         |

# Diagnosis of phosphorus monolayer doping in silicon based on nanowire electrical characterisation

Ray Duffy, Alessio Ricchio, Ruaidhrí Murphy, Graeme Maxwell, Richard Murphy, Guido Piaszenski, Nikolay Petkov, Alan Hydes, Dan O'Connell, Colin Lyons, Noel Kennedy, Brendan Sheehan, Michael Schmidt, Felice Crupi, Justin D. Holmes, Paul K. Hurley, James Connolly, Chris Hatem, and Brenda Long

Citation: Journal of Applied Physics 123, 125701 (2018); doi: 10.1063/1.5019470

View online: https://doi.org/10.1063/1.5019470

View Table of Contents: http://aip.scitation.org/toc/jap/123/12

Published by the American Institute of Physics

### Articles you may be interested in

Ge(001) surface cleaning methods for device integration Applied Physics Reviews **4**, 021308 (2017); 10.1063/1.4984975

Phosphorus ionization in silicon doped by self-assembled macromolecular monolayers AIP Advances **7**, 105310 (2017); 10.1063/1.4999232

Fast determination of the current loss mechanisms in textured crystalline Si-based solar cells Journal of Applied Physics **122**, 203101 (2017); 10.1063/1.4997063

Optical properties of InGaN thin films in the entire composition range Journal of Applied Physics **123**, 125101 (2018); 10.1063/1.5020988

Detailed characterisation of focused ion beam induced lateral damage on silicon carbide samples by electrical scanning probe microscopy and transmission electron microscopy

Journal of Applied Physics **123**, 125104 (2018); 10.1063/1.5022558

Stress management on underlying GaN-based epitaxial films: A new vision for achieving high-performance LEDs on Si substrates

Journal of Applied Physics 122, 204503 (2017); 10.1063/1.4993985

### Diagnosis of phosphorus monolayer doping in silicon based on nanowire electrical characterisation

Ray Duffy, <sup>1</sup> Alessio Ricchio, <sup>1,2</sup> Ruaidhrí Murphy, <sup>1</sup> Graeme Maxwell, <sup>1</sup> Richard Murphy, <sup>1</sup> Guido Piaszenski, <sup>3</sup> Nikolay Petkov, <sup>4</sup> Alan Hydes, <sup>1</sup> Dan O'Connell, <sup>1</sup> Colin Lyons, <sup>1</sup> Noel Kennedy, <sup>5</sup> Brendan Sheehan, <sup>1</sup> Michael Schmidt, <sup>1</sup> Felice Crupi, <sup>2</sup> Justin D. Holmes, <sup>5,6</sup> Paul K. Hurley, <sup>1,5</sup> James Connolly, <sup>7</sup> Chris Hatem, <sup>8</sup> and Brenda Long <sup>5</sup> <sup>1</sup>Tyndall National Institute, University College Cork, Lee Maltings, Cork, Ireland

<sup>2</sup>University of Calabria, Arcavacata di Rende, Italy

(Received 14 December 2017; accepted 1 March 2018; published online 23 March 2018)

The advent of high surface-to-volume ratio devices has necessitated a revised approach to parameter extraction and process evaluation in field-effect transistor technologies. In this work, active doping concentrations are extracted from the electrical analysis of Si nanowire devices with high surface-to-volume ratios. Nanowire resistance and Si resistivity are extracted, by first extracting and subtracting out the contact resistance. Resistivity ( $\rho$ ) is selected as the benchmark parameter to compare different doping processes with each other. The impacts of nanowire diameter scaling to 10 nm and of nanowire spacing scaling to <20 nm are extracted for monolayer doping and beam-line ion implantation. Despite introducing significant crystal damage, P beam-line ion implantation beats allyldiphenylphosphine (ADP) P monolayer doping with a SiO<sub>2</sub> cap in terms of lower Si resistivity and higher dopant activation, with dependencies on the nanowire width greater than on nanowire spacing. Limitations in ADP P monolayer doping with a SiO<sub>2</sub> cap are due to the difficulties in dopant incorporation, as it is based on in-diffusion, and P atoms must overcome a potential barrier on the Si surface. Published by AIP Publishing. https://doi.org/10.1063/1.5019470

### I. INTRODUCTION

With logic devices in the fin field effect transistor (FinFET) era, <sup>1–4</sup> and heading towards the gate-all-around (GAA) nanowire architecture, <sup>5–7</sup> it is critical that novel materials and process options consider high surface-to-volume thin-body structures for the diagnosis of their suitability for future technology applications. In these devices, surfaces dominate, as there are proportionately more atoms bound to or located close to the surface.

Doping processes have historically been characterised on planar Si substrates for a number of reasons, typically because these substrates were relevant to the technology and field-effect transistor (FET) devices of the past, as well as being compatible with many material analysis methods, such as Secondary Ion Mass Spectrometry and Spreading Resistance Microscopy. Nowadays, with FinFET fin widths being in the sub-10 nm regime and edging towards 5 nm, fabrication processes must be evaluated with this in mind.

In these high surface-to-volume ratio structures, careful consideration must be made of surface integrity, surface etching, and roughness or gentleness of a particular process. Previously, if some surface roughening occurred during processing, this could practically be absorbed without a significant impact on the device or circuit performance. Times have changed, and gentleness of a processing technique is now a key metric for GAA technologies. For example, monolayer doping (MLD) has been proposed by several groups<sup>8–12</sup> as a novel alternative to conventional doping techniques, such as beam-line ion implantation and plasma doping; however, if one examines the literature on MLD, there is very little data or discussion referring to surface integrity or surface etching. This should be highlighted in future publications in the field.

Doping related issues that potentially hinder performance in conventional thin-body devices include the crystal damage introduced by ion implantation, lack of dopant conformality, and dramatic dopant trapping at the oxide interface in plasma doped processes. The state of the art in semiconductor doping is beam-line ion implantation. 13-15 It is the industry standard because it can generate a single ion species with single energy in an industrially friendly highly controlled fashion. Plasma doping 16-19 (PLAD) has the advantage of generating more conformal doping profiles than ion implantation, but it causes damage to the target as ions strike. PLAD also has issues surrounding the surface quality post-dopant activation that require an understanding of surface science to properly optimise. MLD is promising as it is surface-based, whereby organic molecules are covalently bonded to the semiconductor surface at relatively low processing temperatures.<sup>20,21</sup> A thermal treatment is then applied to diffuse dopant atoms into the semiconductor. One of the main advantages of MLD is that it is a

<sup>&</sup>lt;sup>3</sup>Raith GmbH, Konrad-Adenauer-Allee 8, 44263 Dortmund, Germany

<sup>&</sup>lt;sup>4</sup>Cork Institute of Technology, Bishopstown, Cork, Ireland

<sup>&</sup>lt;sup>5</sup>School of Chemistry, University College Cork, Cork, Ireland

<sup>&</sup>lt;sup>6</sup>CRANN@AMBER, Trinity College Dublin, Dublin 2, Ireland

<sup>&</sup>lt;sup>7</sup>Applied Materials, Lee Maltings, Cork, Ireland

<sup>&</sup>lt;sup>8</sup>Applied Materials, Gloucester, Massachusetts 01930, USA

low-temperature process, typically processing is done at room temperature or at temperatures on the order of 100–180 °C. In comparison, *in situ* doped epitaxial growth<sup>22,23</sup> has a significant thermal budget, with temperatures on the order of 400–800 °C depending on what material is being grown, while the temperature required to prevent damage accumulation during ion implantation is in the range of 400 °C.<sup>24,25</sup> Furthermore, MLD is a surface reaction based technique, so it should resolve these line-of-sight issues that other doping approaches struggle with. Irrespective of the nanowire or fin shape and dimension, the molecules should bind to each surface. P is the most commonly applied dopant for n-type MLD, <sup>26–33</sup> with only a few have reported of As MLD in Si.<sup>34,35</sup>

Much of the MLD literature to date has been based on planar unpatterned substrates. There is now a pressing need to consider how suitable MLD can be for thin-body three-dimensional semiconductor devices with high surface-to-volume ratios. Furthermore, a systematic benchmarking of MLD versus other processes such as ion implant is still lacking.

Another motivation for the work undertaken here centers around the use of nanowire resistors as a diagnostic tool for doping processes. One can extract active doping concentrations from electrical data analysis in nanowire devices with a proper mask and device design. Of course, there are well-known metrology techniques to profile chemical concentrations such as Atom Probe Tomography<sup>36,37</sup> or active concentrations in cross-section by Scanning Spreading Resistance Microscopy;<sup>38</sup> however, the approach presented here is an alternative and complementary methodology.

Here, we explore the concept of pitch scaling in nanowire devices. FinFET and GAA devices comprise more than one parallel current channel, as there are multiple fins or nanowires running in parallel from source to drain. The next big push in device scaling will incorporate pitch or spacing scaling, and thus process evaluation must now also consider this aspect. Literature reports of MLD, or even ion implant, in nanowires are available, but typically on isolated lines. Having these features closer together (<20 nm spacing) brings another set of physical and chemical challenges not considered before.

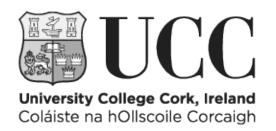

The International Technology Roadmap for Semiconductors (ITRS)<sup>39</sup> projections for FinFET and GAA devices are shown in Fig. 1. It is interesting to note that the fin or nanowire diameter does not scale dramatically, only going from 8 to 5 nm over 5 technology nodes. On the other hand, fin or nanowire pitch scales from 42 to 10 nm in the same timeframe. Densely packed Si nanowires are the next big trend in device scaling, putting pressure on processing technologies where small gaps between features may cause issues and limitations.

In this work, we electrically characterise Si nanowires with widths ranging from 10 to  $300\,\mathrm{nm}$ , and spacings ranging from 20 to  $1000\,\mathrm{nm}$ . Nanowires are doped by ADP P MLD with a  $\mathrm{SiO}_2$  cap and benchmarked against beam-line P ion implantation. Through extensive electrical characterisation, the total device resistance is extracted and sub-components of total resistance are also determined, namely contact resistance ( $R_{\mathrm{CONTACT}}$ ) in order to assess nanowire resistance

FIG. 1. ITRS 2.0 projections for multigate devices consisting of Si fins or nanowires. The pitch, the channel length, and the diameter are predicted to scale, with pitch scaling projected to undergo the largest change.

$(R_{NANOWIRE})$ . Resistivity  $(\rho)$  is then determined, followed by active doping concentration based on well-established values for electron mobility in Si, which are used to benchmark competing processes against each other in this work, and also against values in the literature. In conclusion, the difficulties in doping thin-body Si devices and problems associated with in-diffusion-based processes will be analysed and discussed.

### **II. NANOWIRE DEVICE DESIGN**

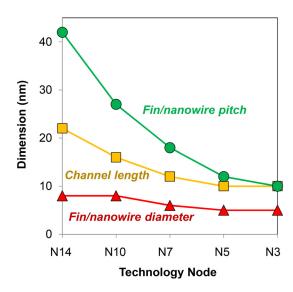

The devices under study to characterise the doping processes consist of multiparallel nanowires to form a resistor structure shown in Fig. 2. This is a simple two-pad test

FIG. 2. (a) A SEM image zoomed into the Si nanowires, which are contacted by metal pads. (b) A schematic drawing of the 4-finger Si nanowire test structure, highlighting the variables' width (W), length (L), and spacing (S).

structure, where current versus voltage characteristics are measured. The Si nanowire features are visible in the Scanning Electron Microscopy (SEM) image in Fig. 2(a). On either side are metal contact pads, which overlap the wider Si regions underneath. In this case, the metals consist of a 10 nm Ti adhesion layer with a 150 nm thick Au layer on top. In Fig. 2(b) is a schematic of the Si portion of the test structure highlighting the variables in the device design on the mask layout. The nanowire width (W), length (L) and spacing (S) are all varied. In this way, we can generate data required to extract  $R_{\rm CONTACT}$ ,  $R_{\rm NANOWIRE}$ , and ultimately  $\rho$ .

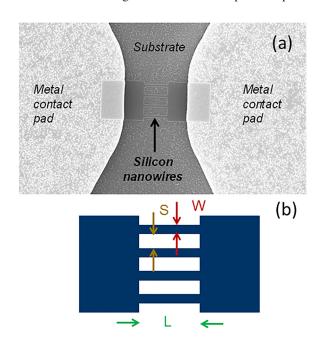

Figure 3 helps explain the extraction methodology in more detail. Let us assume that the current flows uniformly throughout the cross-section of a nanowire say, like that of a metal track. From theory, <sup>40</sup> we know that

$$R = \rho \frac{L}{A} = \rho \frac{L}{t \cdot W},\tag{1}$$

where A is the cross-sectional area, t is the thickness, and R,  $\rho$ , L, and W are as defined previously. Measuring current versus voltage in the two-pad test structure yields total resistance (R<sub>TOTAL</sub>), and the total resistance path through the test structure is given by

$$R_{TOTAL} = 2R_{CONTACT} + \rho \frac{L}{t \cdot W}.$$

(2)

So, by plotting  $R_{TOTAL}$  versus 1/W,  $2R_{CONTACT}$  can be determined from the y-axis intercept at x=0, and thus removed from the equation, leaving behind just the resistance of the nanowires. Note, of course, when considering the cross-sectional area here, we must remember we have 4 nanowires in parallel. With everything else known,  $\rho$  can be extracted.

Moreover, once  $\rho$  is known, we can use the well-established Si theory to extract a value for average active doping concentration in the nanowires. Most Si technology

$$R = \rho \frac{L}{A}$$

$$R = \frac{\rho}{t} \frac{L}{W}$$

w

FIG. 3. A schematic of a conductive track of length L, width W, and thickness t, along with the resistance components in the 2-contact pad test structure investigated in this work.

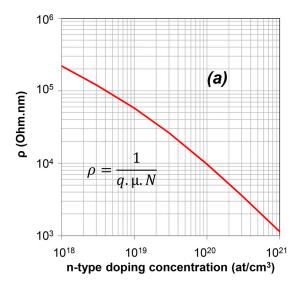

textbooks have a plot of  $\rho$  versus active carrier concentration, which is partially reproduced in Fig. 4, for n-type Si. <sup>41</sup> The inset of Fig. 4 shows the dependence of electron mobility ( $\mu$ ) versus n-type active doping concentration (N). According to

$$\rho = \frac{1}{q \cdot \mu \cdot N},\tag{3}$$

there is a strong dependence of  $\rho$  on  $\mu$  and N. In summary, once  $\rho$  is extracted experimentally, then we can use the graph in Fig. 4 to determine an average active doping concentration, N, throughout the nanowires, as a function of W and S.

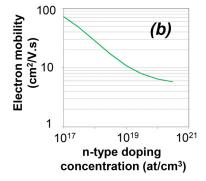

In order to familiarise ourselves with expected trends in R versus doping and W, we carried out drift-diffusion based device simulations of nanowire resistors similar to those in the experimental sections. The simulations have been carried out in the same way as the electrical measurement, using the same dimensions and applied voltages. This is useful here because it enables us to get a preliminary idea of how the nanowire test structure should behave. Figure 5 shows the simulated data for R versus W and active doping concentration. In these idealised simulations, non-idealities such as dopant trapping, quantisation effects, interface states, and Si bandgap variations versus W are not considered, as these would be the subject of a more detailed future modelling study. In Fig. 5, it is clear that R increases with decreased

FIG. 4. (a) Si resistivity ( $\rho$ ) as a function of n-type doping active concentration as derived from (b) standard Si theory for electron mobility.

FIG. 5. Modelling results showing idealised trends of nanowire resistance (R) versus nanowire width. R increases with decreased active doping concentration and with decreased width due to the smaller current-carrying cross-sectional area.

active doping concentration and with decreased width due to the smaller current-carrying cross-sectional area.

### III. EXPERIMENTAL

There are two experimental sets presented in this work. In the first set, we worked on short fat nanowire devices, fabricated from 30 nm thick Si-on-insulator (SOI) wafers, see Fig. 6 for the process flow. In that part, the variables under study are the use of an Radio Corporation of America (RCA) clean prior to MLD functionalisation, and the presence or absence of a capping SiO<sub>2</sub> layer during the drive-in rapid-thermal-annealing (RTA). In the second set of experiments, tall nanowires were fabricated from 66 nm thick SOI wafers, see Fig. 11 for the process flow. There, pitch scaling is particularly interesting, as the tall features form a "Manhattan skyline" type array, where it is envisaged that the narrow spaces combined with the tall features will make conformal doping difficult. ADP P MLD with a SiO<sub>2</sub> cap is benchmarked against a standard beam-line ion implant for P doping in that section.

Throughout this work, nominally undoped (100) SOI substrates were used, with a Si thickness of 30 or 66 nm and

- · Starting wafer, 30 nm SOI

- · E-beam litho, 6 nm HSQ

- Reactive Ion Etch, Cl<sub>2</sub> based

- Phosphorus MLD

- Degrease, IPA and acetone

- RCA clean (optional)

- HF dip

- ADP functionalisation reaction

- Cap with SiO<sub>2</sub> (optional)

- 1050 °C RTA

- Cap removal (optional)

- Ti/Au contact pad metalisation

FIG. 6. Schematic representation of the ADP P MLD process flow on 30 nm tall devices. On the right hand side is a schematic of the ADP molecule bound to the Si surface.

a SiO<sub>2</sub> thickness of 145 nm. For nanowire processing, the SOI substrates were patterned using the Raith VOYAGER electron beam lithography (EBL) system with a beam energy of 50 keV and the high resolution EBL resist hydrogen silsesquioxane (HSQ, XR1541, 2%) from Dow Corning. The substrates were firstly degreased by ultrasonicating them in acetone and isopropyl alcohol (IPA) solvents. After drying the substrates, HSQ resist was spun at 4000 rpm to achieve 15 nm resist thickness. In another set, 6 nm thick layers were prepared by diluting the resist to 1%. Spin coating was performed at 4500 rpm. The EBL exposure was a two-step process, namely a low current set-up pattern for the high resolution nanowires structures, and in the second step, in a high current set-up, the contact pads were exposed. This was done to decrease the total exposure time while maintaining the high resolution required for the nanowires. After the EBL exposure, the substrates were developed in NaCl (4%) and NaOH (1%) solutions for 4 min followed by 15 s rinse in deionised (DI) water and a second 15 s rinse in DI water in a second beaker.

The samples were etched in an Oxford Instruments System 100 ICP etcher operating in the Reactive Ion Etch (RIE) mode. The etch chemistry was a  $\text{Cl}_2/\text{N}_2$  gas mixture at flows of 20 and 40 sccm, respectively, with a process pressure of 10 mTorr and a RF power of 80 W yielding a DC bias of 220 V. The sample temperature was controlled at 20 °C with helium gas backside cooling with the sample mounted on a Si carrier wafer using Krytox vacuum oil. Real time etch depth monitoring of the SOI film layer was achieved using an Intellemetrics LEP500 laser reflection system.

The P MLD process was then implemented on selected samples. To remove any physisorbed contaminants present on the samples, a degreasing step was carried out. Thus, the samples were placed in acetone and ultra-sonicated for 2 min followed by an isopropyl alcohol dip and subsequent drying using a stream of nitrogen gas. A commonly used cleaning step in the semiconductor industry is the RCA cleaning. This involves immersion of a silicon sample in a solution containing a 5:1:1 ratio of DI water, ammonium hydroxide, and hydrogen peroxide at a temperature of 80 °C. This optional step was used in some studies to categorise whether it had a positive effect on MLD and to determine its usefulness for nanoscale nanowires. The removal of the native oxide layer from Si often requires quite harsh treatments involving hydrofluoric (HF) acid, which can etch away this layer to produce a hydrogen terminated surface. Native oxide removal occurred after degreasing or after an RCA clean in cases where it was applied. This hydrogen-terminated surface is prone to re-oxidation and was promptly placed under conditions where this was not possible, under N2 on a Schlenk line.

A solution containing the chosen dopant molecule and solvent was then degassed using multiple freeze-pump-thaw cycles. N-type doping was carried out using allyldiphenylphosphine (ADP) which provides P as the dopant molecule. Mesitylene was used as the solvent when carrying out MLD on oxide-free Si. The degassed solution was cannulated into a round bottom flask containing the Si samples and set to reflux at 180 °C for 3 h to enable functionalisation. Samples

were then removed from the round bottom flask, ultrasonicated in IPA for 1 min and dried under a stream of nitrogen. In order to minimise oxidation of the now functionalised samples, they were placed in gel-boxes and stored in a  $N_2$  environment, either a glove-box or a sample preserver, awaiting thermal treatment. Once functionalised, samples required a thermal treatment to diffuse the target dopant atom into the crystalline Si and provide it with energy to activate through substitutional doping. A 50 nm sputtered  $SiO_2$  capping layer was deposited on selected samples prior to RTA to prevent volatilisation of the dopant molecule. Samples were then treated with a  $1050\,^{\circ}\text{C}$  5 s RTA in  $N_2$ . Cap removal was initially carried out using a 5:1 Buffered Oxide Etch (BOE) solution, in which samples were immersed for 30 s.

As a benchmark, some devices received a P  $4 \times 10^{15}$  cm<sup>-2</sup>  $3 \,\text{keV} 45^{\circ}$  beam-line ion implant. This was done at room temperature, with half of the dose from the left side of the nanowires and half of the dose from the right side in the standard way.

A UV lithography based process was used to pattern the Ti/Au metal contact pads, based on a lift off technique. The steps are as follows: bake the sample in a hexamethyldisilazane (HMDS) primer vapour oven at 115 °C, spin on Micro Chem LOR3A lift-off resist at 3000 rpm for 50 s, hot-plate bake at 150 °C for 3 min, spin on HMDS at 3000 rpm, spin on Micro Chem S1805 imaging resist at 3000 rpm, hot-plate bake at 115°C for 2 min, align and expose in a Karl Suss MA1006 aligner for 4.5 s, exposure dose = 45 mJ/cm<sup>2</sup>, develop for 1 min in Microposit 319 developer, rinse in DI water for 1 min and blow dry with  $N_2$ , immerse in dilute HF (25:1) for 5 s, rinse in DI water and blow dry with N<sub>2</sub>, load in a Temescal FC2000 e-beam evaporator and pump system to  $>5 \times 10^{-7}$  Torr, expose to Ar plasma for 20 s to improve metal to metal adhesion, evaporate Ti:Au (10:150 nm), lift-off resist and excess metal in Microposit R1165 resist remover at 90 °C for 1 h, and finally rinse in DI water and blow dry with  $N_2$ .

Electrochemical Capacitance Voltage (ECV) profiling was also performed to determine the active carrier concentration using dilute ammonium bifluoride as an electrolyte. ECV profilers extract an error with every datapoint in the curve. For the data presented here, the errors do not exceed 20%. As doping concentration axes are plotted in the log-scale, these errors are relatively small and do not affect the overall conclusions of this work. Cross-sectional Transmission Electron Microscopy (XTEM) was carried out using a JEOL 2100 HRTEM operated at 200 kV. Cross-sectional samples were prepared by focused ion beam etching using a FEI's Dual Beam Helios Nanolab system. For current versus voltage measurements, KEITHLEY 37100 and KEITHLEY 2602 were used.

### IV. RESULTS AND DISCUSSION

### A. 30 nm tall nanowires; use of SiO<sub>2</sub> cap and RCA clean

As stated previously, the first set of experiments were performed on 30 nm tall nanowires. In this section, only ADP P MLD was evaluated in order to optimise the process

before comparing it to beam-line ion implantation. The variables under study are the RCA clean step and the SiO<sub>2</sub> capping layer used during RTA. A schematic of the process flow is shown in Fig. 6, along with a representation of the ADP molecule used for P MLD.

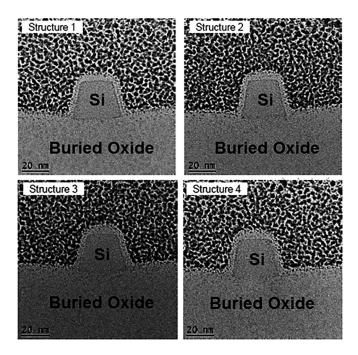

Figure 7 shows representative cross-sectional TEM images of 30 nm tall nanowires fabricated from 30 nm thick SOI substrates. In this case, 6 nm HSQ resist was used to pattern the structures by e-beam lithography. Post-RIE the four XTEM images in Fig. 7 show four nanowires from a single test structure, approximately 25 nm wide, where the nanowires were 1  $\mu$ m apart. The sidewalls of the etched nanowires are quite smooth, with a slight tapering, and the size and the shape are quite reproducible within the test structure. In other words, there is no significant difference in shape and size depending on whether we have an outer or inner wire in the set of four. Note that there is a very thin native oxide around the outside of the nanowire due to exposure to the environment.

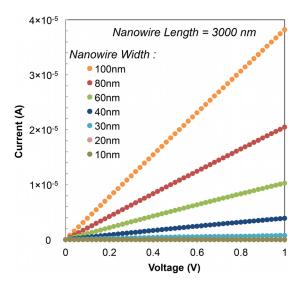

In Fig. 8 are representative current versus voltage data from Si nanowire devices that were P MLD doped, as a function of nanowire W. Other device variables L and S were constant at  $3000\,\mathrm{nm}$  and  $1000\,\mathrm{nm}$ , respectively. Current scales with W, as expected, and forms a straight line through the origin. From these data,  $R_{\mathrm{TOTAL}}$  was extracted.

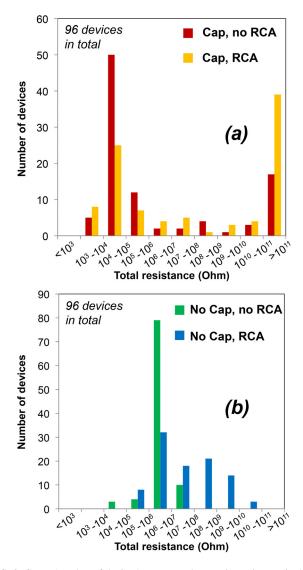

Figure 9 shows the distribution of the number of devices within a  $R_{TOTAL}$  range. In Fig. 9(a) are the devices that had a  $SiO_2$  cap during the RTA. Figure 9(b) shows the same type of plot, but for the devices without the  $SiO_2$  cap during the RTA, and it is observed that in that data there is a high count of devices in the  $R_{TOTAL} = 10^6 - 10^7 \,\Omega$  range. The RCA clean has little effect; if anything, it pushes the average  $R_{TOTAL}$

FIG. 7. Representative cross-sectional TEM images of the 30 nm tall Si nanowires after reactive ion etch. The four fingers within a single test structure are shown to demonstrate there is no significant difference between the outer and inner nanowires in terms of cross-sectional shape.

FIG. 8. Representative current versus voltage data from Si nanowire devices that were ADP P MLD doped, as a function of nanowire width. Length and spacing were constant at 3000 nm and 1000 nm, respectively. Current scales with the width, as expected. From this dataset, resistance was extracted.

FIG. 9. Count (number of devices) versus total nanowire resistance in ADP P MLD nanowire devices. (a) Devices were capped during RTA. (b) Devices were not capped during RTA. The (lack of) effect of the RCA clean is also shown.

value higher. This was also noted in Fig. 9(a), and thus the RCA clean was dropped from future experiments.

Comparing the data with cap versus without cap gave an insight into the purpose of the  ${\rm SiO_2}$  cap. In Fig. 9(a), there is a bimodal  ${\rm R_{TOTAL}}$  distribution and the lower  ${\rm R_{TOTAL}}$  values in the  $10^3$ – $10^5\,\Omega$  range look very promising, much better than those achieved without the  ${\rm SiO_2}$  cap. As a result, it was concluded that capping is an important step to include for follow-on experiments. Furthermore, in Fig. 9, we observed some very high  ${\rm R_{TOTAL}}$  values (> $10^{13}\,\Omega$ ) corresponding to open circuits arising from broken nanowire devices. It was concluded that our original HF dip step for cap oxide removal prior to contact metal deposition was too harsh and was causing the failure of some devices. Optimisation of this  ${\rm SiO_2}$  cap removal was undertaken and it will be seen in the next round of experiments to reduce the number of device failures seen here.

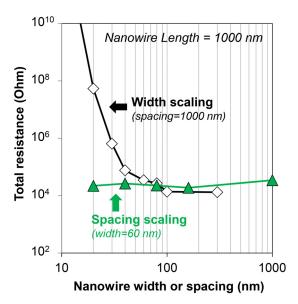

Of the four scenarios in this section, the sample set that did not have an RCA clean but did have a SiO<sub>2</sub> cap looked the most promising, thus, we examined those data more closely. Plotted in Fig. 10 is  $R_{\rm TOTAL}$  versus W for a fixed S (1  $\mu m$ ), and  $R_{\rm TOTAL}$  versus S for a fixed W (60 nm). Note that due to the device loss, as shown in Fig. 9, it was not possible here to extract  $R_{\rm CONTACT}$  for this sample set, thus we are working with  $R_{\rm TOTAL}$ , and not  $\rho$ , but this will be shown in Sec. IV B. From Fig. 10, we can conclude that  $R_{\rm TOTAL}$  increases rapidly for W < 50 nm, while remains relatively constant for S down to 20 nm. This independence of R relative to S may be due to the short nature of these devices. S scaling will be more difficult with taller features.

## B. 66 nm tall tight-pitch nanowires: MLD versus ion implant

In this part, ADP P MLD with a SiO<sub>2</sub> cap and a P ion implant are directly compared in terms of crystal damage, Si

FIG. 10. Total resistance in the P MLD doped four finger nanowire test structure that is 30 nm tall, as a function of W, with S fixed, and as a function of S with W fixed. These devices had a  ${\rm SiO_2}$  cap during RTA and had no RCA clean.

resistivity, W scaling, S scaling, and dopant activation. A schematic of the process flow is shown in Fig. 11. The lithography and patterning process was applied to 66 nm thick Si SOI in order to produce tall nanowire structures, suitable for evaluating whether MLD and ion implant can dope tall tight-pitch features with little inter-nanowire spacing. With the device trends towards tighter spacing and vertically stacked nanowires for GAA applications, doping processes must be tested on this type of test structure. In order to etch 66 nm tall nanowires, a thicker HSQ resist was used (15 nm). The RCA clean was dropped, and all devices had a SiO<sub>2</sub> cap during RTA. Due to the previous data showing device loss using a 5:1 BOE solution for cap removal, this part of the process was redesigned. The original 5:1 BOE solution was diluted further in a 5:1 ratio with DI, meaning that we had a 25:1 strength BOE solution. A test piece of unpatterned Si with the SiO2 cap was annealed side-by-side with the nanowire samples, and this was first subjected to the BOE based cap removal treatment. The sample was dipped into the solution and repeatedly checked for hydrophobicity, which is a sign SiO<sub>2</sub> had been removed. The time was noted, and this process was then repeated on the nanowire samples. Typically, for 50 nm SiO<sub>2</sub> that had been annealed at 1050 °C, the 25:1 BOE solution was applied for 2 min.

The rest of the process was unchanged. As a benchmark, a set of devices were doped using a P  $4 \times 10^{15}$  cm<sup>-2</sup> 3 keV  $45^{\circ}$  beam-line implant. This was done at room temperature, with half of the dose from the left side of the nanowires and half of the dose from the right side in the standard way.

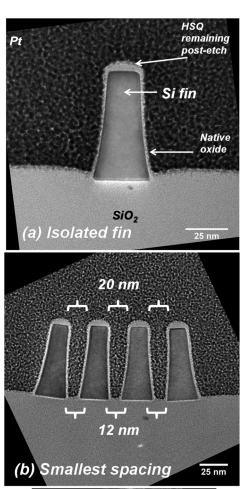

Figure 12 shows representative XTEM images of the test structures prior to doping. In Fig. 12(a) is an isolated Si nanowire which has smooth sidewalls that are slightly tapered. The bright region surrounding the Si is native oxide, seen before, due to ambient exposure. The underlying SiO<sub>2</sub> is slightly bloated on either side of the Si nanowire, but this is an XTEM imaging artefact, regularly seen in XTEM of SOI samples. This is also apparent in Fig. 12(b), where the

- · Starting wafer, 66 nm SOI

- · E-beam litho, 15 nm HSQ

- · Reactive Ion Etch, Cl<sub>2</sub> based

- P MLD

- Degrease, IPA and acetone

- HF dip

- ADP functionalisation

- Cap with SiO<sub>2</sub>

- 1050 °C RTA

- Cap removal

- Ti/Au contact pad metalisation

- P Ion Implant

- 4×10<sup>15</sup> cm<sup>-2</sup>,

45°, 3 keV

- 1050 °C RTA

- Ti/Au contact pad metalisation

FIG. 11. Schematic representation of the ADP P MLD process flow on 66 nm tall devices, and of the P ion implant control process flow.

FIG. 12. Representative cross-sectional TEM images directly after etching of the 66 nm tall So nanowire devices. (a) The isolated structures show smooth slightly tapered sidewalls. There is a small amount of HSQ resist remaining on the top of the nanowire and an approximately 1 nm thick native oxide on the sidewalls. (b) Four Si nanowires with a drawn spacing of 20 nm, resolved at the top of the features, which is 12 nm at the base of the structures. (c) The smallest feature resolved from the mask is 10 nm lines.

outer Si nanowires are leaning in towards the centre slightly. A wide view of Fig. 12(b) showed, under prolonged imaging than shown here, that the oxide on either side of the nanowires continued to bloat and expand upwards. This is possibly due to differences in self-heating of different materials (e.g., SiO<sub>2</sub> versus Si) under electron irradiation. Regardless, in Fig. 12(b), the closest features on the mask are shown, where the drawn spacing on the mask is 20 nm, but in practice, due to the tapered nature of the sidewalls, the spacing is <20 nm, approximately 12 nm at the foot of the nanowires.

Also, note that each individual nanowire in Fig. 12(b) looks like the others in that array, showing a good level of reproducibility. The outer and inner nanowires have practically the same size and shape. Finally, in Fig. 12(c) is the smallest resolved nanowire in this experiment which is 10 nm wide across the middle. Considering that the longest nanowires here are 3000 nm in length, the highest L:W aspect ratio in our nanowire devices is 300:1.

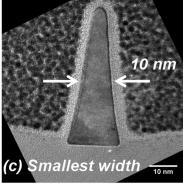

Figure 13 shows the corresponding images to Fig. 12(b), but now after doping. Figure 13(a) shows tightly packed tall nanowires after ion implant and Fig. 13(b) shows tightly packed tall nanowires after MLD. In both cases, a 1050 °C RTA was applied to activate and/or drive-in the dopant. However, note that the XTEM image in the figure is zoomed into the inner structures for clarity, and all four nanowires within each test structure showed the same trends.

For the ion implantation case, there is evidence of crystal damage. The tops of the nanowires have been partially eroded or sputtered by the implant. Also, the characteristic amorphisation and recrystallisation type defects, such as {111} twin boundaries, are clearly visible. This is due to the well-known problems of thin-body Si recrystallisation, where the many surfaces and SiO<sub>2</sub>-Si interfaces inhibit clean

FIG. 13. Representative cross-sectional TEM images taken after doping of the Si nanowires: (a) the effect of P ion implantation performed at room temperature at 45° tilts left and right. The implant is partially amorphising, and the crystal has recrystallised during the RTA, but many crystal defects are evident. Note that the tops of the nanowires are rounded due to sputter erosion during the ion implant. (b) On the other hand, the ADP P MLD process is gentle, and there are no visible twin boundary type defects visible in the nanowires.

Si crystal recovery after amorphisation. 42–45 Evidently, the P room temperature implant partially amorphised these structures. It is interesting to see the regions where twin boundaries exist in these structures. They appear well below half-way down the nanowires, despite the neighbouring nanowire shadowing the 45° beam-line implant to some degree. In fact, it appears as if a significant amount of the 3 keV P implant has passed through the nanowire into the neighbouring nanowire. The projected range of a 3 keV P implant into Si is 6.7 nm. 46

For the MLD case in Fig. 13(b), there is no erosion and the body of the Si nanowire is free from visible crystal damage like {111} twin boundaries. The sidewalls of the nanowires look as smooth as before, indicating the gentleness of the ADP P MLD with n SiO<sub>2</sub> cap process here.

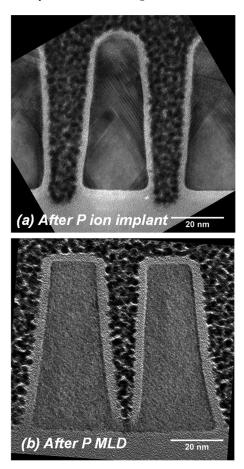

In this part of the experiment, with the improved  $SiO_2$  cap removal process, we had a better device yield, and thus were able to proceed with  $R_{CONTACT}$  extraction. Figure 14 shows a representative plot of  $R_{TOTAL}$  vs 1/W used to extract  $R_{CONTACT}$  from the y-axis intercept at x=0. This example shows data for different L, to which linear fit lines were applied. From these,  $R_{CONTACT}$  was determined from the average y-axis intercept, in this case, for P ion implant, to be  $155\,\Omega$ . From these data  $R_{NANOWIRE}$  and  $\rho$  were calculated according to Eq. (2).

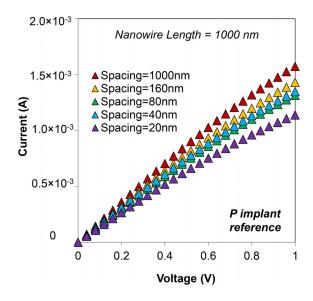

Another electrical set of data of interest at this stage was the impact of S scaling. Figure 15 shows representative current versus voltage data of devices that were P ion implant doped, as a function of S, as drawn in the mask. L and W were constant at 1000 nm and 60 nm, respectively. Current scales with spacing, due to shadowing effects during the implant. The current starts to saturate at higher voltages here; this is thought to be related to the high current densities (>1 mA) through these devices, due to the small cross-sectional areas.

After R<sub>CONTACT</sub> is subtracted out

$$R_{NANOWIRE} = \rho \frac{L}{t \cdot W},\tag{4}$$

FIG. 14. Total nanowire resistance versus 1/W, which is used to extract contact resistance. This is a representative plot showing data grouped according to nanowire L. In this case, the process is P ion implant and the  $R_{\rm CONTACT}$  is 155  $\Omega$ .

FIG. 15. Representative current versus voltage data from Si nanowire devices that were P ion implant doped, as a function of nanowire spacing (as drawn in the mask). The length and the width were constant at 1000 nm and 60 nm, respectively. Current scales with spacing, presumably due to shadowing effects.

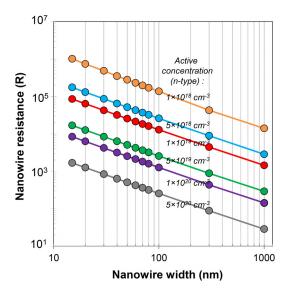

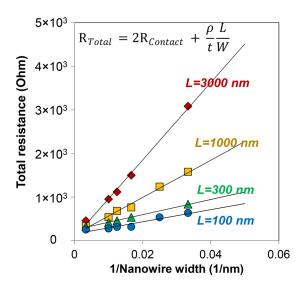

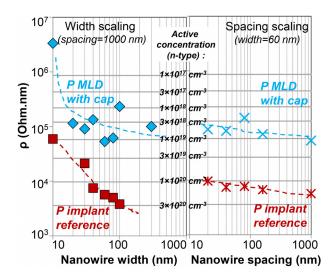

and  $\rho$  is calculated based on L, W, and t = 66 nm. These data are shown in Fig. 16 for both ADP P MLD and P ion implant, versus W scaling and S scaling. Furthermore, the active concentration was calculated from  $\rho$  according to Eq. (3), and is plotted in Fig. 16 as horizontal lines of constant active concentration (N). Once again, this assumes a constant active doping concentration within the nanowire, or could be thought of the "average" active doping concentration.

Firstly, focusing on the comparison of MLD versus ion implant, it is clear that ADP P MLD with a  $\rm SiO_2$  cap does not beat the P ion implant reference in terms of  $\rho$  and N. For ion implant N >  $10^{20}\,\rm cm^{-3}$  while for MLD it is close to  $10^{19}\,\rm cm^{-3}$ .

FIG. 16. Resistivity ( $\rho$ ) in the ADP P MLD and P ion implanted doped four finger nanowire test structures, 66 nm tall, as a function of W with S fixed, and as a function of S with W fixed. The horizontal lines represent active concentration isolines associated with  $\rho$  as calculated using the Si mobility values in Fig. 4, assuming a uniformly doped nanowire. ADP P MLD with an SiO<sub>2</sub> cap reaches approximately  $10^{19}\,\mathrm{cm}^{-3}$ , while ion implant beats  $2\times10^{20}\,\mathrm{cm}^{-3}$ .

Examining the trends of  $\rho$  versus S, it seems neither doping method has a strong dependence of S scaling down to 20 nm. Note in the XTEM shown earlier S is practically <20 nm due to the tapered sidewall on the nanowires, but for the sake of consistency we refer to the dimensions on the mask in Fig. 16 and in the discussion here. There is  $0.5\times$  reduction in average carrier concentration going from S = 1000 nm to S = 20 nm. In comparison average carrier concentration drops orders of magnitude with similar W scaling.

The S dependence of  $\rho$  is a consequence of two different effects for the two doping techniques. For the ion implant, shadowing will become a bigger problem for 45° tilt implants when the features are brought closer together. Even though there is some evidence that the 3 keV implant is partially passing through these structures, a 0.5× reduction in the average carrier concentration is significant, but not an insurmountable problem. For MLD, the wet chemistry based technique may encounter surface coverage issues related to wettability in tight spaces. Conventional MLD is a wetchemistry process, essentially where a liquid comes in contact with the semiconductor surface. As nanowire device pitches are scaled, the issue becomes whether the liquids involved can invade such tight spaces between fins and nanowires. There comes a point where pitches and spaces are just too small for wet chemistry.

The W dependence of  $\rho$  in Fig. 16 is far more significant. In the ADP P MLD with a SiO<sub>2</sub> cap case,  $\rho$  and the average carrier concentration stay relatively constant until W = 20 nm and then degrade. The first part is due to the gentle nature of MLD, avoiding crystal damage which would be strongly influenced by W, and the second part is possibly due to the increased surface-to-volume ratio, which will be discussed further later in terms of an energy barrier at the SiO<sub>2</sub>-Si interface limiting P in-diffusion. In the ion implant case,  $\rho$  and the average carrier concentration degrade consistently versus W, which is linked to worsening the crystal quality as a function of W with partially amorphising implants. It is noteworthy to see the different  $\rho$  versus W trends for MLD and ion implant, highlighting the resulting difference in crystal quality.

At this point, it is important to compare these values of  $\rho$  against those reported for Si:P epi layers with and without a laser annealing treatment. Rosseel *et al.* reported  $\rho$  in the range of 0.6 m $\Omega$  cm (= 6 × 10<sup>3</sup>  $\Omega$  nm) for Si:P epi, and  $\rho$  in the range of 0.3 m $\Omega$  cm (= 3 × 10<sup>3</sup>  $\Omega$  nm) for Si:P epi with laser annealing. <sup>22</sup> It is difficult to compare directly with our data in Fig. 16, as we do not know the W in those Si:P epi structures, but the ion implanted data here are of the same order of the Si:P epi data.

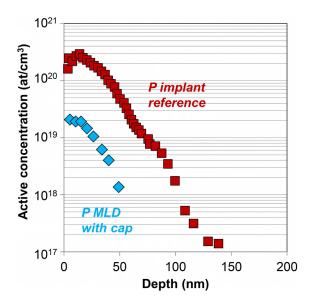

To verify the extraction of average carrier concentration via analysis of nanowire electrical characterisation, control unpatterned bulk Si samples were doped in the same way as the nanowire devices, and Electrochemical Capacitance Voltage (ECV) carrier profiling was used to the extract carrier concentration versus depth. Figure 17 shows indicative active concentration versus depth plots in bulk Si. For the P implant, the peak of the profile is approximately  $3 \times 10^{20} \, \mathrm{cm}^{-3}$ , while for ADP P MLD, it is  $2 \times 10^{19} \, \mathrm{cm}^{-3}$ ,

FIG. 17. Carrier concentration profiles versus depth into Si determined by ECV analysis on bulk Si for ADP P MLD and P ion implant. These samples were processed in conjunction with the nanowire devices.

comparable with the extracted values for N in the wide nanowires, verifying the electrical analysis.

#### C. Difficulties in phosphorus in-diffusion

The problems of doping Si by MLD, or by ion implant, are manifold. The first problem occurs ever before we can consider activation issues or producing substitutional impurities in the Si lattice. The issues with doping semiconductors can usually be simplified into two sub-problems, namely (a) how to incorporate the dopant into the target? and (b) how to activate the incorporated dopant? The first big problem for MLD is related to how do we get the dopant impurity into the target to begin with. This is easier, but not trivial, for ion implant, 48 as we can relatively easily fire ions into a fin or nanowire target with a well-controlled energy, dose, and position. MLD, on the other hand, is based on placing organic molecules containing dopant atoms on the surface, covalently bound, and thereafter in-diffusion of the dopant into the target. The apparent problem is that there is an energy barrier at the SiO<sub>2</sub>-Si interface for P incorporation, shown schematically in Fig. 18(a). P atoms sitting at that interface have to climb over a barrier to enter Si, and from there they can diffuse around during the RTA. The evidence of this potential barrier comes from the relatively low P incorporation ( $\sim 10^{19} \, \text{cm}^{-3}$ ) when the equilibrium solid solubility of P in Si at 1050 °C is  $>10^{20}$  cm<sup>-3</sup>. <sup>49,50</sup> Something must be preventing the P incorporation. It should be noted that several groups worldwide who have worked on P MLD on Si have also reported subequilibrium solid solubility concentrations of incorporated P.<sup>26-33</sup>

So what is wrong? What is causing this energy barrier at the surface? One possibility is that the P supply is not sufficient, as one monolayer of ADP molecule, based on its footprint and expected packing density, should yield a P dose of  $2 \times 10^{14} \, \mathrm{cm}^{-2}$ , but we are incorporating only approximately  $5 \times 10^{13} \, \mathrm{cm}^{-2}$ , so that is unlikely to be the root of the

FIG. 18. (a) A schematic of the energy barriers to P in-diffusion from the surface into the Si substrate. (b) An equivalent schematic of the energy barriers for interface trapping of P, already in the Si substrate, which is evident during the uphill diffusion phenomenon.

problem. If we create multilayer doping, rather than monolayer doping, that could increase the P supply, of course. On the other hand, we could consider the SiO<sub>2</sub>-Si interface to be a trapping site for dopant atoms and thus produce an energy barrier for dopant release into the Si substrate. It is quite conceivable for trap sites to have a lower energy level to other energy levels surrounding them, as depicted in Fig. 18(a). Conversely, a P atom already within the Si substrate could be trapped at the interface while diffusing around, such as is the case of uphill diffusion shown schematically in Fig. 18(b). Uphill diffusion was reported for P in Si,<sup>51,52</sup> as well as for B and As, 53–55 where there was an apparent shift of dopant profiles towards the surface during certain thermal treatments, leading to dopants moving towards regions of high concentration. The very concept of diffusion that something should move from a region of high concentration to a region of low concentration is a fairly fundamental principle, and the observation of the opposite trend is rather counterintuitive. Nevertheless, there have been many reports of uphill diffusion, or diffusion against the concentration gradient. The commonly held physical explanation of that was linked to impurity trapping at the SiO<sub>2</sub>-Si interface. <sup>56,57</sup>

Two further interesting points are to be noted at this stage: firstly, in the area of gas-phase doping, in general, P incorporation from phosphine has produced lower dopant concentrations in the  $10^{19}\,\mathrm{cm^{-3}}$  range<sup>58–60</sup> compared to the equivalent experiments on As incorporation from arsine, which has produced dopant concentrations in the  $10^{20}\,\mathrm{cm^{-3}}$  range. Secondly, Perego *et al.* have explored P *in situ*

doped Si nanocrystals with diameters on the order of 4 nm, <sup>63</sup> and have shown that P tends to be confined within Si at these dimensions, rather than go into SiO<sub>2</sub>. The surface-to-volume ratios of 4 nm diameter nanocrystals will be extremely high, much greater than in the devices tested here. Furthermore, in the *ex situ* doping problem in our system, we have a significant amount of surface C present as a by-product of the ADP MLD process. It is possible that this surface C is also playing a significant role here.

In essence, any proposed ex situ in-diffusion based process will have to overcome a surface barrier. Physically what is generating this, or creating interface traps, is open to debate. For sure, the Si lattice is imperfect in that final monolayer before the surface, and is full of irregular coordinates and bonds of unusual angles and lengths.<sup>64</sup> Added to that is the presence of C from the organic molecules used in MLD, which is a by-product of the process, may contribute to the inhibition of P uptake by Si. It is clear that there is some distance for ADP P MLD with the SiO<sub>2</sub> cap concentrations to reach  $10^{20}$  cm<sup>-3</sup>, although work is underway exploring alternative MLD methodologies at present. There are many potential ways to optimise the MLD procedure, ranging from molecule design, surface preparation methods, choice of capping layers, and alteration of the thermal treatment strategy. For example, gas-phase monolayer doping (GP-MLD),<sup>65</sup> monolayer contact doping (MLCD), 66,67 and remotemonolayer doping (R-MLD)<sup>68</sup> are just a few alternative routes to potentially improve the P retention rate within Si nanostructures. The very fact that new and novel approaches are regularly being reported in the literature in this field proves that the area is dynamic, and that new and inventive approaches are constantly being demonstrated.

### D. Difficulties in doping sub-10 nm silicon

While MLD faces specific problems, all forms of doping technologies face similar challenges as we head towards GAA devices with 5 nm Si dimensions. At these scales, other issues kick in which will need innovative solutions if conventional doping is to continue to be based on substitutional impurities in the Si crystal.

Firstly, the bandgap of Si increases with scaled dimensions<sup>69</sup> and the ionisation energy for common dopants increases,<sup>70</sup> effectively decreasing the doping efficiency,<sup>71</sup> even if the dopant atoms are substitutional. Hiller and König *et al.* have experimentally demonstrated difficulties in doping Si nanocrystals with diameters on the order of 5 nm and below.<sup>72–74</sup> Furthermore, dopant trapping<sup>75</sup> at surfaces will increase with the ever-increasing surface-to-volume ratios, as proportionately more atoms in the target will be surface atoms, or bound to surface atoms. Next, the close dielectric further increases the ionisation energy due to screening,<sup>76</sup> while electrically active interface states<sup>77</sup> will deplete a higher percentage of the Si structure, again due to the higher surface-to-volume ratios.

Innovative thinking will be needed to counteract these issues.

#### **V. CONCLUSIONS**

Regardless of the doping process, electrical characterisation of nanowire devices is essential for the proper diagnosis of any process proposed for GAA nanowire technologies. We have gone beyond the era of planar FET devices, and thus characterisation must also go beyond planar techniques and embrace non-planar type analysis. With the move towards dense pitches and tight spaced features, this aspect must also be incorporated into future works of this kind. When we are working on 5 nm Si structures, any surface etching will be amplified by the high surface-to-volume ratios, which would be a killer for devices.

In terms of evaluating ADP P MLD with a SiO<sub>2</sub> cap in Si against other doping techniques, we must be realistic in terms of where it can or cannot offer solutions. It is challenging for ADP MLD with a SiO2 cap to compete with ion implant or plasma doping, as the latter two can supersaturate the Si target, meaning that millisecond type anneals<sup>78,79</sup> can generate above-equilibrium levels of dopant activation.<sup>80</sup> As an in-diffusion based technique, MLD needs to overcome the equilibrium solubility limit in the target material, and work is progressing in this field, in this regard. On the other hand, MLD has been shown to be an extremely gentle process maintaining Si integrity both in terms of the internal crystal quality as well as external surface smoothness, making it suitable for high surface-to-volume ratio type devices. Furthermore, it is compatible with tight-pitch features, as it does not rely on the deposition of a thin-film layer, showing a relatively low  $\rho$  degradation with scaled spacings in this work.

### **ACKNOWLEDGMENTS**

This work was supported by Enterprise Ireland through the Project IP-2015-0368, and the European Union through the European Regional Development Fund (ERDF) under Ireland's European Structural and Investment Funds Programmes 2014–2020. R.D. would like to thank Eoin McCarthy at Trinity College Dublin for support with TEM analysis.

<sup>1</sup>M. J. H. Van Dal, N. Collaert, G. Doornbos, G. Vellianitis, G. Curatola, B. J. Pawlak, R. Duffy, C. Jonville, B. Degroote, E. Altamirano, E. Kunnen, M. Demand, S. Beckx, T. Vandeweyer, C. Delvaux, F. Leys, A. Hikavyy, R. Rooyackers, M. Kaiser, R. G. R. Weemaes, S. Biesemans, M. Jurczak, K. Anil, L. Witters, and R. J. P. Lander, in 2007 Digest of Technical Papers - Symposium on VLSI Technology (2007), p. 110.

<sup>2</sup>M. J. H. van Dal, G. Vellianitis, G. Doornbos, B. Duriez, T. M. Shen, C. C. Wu, R. Oxland, K. Bhuwalka, M. Holland, T. L. Lee, C. Wann, C. H. Hsieh, B. H. Lee, K. M. Yin, Z. Q. Wu, M. Passlack, and C. H. Diaz, in *Proceedings of the IEEE International Electron Devices Meeting* 2012 (2012), p. 521.

<sup>3</sup>A. Veloso, G. Hellings, M. J. Cho, E. Simoen, K. Devriendt, V. Paraschiv, E. Vecchio, Z. Tao, J. J. Versluijs, L. Souriau, H. Dekkers, S. Brus, J. Geypen, P. Lagrain, H. Bender, G. Eneman, P. Matagne, A. D. Keersgieter, W. Fang, N. Collaert, and A. Thean, in *2015 Symposium on VLSI Technology Digest of Technical Papers* (2015), p. T138.

<sup>4</sup>A. Veloso, A. D. Keersgieter, P. Matagne, N. Horiguchi, and N. Collaert, Mater. Sci. Semicond. Process. **62**, 2 (2017).

<sup>5</sup>N. Singh, A. Agarwal, L. K. Bera, T. Y. Liow, R. Yang, S. C. Rustagi, C. H. Tung, R. Kumar, G. Q. Lo, N. Balasubramanian, and D.-L. Kwong, IEEE Electron Device Lett. **27**, 383 (2006).

- <sup>6</sup>R. Gandhi, Z. Chen, N. Singh, K. Banerjee, and S. Lee, IEEE Electron Device Lett. 32, 1504 (2011).

- <sup>7</sup>K. J. Kuhn, IEEE Trans. Electron Devices **59**, 1813 (2012).

Duffy et al.

- <sup>8</sup>J. C. Ho, R. Yerushalmi, Z. A. Jacobson, Z. Fan, R. L. Alley, and A. Javey, Nat. Mater. 7, 62 (2008).

- <sup>9</sup>J. C. Ho, R. Yerushalmi, G. Smith, P. Majhi, J. Bennett, J. Halim, V. N. Faifer, and A. Javey, Nano Lett. 9, 725 (2009).

- <sup>10</sup>W. P. Voorthuijzen, M. D. Yilmaz, W. J. M. Naber, J. Huskens, and W. G. van der Wiel, Adv. Mater. 23, 1346 (2011).

- <sup>11</sup>K.-W. Ang, J. Barnett, W.-Y. Loh, J. Huang, B.-G. Min, P. Y. Hung, I. Ok, J. H. Yum, G. Bersuker, and M. Rodgers, in Proceedings of the IEEE International Electron Devices Meeting 2011 (2011), p. 35.5.1.

- <sup>12</sup>B. Long, G. Alessio Verni, J. O'Connell, J. Holmes, M. Shayesteh, D. O'Connell, and R. Duffy, in Proceedings of the 20th International Conference on Ion Implantation Technology (IIT) (2014), pp. 1–4.

- <sup>13</sup>A. Renau, ECS Trans. **35**, 173 (2011).

- <sup>14</sup>M. I. Current, Industrial Accelerators and their Applications (World Scientific Publishing Co., 2012), pp. 9-56.

- <sup>15</sup>B. Colombeau, B. Guo, H.-J. Gossmann, F. Khaja, N. Pradhan, A. Waite, K. V. Rao, C. Thomidis, K.-H. Shim, T. Henry, and N. Variam, Phys. Status Solidi A 211, 101 (2014).

- <sup>16</sup>C.-N. Ni, K. V. Rao, F. Khaja, S. Sharma, S. Tang, J. J. Chen, K. E. Hollar, N. Breil, X. Li, M. Jin, C. Lazik, J. Lee, H. Maynard, N. Variam, A. J. Mayur, S. Kim, H. Chung, M. Chudzik, R. Hung, N. Yoshida, and N. Kim, in Digest of Technical Papers - Symposium on VLSI Technology 2016 (2016), p. 7573383.

- <sup>17</sup>P. K. Chu, S. Qin, C. Chan, N. W. Cheung, and L. A. Larson, Mater. Sci. Eng., R 17, 207 (1996).

- <sup>18</sup>Y. Sasaki, K. Okashita, B. Mizuo, M. Kubota, M. Ogura, and O. Nishijima, J. Appl. Phys. 111, 013712 (2012).

- <sup>19</sup>B. H. Kim, S. M. Park, S. W. Park, Y. B. Park, H. J. Kim, and C. G. Park, Appl. Phys. Lett. 101, 213113 (2012).

- <sup>20</sup>L. Ye, M. P. de Jong, T. Kudernac, W. G. van der Wiel, and J. Huskens, Mater. Sci. Semicond. Process. 57, 166 (2017).

- <sup>21</sup>B. Long, G. Alessio Verni, J. O'Connell, M. Shayesteh, A. Gangnaik, Y. M. Georgiev, P. Carolan, D. O'Connell, K. J. Kuhn, S. B. Clendenning, R. Nagle, R. Duffy, and J. D. Holmes, Mater. Sci. Semicond. Process. 62, 196 (2017).

- <sup>22</sup>E. Rosseel, H. B. Profijt, A. Hikavyy, J. Tolle, S. Kubicek, G. Mannaert, C. L'abbé, K. Wostyn, N. Horiguchi, T. Clarysse, B. Parmentier, S. Dhayalan, H. Bender, J. W. Maes, S. Mehta, and R. Loo, ECS Trans. 64, 977 (2014).

- <sup>23</sup>A. Hikavyy, E. Rosseel, G. Eneman, P. Favia, and R. Loo, ECS Trans. 60, 497 (2014).

- <sup>24</sup>L. Pelaz, R. Duffy, M. Aboy, L. Marques, P. Lopez, I. Santos, B. J. Pawlak, M. J. H. van Dal, B. Duriez, T. Merelle, G. Doornbos, N. Collaert, L. Witters, R. Rooyackers, W. Vandervorst, M. Jurczak, M. Kaiser, R. G. R. Weemaes, J. G. M. van Berkum, P. Breimer, and R. J. P. Lander, in Technical Digest -International Electron Devices Meeting (2008), p. 4796744.

- <sup>25</sup>M. Togo, Y. Sasaki, G. Zschätzsch, G. Boccardi, R. Ritzenthaler, J. W. Lee, F. Khaja, B. Colombeau, L. Godet, P. Martin, S. Brus, S. E. Altamirano, G. Mannaert, H. Dekkers, G. Hellings, N. Horiguchi, W. Vandervorst, and A. Thean, in Symposium on VLSI Technology Digest of Technical Papers (2013), p. 196.

- <sup>26</sup>O. Hazut, A. Agarwala, T. Subramani, S. Waichman, and R. Yerushalmi, J. Visualized Exp. 2, 50770 (2013).

- <sup>27</sup>Y. Shimizu, H. Takamizawa, K. Inoue, F. Yano, Y. Nagai, L. Lamagna, G. Mazzeo, M. Perego, and E. Prati, Nanoscale 6, 706 (2014).

- <sup>28</sup>R. A. Puglisi, S. Caccamo, L. D'Urso, G. Fisichella, F. Giannazzo, M. Italia, and A. La Magna, Phys. Status Solidi A 212, 1685 (2015).

- <sup>29</sup>L. Ye, S. P. Pujari, H. Zuilhof, T. Kudernac, M. P. de Jong, W. G. van der

- Wiel, and J. Huskens, ACS Appl. Mater. Interfaces 7, 3231 (2015). <sup>30</sup>E. Arduca, M. Mastromatteo, D. D. Salvador, G. Seguini, C. Lenardi, E.

- Napolitani, and M. Perego, Nanotechnology 27, 75606 (2016). <sup>31</sup>T. Alphazan, L. Mathey, M. Schwarzwälder, T.-H. Lin, A. J. Rossini, R. L. Wischert, V. Enyedi, H. Fontaine, M. Veillerot, A. Lesage, L. Emsley, L. Veyre, F. Martin, C. Thieuleux, and C. Coperet, Chem. Mater. 28, 3634

- <sup>32</sup>J. Veerbeek, L. Ye, W. Vijselaar, T. Kudernac, W. G. van der Wiel, and J. Huskens, Nanoscale 9, 2836 (2017).

- <sup>33</sup>H. Wu, B. Guan, Y. Sun, Y. Zhu, and Y. Dan, Sci. Rep. 7, 41299 (2017).

- <sup>34</sup>J. O'Connell, G. A. Verni, A. Gangnaik, M. Shayesteh, B. Long, Y. M. Georgiev, N. Petkov, G. P. McGlacken, M. A. Morris, R. Duffy, and J. D. Holmes, ACS Appl. Mater. Interfaces 7, 15514 (2015).

- <sup>35</sup>J. O'Connell, G. Collins, G. P. McGlacken, R. Duffy, and J. D. Holmes, ACS Appl. Mater. Interfaces 8, 4101 (2016).

- <sup>36</sup>T. F. Kelly and M. K. Miller, Rev. Sci. Instrum. **78**, 031101 (2007).

- <sup>37</sup>Z. Sun, O. Hazut, B.-C. Huang, Y.-P. Chiu, C.-S. Chang, R. Yerushalmi, L. J. Lauhon, and D. N. Seidman, Nano Lett. 16, 4490 (2016).

- <sup>38</sup>P. D. Wolf, R. Stephenson, T. Trenkler, T. Clarysse, T. Hantschel, and W. Vandervorst, J. Vac. Sci. Technol. B 18, 361 (2000).

- <sup>39</sup>See http://www.itrs2.net/ for Semiconductor Technology trends and

- <sup>40</sup>S. M. Sze, *VLSI Technology* (McGraw-Hill Book Co., Singapore, 1983).

- <sup>41</sup>R. S. Muller and T. I. Kamins, *Device Electronics for Integrated Circuits*, 2nd ed. (John Wiley & Sons, New York, 1977).

- <sup>42</sup>R. Duffy, M. J. H. Van Dal, B. J. Pawlak, M. Kaiser, R. G. R. Weemaes, B. Degroote, E. Kunnen, and E. Altamirano, Appl. Phys. Lett. 90, 241912 (2007).

- <sup>43</sup>L. Pelaz, L. Marques, M. Aboy, P. Lopez, I. Santos, and R. Duffy, in Technical Digest - International Electron Devices Meeting (2009), p. 513.

- <sup>44</sup>E. Lampin and C. Krzeminski, J. Appl. Phys. **109**, 123509 (2011).

- <sup>45</sup>I. Martin-Bragado, Appl. Phys. Lett. **98**, 233109 (2011).

- <sup>46</sup>See http://www.srim.org for Modelling Interactions of Ions with Matter.

- <sup>47</sup>R. Duffy, M. J. H. van Dal, B. J. Pawlak, N. Collaert, L. Witters, R. Rooyackers, M. Kaiser, R. Weemaes, M. Jurczak, and R. Lander, in Proceedings of the European Solid-State Device Research Conference (ESSDERC) (2008), p. 334.

- <sup>48</sup>M. Shayesteh and R. Duffy, IEEE Trans. Semicond. Manuf. 28, 508

- <sup>49</sup>F. A. Trumbore, Bell Syst. Tech. J. **39**, 205 (1960).

- <sup>50</sup>P. Pichler, Intrinsic Point Defects, Impurities, and Their Diffusion in Silicon (Springer, Berlin, 2004).

- <sup>51</sup>R. Duffy, V. C. Venezia, J. Loo, M. J. P. Hopstaken, M. A. Verheijen, J. G. M. Van Berkum, G. C. J. Maas, Y. Tamminga, T. Dao, and C. Demeurisse, Appl. Phys. Lett. 86, 081917 (2005).

- <sup>52</sup>S. Ruffell, I. V. Mitchell, and P. J. Simpson, J. Appl. Phys. **97**, 123518 (2005).

- <sup>53</sup>H. C. H. Wang, C.-C. Wang, C.-S. Chang, T. Wang, P. B. Griffin, and C. H. Diaz, IEEE Electron Device Lett. 22, 65 (2001).

- <sup>54</sup>R. Duffy, V. C. Venezia, A. Heringa, T. W. T. Hüsken, M. J. P. Hopstaken, N. E. B. Cowern, P. B. Griffin, and C. C. Wang, Appl. Phys. Lett. 82, 3647 (2003).

- <sup>55</sup>M. J. P. Hopstaken, Y. Tamminga, M. A. Verheijen, R. Duffy, V. C. Venezia, and A. Heringa, Appl. Surf. Sci. 231–232, 688 (2004).

- <sup>56</sup>M. Ferri, S. Solmi, D. Giubertoni, M. Bersani, J. J. Hamilton, M. Kah, K. Kirkby, E. J. H. Collart, and N. E. B. Cowern, J. Appl. Phys. 102, 103707

- <sup>57</sup>M. Ferri, S. Solmi, A. Parisini, M. Bersani, D. Giubertoni, and M. Barozzi, J. Appl. Phys. 99, 113508 (2006).

- <sup>58</sup>B. Kalkofen, M. Lisker, and E. P. Burte, Mater. Sci. Eng., B **114–115**, 362 (2004).

- <sup>59</sup>Y. Kiyota, T. Nakamura, K. Muraki, and T. Inada, J. Electrochem. Soc. 141, 2241 (1994).

- <sup>60</sup>Y. Kiyota and T. Inada, J. Vac. Sci. Technol. A 19, 2441 (2001).

- <sup>61</sup>C. M. Ransom, T. N. Jackson, J. F. DeGelormo, C. Zeller, D. E. Kotecki, C. Graimann, D. K. Sadana, and J. Benedic, J. Electrochem. Soc. 141, 1378 (1994).

- <sup>62</sup>Y.-H. Song, K.-T. Park, H. Kurino, and M. Koyanagi, Jpn. J. Appl. Phys., Part 1 39, 26 (2000).

- <sup>63</sup>M. Perego, G. Seguini, E. Arduca, J. Frascaroli, D. De Salvador, M. Mastromatteo, A. Carnera, G. Nicotra, M. Scuderi, C. Spinella, G. Impellizzeri, C. Lenardie, and E. Napolitani, Nanoscale 7, 14469 (2015).

- <sup>64</sup>S. Pantelides, Solid State Commun. **84**, 221 (1992).

- <sup>65</sup>P. Taheri, H. M. Fahad, M. Tosun, M. Hettick, D. Kiriya, K. Chen, and A. Javey, ACS Appl. Mater. Interfaces 9, 20648 (2017).

- <sup>66</sup>O. Hazut, A. Agarwala, I. Amit, T. Subramani, S. Zaidiner, Y. Rosenwaks, and R. Yerushalmi, ACS Nano 6, 10311 (2012).

- <sup>67</sup>L. Ye, A. Gonzalez-Campo, T. Kudernac, R. Nuńez, M. de Jong, W. G. van der Wiel, and J. Huskens, Langmuir 33, 3635 (2017).

- <sup>68</sup>O. Hazut and R. Yerushalmi, Langmuir **33**, 5371 (2017).

- <sup>69</sup>L. Lin, Z. Li, J. Feng, and Z. Zhang, Phys. Chem. Chem. Phys. 15, 6063

- <sup>70</sup>G. Cantele, E. Degoli, E. Luppi, R. Magri, D. Ninno, G. Iadonisi, and S. Ossicini, Phys. Rev. B 72, 113303 (2005).

- <sup>71</sup>T.-L. Chan, M. L. Tiago, E. Kaxiras, and J. R. Chelikowsky, Nano Lett. 8,

- <sup>72</sup>D. Hiller, J. López-Vidrier, S. Gutsch, M. Zacharias, K. Nomoto, and D. König, Sci. Rep. 7, 863 (2017).

- <sup>73</sup>D. Hiller, J. López-Vidrier, S. Gutsch, M. Zacharias, M. Wahl, W. Bock, A. Brodyanski, M. Kopnarski, K. Nomoto, J. Valenta, and D. König, Sci. Rep. 7, 8337 (2017).

- <sup>74</sup>D. König, S. Gutsch, H. Gnaser, M. Wahl, M. Kopnarski, J. Göttlicher, R. Steininger, M. Zacharias, and D. Hiller, Sci. Rep. 5, 9702 (2015).

- <sup>75</sup>M. V. Fernández-Serra, C. Adessi, and X. Blase, Phys. Rev. Lett. 96, 166805 (2006).

- <sup>76</sup>M. Diarra, Y.-M. Niquet, C. Delerue, and G. Allan, Phys. Rev. B **75**, 045301 (2007).

- <sup>77</sup>M. T. Björk, H. Schmid, J. Knoch, H. Riel, and W. Riess, Nat. Nanotechnol. 4, 103 (2009).

- <sup>78</sup>S. H. Jain, P. B. Griffin, J. D. Plummer, S. McCoy, J. Gelpey, T. Selinger, and D. F. Downey, IEEE Trans. Electron Devices **52**, 1610 (2005).

- <sup>79</sup>S. Earles, M. Law, R. Brindos, K. Jones, S. Talwar, and S. Corcoran, IEEE Trans. Electron Devices 49, 1118 (2002).

- <sup>80</sup>R. Duffy, T. Dao, Y. Tamminga, K. van der Tak, F. Roozeboom, and E. Augendre, Appl. Phys. Lett. 89, 071915 (2006).