| Title                       | The role of oxide traps aligned with the semiconductor energy gap in MOS systems                                                                                                                                                                                                                                                                                                                  |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Authors                     | Caruso, Enrico;Lin, Jun;Monaghan, Scott;Cherkaoui, Karim;Gity, Farzan;Palestri, Pierpaolo;Esseni, David;Selmi, Luca;Hurley, Paul K.                                                                                                                                                                                                                                                               |  |  |

| Publication date            | 2020-08-31                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Original Citation           | Caruso, E., Lin, J., Monaghan, S., Cherkaoui, K., Gity, F., Palestri, P., Esseni, D., Selmi, L. and Hurley, P. K. (2020) 'The role of oxide traps aligned with the semiconductor energy gap in MOS systems', IEEE Transactions on Electron Devices, 67(10), pp. 4372-4378. doi: 10.1109/TED.2020.3018095                                                                                          |  |  |

| Type of publication         | Article (peer-reviewed)                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Link to publisher's version | 10.1109/TED.2020.3018095                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Rights                      | © 2020, IEEE. Personal use of this material is permitted.  Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. |  |  |

| Download date               | 2024-05-06 01:09:14                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Item downloaded from        | https://hdl.handle.net/10468/10741                                                                                                                                                                                                                                                                                                                                                                |  |  |

# The Role of Oxide Traps Aligned with the Semiconductor Energy Gap in MOS Systems

Enrico Caruso, Jun Lin, Scott Monaghan, Senior Member, IEEE, Karim Cherkaoui, Farzan Gity, Pierpaolo Palestri, Senior Member, IEEE, David Esseni, Fellow, IEEE, Luca Selmi, Fellow, IEEE, and Paul K. Hurley

Abstract—This work demonstrates that when inelastic tunneling between oxide traps and semiconductor bands is considered, the traps with energy aligned to the semiconductor bandgap play a significant role in the frequency dispersion of the capacitance-voltage (C-V) and conductance-voltage (G-V) characteristics of metal-oxide-semiconductor (MOS) systems. The work also highlights that a non-local model for tunneling into interface states is mandatory to reproduce experiments when carrier quantization in the inversion layer is accounted for. A model including these ingredients is used to evaluate the energy and depth distribution of oxide traps in a n-In<sub>0.53</sub>Ga<sub>0.47</sub>As/Al<sub>2</sub>O<sub>3</sub>MOS system, and is able to accurately fit the C-V frequency dispersion from depletion to weak inversion. The oxide trap distribution determined from the C-V response predicts the corresponding G-V dispersion with frequency.

Index Terms—Oxide Traps, Interface Traps, Defects, C-V, G-V, Multifrequency, Spectroscopy, TCAD, Tunneling, Multi-phonon, InGaAs, Al<sub>2</sub>O<sub>3</sub>, Quantum Effects, quantization, NMP

# I. INTRODUCTION

S conventional silicon based field effect transistors ap-A proach the limit of dimensional scaling, new materials and architectures are being investigated to underpin and boost the next generation of integrated circuits. Monolithic 3D cointegration of Silicon CMOS (complementary metal oxide semiconductor), opens up a range of new opportunities to enhance the functionality of systems-on-chip, to reduce power consumption and decrease the overall system cost [1], [2]. In the past decade, important steps have been made towards the integration of memory [3], [4], logic [3], [4], RF [5] and power [6] devices on Silicon wafers, using several candidates semiconducting materials, including: Ge [7], III-V semiconductors [5], [6], semiconducting oxides [4] and 2D semiconductors [8], [9]. However, the thermal budget constraints associated with monolithic 3D integration, or thermal budget limitations from the material system (e.g., III-V semiconductors), precludes the use of high temperature thermal annealing to reduce oxide defect densities in the high dielectric constant (high- $\kappa$ ) oxides used in conjunction with the alternative semiconducting channels [4], [5], [7]. This leads to defective oxides [10], [11] which result in instability, variability and degradation issues.

For these reasons, a correct understanding of the physics and characterization of the oxide defects is needed to overcome the challenges related to the fabrication process of the gate stack

Recent advances in physics based DC and AC modeling of semiconductor/insulator structures have been achieved which allow a fully physics based simulation of MOS systems, including inelastic tunneling from semiconductors to localized defects in insulators [12]. This opens the possibility to simulate, study and extract the density and distribution of electrically active oxide defects from different experimental results. As far as terminology is concerned, oxide defects are often referred to as border traps [13] to emphasize that they are physically close enough (typically < 3 nm) to the border region between the oxide/semiconductor or oxide/metal interface, to allow tunneling between these defect and free carriers in the channel or metal gate. For insulating oxides in current field effect devices, which are frequently  $\leq 6$  nm, all oxide defects are within 3 nm from the metal or semiconductor interface. so there is no distinction between border traps and oxide traps. In this case, we use the general term of oxide defects, with the notation  $D_{OX}(E, z)$  in  $[cm^{-3}eV^{-1}]$  for the density distribution with energy (E) and distance into the oxide from the semiconductor/oxide interface (z).

In this paper, the InGaAs/high- $\kappa$  MOS system is used as case study, based on the extensive range of literature for this MOS structure combined with the growing appreciation that traps in the oxide (OTs), as well as interface states (ITs), play a significant role in both the C-V and the G-V response. A physics based model for traps is employed to interpret and reproduce the multi-frequency capacitance-voltage (C-V) characteristics, that have been analyzed in several Refs. [14]– [18], even if the physical origin of dispersion and stretch out of the characteristics in depletion is still under debate [15], [16], [18]. Commonly, the frequency dispersion from depletion to inversion is attributed to an interface trap response and the accumulation frequency dispersion to oxide traps aligned at, or above, the majority carrier band edge [14]–[19]. However, using this approach is difficult to accurately reproduce the full C-V/G-V response through simulations [15]. In particular, the frequency dependent "humps" in the region of weak inversion cannot be fitted without a large electron capture time response of interface traps with energy close to the InGaAs valence band edge [16], [18]. The main limitation of this method is the attempt to explain the capacitance and conductance frequency dispersion in depletion using only interfacial states

E. Caruso, J. Lin, S. Monaghan, K. Cherkaoui, F. Gity and P. K. Hurley are with Tyndall National Institute, University College Cork, Cork, Ireland (e-mail:enrico.caruso@tyndall.ie)

P. Palestri and D. Esseni are with the Polytechnic Department of Engineering and Architecture (DPIA), University of Udine, 33100 Udine, Italy

L. Selmi is with University of Modena and Reggio Emilia (DIEF), 41125 Modena, Italy

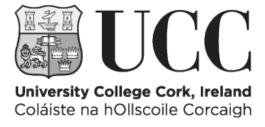

Fig. 1. Sketch of the MOS band diagram including defect and the possible trapping models. In the "standard" approach the simulations rely on the inclusion of interface traps aligned with the semiconductor bandgap, that interact with the free carrier using the local Shockley-Read-Hall (SRH) model (green circles), and oxide traps aligned with the conduction and valence band of the semiconductor, which communicate with the free carrier by elastic tunneling (magenta circles). In this work OTs are included at any energy, also aligned to the semiconductor bandgap. Free carrier and defect communicate through a non-local non-radiative multi-phonon (NMP) model with both elastic and inelastic tunneling (orange circles). In this case, the distinction between ITs and OTs simply relates to the distance from semiconductor/oxide interface.

[14], without providing a full-physical description of the carrier capture/emission process, which has to include both the tunneling through the dielectric barrier and the lattice relaxation at the interface/border trap sites. The comparison between the two different approaches is sketched in Fig. 1 and discussed more in detail in section II.

Building on the work of Ref. [14] we highlight: i) the importance of using OTs energetically aligned with the semi-conductor bandgap to reproduce and explain the "humps" of the C-V and G-V curves in weak inversion and ii) the need to use a nonlocal model to describe capture and emission from interface defects when inversion layer quantization effects are taken into account in the physical simulation. It is noted that, while we apply the model to the case of InGaAs/Al<sub>2</sub>O<sub>3</sub>, it is applicable to all MOS systems.

### II. DEVICE AND MODEL CALIBRATION

The experimental samples used in this work are 90 nm Au/ 70 nm Ni/ 6 nm Al $_2$ O $_3$ / 2  $\mu m$  n-In $_{0.53}$ Ga $_{0.47}$ As/n-InP MOS structures with a nominal S doping concentration of  $4\times10^{17}$  cm $^{-3}$  in the InGaAs epitaxial layer, as described in Ref. [20]. The C-V/G-V characteristics have been measured from 1 MHz to 1 kHz with 25 mV signal amplitude, first fixing the the gate bias (VG) and then performing the AC measurements at various frequencies, and not vice versa. In this way, transient effects due to traps dynamics are minimized yielding experimental conditions closer to the simulation environment, where the linearized small signal AC analysis is carried out after solving the stationary problem. In addition, the C-V/G-V

data was measured from accumulation to inversion and was obtained by interpreting the impedance and phase angle data of the measurement system (Agilent E4980A) as a parallel combination of a capacitance and a conductance. This is important, as the impedance and phase angle data generated by the simulation environment is converted to a capacitance and a conductance based on a parallel model.

Sentaurus [21] simulations include Fermi-Dirac statistics and multi-valley/non-parabolic band structure. Generation-recombination processes governing carriers transitions between conduction and valence bands are modeled using the Shockley-Read-Hall (SRH) theory and described by the minority carrier lifetime  $\tau_g$ . Quantum corrections of the carrier density are taken into account via the modified local density approximation [22] (MLDA). The interface traps distribution  $(D_{IT}(E) \text{ in } [cm^{-2}eV^{-1}])$  is considered in simulations using the SRH extended formalism for phonon-assisted recombination at defects in semiconductor devices. In the SRH model, the recombination center is described either by a capture cross section  $\sigma$  and a trap level  $E_T$  or as distributed levels  $D_{IT}(E)$ . For the case of oxide traps, the models for interaction of the defects with free carriers in the semiconductor conduction and valance bands requires sophisticated models accounting for the tunneling process [23]. Usually, the electrical characteristics are interpreted by modeling the OTs as a distributed network of capacitors/resistors assuming elastic tunneling, as shown in Refs. [15], [17], [24]. However, it has long been understood that charge exchange between oxide states and the channel occurs via a multi-phonon rather than an elastic tunneling process [23], [25]. For these reasons, this work employs the inelastic nonlocal band-to-trap tunneling model used in Ref. [12] which relies on the non-radiative multi-phonon (NMP) theory [23], [26]. In the NMP model, the electrically active defect is described by a trap volume  $V_T$  (equivalent to  $\sigma$  for ITs), the Huang-Rhys factor S, the phonon energy  $\hbar\omega$ , the tunneling mass m<sub>t</sub> and either a trap level localized in energy and space  $E_{T,z}$  or a distribution of levels  $D_{OX}(E,z)$ . The Huang-Rhys factor S is linked to the relaxation energy ( $E_{REL}$ ) of the defect through the relation  $E_{REL} = S\hbar\omega$ . It represents the energy that is required for the lattice relaxation process to occur [12], [27], determines the capture and emission time constants and their temperature dependence. Moreover it can be useful to identify the physical nature of the defects [28], [29]. E<sub>REL</sub> is a property of the defect and very little data on  $Al_2O_3$  is available in the literature [28], [30], [31]. To our knowledge, there isn't any experimental data which extracts S and  $\hbar\omega$  at the same time, however, the expected value for the  $Al_2O_3$  phonon energy is  $\sim 50$  meV [32], [33] and the Huang-Rhys factor reported in literature is around 12 [28], [30]. In an amorphous oxide, the parameter E<sub>REL</sub> is distributed in energy due to the non-uniformity in the local environment of the oxide lattice [34]. Although a distributed  $E_{\rm REL}$  reproduce the emission and capture time of the defects more accurately than a single value of EREL, such a fundamental description goes beyond the purpose of this work, as well as beyond the options typically available in a commercial TCAD environment. For this reason, a single value of  $E_{\rm REL}$  is employed in the simulations.

TABLE I SIMULATION PARAMETERS FOR ITS AND OTS: CAPTURE CROSS SECTION ( $\sigma$ ), TRAP VOLUME ( $V_T$ ), TUNNELING MASS ( $m_t$ ), HUANG-RHYS FACTOR (S) AND PHONON ENERGY ( $\hbar\omega$ ).

|                  |                             | ITs                                   | OTs                         |

|------------------|-----------------------------|---------------------------------------|-----------------------------|

|                  | InGaAs                      | InGaAs/Al <sub>2</sub> O <sub>3</sub> | $Al_2O_3$                   |

| $\sigma$         | -                           | $10^{-15} \text{ cm}^2 \text{ a}$     | -                           |

| $V_{\mathrm{T}}$ | -                           | -                                     | $10^{-23}~{ m cm}^3~{ m b}$ |

| $m_{\mathrm{t}}$ | $0.043  \mathrm{m_0}^{\ c}$ | -                                     | $0.23  \mathrm{m_0}^{-d}$   |

| S                | -                           | -                                     | 12 e                        |

| $\hbar\omega$    | -                           | -                                     | 48 meV f                    |

<sup>&</sup>lt;sup>a</sup> From Ref. [15] (Large spread of  $\sigma$  in the literature [35], [36]);

The capture and emission time constants depend also on the trap volume, which is a property of the defect. Most of the NMP models present in literature use the concept of capture cross section [14], [29], [31] instead of trap volume and more importantly only limited experimental data is available for Al<sub>2</sub>O<sub>3</sub> [33]. For these reasons, capture cross section values ranging between  $10^{-14}~\rm cm^2$  and  $10^{-16}~\rm cm^2$  are typically assumed for Al<sub>2</sub>O<sub>3</sub> defects. In this work, the cubic  $V_T$  is chosen to be  $10^{-23}~\rm cm^3$ , whose edge correspond to the radius on an IT with a circular capture cross section  $\sigma$  of  $1.46\times10^{-15}~\rm cm^2$ , a typical value used for interface and oxide defects. The traps dynamic parameter used in simulations are reported in Tab. I.

## III. EXPERIMENTAL RESULTS AND SIMULATIONS

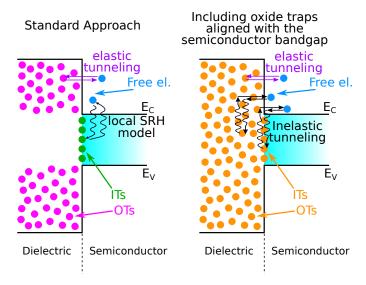

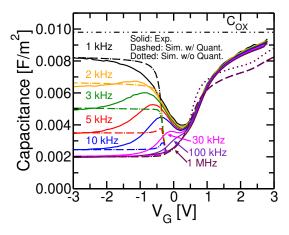

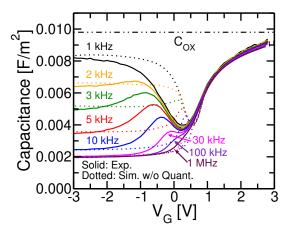

Electrically active interface and oxide traps make the experimental C-V response deviate from the ideal case. Hence, it is instructive to first consider the multi-frequency C-V characteristics of the ideal InGaAs MOS structure and the effect of the quantization model for electrons (dashed and dotted lines in Fig. 2). As expected, quantization reduces the accumulation capacitance in devices with thin oxides due to the shift of the charge centroid from the interface [39] (Fig. 3a).

The deviation between the experiments (solid lines in Fig. 2) and the ideal (no traps) case is significant, and is due to the AC and DC response of electrically active defects in the measured structures. At this point, ITs and OTs are introduced in simulations to reproduce the experimental data, using the typical approach embraced in the literature, i.e. ITs inside the InGaAs bandgap and OTs in the oxide with energies aligned with the InGaAs conduction and valence band [15]-[18], [24]. The quantum correction model is important to simulate correctly the accumulation capacitance. However, it is incompatible with IT models based on the local SRH theory because a local calculation of the emission rate relies on the carrier density at the interface [21]. When quantization is accounted for, the electron surface concentration drops dramatically for all bias regions (Fig. 3) and so does the associated emission rate.

To correctly simulate the capture and emission rates of interface traps it is then necessary either to i) neglect quantization effects, making an error in the value of the accumulation

Fig. 2. Experimental multi-frequency C-V (solid lines) at 300 K compared with ideal simulations (without traps). Simulations obtained with/without quantization for electrons are reported with dashed and dotted lines respectively. Simulations use a doping value of  $N_D=4.6\times10^{17}~cm^{-3}$  (from ECV measurements [20]) and an InGaAs minority carrier lifetime of  $\tau_g{=}80$  ps calibrated in order to match the experimental C-V in inversion. The  $C_{\rm OX}$  value used in simulations is shown with the dash-dot-dotted line and assumes an oxide thickness  $t_{\rm OX}{=}6.3$  nm (from TEM measurements [20]) and a dielectric constant of  $\varepsilon_{\rm OX}{=}7$  [20].

Fig. 3. Comparison between the electron densities extracted from simulations of Fig. 2 along the MOS structure in strong accumulation (a) and in depletion (b). The  $InGaAs/Al_2O_3$  interface is located at z=0 nm.

capacitance and consequently in the density of oxide traps needed to reproduce experiments or ii) include the quantization and then use a nonlocal model for the interaction between the defects' states and the carriers in the semiconductor.

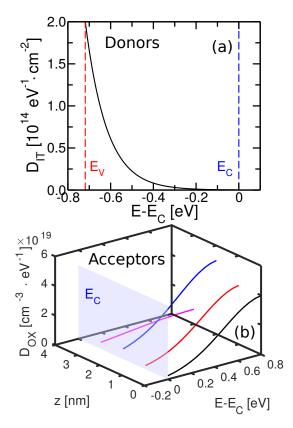

First, we analyze the consequences of using the SRH model for ITs and neglecting the quantization effects. Fig. 4 compares the experimental C-V with simulations (without quantization) including  $D_{\rm IT}(E)$  within the InGaAs bandgap and  $D_{\rm OX}(E,z)$  traps at energies primarily above  $E_{\rm C}$  in the InGaAs, shown in Fig. 5. Excellent agreement with the accumulation frequency dispersion can be achieved using the oxide trap energy/depth distribution shown in Fig. 5b. However, even if the simulated peak height of the "humps" in weak inversion match the experimental ones (Fig. 4), the width cannot be reproduced, as also reported in Ref. [15]. In fact, in order to further stretch out the "humps" an unphysically large  $D_{\rm IT}(E)$  would be necessary which, in turn, would then result in capacitance "humps" much larger than the ones observed in experiments.

<sup>&</sup>lt;sup>b</sup> From Ref. [20]; <sup>c</sup> From Ref. [37] (same as the electron effective mass);

<sup>&</sup>lt;sup>d</sup> From Ref. [38]; <sup>e</sup> From Ref. [28]; <sup>f</sup> From Ref. [32]

Fig. 4. Experimental multi-frequency C-V (solid lines) and simulated one (dotted lines) including  $D_{IT}(E)$  and  $D_{OX}(E,z)$  shown in Fig. 5. Simulations use  $N_D=3.0\times 10^{17}~cm^{-3}$  and  $\tau_g=80 ps.$  Quantization is not active.

It may be noticed in Fig. 5b that OTs located beyond 3 nm into the oxide are not considered. For our device, in fact, the maximum tunneling distance corresponding to an AC signal frequency of 1 kHz, is about 3 nm, so that oxide traps beyond this distance do not contribute to the measured C and G values. In the real device, defects may be located deeper in the oxide, however, their density and distribution cannot be determined beyond this distance due to the experimental conditions. Lower AC signal frequencies for the C-V/G-V measurements, 1/f noise below 1 kHz in MOSFET structures, or C-V hysteresis measurements are required to profile  $D_{\rm OX}(E,z)$  beyond this depth.

From the physical point of view there is no reason why the traps in the oxide should not be aligned to the InGaAs bandgap. Most works in the literature do not consider oxide traps aligned with the semiconductor bandgap, as an elastic tunneling model is employed for oxide traps [24]. As a consequence, oxide defects in this energy window are not effective since there are no semiconductor free carriers to interact with the OTs in this energy range. However, there is a large number of reports in literature based on different experiments [40], i.e. low frequency noise [41], gate leakage current [42], hysteresis [10], [43] etc., which show the presence of defects in the dielectric aligned to the bandgap of the InGaAs, whose existence has been also predicted by DFT calculations [44]. Finally, many of these experiments suggest that the transitions between the free carriers in the semiconductor and ITs/OTs are governed by inelastic processes assisted by multi-phonons [23], [25], [33]. Following all these considerations, OTs aligned to the semiconductor band gap and an inelastic nonlocal model for interaction of the defects states with electrons/holes in the semiconductor must be included in the simulations to correctly represent the physics of the experiment.

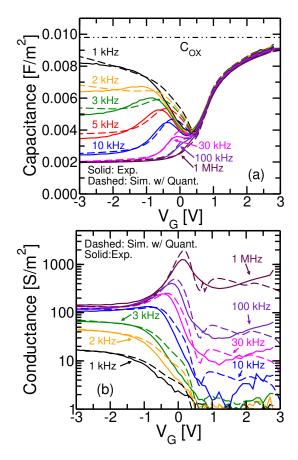

The simulated C-V response is shown together with the experimental response in Fig. 6a, where the results have been obtained by considering the  $D_{\rm OX}(E,z)$  distribution shown in Fig. 7 and a nonlocal model for electron and hole interaction with oxide defects. Consequently, quantization effects can be

Fig. 5. (a) Donor  $D_{IT}(E)$  at the InGaAs/Al $_2O_3$  interface and (b) acceptor  $D_{OX}(E,z)$  inside the Al $_2O_3$  used in Fig. 4. The energy distributions are referred to the InGaAs conduction band edge (E $_C$ ). ITs are defined with energies within the InGaAs bandgap, while OTs above E $_C$ .

taken into account, and are included in the simulation. It is important to note that this fit to the experimental data is achieved using only oxide traps which extend to the oxide/InGaAs interface. No specific distribution to represent  $D_{\rm IT}(E)$  is included at the interface (z=0).

By assuming the same oxide trap distribution used in Fig. 6a the corresponding G-V response (Fig. 6b) is predicted with remarkable accuracy and without any adjustment of the simulated parameters, suggesting again the congruity of the approach and the physics. The agreement between simulations and experiments is good, although second-order adjustments on  $D_{\rm OX}(E,z)$  may allow us to further improve the agreement. The inclusion of the OTs aligned to the InGaAs bandgap and extended up to the surface (z=0) and without any need of an additional  $D_{\rm IT}(E)$  has improved the agreement in the transition between depletion to weak inversion capacitance and conductance, which has not previously been achieved to this extent [15].

Similar conclusions, on the use of an extended OTs distribution up to the surface (z=0), without using any specific  $D_{\rm IT}(E)$ , is recently presented in Ref. [45], where a RF characterization of the OTs is carried out for  $In_{0.53}Ga_{0.47}As/Al_2O_3$  nanowires.

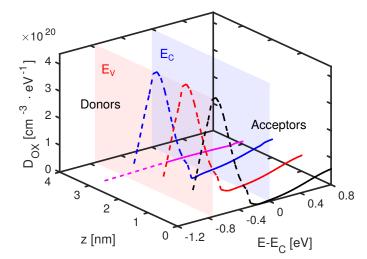

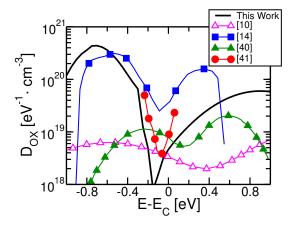

It should be noted that the energy profile of  $D_{\rm OX}(E,z)$  at a given coordinate z (Fig. 8) has shape and values similar to those obtained in other experiments and devices [10], [14], [40], [41], showing a consistency between results extracted with different approaches. It must be stressed that in the stan-

Fig. 6. Experimental (solid lines) multi-frequency C-V (a) and G-V (b) compared with simulated data (dashed lines) including quantization correction and nonlocal model for traps. Simulations use the  $D_{OX}(E,z)$  shown in Fig. 7,  $N_D=3.0\times 10^{17}~\rm cm^{-3}$  and  $\tau_g=80\rm ps.~N_D$  and  $\tau_g$  have been calibrated in order to match the experimental C-V in strong inversion.

Fig. 7.  $D_{\rm OX}(E,z)$  inside the  $Al_2O_3$  of donor and acceptor traps used in simulations of Fig. 6. The energy distributions are referred to the InGaAs conduction band edge  $(E_{\rm C})$ . It is noted that the density of donor states aligned with the InGaAs band gap, and the acceptor states at energies above  $E_{\rm C}$ , both exhibit a gradual increase with depth into the oxide (z).

Fig. 8. Comparison between the value OTs density  $D_{\rm OX}(E)$  of Fig. 7 at 1 nm inside the  $Al_2O_3$  and the OTs distribution reported in the literature from other devices and extracted from different experiments. OT distributions extracted in [40], [41] (triangle symbols) are based on DC charge trapping measurements (hysteresis and BTI), which assume a uniform distribution of the defect through the whole oxide. Therefore, the extracted effective distribution of OTs (averaged along the oxide) depends on the charging time used in the measurements and thus on the actual occupation of the deep defects in the oxide. If the charging times are not long enough to fill all the defects through the oxide, the resulting  $D_{\rm OX}(E)$  might be underestimated. The energy distributions are referred to the InGaAs conduction band ( $E_{\rm C}$ ).

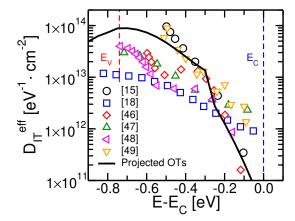

dard extraction method based on C-V and G-V response [19], i.e. Terman, high-low frequency and conductance methods, all deviations from the ideal C-V/G-V response are interpreted as interface states. As a result, these techniques yield an effective D<sub>IT</sub>(E) which consists of conventional interface states, in addition to a projection to the semiconductor/oxide interface of all oxide traps in the oxide which can respond to the DC sweep and the AC signal at a given frequency. Most of the papers that use these techniques report a rapidly increasing  $D_{\mathrm{IT}}(E)$  towards and beyond the valance band edge [15], [16], [18], [46], likely due to the projection of the 'z' distribution of OTs on the interface. To illustrate this point Fig. 9 shows the effective IT distribution  $(D_{IT}^{eff}(E))$ , obtained by spatial integration of  $D_{OX}(E,z)$  at flat band condition (no band bending), weighing the contribution of each trap in the oxide in such a way it has the same electrostatic effect of a trap placed at the interface (z=0), that is:  $D_{IT}^{eff}(E) = \int_0^{t_{OX}} \left[ D_{OX}\left(E,z\right) \left(t_{OX}-z\right) / t_{OX} \right] dz$ . These results are fairly consistent with our present work but they don't provide the spatial distribution of defects into the oxide.

# IV. CONCLUSIONS

In this work we examined the role of oxide defects aligned with the semiconductor bandgap in MOS structures. As interactions between oxide defects and free carriers in the semiconductor involve multi-phonon transitions, oxide defects at energies aligned with semiconductor bandgap do contribute to the small signal AC response of the MOS structure. In addition it is shown that, when quantum corrections are considered in the numerical calculations, the SRH model for interface states yields incorrect values of the time response. If a non-local model based on NMP theory is introduced instead, the interaction between semiconductor free carriers

Fig. 9. Comparison between the effective  $D_{IT}^{\rm eff}(E)$  obtained from Fig. 7 by the projection of all the electrically active traps at the semiconductor/oxide interface (solid black) and the  $D_{IT}(E)$  reported in the literature extracted from different devices and using standard extraction method based on C-V and G-V response. The energy distributions are referred to the InGaAs conduction band edge  $(E_C)$ .

and oxide defects (either at the interface or in the oxide) is via an inelastic tunneling process, and the distinction between interface states and oxide traps simply relates to the distance from semiconductor/oxide interface.

The model was applied to the InGaAs MOS system, which is known to exhibit a high density of electrically active defect states in the gate insulator. When OTs aligned to the semiconductor bandgap are included, the simulated response of the C-V with frequency can accurately reproduce the experimental characteristics, which is not possible when only ITs are used. The oxide trap density distribution, determined from a fit to the C-V data, also independently reproduces the corresponding G-V response over the frequency range, which is not trivial. While the model was applied to an InGaAs MOS structure in this work, the approach is generic, and is applicable to interpret the data of any MOS system affected by oxide traps.

### ACKNOWLEDGMENT

This work was supported by the European Union H2020 program SEQUENCE (Grant - 871764), SFI through AMBER 2 (12/RC/2278\_P2) and INSIGHT (Grant - 688784).

### REFERENCES

- [1] P. Batude, M. Vinet, B. Previtali, C. Tabone, C. Xu, J. Mazurier, O. Weber, F. Andrieu, L. Tosti, L. Brevard, B. Sklenard, P. Coudrain, S. Bobba, H. Ben Jamaa, P. Gaillardon, A. Pouydebasque, O. Thomas, C. Le Royer, J. . Hartmann, L. Sanchez, L. Baud, V. Carron, L. Clavelier, G. De Micheli, S. Deleonibus, O. Faynot, and T. Poiroux, "Advances, challenges and opportunities in 3D CMOS sequential integration," in *Proc. IEDM*, 2011, pp. 7.3.1–7.3.4.

- [2] N. Collaert, A. Alian, H. Arimura, G. Boccardi, G. Eneman, J. Franco, T. Ivanov, D. Lin, R. Loo, C. Merckling *et al.*, "Ultimate nanoelectronics: New materials and device concepts for scaling nanoelectronics beyond the Si roadmap," *Microelectronic Engineering*, vol. 132, pp. 218–225, 2015.

- [3] N. Collaert, "More Moore: From device scaling to 3D integration and system-technology co-optimization," in *Silicon Nanoelectronics Work-shop (SNW)*, 2017, pp. 123–124.

- [4] S. Datta, S. Dutta, B. Grisafe, J. Smith, S. Srinivasa, and H. Ye, "Back-End-of-Line Compatible Transistors for Monolithic 3-D Integration," *IEEE Micro*, vol. 39, no. 6, pp. 8–15, 2019.

- [5] S. Andric, L. Ohlsson Fhager, F. Lindelöw, O.-P. Kilpi, and L.-E. Wernersson, "Low-temperature back-end-of-line technology compatible with III-V nanowire MOSFETs," *Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena*, vol. 37, no. 6, p. 061204, 2019.

- [6] X. Li, M. Van Hove, M. Zhao, K. Geens, V. Lempinen, J. Sormunen, G. Groeseneken, and S. Decoutere, "200 V Enhancement-Mode p-GaN HEMTs Fabricated on 200 mm GaN-on-SOI With Trench Isolation for Monolithic Integration," *IEEE Electron Device Lett.*, vol. 38, no. 7, pp. 918–921, 2017.

- [7] "3D monolithic integration: Technological challenges and electrical results, author=Vinet, M and Batude, P and Tabone, C and Previtali, B and LeRoyer, C and Pouydebasque, A and Clavelier, L and Valentian, A and Thomas, O and Michaud, S and others," *Microelectronic Engineering*, vol. 88, no. 4, pp. 331–335, 2011.

- [8] L. Ansari, S. Monaghan, N. McEvoy, C. Ó. Coileáin, C. P. Cullen, J. Lin, R. Siris, T. Stimpel-Lindner, K. F. Burke, G. Mirabelli et al., "Quantum confinement-induced semimetal-to-semiconductor evolution in large-area ultra-thin PtSe 2 films grown at 400° C," npj 2D Materials and Applications, vol. 3, no. 1, pp. 1–8, 2019.

- [9] P. Bolshakov, A. Khosravi, P. Zhao, P. K. Hurley, C. L. Hinkle, R. M. Wallace, and C. D. Young, "Dual-gate MoS2 transistors with sub-10 nm top-gate high-k dielectrics," *Applied Physics Letters*, vol. 112, no. 25, p. 253502, 2018.

- [10] J. Franco, A. Vais, S. Sioncke, V. Putcha, B. Kaczer, B. . Shie, X. Shi, R. Mahlouji, L. Nyns, D. Zhou, N. Waldron, J. W. Maes, Q. Xie, M. Givens, F. Tang, X. Jiang, H. Arimura, T. Schram, L. . Ragnarsson, A. Sibaja Hernandez, G. Hellings, N. Horiguchi, M. Heyns, G. Groeseneken, D. Linten, N. Collaert, and A. Thean, "Demonstration of an InGaAs gate stack with sufficient PBTI reliability by thermal budget optimization, nitridation, high-k material choice, and interface dipole," in *IEEE Symposium on VLSI Technology Technical Digest*, 2016, pp. 1–2.

- [11] P. Zhao, A. Khosravi, A. Azcatl, P. Bolshakov, G. Mirabelli, E. Caruso, C. L. Hinkle, P. K. Hurley, R. M. Wallace, and C. D. Young, "Evaluation of border traps and interface traps in HfO<sub>2</sub>/MoS<sub>2</sub> gate stacks by capacitance–voltage analysis," 2D Materials, vol. 5, no. 3, p. 031002, 2018.

- [12] A. Palma, A. Godoy, J. A. Jiménez-Tejada, J. E. Carceller, and J. A. López-Villanueva, "Quantum two-dimensional calculation of time constants of random telegraph signals in metal-oxide-semiconductor structures," *Phys. Rev. B*, vol. 56, pp. 9565–9574, Oct 1997.

- [13] D. M. Fleetwood, "Border traps' in MOS devices," *IEEE Transactions on Nuclear Science*, vol. 39, no. 2, pp. 269–271, 1992.

- [14] G. Sereni, L. Vandelli, D. Veksler, and L. Larcher, "A New Physical Method Based on CV-GV Simulations for the Characterization of the Interfacial and Bulk Defect Density in High-κ/III-V MOSFETs," *IEEE Trans. on Electron Devices*, vol. 62, no. 3, pp. 705–712, March 2015.

- [15] G. Brammertz, A. Alian, D. H. C. Lin, M. Meuris, M. Caymax, and W. E. Wang, "A Combined Interface and Border Trap Model for High-Mobility Substrate Metal-Oxide-Semiconductor Devices Applied to In<sub>0.53</sub>Ga<sub>0.47</sub>As and InP Capacitors," IEEE Trans. on Electron Devices, vol. 58, no. 11, pp. 3890–3897, Nov 2011.

- [16] I. Krylov, "Determination of physical mechanism responsible for the capacitance-voltage weak inversion "hump" phenomenon in n-InGaAs based metal-oxide-semiconductor gate stacks," *Journal of Vacuum Sci*ence & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena, vol. 37, no. 3, p. 031202, 2019.

- [17] M. Rahman, D.-H. Kim, T.-W. Kim et al., "Border Trap Characterizations of Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> Bilayer Films Based on Ambient Post Metal Annealing and Constant Voltage Stress," Nanomaterials, vol. 10, no. 3, p. 527, 2020.

- [18] H. Chen, Y. Yuan, B. Yu, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, "Interface-State Modeling of Al<sub>2</sub>O<sub>3</sub> –InGaAs MOS From Depletion to Inversion," *IEEE Trans. on Electron Devices*, vol. 59, no. 9, pp. 2383–2389, 2012.

- [19] R. Engel-Herbert, Y. Hwang, and S. Stemmer, "Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces," *Journal of Applied Physics*, vol. 108, no. 12, 2010.

- [20] E. Caruso, J. Lin, K. F. Burke, K. Cherkaoui, D. Esseni, F. Gity, S. Monaghan, P. Palestri, P. Hurley, and L. Selmi, "Profiling bordertraps by TCAD analysis of multifrequency CV-curves in Al<sub>2</sub>O<sub>3</sub>/InGaAs stacks," in *Proc. EuroSOI-ULIS*, 2018, pp. 1–4.

- [21] Synopsys inc, Sentaurus Device L ver., 2016.

- [22] G. Paasch and H. Übensee, "A Modified Local Density Approximation. Electron Density in Inversion Layers," *Physica Status Solidi (b)*, vol. 113, no. 1, pp. 165–178, 1982.

- [23] T. Grasser, "Stochastic charge trapping in oxides: From random tele-graph noise to bias temperature instabilities," *Microelectronic Reliability*, vol. 52, no. 1, pp. 39–70, 2012.

- [24] Y. Yuan, L. Wang, B. Yu, B. Shin, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. Rodwell, and Y. Taur, "A Distributed Model for Border Traps in Al<sub>2</sub>O<sub>3</sub> – InGaAs MOS Devices," *IEEE Electron Device Lett.*, vol. 32, no. 4, pp. 485–487, 2011.

- [25] M. Kirton and M. Uren, "Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise," Advances in Physics, vol. 38, no. 4, pp. 367–468, 1989.

- [26] L. Vandelli, A. Padovani, L. Larcher, R. G. Southwick, W. B. Knowlton, and G. Bersuker, "A Physical Model of the Temperature Dependence of the Current Through SiO<sub>2</sub>/HfO<sub>2</sub> Stacks," *IEEE Trans. on Electron Devices*, vol. 58, no. 9, pp. 2878–2887, 2011.

- [27] C. Henry and D. V. Lang, "Nonradiative capture and recombination by multiphonon emission in GaAs and GaP," *Phys. Rev. B*, vol. 15, no. 2, p. 989, 1977.

- [28] A. Padovani, B. Kaczer, M. Pešić, A. Belmonte, M. Popovici, L. Nyns, D. Linten, V. V. Afanas'ev, I. Shlyakhov, Y. Lee, H. Park, and L. Larcher, "A Sensitivity Map-Based Approach to Profile Defects in MIM Capacitors From I V , C V , and G V Measurements," IEEE Trans. on Electron Devices, vol. 66, no. 4, pp. 1892–1898, 2019.

- [29] W. Gös, Y. Wimmer, A.-M. El-Sayed, G. Rzepa, M. Jech, A. L. Shluger, and T. Grasser, "Identification of oxide defects in semiconductor devices: A systematic approach linking DFT to rate equations and experimental evidence," *Microelectronic Reliability*, vol. 87, pp. 286–320, 2018.

- [30] Q. Smets, A. S. Verhulst, E. Simoen, D. Gundlach, C. Richter, N. Collaert, and M. M. Heyns, "Calibration of Bulk Trap-Assisted Tunneling and Shockley-Read-Hall Currents and Impact on InGaAs Tunnel-FETs," *IEEE Trans. on Electron Devices*, vol. 64, no. 9, pp. 3622–3626, 2017

- [31] A. Vais, H.-C. Lin, C. Dou, K. Martens, T. Ivanov, Q. Xie, F. Tang, M. Givens, J. Maes, N. Collaert et al., "Temperature dependence of frequency dispersion in III–V metal-oxide-semiconductor CV and the capture/emission process of border traps," Applied Physics Letters, vol. 107, no. 5, p. 053504, 2015.

- [32] M. Fischetti, D. Neumayer, and E. Cartier, "Effective electron mobility in Si inversion layers in MOS systems with a high-k insulator: The role of remote phonon scattering," *Journal of Applied Physics*, vol. 90, no. 9, p. 4587, 2001.

- [33] Y. N. Novikov, A. Vishnyakov, V. Gritsenko, K. Nasyrov, and H. Wong, "Modeling the charge transport mechanism in amorphous Al<sub>2</sub>O<sub>3</sub> with multiphonon trap ionization effect," *Microelectronic Reliability*, vol. 50, no. 2, pp. 207–210, 2010.

- [34] G. Rzepa, J. Franco, B. O'Sullivan, A. Subirats, M. Simicic, G. Hellings, P. Weckx, M. Jech, T. Knobloch, M. Waltl, P. J. Roussel, D. Linten, B. Kaczer, and T. Grasser, "Comphy — A Compact-Physics Framework for Unified Modeling of BTI," *Microelectronics Reliability*, vol. 85, pp. 49–65, 2018.

- [35] G. Brammertz, H. Lin, K. Martens, D. Mercier, C. Merckling, J. Penaud, C. Adelmann, S. Sioncke, W. Wang, M. Caymax et al., "Capacitance– voltage characterization of GaAs–oxide interfaces," *Journal of the Electrochemical Society*, vol. 155, no. 12, pp. H945–H950, 2008.

- [36] R. Engel-Herbert, Y. Hwang, and S. Stemmer, "Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces," *Journal of Applied Physics*, vol. 108, no. 12, p. 124101, 2010.

- [37] I. Vurgaftman, J. R. Meyer, and L. R. Ram-Mohan, "Band parameters for III-V compound semiconductors and their alloys," *Journal of Applied Physics*, vol. 89, no. 11, p. 5815, 2001.

- [38] M. Groner, J. Elam, F. Fabreguette, and S. M. George, "Electrical characterization of thin Al<sub>2</sub>O<sub>3</sub> films grown by atomic layer deposition on silicon and various metal substrates," *Thin solid films*, vol. 413, no. 1-2, pp. 186–197, 2002.

- [39] Donghyun Jin, D. Kim, Taewoo Kim, and J. A. del Alamo, "Quantum capacitance in scaled down III–V FETs," in *Proc. IEDM*, 2009, pp. 1–4.

- [40] J. Franco, V. Putcha, A. Vais, S. Sioncke, N. Waldron, D. Zhou, G. Rzepa, P. J. Roussel, G. Groeseneken, M. Heyns *et al.*, "Characterization of oxide defects in InGaAs MOS gate stacks for high-mobility n-channel MOSFETs," in *Proc. IEDM*. IEEE, 2017, pp. 7–5.

- [41] M. Hellenbrand, O.-P. Kilpi, J. Svensson, E. Lind, and L.-E. Wernersson, "Low-frequency noise in nanowire and planar III-V MOSFETs," *Microelectronic Engineering*, vol. 215, p. 110986, 2019.

- [42] G. Sereni, L. Larcher, L. Vandelli, D. Veksler, T. Kim, D. Koh, and G. Bersuker, "A novel technique exploiting C-V, G-V and I-V simulations to investigate defect distribution and native oxide in high-κ dielectrics for III-V MOSFETs," *Microelectronic Engineering*, vol. 147, pp. 281–284, 2015.

- [43] P. Pavan, N. Zagni, F. M. Puglisi, A. Alian, A. V.-Y. Thean, N. Collaert, and G. Verzellesi, "The impact of interface and border traps on current–voltage, capacitance–voltage, and split-CV mobility measurements in InGaAs MOSFETs," *physica status solidi* (a), vol. 214, no. 3, p. 1600592, 2017.

- [44] M. Choi, A. Janotti, and C. G. Van de Walle, "Native point defects and dangling bonds in  $\alpha$ -Al<sub>2</sub>O<sub>3</sub>," *Journal of Applied Physics*, vol. 113, no. 4, p. 044501, 2013.

- [45] M. Hellenbrand, E. Lind, O.-P. Kilpi, and L.-E. Wernersson, "Effects of traps in the gate stack on the small-signal RF response of III-V nanowire MOSFETs," *Solid State Electronics*, p. 107840, 2020.

- [46] V. Djara, T. O'Regan, K. Cherkaoui, M. Schmidt, S. Monaghan, É. O'Connor, I. Povey, D. O'Connell, M. Pemble, and P. Hurley, "Electrically active interface defects in the InO. 53GaO. 47As MOS system," *Microelectronic Engineering*, vol. 109, pp. 182–188, 2013.

- [47] G. Brammertz, H.-C. Lin, M. Caymax, M. Meuris, M. Heyns, and M. Passlack, "On the interface state density at In<sub>0.53</sub>Ga<sub>0.47</sub>As/oxide interfaces," *Applied Physics Letters*, vol. 95, no. 20, p. 202109, 2009.

- [48] G. Brammertz, H. Lin, K. Martens, A.-R. Alian, C. Merckling, J. Penaud, D. Kohen, W.-E. Wang, S. Sioncke, A. Delabie *et al.*, "Electrical properties of III-V/oxide interfaces," *ECS transactions*, vol. 19, no. 5, pp. 375–386, 2009.

- [49] D. Veksler, G. Bersuker, H. Madan, L. Morassi, and G. Verzellesi, "Extraction of interface state density in oxide/III–V gate stacks," Semiconductor Science and Technology, vol. 30, no. 6, p. 065013, 2015.